VSC8244

Data Sheet

Quad 10/100/1000BASE-T PHY with RGMII and RTBI Interfaces

1 General Description

Ideally suited for high port density Gigabit Ethernet switches

and routers, or multi-port Network Interface Cards (NICs),

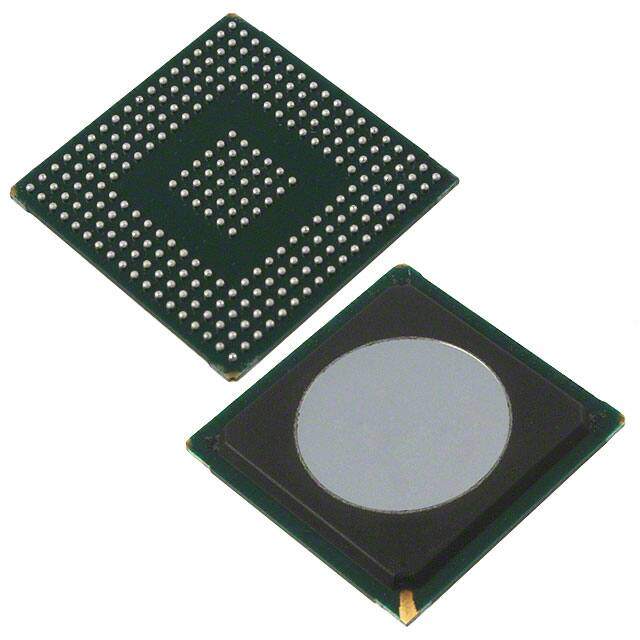

Microsemi's VSC8244 integrates four low-power, triple speed

(10BASE-T, 100BASE-TX, and 1000BASE-T) Ethernet

transceivers in thermally-enhanced, 260-pin plastic Ball Grid

Array (BGA).

Each of the four independent triple-speed transceivers

features pin-efficient RGMII and RTBI compliant MAC

interfaces. On-chip RGMII/RTBI series termination resistors

simplify board design challenges by improving signal integrity

and completely eliminating dozens of external series

termination resistors on the receive side of the MAC

interface. In addition, the VSC8244 integrates, for the first

time in the industry, all copper media side line termination

resistors.

The VSC8244 physical layer "PHY" IC leverages Microsemi’s

proprietary 4th generation DSP Technology. Microsemi's

highly optimized DSP architecture yields industry leading

performance at less than 640mW per port, supporting

1000BASE-T with respect to all worst case impairments

(NEXT, FEXT, Echo, and system noise sources).

The VeriPHY® suite has the ability to identify the cable length

and operating conditions and to isolate common faults that

can occur on Cat5 twisted pair cabling.

2 System Diagrams

RGMII, RTBI

1.2 v

3.3 v

10/100/1000 Mbps

Ethernet MAC

10/100/1000 Mbps

Ethernet MAC

VSC8244

Quad 10/100/1000BASE-T

Transceiver

10/100/1000 Mbps

Ethernet MAC

10/100/1000 Mbps

Ethernet MAC

SimpliPHY d

Magnetics

RJ-45

SimpliPHY d

Magnetics

RJ-45

SimpliPHY d

Magnetics

RJ-45

SimpliPHY d

Magnetics

RJ-45

MDC, MDIO

Management

I/F

MDINT#_n

Serial

I/F

Optional

EEPROM

Figure 1. VSC8244 System Diagram

VMDS-10108 Revision 4.2

February 2019

Microsemi Corporation One Enterprise, Aliso Viejo, CA 92656 USA

sales.support@microsemi.com www.microsemi.com

1 of 3

�VSC8244

Data Sheet

3 Features

Benefits

•

Quad, low power, 10/100/1000BASE-T in a

19mm HS-BGA package

•

Catalyzes market for low-cost & high density LAN, WAN,

SAN, & MAN switches

•

Lowest power consumption in the industry at less than

640mW/port (1000BASE-T mode)

•

Eliminates heatsinks and fans for Gigabit to the desktop

LAN switches

•

Supports PICMG 2.16 and 3.0 Ethernet backplanes at

less than 500 mW/port

•

Lowest power mode reduces supply costs

•

Removes 12 passive components per PHY*, reducing

PCB area & cost by 50%

•

Saves up to 50% on magnetic module cost with

SimpliPHY’d magnetics

•

Enables magnetic-less PICMG backplane designs

•

Patented, low EMI line driver with integrated line side

termination resistors

•

Supports RGMII v1.3 (2.5V & 3.3V) & v2.0 (1.5V HSTL)

•

Compatible with a wide variety of parallel I/F switch ICs

•

User-programmable RGMII timing compensation

•

Simplifies PCB layout; eliminates PCB trombones

•

Compliant with IEEE 802.3 (10BASE-T, 100BASE-TX,

1000BASE-T) specifications

•

Ensures seamless deployment throughout copper

networks with industry’s highest tolerance to noise and

substandard cable plants

•

>10kB jumbo frame support with programmable

synchronization FIFOs

•

Provides for maximum jumbo frame sizes in custom

SAN and LAN systems

•

Five Direct drive LEDs per port with on-chip filtering or

serial LED interface option

•

Eliminates external components and EMI issues

•

Three user configuration options: 1) optional serial

EEPROM, 2) hardware configuration pins, or 3) Serial

Management Interface (SMI)

•

Offers design engineer a solution to fit any unmanaged

or managed system requirement

•

Full suite of BIST, near-end, and far-end loopback

modes

•

Simplifies comprehensive in-system test to ensure

highest product quality

•

VeriPHY® cable diagnostics

•

Identifies cable length and operating conditions to

isolate common faults that can occur on Cat5 twisted

pair cabling

•

Automatic detection and correction of cable pair swaps,

pair skew and pair polarity, along with HP Auto MDI/

MDI-X crossover function

•

Compatible with 1st generation 1000BASE-T PHYs.

•

Supports Auto MDI/MDI-X even when Autonegotiation is

disabled

Manufactured in advanced 0.13µm, 3.3V/1.2V digital

CMOS process

•

Most cost effective technology eliminates more

expensive analog process variants

•

* or, 576 components for a 48-port switch

4 Applications

•

•

•

High Port Density 10/100/1000BASE-T Switches

Workgroup LAN Switches & Routers

Backplane Applications such as PICMG 2.16, 3.0

•

•

Gigabit Ethernet-based SAN, NAS, and MAN Systems

High Performance Workstations & Multi-Port Server NICs

2 of 3

VMDS-10108 Revision 4.2

February 2019

3

�VSC8244

Data Sheet

5 Device Block Diagram

MAC I/F

TXD[3:0]_n

TX_CTL_n

TX_CLK_n

RXD[3:0]_n

RX_CTL_n

RGMII

or

RTBI

RX_CLK_n

Interface Selection and Autonegotiation

PCS

PMA (DSP Data Pump)

MDI (Analog Front End )

TX FIR

PCS ENCODER

PAM -5 SYMBOL

MAPPER ,

SCRAMBLER

DAC

HYBRID

TXVP_A_n

TXVN_A_n

NC1

NC2

NC3

EC

TXVP_B_n

TXVN_B_n

PCS DECODER

PAM -5 SYMBOL DEMAPPER ,

DESCRAMBLER

TRELLIS

DECODER

FFE

+

ADC

VGA

X4

TXVN_D_n

TIMING RECOVERY

XTAL1/2

CONTROL

REF_FILT

MDC

MDINT_n

EEDAT

SYSTEM

JTAG

TEST

MANAGER

SOFT_RESET

MDIO

CLK125micro

MANAGEMENT

INTERFACE

LED INTERFACE

TMS

TRST

TCK

TDO

TDI

Figure 2. VSC8244 Block Diagram1

= port number (0, 1, 2, 3)

3 of 3

VMDS-10108 Revision 4.2

February 2019

REF_REXT

CLK125MAC

EECLK

1n

TXVP_C_n

TXVN_C_n

TXVP_D_n

4

CMODE[7:0]

RESET

Port 3

Port 2

Port 1

Port 0

3

LED[4:0]_n

�VSC8244

Data Sheet

Contents

1

General Description ......................................................................................................................................... 1

2

System Diagrams ............................................................................................................................................. 1

3

Features............................................................................................................................................... Benefits2

4

Applications ...................................................................................................................................................... 2

5

Device Block Diagram...................................................................................................................................... 3

6

Relevant Specifications & Documentation .................................................................................................. 12

7

VSC8244 Differences vs. VSC8224/VSC8234 Devices ................................................................................ 13

7.1

VSC8244 Functional Differences ..............................................................................................................................13

7.2

VSC8244 Register Differences .................................................................................................................................13

7.3

VSC8244 Pinout Differences ....................................................................................................................................14

8

Data Sheet Conventions ................................................................................................................................ 14

9

Package Pin Assignments & Signal Descriptions....................................................................................... 15

9.1

260 HS-PBGA Package Ball Diagram ......................................................................................................................15

9.2

BGA Ball to Signal Name Cross Reference (LEFT side) .........................................................................................16

9.3

BGA Ball to Signal Name Cross Reference (RIGHT side) ........................................................................................17

9.4

Signal Type Descriptions ..........................................................................................................................................18

9.5

MAC Transmit Interface (MAC TX) Pins ...................................................................................................................19

9.6

MAC Receive Interface (MAC RX) Pins ....................................................................................................................20

9.7

Twisted Pair Interface Pins .......................................................................................................................................21

9.8

Serial Management Interface Pins (IEEE SMI) .........................................................................................................22

9.9

Serial EEPROM Interface Pins .................................................................................................................................23

9.10

Configuration and Control Pins .................................................................................................................................23

9.11

System Clock Interface Pins .....................................................................................................................................24

9.12

LED Interface Pins ....................................................................................................................................................24

9.13

JTAG Test Access Port Pins .....................................................................................................................................25

9.14

Analog Bias Pins .......................................................................................................................................................25

9.15

HSTL Voltage Reference Pins .................................................................................................................................. 25

9.16

No Connect Pins ...................................................................................................................................................... 26

9.17

Power Supply Pins ....................................................................................................................................................26

9.18

Power Supply and Associated Functional Pins .........................................................................................................27

10 System Schematics........................................................................................................................................ 28

10.1

Input Clock Options ..................................................................................................................................................29

10.2

Analog Bias Pins Configuration ................................................................................................................................30

11 MAC Interfaces ............................................................................................................................................... 31

11.1

RGMII MAC I/F .........................................................................................................................................................31

11.2

RTBI MAC I/F ............................................................................................................................................................32

4 of 7

VMDS-10108 Revision 4.2

February 2019

7

�VSC8244

Data Sheet

12 Twisted Pair Interface..................................................................................................................................... 33

12.1

Twisted Pair Autonegotiation (IEEE802.3 Clause 28) ...............................................................................................33

12.2

Twisted Pair Auto MDI/MDI-X Function .....................................................................................................................34

12.3

Auto MDI/MDI-X in Forced 10/100 Link Speeds .......................................................................................................34

12.4

Twisted Pair Link Speed Downshift ..........................................................................................................................34

13 Transformerless Ethernet Operation for PICMG 2.16 and 3.0 IP-based Backplanes ............................... 35

14 Serial Management Interface (SMI) ............................................................................................................... 35

14.1

SMI Interrupt .............................................................................................................................................................36

15 Parallel LED Interface..................................................................................................................................... 38

16 Serial LED Output........................................................................................................................................... 41

17 Test Mode Interface (JTAG) ........................................................................................................................... 42

17.1

Supported Instructions and Instruction Codes ..........................................................................................................43

17.2

Boundary-Scan Register Cell Order .........................................................................................................................44

18 VeriPHY Cable Diagnostics ........................................................................................................................... 45

19 ActiPHY Power Management......................................................................................................................... 46

19.1

Operation in ActiPHY Mode ......................................................................................................................................46

19.2

Low power state ........................................................................................................................................................47

19.3

LP Wake up state ......................................................................................................................................................47

19.4

Normal operating state .............................................................................................................................................47

20 Ethernet In-line Powered Device Support .................................................................................................... 48

20.1

Cisco In-Line Powered Device Detection ..................................................................................................................48

20.2

In-Line Power Ethernet Switch Diagram ...................................................................................................................48

20.3

In-Line Powered Device Detection (Cisco Method) ..................................................................................................49

20.4

IEEE 802.3af (DTE Power via MDI) ..........................................................................................................................49

21 Advanced Test Modes .................................................................................................................................... 49

21.1

Ethernet Packet Generator (EPG) ............................................................................................................................49

21.2

CRC Counter ............................................................................................................................................................49

21.3

Far-end Loopback .....................................................................................................................................................50

21.4

Near-end Loopback ..................................................................................................................................................50

21.5

Connector Loopback .................................................................................................................................................51

22 Initialization & Configuration......................................................................................................................... 52

22.1

Resets .......................................................................................................................................................................52

22.2

Power-Up Sequence .................................................................................................................................................52

22.3

CMODE Pin Configuration ........................................................................................................................................52

22.4

EEPROM Interface ...................................................................................................................................................55

23 MII Register Set............................................................................................................................................... 61

23.1

MII Extended Page Registers ...................................................................................................................................62

23.3

MII Register Quick Reference .................................................................................................................................63

5 of 7

VMDS-10108 Revision 4.2

February 2019

7

�VSC8244

Data Sheet

23.4

MII Register Quick Reference - Extended Page Mode .............................................................................................65

24 MII Register Descriptions .............................................................................................................................. 66

24.1

Register 0 (00h) – Mode Control Register ................................................................................................................66

24.2

Register 1 (01h) – Mode Status Register ..................................................................................................................67

24.3

Register 2 (02h) – PHY Identifier Register #1 ...........................................................................................................67

24.4

Register 3 (03h) – PHY Identifier Register #2 ...........................................................................................................67

24.5

Register 4 (04h) – Auto-Negotiation Advertisement Register ...................................................................................68

24.6

Register 5 (05h) – Auto-Negotiation Link Partner Ability Register ............................................................................68

24.7

Register 6 (06h) – Auto-Negotiation Expansion Register .........................................................................................68

24.8

Register 7 (07h) – Auto-Negotiation Next-Page Transmit Register ..........................................................................69

24.9

Register 8 (08h) – Auto-Negotiation Link Partner Next-Page Receive Register .......................................................69

24.10 Register 9 (09h) – 1000BASE-T Control Register ....................................................................................................70

24.11 Register 10 (0Ah) – 1000BASE-T Status Register ...................................................................................................72

24.12 Register 11 (0Bh) – Reserved Register ....................................................................................................................72

24.13 Register 12 (0Ch) – Reserved Register ....................................................................................................................72

24.14 Register 13 (0Dh) – Reserved Register ....................................................................................................................72

24.15 Register 14 (0Eh) – Reserved Register ....................................................................................................................73

24.16 Register 15 (0Fh) – 1000BASE-T Status Extension Register #1 ..............................................................................73

24.17 Register 16 (10h) – 100BASE-TX Status Extension Register ..................................................................................74

24.18 Register 17 (11h) – 1000BASE-T Status Extension Register #2 ..............................................................................74

24.19 Register 18 (12h) – Bypass Control Register ...........................................................................................................75

24.20 Register 19 (13h) – Reserved................................................................................................................................... 77

24.21 Register 20 (14h) – Reserved ...................................................................................................................................77

24.22 Register 21 (15h) – Reserved ...................................................................................................................................77

24.23 Register 22 (16h) – Extended Control & Status Register .........................................................................................78

24.24 Register 23 (17h) – Extended PHY Control Register #1 ...........................................................................................79

24.25 Register 24 (18h) – Extended PHY Control Register #2 ...........................................................................................81

24.26 Register 25 (19h) – Interrupt Mask Register .............................................................................................................83

24.27 Register 26 (1Ah) – Interrupt Status Register ...........................................................................................................84

24.28 Register 27 (1Bh) – LED Control Register ................................................................................................................86

24.29 Register 28 (1Ch) – Auxiliary Control & Status Register ..........................................................................................87

24.30 Register 29 (1Dh) – Reserved ..................................................................................................................................89

24.31 Register 30 (1Eh) - Reserved ...................................................................................................................................89

24.32 Register 31 (1Fh) – Extended Page Access .............................................................................................................89

24.33 Register 16E (10h) - Reserved .................................................................................................................................90

24.34 Register 17E (11h) - CLK125micro Clock Enable .....................................................................................................90

24.35 Register 18E (12h) - Reserved .................................................................................................................................90

24.36 Register 19E (13h) - Reserved .................................................................................................................................90

24.37 Register 20E (14h) - Extended PHY Control Register #3 .........................................................................................91

24.38 Register 21E (15h) - EEPROM Interface Status and Control Register .....................................................................92

24.39 Register 22E (16h) - EEPROM Data Read/Write Register .......................................................................................93

24.40 Register 23E (17h) - Extended PHY Control Register #4 .........................................................................................93

24.41 Register 24E (18h) – Reserved ................................................................................................................................94

6 of 7

VMDS-10108 Revision 4.2

February 2019

7

�VSC8244

Data Sheet

24.42 Register 25E (19h) – Reserved ................................................................................................................................94

24.43 Register 26E (1Ah) – Reserved ................................................................................................................................94

24.44 Register 27E (1Bh) – Reserved ................................................................................................................................94

24.45 Register 28E (1Ch) – Reserved................................................................................................................................ 94

24.46 Register 29E (1Dh) - 1000BASE-T Ethernet Packet Generator (EPG) Register #1................................................. 95

25 Electrical Specifications ................................................................................................................................ 96

25.1

Absolute Maximum Ratings ......................................................................................................................................96

25.2

Recommended Operating Conditions .......................................................................................................................97

25.3

Thermal Application Data ..........................................................................................................................................98

25.4

Package Thermal Specifications - 260 HS-PBGA ...................................................................................................98

25.5

Current and Power Consumption Estimates .............................................................................................................99

25.6

DC Specifications ...................................................................................................................................................100

25.7

Clocking Specifications ...........................................................................................................................................102

25.8

System Timing Specifications .................................................................................................................................103

26 Packaging Specifications .............................................................................................................................115

26.1

19mm HS-PBGA Mechanical Specification ............................................................................................................ 115

26.2

Package Moisture Sensitivity .................................................................................................................................. 115

27 Ordering Information.....................................................................................................................................116

27.1

Devices ................................................................................................................................................................... 116

27.2

Related Devices ...................................................................................................................................................... 116

28 Design Guidelines .........................................................................................................................................117

28.1

Required SMI Register Write Sequence ................................................................................................................. 117

28.2

Interoperability with Intel 82547E1 L322SQ96 ....................................................................................................... 117

29 Product Support ............................................................................................................................................119

29.1

Available Documents and Application Notes .......................................................................................................... 119

30 Document History & Notices ....................................................................................................................... 120

7 of 7

VMDS-10108 Revision 4.2

February 2019

7

�VSC8244

Data Sheet

Figures

Figure 1.

VSC8244 System Diagram ..................................................................................................................................1

Figure 2.

VSC8244 Block Diagram .....................................................................................................................................3

Figure 3.

260 HS-PBGA Package Ball Diagram ...............................................................................................................15

Figure 4.

260-Pin HS-PBGA (19mm) Signal Map (TOP LEFT side of package) ..............................................................16

Figure 5.

260-Pin HS-PBGA (19mm) Signal Map (TOP RIGHT side of package) ............................................................17

Figure 6.

General System Schematic (shown with RGMII and 3.3V I/O) .........................................................................28

Figure 7.

Crystal Clock Option ..........................................................................................................................................29

Figure 8.

25 MHz Reference Clock Option .......................................................................................................................29

Figure 9.

125 MHz Reference Clock Option .....................................................................................................................30

Figure 10.

Analog Bias Pins Ground Connection Diagram .................................................................................................30

Figure 11.

RGMII MAC Interface ........................................................................................................................................31

Figure 12.

RTBI MAC Interface ...........................................................................................................................................32

Figure 13.

Twisted Pair Interface ........................................................................................................................................33

Figure 14.

MDIO Read Frame ............................................................................................................................................36

Figure 15.

MDIO Write Frame .............................................................................................................................................36

Figure 16.

Logical Representation of Open-Drain (Active-Low) MDINT_n Pin ...................................................................37

Figure 17.

Logical Representation of Open-Source (Active-High) MDINT_n Pin ...............................................................37

Figure 18.

Test Access Port and Boundary Scan Architecture ...........................................................................................42

Figure 19.

ActiPHY State Diagram .....................................................................................................................................46

Figure 20.

In-line Powered Ethernet Switch Diagram .........................................................................................................48

Figure 21.

Far-end Loopback Block Diagram .....................................................................................................................50

Figure 22.

Near-end Loopback Block Diagram ...................................................................................................................50

Figure 23.

Connector Loopback .........................................................................................................................................51

Figure 24.

VSC8244 Devices Connected to use the same Startup EEPROM ..................................................................57

Figure 25.

EEPROM Read and Write Register Flow ..........................................................................................................60

Figure 26.

Extended Page Register ....................................................................................................................................62

Figure 27.

RGMII Uncompensated AC Timing and Multiplexing .......................................................................................104

Figure 28.

RGMII Compensated AC Timing and Multiplexing ...........................................................................................105

Figure 29.

RTBI Uncompensated AC Timing and Multiplexing .........................................................................................107

Figure 30.

RTBI Compensated AC Timing and Multiplexing .............................................................................................108

Figure 31.

JTAG Interface AC Timing ...............................................................................................................................109

Figure 32.

SMI AC Timing ................................................................................................................................................. 110

Figure 33.

LED_CLK and LED_DATA Output AC Timing .................................................................................................. 111

Figure 34.

REFCLK AC Timing ......................................................................................................................................... 112

8 of 9

VMDS-10108 Revision 4.2

February 2019

9

�VSC8244

Data Sheet

Figure 35.

CLK125 AC Timing .......................................................................................................................................... 113

Figure 36.

RESET AC Timing ........................................................................................................................................... 114

Figure 37.

19mm HS-PBGA Mechanical Specification ..................................................................................................... 115

9 of 9

VMDS-10108 Revision 4.2

February 2019

9

�VSC8244

Data Sheet

Tables

Table 1.

VSC8244 Relevant Specifications ..................................................................................................................... 12

Table 2.

VSC8224/VSC8234/VSC8244 MAC / Media Interface Support Options........................................................... 13

Table 3.

Data Sheet Conventions.................................................................................................................................... 14

Table 4.

Signal Type Descriptions ................................................................................................................................... 18

Table 5.

MAC TX Signal Descriptions ............................................................................................................................. 19

Table 6.

MAC RX Signal Descriptions ............................................................................................................................. 20

Table 7.

Twisted Pair Interface Pins ................................................................................................................................ 21

Table 8.

Serial Management Interface Pins .................................................................................................................... 22

Table 9.

Serial EEPROM Interface Pins .......................................................................................................................... 23

Table 10.

Configuration and Control Pins.......................................................................................................................... 23

Table 11.

System Clock Interface Pins.............................................................................................................................. 24

Table 12.

LED Interface Pins............................................................................................................................................. 24

Table 13.

JTAG TAP Signal Descriptions .......................................................................................................................... 25

Table 14.

Analog Bias Pins ............................................................................................................................................... 25

Table 15.

HSTL Voltage Reference Pins ........................................................................................................................... 25

Table 16.

No Connect Pins................................................................................................................................................ 26

Table 17.

Power Supply Pins ............................................................................................................................................ 26

Table 18.

Power Supply and Associated Functional Pins ................................................................................................. 27

Table 19.

Accepted MDI Pair Connection Combinations................................................................................................... 34

Table 20.

SMI Frame Format ............................................................................................................................................ 35

Table 21.

LED Function Assignments ............................................................................................................................... 38

Table 22.

LED Functions ................................................................................................................................................... 38

Table 23.

LED Output Options .......................................................................................................................................... 40

Table 24.

Serial LED Output Data ..................................................................................................................................... 41

Table 25.

JTAG Device Identification Register Description ............................................................................................... 43

Table 26.

JTAG Interface Instruction Codes...................................................................................................................... 43

Table 27.

CMODE Hardware Configuration Bits ............................................................................................................... 53

Table 28.

CMODE Pin Combinations ................................................................................................................................ 53

Table 29.

CMODE Configuration Bits ................................................................................................................................ 54

Table 30.

EEPROM Configuration Contents ..................................................................................................................... 55

Table 31.

EEPROM Configuration Contents for Multiple VSC8244 Devices..................................................................... 57

Table 32.

MII Register Bit Modes ...................................................................................................................................... 61

Table 33.

MII Register Quick Reference ........................................................................................................................... 63

Table 34.

MII Register Quick Reference - Extended Page Mode...................................................................................... 65

10 of 11

VMDS-10108 Revision 4.2

February 2019

11

�VSC8244

Data Sheet

Table 35.

Transmitter/Receiver Test Mode ........................................................................................................................ 70

Table 36.

Test Mode 4 ....................................................................................................................................................... 71

Table 37.

Transmitter Test Clock Enable ........................................................................................................................... 76

Table 38.

MAC/Media Interface Mode Select .................................................................................................................... 80

Table 39.

Thermal Air Flow Specifications - 260 ball HSBGA 19mm package.................................................................. 98

Table 40.

Thermal Specifications - 260 ball HSBGA 19mm package................................................................................ 98

Table 41.

Current and Power Consumption Estimates - HSTL @ 1.5V, RGMII mode, no LEDs, no CLK125 .................. 99

Table 42.

Current and Power Consumption Estimates - 2.5V, RGMII mode, no LEDs, no CLK125 ................................. 99

Table 43.

Current and Power Consumption Estimates - 3.3V, RGMII mode, no LEDs, no CLK125 ................................. 99

Table 44.

Digital Pins Specifications (VDDIO = 3.3V) ..................................................................................................... 100

Table 45.

Digital Pins Specifications (VDDIO = 2.5V) ..................................................................................................... 100

Table 46.

Digital Pins Specifications (VDDIO = 1.5V) ..................................................................................................... 101

Table 47.

LED Output Pins Specifications....................................................................................................................... 102

Table 48.

Reference Clock Option Specifications ........................................................................................................... 102

Table 49.

Crystal Option Specifications........................................................................................................................... 103

Table 50.

RGMII Mode AC Timing Specifications............................................................................................................ 103

Table 51.

RTBI Mode AC Timing Specifications .............................................................................................................. 106

Table 52.

JTAG Interface AC Timing Specifications ........................................................................................................ 109

Table 53.

SMI AC Timing Specifications.......................................................................................................................... 110

Table 54.

MDINT AC Timing Specifications..................................................................................................................... 111

Table 55.

LED_CLK and LED_DATA Output AC Timing Specification ............................................................................ 111

Table 56.

REFCLK AC Timing Specifications .................................................................................................................. 112

Table 57.

CLK125 AC Timing Specifications ................................................................................................................... 113

Table 58.

RESET AC Timing Specification ...................................................................................................................... 114

Table 59.

Startup Write Sequence Changes ................................................................................................................... 117

Table 60.

Startup Write Sequence Changes for Intel 82547E1 Interoperability .............................................................. 118

Table 61.

Document Revision History ............................................................................................................................. 120

11 of 11

VMDS-10108 Revision 4.2

February 2019

11

�VSC8244

Data Sheet

6 Relevant Specifications & Documentation

The VSC8244 conforms to the following specifications. Please refer to these documents for additional information.

Table 1. VSC8244 Relevant Specifications

Specification - Revision

Description

IEEE 802.3-2002

Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and

Physical Layer Specifications. IEEE 802.3-2002 consolidates and supersedes the following

specifications:

802.3ab (1000BASE-T), 802.3u (Fast Ethernet), with references to

ANSI X3T12 TP-PMD standard (ANSI X3.263 TP-PMD).

IEEE 1149.1-1990

Test Access Port and Boundary Scan Architecture1.

Includes IEEE Standard 1149.1a-1993 and IEEE Standard 1149.1b-1994.

JEDEC EIA/JESD8-5

2.5V±0.2V (Normal Range), and 1.8V to 2.7V (Wide Range) Power Supply Voltage and

Interface Standard for Nonterminated Digital Integrated Circuits.

JEDEC JESD22-A114-B

Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM).

Revision of JESD22-A114-A.

JEDEC JESD22-A115-A

Electrostatic Discharge (ESD) Sensitivity Testing Machine Model (MM).

Revision of EIA/JESD22-A115.

JEDEC EIA/JESD78

MIL-STD-883E

IC Latch-Up Test Standard.

Miltary Test Method Standard for Microcircuits.

Reduced Pin-Count Interface for Gigabit Ethernet Physical Layer Devices (per Hewlett

RGMII Specification - v1.3, v2.0 Packard).

Includes both RGMII and RTBI standards.

PICMG 2.16

IP Backplane specification for CompactPCI v2.16.

Advanced TCA™ Base

PICMG 3.0

IP Backplane specification for CompactPCI v3.0.

Cisco InLIne Power Detection

Algorithmn

1

Cisco Sytems InLine Power Detection:

http://www.cisco.com/en/US/products/hw/phones/ps379/products_tech_note09186a00801189b5.shtml

Often referred to as the “JTAG” test standard.

12 of 14

VMDS-10108 Revision 4.2

February 2019

14

�VSC8244

Data Sheet

7 VSC8244 Differences vs. VSC8224/VSC8234 Devices

The VSC8244 is one of three, quad port PHY devices featuring Microsemi’s proprietary fourth-generation DSP technology. It

provides parallel RGMII/RTBI interfaces and 10/100/1000BASE-T Category-5, Unshielded Twisted Pair (UTP) copper media

interfaces. The VSC8234 features serial SGMII/SerDes MAC interfaces with Category-5 UTP media interfaces. The VSC8224

is the dual media capable device featuring RGMII/RTBI parallel MAC interfaces with support for both 10/100/1000BASE-T and

1000BASE-X media interfaces.

The following table summarizes the MAC and media interfaces supported by the VSC8244, the VSC8234, and the VSC8244

quad-port PHY:

Table 2. VSC8224/VSC8234/VSC8244 MAC / Media Interface Support Options

Device #

VSC8224

VSC8234

VSC8244

MAC Interface

Media Interface

RGMII / RTBI

CAT-5

RGMII / RTBI

SerDes (1000Base-X)

SGMII (4 or 6 pin)

CAT-5

SerDes (1000Base-X)

CAT-5

RGMII / RTBI

CAT-5

Package Options

Full Part Number

260-pin HS-PBGA

VSC8224HG

260-pin HS-PBGA

VSC8234HG

260-pin HS-PBGA

VSC8244HG

7.1 VSC8244 Functional Differences

The VSC8244 is a functional subset of the VSC8224 in that it provides all the same features except for the following:

•

No media side SerDes interfaces for supporting 1000BASE-X (fiber).

•

Differences in the CMODE configurations settings as certain functions in the VSC8224 relating to

the serial interface are not present in the VSC8244. This includes several MAC interfaces,

SIGDET direction setting, and SerDes termination impedance setting

7.2 VSC8244 Register Differences

The VSC8244 is the exact register map equivalent to the VSC8224’s register map with the following exceptions:

•

Register 3: Device number indication changes to VSC8244.

•

Register 23:

– Bit 15 is Reserved and must be set to 0.

– Bits 14:12 less modes are present. Only modes involving RGMII-CAT5 and RTBI-CAT5

exist in the VSC8244.

•

Register 24: TXFIFO settings only affect RGMII as opposed to SerDes and SGMII as in the

VSC8224.

•

Register 25 & 26: Bit 4 for the Auto-Media Sense (AMS) indication condition is not available.

•

Register 16E: Only bits 2:0 (Remote Fault bit settings) are relevant on the VSC8244.

•

Register 20E: Bits 7:5 related to AMS and SerDes termination impedance for the VSC8224 are not

present in the VSC8224.

13 of 14

VMDS-10108 Revision 4.2

February 2019

14

�VSC8244

Data Sheet

7.3 VSC8244 Pinout Differences

The 260-pin HS-PBGA packages between the VSC8224HG and the VSC8244HG are the exact same (pin-for-pin compatible),

except for the following pins:

The following pins are NC on the VSC8244HG 260-pin HS-PBGA:

•

Pins T1, M1, H1, D1, U1, N1, J1, E1 -- TDP/N_[3:0] signals

•

Pins R1, L1, G1, C1, P1, K1, F1, B1 -- RDP/N_[3:0] signals

•

Pins R2, L2, G2, C2, T2, M2, H2, D2 -- RCP/N_[3:0] signals

•

Pins E2, J2, N2, U2 -- SIGDET_[3:0] signals

8 Data Sheet Conventions

Conventions used throughout this data sheet are specified in the following table.

Table 3. Data Sheet Conventions

Convention

Syntax

Examples

Description

Register

number

RegisterNumber.Bit

or

RegisterNumber.BitRange

23.10

23.12:10

Extended

Page Register number

RegisterNumberE.Bit

or

RegisterNumberE.BitRange

23E.10

23E.12:10

Extended Register 23 (address 17h), bit 10.

Extended Register 23 (address 17h), bits 12, 11, and 10.

Signal name

(active high)

SIGNALNAME1

PLLMODE

Signal name for PLLMODE.

Signal name

(active low)

SIGNALNAME1

RESET

Signal bus

name

BUSNAME[MSB:LSB]1

CMODE[4:0]2

PHY port

number

_n

_3

PHY-specific

port signal

SIGNALNAME_n1

RX_CTL_3

RX_CTL signal for PHY port 33.

Signal bus for

a specific PHY

port

SIGNALNAME[MSB:LSB]_n1

RXD[3:0]_3

Receive data bus, bits 3through 0, for PHY port #33.

Register 23 (address 17h), bit 10.

Register 23 (address 17h), bits 12, 11, and 10.

Active low reset signal.

CMODE configuration bits 4, 3, 2, 1, and 0.

Denotes a specific PHY port #3. n= {3 || 2 || 1 ||0}.

1

All signal names are in all CAPITAL LETTERS.

CMODE is common to entire device.

3 RXD signals are unique to each PHY.

2

14 of 14

VMDS-10108 Revision 4.2

February 2019

14

�VSC8244

Data Sheet

9 Package Pin Assignments & Signal Descriptions

9.1 260 HS-PBGA Package Ball Diagram

18

17

16

15

14

13

12

11

B

C

10

9

8

7

6

5

4

3

2

A

1

For complete specifications, refer to Section 26: “Packaging Specifications”.

B

C

D

E

D

E

F

G

F

G

H

J

H

J

VSC8244

18

17

16

15

U

V

14

U

V

13

T

12

R

T

11

R

10

P

9

P

8

N

7

N

6

M

5

M

4

L

3

L

2

K

1

K

260 HS-PBGA

1.0mm Ball Pitch (19mm body size)

(Top View)

Figure 3. 260 HS-PBGA Package Ball Diagram

(View from top of package with underlying BGA ball positions superimposed)

15 of 27

VMDS-10108 Revision 4.2

February 2019

A

27

�VSC8244

Data Sheet

9.2 BGA Ball to Signal Name Cross Reference (LEFT side)

1

2

3

4

5

6

7

8

9

A

LED[4]_3

LED[0]_2

TXVPD_3

TXVPC_3

TXVPB_3

TXVPA_3

TXVPD_2

TXVPC_2

TXVPB_2

B

NC

LED[1]_2

TXVND_3

TXVNC_3

TXVNB_3

TXVNA_3

TXVND_2

TXVNC_2

TXVNB_2

C

NC

NC

LED[2]_2

LED[3]_2

LED[4]_2

NC

NC

VDD33

REF_REXT

D

NC

NC

LED[3]_3

VDD33

VDD33

VDD33

VSSS

VSSS

VDD33

E

NC

NC

LED[2]_3

VDD12

F

NC

VSSS

LED[1]_3

VDD12

G

NC

NC

LED[0]_3

VSSS

VSSS

VSSS

VSSS

H

NC

NC

VDD12

VDDDIG

VSSS

VSSS

VSSS

J

NC

NC

VDD12

VDDDIG

VSSS

VSSS

VSSS

K

NC

VSSS

VSSS

VSSS

VSSS

VSSS

VSSS

L

NC

NC

VSSS

VDD33

VSSS

VSSS

VSSS

M

NC

NC

VDD12

VSSS

VSSIO

VSSIO

VSSIO

N

NC

NC

VDD12

VSSS

P

NC

VSSS

VSSS

VDDDIG

R

NC

NC

VDD12

VDDDIG

VDDIOMAC

VDDIOMAC

VDDIOMAC

TXREF_2

VDDIOMAC

T

NC

NC

TXREF_3

RXD[2]_3

TX_CLK_3

TXD[2]_3

RX_CLK_2

RXD[2]_2

TX_CLK_2

U

NC

NC

RX_CTL_3

RXD[1]_3

TX_CTL_3

TXD[1]_3

RX_CTL_2

RXD[1]_2

TX_CTL_2

V

NC

RX_CLK_3

RXD[3]_3

RXD[0]_3

TXD[3]_3

TXD[0]_3

RXD[3]_2

RXD[0]_2

TXD[3]_2

1

2

3

4

5

6

7

8

9

Figure 4. 260-Pin HS-PBGA (19mm) Signal Map (TOP LEFT side of package)

16 of 27

VMDS-10108 Revision 4.2

February 2019

27

�VSC8244

Data Sheet

9.3 BGA Ball to Signal Name Cross Reference (RIGHT side)

10

11

12

13

14

15

16

17

18

TXVPA_2

TXVPD_1

TXVPC_1

TXVPB_1

TXVPA_1

TXVPD_0

TXVPC_0

TXVPB_0

TXVPA_0

A

TXVNA_2

TXVND_1

TXVNC_1

TXVNB_1

TXVNA_1

TXVND_0

TXVNC_0

TXVNB_0

TXVNA_0

B

REF_FILT

VSSS

VSSS

VSSS

VSSS

NC

CMODE[7]

CMODE[6]

CMODE[5]

C

VDD33

VDD33

VDD33

VDD33

VDD12

VDD12

CMODE[4]

XTAL1 or

REFCLK

XTAL2

D

NC

CMODE[3]

CMODE[2]

CMODE[1]

E

VDD33

CMODE[0]

LED[0]_1

LED[1]_1

F

VSSS

VSSS

VSSS

VDD33

LED[2]_1

LED[3]_1

LED[4]_1

G

VSSS

VSSS

VSSS

VDDDIG

LED[0]_0

LED[1]_0

LED[2]_0

H

VSSS

VSSS

VSSS

VDDDIG

TDI

LED[3]_0

LED[4]_0

J

VSSS

VSSS

VSSS

VDDIOctl

TDO

TCK

TMS

K

VSSS

VSSS

VSSS

VDDIOmicro

TRST

EECLK or

PLLMODE

EEDAT

L

VSSIO

VSSIO

VSSIO

VSSIO

RESET

SOFT_

RESET

OSCEN or

CLK125micro

M

VSSS

MDINT_1

MDINT_2

MDINT_3

N

VSSS

MDC

MDIO

MDINT_0

P

TXREF_1

VDDIOMAC

VDDIOMAC

TXREF_0

VDDDIG

VDDDIG

VDD33

CLK125MAC MICROREF

TXD[2]_2

RX_CLK_1

RXD[0]_1

TXD[3]_1

TXD[0]_1

RXD[3]_0

RXD[0]_0

TXD[3]_0

TXD[0]_0

T

TXD[1]_2

RX_CTL_1

RXD[1]_1

TX_CLK_1

TXD[1]_1

RX_CTL_0

RXD[1]_0

TX_CTL_0

TXD[1]_0

U

TXD[0]_2

RXD[3]_1

RXD[2]_1

TX_CTL_1

TXD[2]_1

RX_CLK_0

RXD[2]_0

TX_CLK_0

TXD[2]_0

V

10

11

12

13

14

15

16

17

18

Figure 5. 260-Pin HS-PBGA (19mm) Signal Map (TOP RIGHT side of package)

17 of 27

VMDS-10108 Revision 4.2

February 2019

27

R

�VSC8244

Data Sheet

9.4 Signal Type Descriptions

Table 4. Signal Type Descriptions

Symbol

Signal Type

I

Digital Input

IPU

Digital Input with Pull-up

IPD

Digital Input with Pull-down

OZC

Description

Standard digital input signal. No internal pull-up or pull-down.

Standard digital input. Includes on-chip 100kΩ pull-up to VDDIO.

Standard digital input. Includes on-chip 100kΩ pull-down to VSSIO.

50Ω integrated (on-chip) source series terminated, digital output signal. Used priImpedance Controlled Output marily for timing-sensitive MAC I/F and 125MHz clock output pins, in addition to

high speed manufacturing test mode pins.

Tristate-able, digital input and output signal. Includes on-chip 100kΩ pull-down to

VSSIO.

IPD/O

Digital Bidirectional

OD

Digital Open Drain Output

ADIFF

Analog Differential

ABIAS

Analog Bias

Analog bias or reference signal. Must be tied to external resistor and/or capacitor

bias network, as shown in Section 10: “System Schematics”.

IA

Analog Input

Analog input for sensing variable voltage levels.

OS

Open Source

Open source digital output signal. Must be pulled to GND through an external pulldown resistor.

VREF

Voltage Reference Input

IPUJTAG

JTAG Input

OCRYST

Crystal Output

NC

No Connect

Open drain digital output signal. Must be pulled to VDDIO through an external pullup resistor.

Analog differential signal pair for twisted pair interface.

Voltage Reference input pins required for VDDIO HSTL mode.

JTAG input pin. Includes on-chip pullup to VDDIOCTL. These pins are 5V tolerant

when VDDIOCTL = 3.3V. For VDDIOCTL = 2.5V, these pins are up to 4.7V tolerant.

Crystal clock output pin. If not used, leave unconnected.

No connect signal. Must be left floating.

18 of 27

VMDS-10108 Revision 4.2

February 2019

27

�VSC8244

Data Sheet

9.5 MAC Transmit Interface (MAC TX) Pins

The following pins are used for connecting to a parallel data bus MAC via the industry-standard RGMII and RTBI interfaces.

Table 5. MAC TX Signal Descriptions

HSBGA

Ball #

V5, T6, U6, V6

V9, T10, U10, V10

T13, V14, U14, T14

T17, V18, U18, T18

U5

U9

V13

U17

Signal Name

MAC Interface Modes Type

RGMII

TXD[3:0]_3

TXD[3:0]_2

TXD[3:0]_1

TXD[3:0]_0

TX_CTL_3

TX_CTL_2

TX_CTL_1

TX_CTL_0

Description

RTBI

TXD[3:0]_3

TXD[3:0]_2

TXD[3:0]_1

TXD[3:0]_0

TXD[4]_3

TXD[4]_2

TXD[4]_1

TXD[4]_0

Multiplexed Transmit Data Nibbles (RGMII mode)

Bits [3:0] are synchronously input on the rising edge of TX_CLK_n, and

bits [7:4] on the falling edge of TX_CLK_n.

IPD

Multiplexed Transmit Data Nibbles (RTBI mode)

Bits [3:0] are synchronously input on the rising edge of TX_CLK_n, and

bits [8:5] on the falling edge of TX_CLK_n.

Transmit Enable, Transmit Error Multiplexed Input (RGMII mode)

In RGMII mode, this input is sampled by the PHY on opposite edges of

TX_CLK_n to indicate two transmit conditions of the MAC:

1) on the rising edge of TX_CLK_n, this input serves as TXEN, indicating

valid data is available on the TD input data bus.

2) on the falling edge of TX_CLK_n, this input signals a transmit error

IPD

from the MAC, based on a logical derivative of TXEN and TXER, per

RGMII specification Version 2.0.

Multiplexed Transmit Data (RTBI mode)

Bit [4] is synchronously input on the rising edge of TX_CLK_n, and bit [9]

on the falling edge of TX_CLK_n.

T5

T9

U13

V17

TX_CLK_3

TX_CLK_2

TX_CLK_1

TX_CLK_0

TX_CLK_3

TX_CLK_2

TX_CLK_1

TX_CLK_0

Transmit Clock Input (RGMII mode)

The transmit clock shall be either a 125MHz or 25MHz (for 1000Mb or

IPD

100Mb modes, respectively), with a +/-50ppm tolerance. If left unconnected, these pins will require a pull-down resistor to ground.

19 of 27

VMDS-10108 Revision 4.2

February 2019

27

�VSC8244

Data Sheet

9.6 MAC Receive Interface (MAC RX) Pins

All output pins for the MAC interface include impedance-calibrated, tristateable output drive capability.

Table 6. MAC RX Signal Descriptions

HSBGA

Ball #

Signal Name

MAC Interface Modes

RGMII

Type

Description

RTBI

Multiplexed Receive Data Nibble (RGMII mode only)

Bits [3:0] are synchronously output on the rising edge of RX_CLK_n, and

bits [7:4] on the falling edge of RX_CLK_n.

V3, T4, U4, V4

V7, T8, U8, V8

V11, V12, U12, T12

T15, V16, U16, T16

RXD[3:0]_3

RXD[3:0]_2

RXD[3:0]_1

RXD[3:0]_0

RXD[3:0]_3

RXD[3:0]_2

RXD[3:0]_1

RXD[3:0]_0

OZC

V2

T7

T11

V15

RX_CLK_3

RX_CLK_2

RX_CLK_1

RX_CLK_0

RX_CLK_3

RX_CLK_2

RX_CLK_1

RX_CLK_0

Receive Clock Output (RGMII and RTBI modes)

OZC Receive data is sourced from the PHY synchronously on the rising edge

of RX_CLK_n and is the recovered clock from the media.

U3

U7

U11

U15

RX_CTL_3

RX_CTL_2

RX_CTL_1

RX_CTL_0

RXD[4]_3

RXD[4]_2

RXD[4]_1

RXD[4]_0

Multiplexed Receive Data Nibbles (RTBI mode)

Bits [3:0] are synchronously output on the rising edge of RX_CLK_n, and

bits [8:5] on the falling edge of RX_CLK_n.

Multiplexed Receive Data Valid / Receive Error Output (RGMII mode

only). In RGMII mode, this output is sampled by the MAC on opposite

edges of RX_CLK_n to indicate two receive conditions from the PHY:

1) on the rising edge of RX_CLK_n, this output serves as RXDV, signaling valid data is available on the RD input data bus,

2) on the falling edge of RX_CLK_n, this output signals a receive error

OZC

from the PHY, based on a logical derivative of RXDV and RXER, per

RGMII specification Version 2.0.

Multiplexed Receive Data (RTBI mode)

Bit [4] is synchronously output on the rising edge of RX_CLK_n, and bit

[9] on the falling edge of RX_CLK_n.

20 of 27

VMDS-10108 Revision 4.2

February 2019

27

�VSC8244

Data Sheet

9.7 Twisted Pair Interface Pins

Table 7. Twisted Pair Interface Pins

HSBGA

Ball #

Signal

Name

A6

A10

A14

A18

TXVPA_3

TXVPA_2

TXVPA_1

TXVPA_0

B6

B10

B14

B18

Type

Description

ADIFF

TX/RX Channel "A" Positive Signal

Positive differential signal connected to the positive primary side of the transformer. This pin

signal forms the positive signal of the "A" data channel. In all three speeds, these pins generate the secondary side signal, normally connected to RJ-45 pin 1. See System Schematic.

TXVNA_3

TXVNA_2

TXVNA_1

TXVNA_0

ADIFF

TX/RX Channel "A" Negative Signal

Negative differential signal connected to the negative primary side of the transformer. This

pin signal forms the negative signal of the "A" data channel. In all three speeds, these pins

generate the secondary side signal, normally connected to RJ-45 pin 2. See System Schematic.

A5

A9

A13

A17

TXVPB_3

TXVPB_2

TXVPB_1

TXVPB_0

ADIFF

TX/RX Channel "B" Positive Signal

Positive differential signal connected to the positive primary side of the transformer. This pin

signal forms the positive signal of the "B" data channel. In all three speeds, these pins generate the secondary side signal, normally connected to RJ-45 pin 3. See System Schematic.

B5

B9

B13

B17

TXVNB_3

TXVNB_2

TXVNB_1

TXVNB_0

ADIFF

TX/RX Channel "B" Negative Signal

Negative differential signal connected to the negative primary side of the transformer. This

pin signal forms the negative signal of the "B" data channel. In all three speeds, these pins

generate the secondary side signal, normally connected to RJ-45 pin 6. See System Schematic.

A4

A8

A12

A16

TXVPC_3

TXVPC_2

TXVPC_1

TXVPC_0

ADIFF

TX/RX Channel "C" Positive Signal

Positive differential signal connected to the positive primary side of the transformer. This pin

signals forms the positive signal of the "C" data. In 1000Mb mode, these pins generate the

secondary side signal, normally connected to RJ-45 pin 4 (pins not used in 10M/100M

modes). See System Schematic.

B4

B8

B12

B16

TXVNC_3

TXVNC_2

TXVNC_1

TXVNC_0

ADIFF

TX/RX Channel "C" Negative Signal

Negative differential signal connected to the negative primary side of the transformer. This

pin signal forms the negative signal of the "C" data channel. In 1000Mb mode, these pins

generate the secondary side signal, normally connected to RJ-45 pin 5 (pins not used in

10M/100M modes). See System Schematic.

A3

A7

A11

A15

TXVPD_3

TXVPD_2

TXVPD_1

TXVPD_0

ADIFF

TX/RX Channel "D" Positive Signal

Positive differential signal connected to the positive primary side of the transformer. This pin

signal forms the positive signal of the "D" data channel. In 1000Mb mode, these pins generate the secondary side signal, normally connected to RJ-45 pin 7 (pins not used in 10M/100M

modes). See System Schematic.

B3

B7

B11

B15

TXVND_3

TXVND_2

TXVND_1

TXVND_0

ADIFF

TX/RX Channel "D" Negative Signal

Negative differential signal connected to the negative primary side of the transformer. This

pin signal forms the positive signal of the "D" data channel. In 1000Mb mode, these pins generate the secondary side signal, normally connected to RJ-45 pin 8 (pins not used in 10M/

100M modes). See System Schematic.

21 of 27

VMDS-10108 Revision 4.2

February 2019

27

�VSC8244

Data Sheet

9.8 Serial Management Interface Pins (IEEE SMI)

Table 8. Serial Management Interface Pins

HSBGA

Ball

P16

P17

Signal Name

MDC

MDIO

Type

Description

I

Management Data Clock

A 0 to 12.5MHz reference input is used to clock serial MDIO data into and out of the

VSC8244. The expected nominal frequency is 2.5MHz, as specified by the IEEE standard. This clock is typically asynchronous with respect to the PHY’s transmit or

receive clock.

OD

Management Data I/O

MDIO configuration and status data is exchanged on this pin bidirectionally between

the PHY and the Station Manager, synchronously to the rising edge of MDC. This signal normally requires a 1.5kΩ to 2kΩ external pull-up resistor at the Station Manager.

The value of the pull-up resistor depends on the MDC clock frequency and the maximum capacitive load on the MDIO pin.

Management Interrupt Outputs

These output signals indicate a change in each of the four PHY’s link operating conditions for which a station manager must interrogate to determine further information.

P18

N16

N17

N18

MDINT_0

MDINT_1

MDINT_2

MDINT_3

OS/

OD

Upon reset or powerup, the VSC8244 will automatically configure these pins as

active-low (open drain) or active-high (open source) based on the polarity of an external resistor connection. For active-low configuration, tie each MDINT_n pin to VDD33

through an external 10kΩ pull-up resistor. For active-high configuration, tie each

MDINT_n pin to GND through an external 10kΩ pull-down resistor.

If only one MDINT_n signal is desired for all four PHYs, these pins can be tied

together on the PCB in a wired-OR configuration with only a single pull-up or pulldown resistor.

22 of 27

VMDS-10108 Revision 4.2

February 2019

27

�VSC8244

Data Sheet

9.9 Serial EEPROM Interface Pins

Table 9. Serial EEPROM Interface Pins

HSBGA

Ball

Signal

Name

L18

EEDAT

Type

Description

EEPROM Serial Data I/O

The optional EEPROM interface can be used to allow VSC8244 operating mode and configuration data to be read from an external EEPROM. (The EEPROM can also be written if

desired.) EEPROM data is synchronously exchanged, bi-directionally, between the VSC8244

and the external EEPROM. Data is clocked from the VSC8244 on the falling edge of EECLK,

and into the VSC8244 on the rising edge of EECLK as defined by the ATMEL "AT24CXXX"

IPD/O

type EEPROMs. This pin should be connected to the SDA pin of the EEPROM.

The VSC8244 determines that an external EEPROM is present by monitoring the EEDAT pin

at power-up or when RESET is de-asserted: if EEDAT has a 4.7k external pull-up resistor, the

VSC8244 assumes an EEPROM is present. The EEDAT pin can be left floating or grounded

to indicate no EEPROM.

EECLK - Serial EEPROM Clock Output

This output is the clock line of the two-wire, serial EEPROM interface. The VSC8244 drives

this line at a 50 kHz rate on reset. When accessed through the MII registers, this line is driven

at a 100kHz rate. This pin should be connected to the SCL pin of the EEPROM.

L17

EECLK or

PLLMODE

IPD/

OZC PLLMODE - PLLMODE - PLL Mode Select Input

PLLMODE is sampled during the device power-up sequence or in reset. When PLLMODE is

high, the VSC8244 expects a 125MHz clock input as the PHY's reference clock. When pulled

low (default), a reference clock of 25MHz is expected from either an external crystal or a clock

reference input. This pin is internally pulled down with a 100k resistor.

9.10 Configuration and Control Pins

Table 10. Configuration and Control Pins

HSBGA

Ball

Signal Name

F16

E18

E17

E16

D16

C18

C17

C16

CMODE0

CMODE1

CMODE2

CMODE3

CMODE4

CMODE5

CMODE6

CMODE7

M16

RESET

Type

IA

IPU

Description

Hardware Chip Mode Select

The CMODE inputs are used for hardware configuration of the various operating modes of

the VSC8244. Each pin has multiple settings, each of which is established by an external

1% resistor tied to GND or VDD33. See Section 22.3: “CMODE Pin Configuration” for details

on configuring the VSC8244 with the CMODE pins.

Hardware Chip Reset

RESET is an active low input, which powers down all of the internal reference voltages and

the PLL, and resets all internal logic, including the DSPs, PLLs and the MII Management

Register bits are set to their default states.

Hardware reset is distinct from Software reset which only resets the standard MII Registers.

M17

SOFT_RESET

IPU

Soft Reset

SOFT_RESET is an active low input, which places the VSC8244 in a low power state.

Although the device is powered down; non-volatile, serial management interface registers

retain their values.

23 of 27

VMDS-10108 Revision 4.2

February 2019

27

�VSC8244

Data Sheet

9.11 System Clock Interface Pins

Table 11. System Clock Interface Pins

HSBGA

Signal Name

Ball

R17

Type

CLK125MAC

OZC

Description

Reference Clock Output for MAC

This pin serves as a 125MHz reference clock output, which can be used to drive a MAC or

other external device. CLK125MAC is powered by the VDDIOMAC supply.

This 125MHz clock output pin is enabled by default, but can be disabled via an MII register

setting.

M18

OSCEN or

I /O

CLK125micro PD ZC

OSCEN - Oscillator Enable

OSCEN is sampled on the rising edge of RESET to determine if the on-chip oscillator is

enabled, or an external clock is to be used. When tied high through an external 10k pull-up

resistor, the oscillator is enabled, allowing operation with an external 25MHz crystal. If

OSCEN is tied low (or left floating), the oscillator circuit is disabled and the device must be

supplied with either a 25MHz or 125MHz clock input to REFCLK (see EECLK or PLLMODE

pin description for more details).

CLK125micro - Reference Clock Output for Microprocessor

This pin serves as a 125MHz or 4MHz reference clock output, which can be used to drive a

Microprocessor or other external device. CLK125micro is powered by the VDDIOmicro supply.

This 125MHz or 4MHz clock output pin is disabled by default, but can be enabled via an MII

register setting.

D17

XTAL1 or

REFCLK

XTAL1 - Crystal Oscillator Input