Ultralow Distortion, Low Power,

Low Noise, High Speed Op Amp

ADA4857-1/ADA4857-2

Data Sheet

CONNECTION DIAGRAMS

High speed

850 MHz, −3 dB bandwidth (G = +1, RL = 1 kΩ, LFCSP)

750 MHz, −3 dB bandwidth (G = +1, RL = 1 kΩ, SOIC)

2800 V/μs slew rate

Low distortion: −88 dBc at 10 MHz (G = +1, RL = 1 kΩ)

Low power: 5 mA/amplifier at 10 V

Low noise: 4.4 nV/√Hz

Wide supply voltage range: 5 V to 10 V

Power-down feature

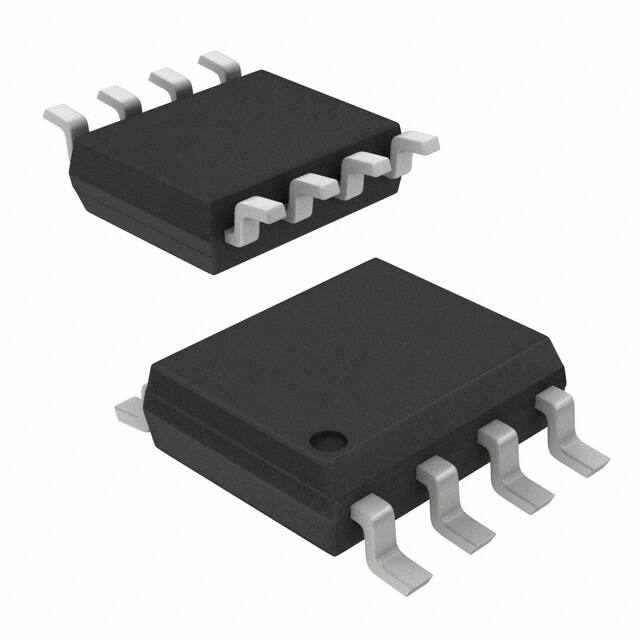

Available in 3 mm × 3 mm 8-lead LFCSP (single), 8-lead SOIC

(single), and 4 mm × 4 mm 16-lead LFCSP (dual)

ADA4857-1

TOP VIEW

(Not to Scale)

PD 1

8 +VS

FB 2

7 OUT

–IN 3

6 NC

+IN 4

5 –VS

NOTES

1. NC = NO CONNECT. DO NOT CONNECT

TO THIS PIN.

2. THE EXPOSED PAD MAY BE CONNECTED

TO GND OR VS.

07040-001

FEATURES

Figure 1. 8-Lead LFCSP (CP)

ADA4857-1

APPLICATIONS

FB 1

8

PD

–IN 2

7

+VS

+IN 3

6

OUT

–VS 4

5

NC

NC = NO CONNECT

07040-002

TOP VIEW

(Not to Scale)

Instrumentation

IF and baseband amplifiers

Active filters

ADC drivers

DAC buffers

Figure 2. 8-Lead SOIC (R)

ADA4857-2

13 OUT1

14 +VS1

16 FB1

15 PD1

TOP VIEW

(Not to Scale)

–IN1 1

12 –VS1

+IN1 2

11 NC

10 +IN2

NC 3

9

–IN2

NOTES

1. NC = NO CONNECT. DO NOT CONNECT

TO THIS PIN.

2. THE EXPOSED PAD MAY BE CONNECTED

TO GND OR VS.

07040-003

FB2 8

PD2 7

+VS2 6

OUT2 5

–VS2 4

Figure 3. 16-Lead LFCSP (CP)

GENERAL DESCRIPTION

The ADA4857 is a unity-gain stable, high speed, voltage feedback

amplifier with low distortion, low noise, and high slew rate. With a

spurious-free dynamic range (SFDR) of −88 dBc at 10 MHz, the

ADA4857 is an ideal solution for a variety of applications, including

ultrasounds, ATE, active filters, and ADC drivers. The Analog

Devices, Inc., proprietary next-generation XFCB process and

innovative architecture enables such high performance amplifiers.

The ADA4857 has 850 MHz bandwidth, 2800 V/μs slew rate, and

settles to 0.1% in 15 ns. With a wide supply voltage range (5 V to

Rev. D

10 V), the ADA4857 is an ideal candidate for systems that require

high dynamic range, precision, and speed.

The ADA4857-1 amplifier is available in a 3 mm × 3 mm, 8-lead

LFCSP and a standard 8-lead SOIC. The ADA4857-2 is available in

a 4 mm × 4 mm, 16-lead LFCSP. The LFCSP features an exposed

paddle that provides a low thermal resistance path to the printed

circuit board (PCB). This path enables more efficient heat transfer

and increases reliability. The ADA4857 works over the extended

industrial temperature range (−40°C to +125°C).

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2008–2017 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

�ADA4857-1/ADA4857-2

Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

Test Circuits ..................................................................................... 16

Applications ....................................................................................... 1

Applications Information .............................................................. 17

Connection Diagrams ...................................................................... 1

Power-Down Operation ............................................................ 17

General Description ......................................................................... 1

Capacitive Load Considerations .............................................. 17

Revision History ............................................................................... 2

Recommended Values for Various Gains................................ 17

Specifications..................................................................................... 3

Active Low-Pass Filter (LPF) .................................................... 18

±5 V Supply ................................................................................... 3

Noise ............................................................................................ 19

+5 V Supply ................................................................................... 4

Circuit Considerations .............................................................. 19

Absolute Maximum Ratings............................................................ 6

PCB Layout ................................................................................. 19

Thermal Resistance ...................................................................... 6

Power Supply Bypassing ............................................................ 19

Maximum Power Dissipation ..................................................... 6

Grounding ................................................................................... 19

ESD Caution .................................................................................. 6

Outline Dimensions ....................................................................... 20

Pin Configurations and Function Descriptions ........................... 7

Ordering Guide .......................................................................... 21

Typical Performance Characteristics ............................................. 9

REVISION HISTORY

1/2017—Rev. C to Rev. D

Changes to Figure 1 .......................................................................... 1

Changes to Table 1 ............................................................................ 3

Changes to Table 2 ............................................................................ 4

Changes to Figure 5 .......................................................................... 7

Added Figure 40 and Figure 43; Renumbered Sequentially ..... 14

Added Figure 44, Figure 45, Figure 46, Figure 47,

and Figure 48 ................................................................................... 15

Changes to Power-Down Operation Section .............................. 17

Updated Outline Dimensions ....................................................... 20

Changes to Ordering Guide .......................................................... 21

9/2013—Rev. B to Rev. C

Changes to Figure 1 and Figure 3 ................................................... 1

Change to Figure 5 ........................................................................... 7

Change to Figure 7 ........................................................................... 8

Updated Outline Dimensions ....................................................... 20

Changes to Ordering Guide .......................................................... 20

11/2008—Rev. 0 to Rev. A

Changes to Table 5.............................................................................7

Changes to Table 7.............................................................................8

Changes to Figure 32...................................................................... 13

Added Figure 44; Renumbered Sequentially .............................. 15

Changes to Layout .......................................................................... 15

Changes to Table 8.......................................................................... 16

Added Active Low-Pass Filter (LFP) Section ............................. 17

Added Figure 48 and Figure 49; Renumbered Sequentially ..... 17

Changes to Grounding Section .................................................... 18

Exposed Paddle Notation Added to Outline Dimensions ........ 19

Changes to Ordering Guide .......................................................... 20

5/2008—Revision 0: Initial Version

8/2011—Rev. A to Rev. B

Changes to Table 1 Conditions ....................................................... 3

Changes to Table 2 Conditions ....................................................... 4

Changes to Typical Performance Characteristics Conditions .... 9

Changes to Figure 18 ...................................................................... 10

Changes to Figure 42 ...................................................................... 15

Changes to Table 9 .......................................................................... 16

Changes to Ordering Guide .......................................................... 20

Rev. D | Page 2 of 21

�Data Sheet

ADA4857-1/ADA4857-2

SPECIFICATIONS

±5 V SUPPLY

TA = 25°C, G = 2, RG = RF = 499 Ω, RS = 100 Ω for G = 1 (SOIC), RL = 1 kΩ to ground, PD = no connect, unless otherwise noted.

Table 1.

Parameter

DYNAMIC PERFORMANCE

–3 dB Bandwidth (LFCSP/SOIC)

Full Power Bandwidth

Bandwidth for 0.1 dB Flatness

(LFCSP/SOIC)

Slew Rate (10% to 90%)

Settling Time to 0.1%

NOISE/HARMONIC PERFORMANCE

Harmonic Distortion

Input Voltage Noise

Input Current Noise

DC PERFORMANCE

Input Offset Voltage

Input Offset Voltage Drift

Input Bias Current

Test Conditions/Comments

Min

Typ

Gain (G) = 1, VOUT = 0.2 V p-p

G = 1, VOUT = 2 V p-p

G = 2, VOUT = 0.2 V p-p

G = 1, VOUT = 2 V p-p, THD < −40 dBc

G = 2, VOUT = 2 V p-p, RL = 150 Ω

650

850/750

600/550

400/350

110

75/90

MHz

MHz

MHz

MHz

MHz

G = 1, VOUT = 4 V step

G = 2, VOUT = 2 V step

2800

15

V/μs

ns

f = 1 MHz, G = 1, VOUT = 2 V p-p (HD2)

f = 1 MHz, G = 1, VOUT = 2 V p-p (HD3)

f = 10 MHz, G = 1, VOUT = 2 V p-p (HD2)

f = 10 MHz, G = 1, VOUT = 2 V p-p (HD3)

f = 50 MHz, G = 1, VOUT = 2 V p-p (HD2)

f = 50 MHz, G = 1, VOUT = 2 V p-p (HD3)

f = 100 kHz

f = 100 kHz

−108

−108

−88

−93

−65

−62

4.4

1.5

dBc

dBc

dBc

dBc

dBc

dBc

nV/√Hz

pA/√Hz

±2

TMIN to TMAX

TMIN to TMAX

2.3

−2

TMIN to TMAX

Input Bias Offset Current

Open-Loop Gain

PD (POWER-DOWN) PIN

PD Input Voltage

Turn-Off Time

Turn-On Time

PD Pin Leakage Current

INPUT CHARACTERISTICS

Input Resistance

Input Capacitance

Input Common-Mode Voltage

Range

Common-Mode Rejection Ratio

50

57

VOUT = −2.5 V to +2.5 V

Chip powered down

Chip powered down, TMIN to TMAX

Chip enabled

Chip enabled, TMIN to TMAX

50% off PD to