LTM4602

6A High Efficiency

DC/DC µModule

FEATURES

DESCRIPTION

n

The LTM®4602 is a complete 6A DC/DC step down power

supply. Included in the package are the switching controller, power FETs, inductor, and all support components.

Operating over an input voltage range of 4.5V to 20V, the

LTM4602 supports an output voltage range of 0.6V to 5V,

set by a single resistor. This high efficiency design delivers

6A continuous current (8A peak), needing no heat sinks or

airflow to meet power specifications. Only bulk input and

output capacitors are needed to finish the design.

n

n

n

n

n

n

n

n

n

n

n

n

n

n

Complete Switch Mode Power Supply

Wide Input Voltage Range: 4.5V to 20V

6A DC, 8A Peak Output Current

0.6V to 5V Output Voltage

1.5% Output Voltage Regulation

Ultrafast Transient Response

Current Mode Control

Pb-Free (e4) RoHS Compliant Package with GoldPad Finish

Pin Compatible with the LTM4600

Up to 92% Efficiency

Programmable Soft-Start

Output Overvoltage Protection

Optional Short-Circuit Shutdown Timer

See the LTM4602HV for Operation Up to 28VIN

Small Footprint, Low Profile (15mm × 15mm ×

2.8mm) Surface Mount LGA Package

APPLICATIONS

n

n

n

n

The low profile package (2.8mm) enables utilization of

unused space on the bottom of PC boards for high density

point of load regulation. High switching frequency and an

adaptive on-time current mode architecture enables a very

fast transient response to line and load changes without

sacrificing stability. Fault protection features include

integrated overvoltage and short circuit protection with

a defeatable shutdown timer. A built-in soft-start timer is

adjustable with a small capacitor.

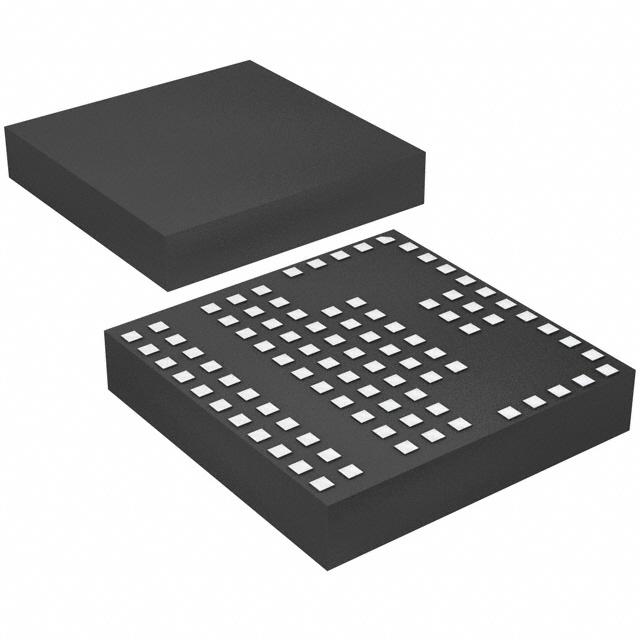

The LTM4602 is packaged in a thermally enhanced, compact

(15mm × 15mm) and low profile (2.8mm) over-molded

Land Grid Array (LGA) package suitable for automated assembly by standard surface mount equipment. For the 4.5V

to 28V input range version, refer to the LTM4602HV.

Telecom and Networking Equipment

Servers

Industrial Equipment

Point of Load Regulation

L, LT, LTC and LTM are registered trademarks of Linear Technology Corporation.

μModule is a trademark of Linear Technology Corporation. All other trademarks are the property

of their respective owners. Protected by U.S. Patents including 5481178, 6100678, 6580258,

5847554, 6304066.

TYPICAL APPLICATION

Efficiency vs Load Current

with 12VIN (FCB = 0)

100

6A μModuleTM Power Supply with 4.5V to 20V Input

90

VIN

CIN

VOUT

1.5V

6A

VOUT

LTM4602

VOSET

PGND SGND

COUT

RSET

66.5k

4602 TA01a

EFFICIENCY (%)

80

VIN

4.5V TO 20V

70

60

0.8VOUT

1.2VOUT

1.5VOUT

1.8VOUT

2.5VOUT

3.3VOUT

3.3VOUT (950kHz)*

50

40

30

20

*950kHz INSTEAD OF 1.3MHz

INCREASES 3.3V EFFICIENCY 2%

10

0

0

2

4

6

LOAD CURRENT (A)

8

4602 TA01b

4602fa

1

�LTM4602

ABSOLUTE MAXIMUM RATINGS

PIN CONFIGURATION

(Note 1)

TOP VIEW

fADJ

SVIN

EXTVCC

VOSET

FCB, EXTVCC, PGOOD, RUN/SS, VOUT .......... –0.3V to 6V

VIN, SVIN, fADJ ............................................ –0.3V to 20V

VOSET, COMP ............................................. –0.3V to 2.7V

Operating Temperature Range (Note 2).... –40°C to 85°C

Junction Temperature ........................................... 125°C

Storage Temperature Range................... –55°C to 125°C

COMP

SGND

RUN/SS

FCB

VIN

PGOOD

PGND

VOUT

LGA PACKAGE

104-LEAD (15mm × 15mm × 2.8mm)

TJMAX = 125°C, θJA = 15°C/W, θJC = 6°C/W,

θJA DERIVED FROM 95mm × 76mm PCB WITH 4 LAYERS

WEIGHT = 1.7g

ORDER INFORMATION

LEAD FREE FINISH

PART MARKING*

PACKAGE DESCRIPTION

TEMPERATURE RANGE

LTM4602EV#PBF

LTM4602V

104-Lead (15mm × 15mm × 2.8mm) LGA

–40°C to 85°C

LTM4602IV#PBF

LTM4602V

104-Lead (15mm × 15mm × 2.8mm) LGA

–40°C to 85°C

Consult LTC Marketing for parts specified with wider operating temperature ranges. *The temperature grade is identified by a label on the shipping container.

Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

This product is only offered in trays. For more information go to: http://www.linear.com/packaging/

ELECTRICAL CHARACTERISTICS

The l denotes the specifications which apply over the –40°C to 85°C

temperature range, otherwise specifications are at TA = 25°C, VIN = 12V. External CIN = 120μF, COUT = 200μF/Ceramic per typical

application (front page) configuration.

SYMBOL

PARAMETER

VIN(DC)

Input DC Voltage

VOUT(DC)

Output Voltage

CONDITIONS

FCB = 0V

VIN = 5V or 12V, VOUT = 1.5V, IOUT = 0A

MIN

l

4.5

l

1.478

1.470

TYP

MAX

UNITS

20

V

1.50

1.50

1.522

1.530

V

4

V

Input Specifications

VIN(UVLO)

Under Voltage Lockout Threshold

IOUT = 0A

3.4

IINRUSH(VIN)

Input Inrush Current at Startup

IOUT = 0A. VOUT = 1.5V, FCB = 0

VIN = 5V

VIN = 12V

0.6

0.7

A

A

IOUT = 0A, EXTVCC Open

VIN = 12V, VOUT = 1.5V, FCB = 5V

VIN = 12V, VOUT = 1.5V, FCB = 0V

VIN = 5V, VOUT = 1.5V, FCB = 5V

VIN = 5V, VOUT = 1.5V, FCB = 0V

Shutdown, RUN = 0.8V, VIN = 12V

1.2

42

1.0

52

50

mA

mA

mA

mA

μA

IQ(VIN)

Input Supply Bias Current

100

4602fa

2

�LTM4602

ELECTRICAL CHARACTERISTICS

The l denotes the specifications which apply over the –40°C to 85°C

temperature range, otherwise specifications are at TA = 25°C, VIN = 12V. Per typical application (front page) configuration.

SYMBOL

PARAMETER

CONDITIONS

MIN

IS(VIN)

Input Supply Current

VIN = 12V, VOUT = 1.5V, IOUT = 6A

VIN = 12V, VOUT = 3.3V, IOUT = 6A

VIN = 5V, VOUT = 1.5V, IOUT = 6 A

TYP

MAX

0.88

1.80

2.08

UNITS

A

A

A

Output Specifications

IOUTDC

Output Continuous Current Range

VIN = 12V, VOUT = 1.5V

(See Output Current Derating Curves for

Different VIN, VOUT and TA)

ΔVOUT(LINE)

Line Regulation Accuracy

VOUT = 1.5V, IOUT = 0A, FCB = 0V,

VIN = 4.5V to 20V

Load Regulation Accuracy

VOUT = 1.5V, IOUT = 0A to 6A, FCB = 0V,

VIN = 5V, VIN = 12V (Note 3)

VOUT

ΔVOUT(LOAD)

VOUT

0

6

A

l

0.15

0.3

%

l

±0.25

±0.15

±0.5

±1.0

%

%

15

VOUT(AC)

Output Ripple Voltage

VIN = 12V, VOUT = 1.5V, IOUT = 0A, FCB = 0V

10

mVP-P

fs

Output Ripple Voltage Frequency

VOUT = 1.5V, IOUT = 6A, FCB = 0V

850

kHz

tSTART

Turn-On Time

VOUT = 1.5V, IOUT = 1A

VIN = 12V

VIN = 5V

0.5

0.7

ms

ms

ΔVOUTLS

Voltage Drop for Dynamic Load Step

VOUT = 1.5V, Load Step: 0A/μs to 3A/μs

COUT = 22μF 6.3V, 330μF 4V POSCAP,

See Table 2

30

mV

tSETTLE

Settling Time for Dynamic Load Step

Load: 10% to 50% to 10% of Full Load

25

μs

IOUTPK

Output Current Limit

Output Voltage in Foldback

VIN = 12V, VOUT = 1.5V

VIN = 5V, VOUT = 1.5V

9

9

A

A

Control Stage

VOSET

Voltage at VOSET Pin

VRUN/SS

RUN ON/OFF Threshold

IRUN(C)/SS

Soft-Start Charging Current

IRUN(D)/SS

Soft-Start Discharging Current

VIN – SVIN

IOUT = 0A, VOUT = 1.5V

l

0.591

0.6

0.609

V

0.8

1.5

2

V

VRUN/SS = 0V

–0.5

–1.2

–3

μA

VRUN/SS = 4V

0.8

1.8

3

μA

EXTVCC = 0V, FCB = 0V

100

mV

EXTVCC = 5V, FCB = 0V, VOUT = 1.5V,

IOUT = 0A

16

mA

100

kΩ

IEXTVCC

Current into EXTVCC Pin

RFBHI

Resistor Between VOUT and VOSET Pins

VFCB

Forced Continuous Threshold

IFCB

Forced Continuous Pin Current

VFCB = 0.6V

0.57

0.6

0.63

V

–1

–2

μA

PGOOD Output

ΔVOSETH

PGOOD Upper Threshold

VOSET Rising

7.5

10

12.5

%

ΔVOSETL

PGOOD Lower Threshold

VOSET Falling

–7.5

–10

–12.5

%

ΔVOSET(HYS)

PGOOD Hysteresis

VOSET Returning

VPGL

PGOOD Low Voltage

IPGOOD = 5mA

Note 1: Stresses beyond those listed under Absolute Maximum Ratings

may cause permanent damage to the device. Exposure to any Absolute

Maximum Rating condition for extended periods may affect device

reliability and lifetime.

2

0.15

%

0.4

V

Note 2: The LTM4602E is guaranteed to meet performance specifications

from 0°C to 85°C. Specifications over the –40°C to 85°C operating

temperature range are assured by design, characterization and correlation

with statistical process controls. The LTM4602I is guaranteed over the

–40°C to 85°C temperature range.

Note 3: Test assumes current derating versus temperature.

4602fa

3

�LTM4602

TYPICAL PERFORMANCE CHARACTERISTICS

Efficiency vs Load Current

with 20VIN (FCB = 0)

Efficiency vs Load Current

with 12VIN (FCB = 0)

100

100

90

90

90

80

80

80

70

0.8VOUT

1.2VOUT

1.5VOUT

1.8VOUT

2.5VOUT

3.3VOUT*

*FOR 5V TO 3.3V CONVERSION,

SEE FREQUENCY ADJUSTMENT

IN APPLICATIONS INFORMATION

60

50

40

30

0

2

8

4

6

LOAD CURRENT (A)

70

0.8VOUT

1.2VOUT

1.5VOUT

1.8VOUT

2.5VOUT

3.3VOUT

3.3VOUT (950kHz)*

60

50

40

*950kHz INSTEAD OF 1.3MHz

INCREASES 3.3V EFFICIENCY 2%

30

0

2

4

6

LOAD CURRENT (A)

4602 G01

8

EFFICIENCY (%)

100

EFFICIENCY (%)

EFFICIENCY (%)

Efficiency vs Load Current

with 5VIN (FCB = 0)

(See Figure 21 for all curves)

70

60

1.2VOUT

1.5VOUT

1.8VOUT

2.5VOUT

3.3VOUT

50

40

30

0

2

4

6

4602 G02

Light Load Efficiency vs

Load Current with 12VIN

(FCB > 0.7V, COUT • VOUT (10 –3[F / VS ])

Generally 0.1μF is more than sufficient.

Since the load current is already limited by the current mode

control and current foldback circuitry during a short circuit,

overcurrent latchoff operation is NOT always needed or

desired, especially if the output has large capacitance or

the load draws high current during start up. The latchoff

feature can be overridden by a pull-up current greater than

5μA but less than 80μA to the RUN/SS pin. The additional

current prevents the discharge of CSS during a fault and

also shortens the soft-start period. Using a resistor from

RUN/SS pin to VIN is a simple solution to defeat latchoff. Any

pull-up network must be able to maintain RUN/SS above

4V maximum latchoff threshold and overcome the 4μA

maximum discharge current. Figure 3 shows a conceptual

drawing of VRUN during start-up and short circuit.

VRUN/SS

4V

3.5V

3V

1.5V

SHORT-CIRCUIT

LATCH ARMED

t

SOFT-START

CLAMPING

OF IL RELEASED

OUTPUT

OVERLOAD

HAPPENS

SHORT-CIRCUIT

LATCHOFF

VOUT

75%VO

t

SWITCHING

STARTS

4602 F03

Figure 3. RUN/SS Pin Voltage During Startup and

Short-Circuit Protection

VIN

VIN

RRUN/SS

LTM4602

RUN/SS

PGND SGND

RECOMMENDED VALUES FOR RRUN/SS

VIN

RRUN/SS

4.5V TO 5.5V

10.8V TO 13.8V

16V TO 20V

50k

150k

330k

4602 F04

Figure 4. Defeat Short-Circuit Latchoff with a Pull-Up

Resistor to VIN

4602fa

12

�LTM4602

APPLICATIONS INFORMATION

Enable

EXTVCC Connection

The RUN/SS pin can be driven from logic as shown in

Figure 5. This function allows the LTM4602 to be turned

on or off remotely. The ON signal can also control the

sequence of the output voltage.

An internal low dropout regulator produces an internal 5V

supply that powers the control circuitry and FET drivers.

Therefore, if the system does not have a 5V power rail,

the LTM4602 can be directly powered by VIN. The gate

driver current through LDO is about 18mA. The internal

LDO power dissipation can be calculated as:

RUN/SS

ON

PLDO_LOSS = 18mA • (VIN – 5V)

LTM4602

PGND SGND

2N7002

4602 F05

Figure 5. Enable Circuit with External Logic

Output Voltage Tracking

For the applications that require output voltage tracking,

several LTM4602 modules can be programmed by the

power supply tracking controller such as the LTC2923.

Figure 6 shows a typical schematic with LTC2923. Coincident, ratiometric and offset tracking for VOUT rising and

falling can be implemented with different sets of resistor

values. See the LTC2923 data sheet for more details.

Q1

VIN

5V

3.3V

DC/DC

VIN

VIN

RONB

VCC

RAMP

GATE

ON

RONA

LTM4602

VOSET

VOUT

FB1

RAMPBUF

STATUS

VIN

RTB1

TRACK1

RTA1

SDO

VIN

FB2

LTM4602

VOSET

VOUT

RTB2

TRACK2

RTA2

GND

1. EXTVCC grounded. Internal 5V LDO is always powered

from the internal 5V regulator.

2. EXTVCC connected to an external supply. Internal LDO

is shut off. A high efficiency supply compatible with the

MOSFET gate drive requirements (typically 5V) can improve overall efficiency. With this connection, it is always

required that the EXTVCC voltage can not be higher than

VIN pin voltage.

Discontinuous Operation and FCB Pin

1.8V

RSET

49.9k

LTC2923

The LTM4602 also provides an external gate driver voltage pin EXTVCC. If there is a 5V rail in the system, it is

recommended to connect EXTVCC pin to the external 5V

rail. Whenever the EXTVCC pin is above 4.7V, the internal 5V LDO is shut off and an internal 50mA P-channel

switch connects the EXTVCC to internal 5V. Internal 5V is

supplied from EXTVCC until this pin drops below 4.5V. Do

not apply more than 6V to the EXTVCC pin and ensure that

EXTVCC < VIN. The following list summaries the possible

connections for EXTVCC:

1.5V

RSET

66.5k

4602 F06

Figure 6. Output Voltage Tracking with the LTC2923 Controller

The FCB pin determines whether the internal bottom

MOSFET remains on when the inductor current reverses.

There is an internal 4.75k pull-down resistor connecting

this pin to ground. The default light load operation mode

is forced continuous (PWM) current mode. This mode

provides minimum output voltage ripple.

In the application where the light load efficiency is important, tying the FCB pin above 0.6V threshold enables

discontinuous operation where the bottom MOSFET turns

off when inductor current reverses. Therefore, the conduc-

4602fa

13

�LTM4602

APPLICATIONS INFORMATION

tion loss is minimized and light load efficiency is improved.

The penalty is that the controller may skip cycle and the

output voltage ripple increases at light load.

where N is the number of LTM4602s in parallel.

sinking methods. Thermal models are derived from

several temperature measurements at the bench,

and thermal modeling analysis. Application Note 103

provides a detailed explanation of the analysis for the

thermal models, and the derating curves. Tables 3

and 4 provide a summary of the equivalent θJA for the

noted conditions. These equivalent θJA parameters are

correlated to the measured values, and improve with

air-flow. The case temperature is maintained at 100°C

or below for the derating curves. This allows for 4W

maximum power dissipation in the total module with

top and bottom heat sinking, and 2W power dissipation

through the top of the module with an approximate

θJC between 6°C/W to 9°C/W. This equates to a total

of 124°C at the junction of the device. The θJA values

in Tables 3 and 4 can be used to derive the derating

curves for other output voltages.

Thermal Considerations and Output Current Derating

Safety Considerations

The power loss curves in Figures 8 and 13 can be used

in coordination with the load current derating curves

in Figures 9 to 12, and Figures 14 to 15 for calculating

an approximate θJA for the module with various heat

The LTM4602 modules do not provide isolation from VIN to

VOUT. There is no internal fuse. If required, a slow blow fuse

with a rating twice the maximum input current should be

provided to protect each unit from catastrophic failure.

Paralleling Operation with Load Sharing

Two or more LTM4602 modules can be paralleled to provide

higher than 6A output current. Figure 7 shows the necessary interconnection between two paralleled modules. The

OPTI-LOOP® current mode control ensures good current

sharing among modules to balance the thermal stress.

The new feedback equation for two or more LTM4602s

in parallel is:

100k

+ RSET

N

VOUT = 0.6V •

RSET

OPTI-LOOP is a registered trademark of Linear Technology Corporation.

VPULLUP

100k

PGOOD

VIN

VIN

LTM4602

VOUT

12A MAX

VOUT

PGND COMP VOSET SGND

RSET

PGOOD COMP VOSET SGND

VIN

PGND

LTM4602

VOUT

4602 F07

Figure 7. Parallel Two μModules with Load Sharing

4602fa

14

�LTM4602

APPLICATIONS INFORMATION

2.0

1.8

7

7

6

6

5

5

12V TO 1.5V

LOSS

1.2

1.0

0.8

5V TO 1.5V

LOSS

0.6

0.4

CURRENT (A)

1.4

CURRENT (A)

POWER LOSS (W)

1.6

4

3

2

0LFM

200LFM

400LFM

1

0

0

1.0

3.1

4.1

2.1

CURRENT (A)

5.1

6.1

50

60

70

80

90

0LFM

200LFM

400LFM

1

0

100

6

6

3.5

5

5

2

4

3

2

0LFM

200LFM

400LFM

50

60

70

80

90

0

50

TEMPERATURE (°C)

60

70

80

90

2.5

2.0

1.5

0.5

0

0.5

100

1.0

2.1

4.1

3.1

CURRENT (A)

TEMPERATURE (°C)

4602 F11

5.1

Figure 12. 12v to 1.5V, BGA Heat Sink

7

6

6

5

5

CURRENT (A)

7

4

3

2

6.1

4601 F13

4602 F09

Figure 11. 12V to 1.5V, No Heat Sink

CURRENT (A)

5V TO 3.3V LOSS

12V TO 3.3V LOSS

12V TO 3.3V (950kHz) LOSS

1.0

0LFM

200LFM

400LFM

1

100

100

3.0

POWER LOSS (W)

CURRENT (A)

4.0

0

90

Figure 10. 5V to 1.5V, BGA Heat Sink

7

3

80

4602 F10

Figure 9. 5V to 1.5V, No Heat Sink

7

4

70

TEMPERATURE (°C)

4602 F09

Figure 8. 1.5V Power Loss vs Load Current

1

60

50

TEMPERATURE (°C)

4602 F08

CURRENT (A)

3

2

0.2

0.6

4

Figure 13. 3.3V Power Loss

vs Load Current

4

3

2

0LFM

200LFM

400LFM

1

0

50

60

70

80

90

100

TEMPERATURE (°C)

0LFM

200LFM

400LFM

1

0

50

60

70

80

90

100

TEMPERATURE (°C)

4602 F14

Figure 14. 5V to 3.3V, No Heat Sink

4602 F15

Figure 15. 5V to 3.3V, BGA Heat Sink

4602fa

15

�LTM4602

7

7

6

6

5

5

CURRENT (A)

CURRENT (A)

APPLICATIONS INFORMATION

4

3

4

3

2

2

0LFM

200LFM

400LFM

1

0

50

60

0LFM

200LFM

400LFM

1

0

70

80

90

100

50

TEMPERATURE (°C)

60

70

80

90

100

TEMPERATURE (°C)

4602 F16

4602 F16

Figure 17. 12V to 3.3V, BGA Heat Sink

Figure 16. 12V to 3.3V, No Heat Sink

Table 3. 1.5V Output

Table 4. 3.3V Output

AIR FLOW (LFM)

HEAT SINK

θJA (°C/W)

AIR FLOW (LFM)

HEAT SINK

θJA (°C/W)

0

None

15.2

0

None

15.2

200

None

14

200

None

14.6

400

None

12

400

None

13.4

0

BGA Heat Sink

13.9

0

BGA Heat Sink

13.9

200

BGA Heat Sink

11.3

200

BGA Heat Sink

11.1

400

BGA Heat Sink

10.25

400

BGA Heat Sink

10.5

Layout Checklist/Example

The high integration of the LTM4602 makes the PCB board

layout very simple and easy. However, to optimize its electrical and thermal performance, some layout considerations

are still necessary.

• Use large PCB copper areas for high current path,

including VIN, PGND and VOUT. It helps to minimize the

PCB conduction loss and thermal stress.

• Place high frequency ceramic input and output capacitors next to the VIN, PGND and VOUT pins to minimize

high frequency noise.

• Place a dedicated power ground layer underneath

the unit.

• To minimize the via conduction loss and reduce module

thermal stress, use multiple vias for interconnection

between top layer and other power layers.

• Do not put vias directly on pads unless they are capped.

• Use a separated SGND ground copper area for components connected to signal pins. Connect the SGND

to PGND underneath the unit.

Figure 18 gives a good example of the recommended

layout.

LTM4602 Frequency Adjustment

The LTM4602 is designed to typically operate at 850kHz

across most input and output conditions. The control architecture is constant on time valley mode current control.

The fADJ pin is typically left open or decoupled with an

optional 1000pF capacitor. The switching frequency has

been optimized to maintain constant output ripple over the

operating conditions. The equations for setting the operating frequency are set around a programmable constant on

time. This on time is developed by a programmable current

into an on board 10pF capacitor that establishes a ramp

that is compared to a voltage threshold equal to the output

voltage up to a 2.4V clamp. This ION current is equal to:

ION = (VIN – 0.7V)/110k, with the 110k onboard resistor

4602fa

16

�LTM4602

APPLICATIONS INFORMATION

VIN

CIN

PGND

VOUT

4600 F16

LOAD

TOP LAYER

Figure 18. Recommended PCB Layout

from VIN to fADJ. The on time is equal to tON = (VOUT/ION)

• 10pF and tOFF = ts – tON. The frequency is equal to: Freq.

= DC/tON. The ION current is proportional to VIN, and the

regulator duty cycle is inversely proportional to VIN, therefore the step-down regulator will remain relatively constant

frequency as the duty cycle adjustment takes place with

lowering VIN. The on time is proportional to VOUT up to a

2.4V clamp. This will hold frequency relatively constant

with different output voltages up to 2.4V. The regulator

switching period is comprised of the on time and off time

as depicted in Figure 19.

t

(DC) DUTY CYCLE = ON

ts

tOFF

tON

t

V

DC = ON = OUT

ts

VIN

DC

FREQ =

tON

4602 F19

PERIOD ts

Figure 19. LTM4602 Switching Period

The LTM4602 has a minimum (tON) on time of 100 nanoseconds and a minimum (tOFF) off time of 400 nanoseconds.

The 2.4V clamp on the ramp threshold as a function of

VOUT will cause the switching frequency to increase by the

ratio of VOUT/2.4V for 3.3V and 5V outputs. This is due to

the fact the on time will not increase as VOUT increases

past 2.4V. Therefore, if the nominal switching frequency

is 850kHz, then the switching frequency will increase

to ~1.2MHz for 3.3V, and ~1.7MHz for 5V outputs due

to Frequency = (DC/tON) When the switching frequency

increases to 1.2MHz, then the time period tS is reduced

to ~833 nanoseconds and at 1.7MHz the switching period

reduces to ~588 nanoseconds. When higher duty cycle

conversions like 5V to 3.3V and 12V to 5V need to be

accommodated, then the switching frequency can be

lowered to alleviate the violation of the 400ns minimum

off time. Since the total switching period is tS = tON + tOFF,

tOFF will be below the 400ns minimum off time. A resistor

from the fADJ pin to ground can shunt current away from

the on time generator, thus allowing for a longer on time

and a lower switching frequency. 12V to 5V and 5V to

3.3V derivations are explained in the data sheet to lower

switching frequency and accommodate these step-down

conversions.

Equations for setting frequency for 12V to 5V:

ION = (VIN – 0.7V)/110k; ION = 103μA

frequency = (ION/[2.4V • 10pF]) • DC = 1.79MHz;

DC = duty cycle, duty cycle is (VOUT/VIN)

tS = tON + tOFF, tON = on-time, tOFF = off-time of the

switching period; tS = 1/frequency

tOFF must be greater than 400ns, or tS – tON > 400ns.

tON = DC • tS

1MHz frequency or 1μs period is chosen for 12V to 5V.

tON = 0.41 • 1μs ≅ 410ns

tOFF = 1μs – 410ns ≅ 590ns

tON and tOFF are above the minimums with adequate guard

band.

Using the frequency = (ION/[2.4V • 10pF]) • DC, solve for

ION = (1MHz • 2.4V • 10pF) • (1/0.41) ≅ 58μA. ION current

calculated from 12V input was 103μA, so a resistor from

fADJ to ground = (0.7V/15k) = 46μA. 103μA – 46μA =

57μA, sets the adequate ION current for proper frequency

range for the higher duty cycle conversion of 12V to

5V. Input voltage range is limited to 9V to 16V. Higher

input voltages can be used without the 15k on fADJ. The

inductor ripple current gets too high above 16V, and the

400ns minimum off-time is limited below 9V.

4602fa

17

�LTM4602

APPLICATIONS INFORMATION

Equations for setting frequency for 5V to 3.3V:

ION = (VIN – 0.7V)/110k; ION = 39μA

frequency = (ION/[2.4V • 10pF]) • DC = 1.07MHz;

DC = duty cycle, duty cycle is (VOUT/VIN)

tS = tON + tOFF, tON = on-time, tOFF = off-time of the

switching period; tS = 1/frequency

tOFF must be greater than 400ns, or tS – tON > 400ns.

tON = DC • tS

~450kHz frequency or 2.22μs period is chosen for 5V to

3.3V. Frequency range is about 450kHz to 650kHz from

4.5V to 7V input.

tON = 0.66 • 2.22μs ≅ 1.46μs

tOFF = 2.22μs – 1.46μs ≅ 760ns

Using the frequency = (ION/[2.4V • 10pF]) • DC, solve for

ION = (450kHz • 2.4V • 10pF) • (1/0.66) ≅ 16μA. ION current

calculated from 5V input was 39μA, so a resistor from fADJ

to ground = (0.7V/30.1k) = 23μA. 39μA – 23μA = 16μA,

sets the adequate ION current for proper frequency range

for the higher duty cycle conversion of 5V to 3.3V. Input

voltage range is limited to 4.5V to 7V. Higher input voltages

can be used without the 30.1k on fADJ. The inductor ripple

current gets too high above 7V, and the 400ns minimum

off-time is limited below 4.5V.

In 12V to 3.3V applications, if a 35k resistor is added from

the fADJ pin to ground, then a 2% efficiency gain will be

achieved as shown in the 12V efficiency graph in the Typical Performance Characteristics. This is due to the lower

transition losses in the power MOSFETs after lowering the

switching frequency down from 1.3MHz to 950kHz.

tON and tOFF are above the minimums with adequate guard

band.

4602fa

18

�LTM4602

APPLICATIONS INFORMATION

5V to 3.3V at 5A

R1

30.1k

VIN

4.5V TO 7V

C3

10μF

25V

C1

10μF

25V

C5

100pF

fADJ

VIN

EXTVCC

EFFICIENCY = 94%

AT 5A LOAD

VOUT

FCB

VOSET

RSET

22.1k

1%

LTM4602

RUN/SS

RUN/SOFT-START

VOUT

3.3V AT 5A

SVIN

PGOOD

COMP

SGND

C2

22μF

+

C4

330μF

6.3V

OPEN DRAIN

PGND

4602 F20a

5V TO 3.3V AT 5A WITH fADJ = 30.1k

C1, C3: TDK C3216X5R1E106MT

C2: TAIYO YUDEN, JMK316BJ226ML

C4: SANYO POSCAP, 6TPE330MIL

12V to 5V at 5A

R1

15k

VIN

7V TO 20V

C3

10μF

25V

C1

10μF

25V

VIN

C5

100pF

fADJ

EXTVCC

FCB

VOSET

RSET

13.7k

1%

LTM4602

RUN/SS

RUN/SOFT-START

VOUT

5V AT 5A

VOUT

SVIN

PGOOD

COMP

SGND

EFFICIENCY = 92.5%

AT 5A LOAD

C2

22μF

+

C4

330μF

6.3V

OPEN DRAIN

PGND

4602 F20b

7V TO 20V AT 5A WITH fADJ = 15k

C1, C3: TDK C3216X5R1E106MT

C2: TAIYO YUDEN, JMK316BJ226ML

C4: SANYO POSCAP, 6TPE330MIL

Figure 20. VIN to VOUT Step-Down Ratio for 12VIN to 5VOUT and 5VIN to 3.3VOUT

VIN

+

5V TO 20V

CIN

10μF

×2

CER

CIN

150μF

BULK

VIN

(MULTIPLE PINS)

GND

EXTVCC

C3

100pF

SVIN

VOUT

(MULTIPLE PINS)

fADJ

VOSET

VOUT

VOUT

6A

COUT1

REFER TO

TABLE 2

+

COUT2

REFER TO

TABLE 2

LTM4602

COMP

RSET

66.5k

REFER TO

TABLE 1

FCB

C4

OPT

RUN/SS

PGOOD

0.6V TO 5V

SGND

REFER TO STEP-DOWN

RATIO GRAPH

PGND

(MULTIPLE PINS)

GND

4602 F21

Figure 21. Typical Application, 5V to 20V Input, 0.6V to 5V Output, 6A Max

4602fa

19

�LTM4602

TYPICAL APPLICATION

Parallel Operation and Load Sharing

VIN

4.5V TO 20V

VOUT = 0.6V • ([100k/N] + RSET)/RSET

WHERE N = 2

C7

10μF

25V

VIN

fADJ

EXTVCC

VOUT

FCB

VOSET

LTM4602

RUN

SVIN

C9

22μF

RSET

15.8k

1%

+

C10

330μF

4V

PGOOD

COMP

SGND

PGND

VOUT

2.5V

12A

RUN/SOFT-START

C1

10μF

25V

VIN

C4

220pF

fADJ

EXTVCC

VOUT

FCB

C2

22μF

VOSET

LTM4602

RUN

+

C5

330μF

4V

R1

100k

SVIN

PGOOD

COMP

SGND

PGND

4602 TA02

C1, C7: TDK C3216X5R1E106MT

C2, C9: TAIYO YUDEN, JMK316BJ226ML-T501

C5, C10: SANYO POSCAP, 4TPE330MI

Current Sharing Between Two

LTM4602 Modules

6

INDIVIDUAL SHARE

12VIN

2.5VOUT

12AMAX

4

IOUT2

IOUT1

2

0

0

6

TOTAL LOAD

12

4602 TA03

4602fa

20

�5.7150

2.5400

0.3175

0.3175

2.7375

C(0.30)

PAD 1

13.97

BSC

0.11 – 0.27

6.9850

4.4450

1.2700

0.0000

1.4675

4.0075

6.9421

94

83

72

61

50

39

5.7158

43

89

78

67

56

45

15

11

100

36

29

7

99

88

77

66

55

44

14

10

98

87

76

65

54

35

28

6

1.9042

37

30

16

91

102

101

80

69

58

47

90

79

68

57

46

38

31

17

18

4.4442

33

1

1

8

3

5

6

7

4

8

13

10

9

11

6

28

35

14

44

55

13

13.93

BSC

12

10

7

29

36

15

45

56

67

78

89

100

14

11

15

16

30

37

BOTTOM VIEW

9

5

27

34

54

43

66

77

88

99

16

46

57

68

79

90

101

17

17

31

38

18

47

58

69

80

91

102

18

20

48

19

22

49

60

71

70

59

82

93

104

81

92

103

104

93

82

71

60

49

20

24

24

23

22

21

19

21

23

20

21

22

26

42

53

65

76

87

98

12.70

BSC

103

92

81

70

59

48

19

12

4

34

27

13

9

6.9865

23

2

3

41

52

40

51

50

86

97

64

85

96

63

61

1.9058

5

3.1742

SUGGESTED SOLDER PAD LAYOUT

TOP VIEW

62

73

72

97

86

75

64

53

42

75

84

83

96

85

74

63

52

41

33

26

4.4950

74

95

2

95

84

73

62

51

40

1.0900

94

39

4.4458

2.3600

3.1758

4

5.7142

25

32

32

25

12

6.3500

8

3.8100

0.0000

1.2700

5.2775

5.0800

0.6358

0.3175

0.3175

0.0000

5.7650

2.5400

0.6342

1.2700

3

2.5400

2

3.8100

1

5.0800

6.9888

6.3500

6.5475

A

C

E

G

J

L

M

N

P

R

B

D

F

H

K

DETAIL B

MOLD

CAP

LGA104 0206

DETAIL B

4

PAD 1

CORNER

aaa Z

DETAILS OF PAD #1 IDENTIFIER ARE OPTIONAL,

BUT MUST BE LOCATED WITHIN THE ZONE INDICATED.

THE PAD #1 IDENTIFIER IS A MARKED FEATURE OR A

NOTCHED BEVELED PAD

4

SYMBOL TOLERANCE

aaa

0.15

bbb

0.10

eee

0.15

6. THE TOTAL NUMBER OF PADS: 104

5. PRIMARY DATUM -Z- IS SEATING PLANE

LAND DESIGNATION PER JESD MO-222, SPP-010

3

2. ALL DIMENSIONS ARE IN MILLIMETERS

NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994

0.27 – 0.37

SUBSTRATE

2.72 – 2.92

(Reference LTM DWG # 05-05-1800)

eee M X Y

PADS

SEE NOTES

T

3

2.45 – 2.55

bbb Z

LGA Package

104-Lead (15mm × 15mm)

TOP VIEW

15

BSC

X

15

BSC

Y

aaa Z

LTM4602

PACKAGE DESCRIPTION

4602fa

21

Z

�LTM4602

PACKAGE DESCRIPTION

Pin Assignment Tables

(Arranged by Pin Number)

PIN NAME

A1 A2 A3 VIN

A4 A5 VIN

A6 A7 VIN

A8 A9 VIN

A10 A11 VIN

A12 A13 VIN

A14 A15 fADJ

A16 A17 SVIN

A18 A19 EXTVCC

A20 A21 VOSET

A22 A23 -

PIN NAME

B1 VIN

B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 B12 B13 B14 B15 B16 B17 B18 B19 B20 B21 B22 B23 COMP

PIN NAME

C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 VIN

C11 C12 VIN

C13 C14 VIN

C15 C16 C17 C18 C19 C20 C21 C22 C23 -

PIN NAME

D1 VIN

D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 D16 D17 D18 D19 D20 D21 D22 D23 SGND

PIN NAME

E1 E2 E3 E4 E5 E6 E7 E8 E9 E10 VIN

E11 E12 VIN

E13 E14 VIN

E15 E16 E17 E18 E19 E20 E21 E22 E23 -

PIN NAME

F1 VIN

F2 F3 F4 F5 F6 F7 F8 F9 F10 F11 F12 F13 F14 F15 F16 F17 F18 F19 F20 F21 F22 F23 RUN/SS

PIN NAME

G1 PGND

G2 G3 G4 G5 G6 G7 G8 G9 G10 G11 G12 G13 G14 G15 G16 G17 G18 G19 G20 G21 G22 G23 FCB

PIN NAME

H1 H2 H3 H4 H5 H6 H7 PGND

H8 H9 PGND

H10 H11 PGND

H12 H13 PGND

H14 H15 PGND

H16 H17 PGND

H18 H19 H20 H21 H22 H23 -

PIN NAME

J1 PGND

J2 J3 J4 J5 J6 J7 J8 J9 J10 J11 J12 J13 J14 J15 J16 J17 J18 J19 J20 J21 J22 J23 PGOOD

PIN NAME

K1 K2 K3 K4 K5 K6 K7 PGND

K8

K9 PGND

K10

K11 PGND

K12 K13 PGND

K14 K15 PGND

K16 K17 PGND

K18 K19 K20 K21 K22 K23 -

PIN NAME

L1 L2 PGND

L3 L4 PGND

L5 L6 PGND

L7 L8 PGND

L9 L10 PGND

L11 L12 PGND

L13 L14 PGND

L15 L16 PGND

L17 L18 PGND

L19 L20 PGND

L21 L22 PGND

L23 -

PIN NAME

M1 M2 PGND

M3 M4 PGND

M5 M6 PGND

M7 M8 PGND

M9 M10 PGND

M11 M12 PGND

M13 M14 PGND

M15 M16 PGND

M17 M18 PGND

M19 M20 PGND

M21 M22 PGND

M23 -

PIN NAME

N1 N2 PGND

N3 N4 PGND

N5 N6 PGND

N7 N8 PGND

N9 N10 PGND

N11 N12 PGND

N13 N14 PGND

N15 N16 PGND

N17 N18 PGND

N19 N20 PGND

N21 N22 PGND

N23 -

PIN NAME

P1 P2 VOUT

P3 P4 VOUT

P5 P6 VOUT

P7 P8 VOUT

P9 P10 VOUT

P11 P12 VOUT

P13 P14 VOUT

P15 P16 VOUT

P17 P18 VOUT

P19 P20 VOUT

P21 P22 VOUT

P23 -

PIN NAME

R1 R2 VOUT

R3 R4 VOUT

R5 R6 VOUT

R7 R8 VOUT

R9 R10 VOUT

R11 R12 VOUT

R13 R14 VOUT

R15 R16 VOUT

R17 R18 VOUT

R19 R20 VOUT

R21 R22 VOUT

R23 -

PIN NAME

T1 T2 VOUT

T3 T4 VOUT

T5 T6 VOUT

T7 T8 VOUT

T9 T10 VOUT

T11 T12 VOUT

T13 T14 VOUT

T15 T16 VOUT

T17 T18 VOUT

T19 T20 VOUT

T21 T22 VOUT

T23 4602fa

22

�LTM4602

PACKAGE DESCRIPTION

Pin Assignment Tables

(Arranged by Pin Number)

PIN NAME

G1

PGND

H7

H9

H11

H13

H15

H17

PGND

PGND

PGND

PGND

PGND

PGND

J1

PGND

K7

K9

K11

K13

K15

K17

PGND

PGND

PGND

PGND

PGND

PGND

L2

L4

L6

L8

L10

L12

L14

L16

L18

L20

L22

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

M2

M4

M6

M8

M10

M12

M14

M16

M18

M20

M22

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

N2

N4

N6

N8

N10

N12

N14

N16

N18

N20

N22

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PIN NAME

P2

P4

P6

P8

P10

P12

P14

P16

P18

P20

P22

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

R2

R4

R6

R8

R10

R12

R14

R16

R18

R20

R22

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

T2

T4

T6

T8

T10

T12

T14

T16

T18

T20

T22

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

PIN NAME

A3

A5

A7

A9

A11

A13

VIN

VIN

VIN

VIN

VIN

VIN

B1

VIN

C10

C12

C14

VIN

VIN

VIN

D1

VIN

E10

E12

E14

VIN

VIN

VIN

F1

VIN

PIN NAME

A15

fADJ

A17

SVIN

A19

EXTVCC

A21

VOSET

B23

COMP

D23

SGND

F23

RUN/SS

G23

FCB

J23

PGOOD

4602fa

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

23

�LTM4602

TYPICAL APPLICATION

1.8V, 6A Regulator

VIN

4.5V TO 20V

C2

10μF

25V

C1

10μF

25V

VIN

C5

100pF

fADJ

EXTVCC

VOUT

1.8V AT 6A

VOUT

FCB

VOSET

R1

100k

LTM4602

RUN

C3

22μF

+

C4

330μF

4V

SVIN

PGOOD

COMP

SGND

PGOOD

PGND

4602 TA04

RSET

49.9k

1%

C1, C2: TDK C3216X5R1E106MT

C3: TAIYO YUDEN, JMK316BJ226ML-T501

C4: SANYO POSCAP, 4TPE330MI

RELATED PARTS

PART NUMBER

DESCRIPTION

COMMENTS

LTC2900

Quad Supply Monitor with Adjustable Reset Timer

Monitors Four Supplies; Adjustable Reset Timer

LTC2923

Power Supply Tracking Controller

Tracks Both Up and Down; Power Supply Sequencing

LT3825/LT3837

Synchronous Isolated Flyback Controllers

No Optocoupler Required; 3.3V, 12A Output; Simple Design

LTM4600

10A DC/DC μModule

10A Basic DC/DC Module

LTM4601

12A DC/DC μModule with PLL, Output Tracking/

Margining and Remote Sensing

Synchronizable, PolyPhase® Operation, LTM4601-1 Version has no Remote

Sensing, Fast Transient Response

LTM4603

6A DC/DC μModule with PLL and Output Tracking/

Margining and Remote Sensing

Synchronizable, PolyPhase Operation, LTM4603-1 Version has no Remote

Sensing, Fast Transient Response

PolyPhase is a registered trademark of Linear Technology Corporation.

This product contains technology licensed from Silicon Semiconductor Corporation.

24 Linear Technology Corporation

®

4602fa

LT 0807 REV A • PRINTED IN USA

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900 ● FAX: (408) 434-0507

●

www.linear.com

© LINEAR TECHNOLOGY CORPORATION 2007

�