Not Recommended For New Designs

bq24150

bq24151

www.ti.com

SLUS824A – JUNE 2008 – REVISED JANUARY 2010

Fully Integrated Switch-Mode One-Cell Li-Ion Charger with Full USB Compliance and

USB-OTG Support

Check for Samples: bq24150, bq24151

FEATURES

1

•

•

2

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Charge Faster than Linear Chargers

High-Accuracy Voltage and Current Regulation

– Input Current Regulation Accuracy: ±5%

(100 mA and 500 mA)

– Charge Voltage Regulation Accuracy:

±0.5% (25°C), ±1% (0°C to 125°C)

– Charge Current Regulation Accuracy: ±5%

High-Efficiency Mini-USB/AC Battery Charger

for Single-Cell Li-Ion and Li-Polymer Battery

Packs

20-V Absolute Maximum Input Voltage Rating

6-V Maximum Operating Input Voltage

Built-In Input Current Sensing and Limiting

Integrated Power FETs for Up To 1.25-A

Charge Rate

Programmable Charge Parameters through

I2C™ Interface (up to 3.4 Mbps):

– Input Current

– Fast-Charge/Termination Current

– Charge Voltage (3.5 V to 4.44 V)

– Safety Timer

– Termination Enable

Synchronous Fixed-Frequency PWM

Controller Operating at 3 MHz With 0% to

99.5% Duty Cycle

Automatic High Impedance Mode for Low

Power Consumption

Safety Timer with Reset Control

Reverse Leakage Protection Prevents Battery

Drainage

Thermal Regulation and Protection

Input/Output Overvoltage Protection

Status Output for Charging and Faults

USB Friendly Boot-Up Sequence

Automatic Charging – bq24150

Automatic High Impedance Mode – bq24151

Boost Mode Operation for USB OTG:

– Input Voltage Range (from Battery): 2.5 V to

4.5 V

– Output Voltage for VBUS: 5.05 V

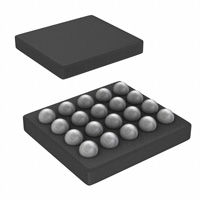

1.976 x 1.946mm 20-Pin WCSP Package

•

APPLICATIONS

•

•

•

Mobile and Smart Phones

MP3 Players

Handheld Devices

DESCRIPTION

The bq24150/1 is a compact, flexible, high-efficiency,

USB-friendly switch-mode charge management

device for single-cell Li-ion and Li-polymer batteries

used in a wide range of portable applications. The

charge parameters can be programmed through an

I2C interface. The bq24150/1 integrates a

synchronous PWM controller, power MOSFETs, input

current sensing, high-accuracy current and voltage

regulation, and charge termination, into a small

WCSP package.

The bq24150/1 charges the battery in three phases:

conditioning, constant current and constant voltage.

The input current is automatically limited to the value

set by the host. Charge is terminated based on

user-selectable minimum current level. A safety timer

with reset control provides a safety backup for I2C

interface. During normal operation, bq24150/1

automatically restarts the charge cycle if the battery

voltage falls below an internal threshold and

automatically enters sleep mode or high impedance

mode when the input supply is removed. The charge

status is reported to the host using the I2C interface.

Typical Application Circuit

LO 1.0 mH

VBUS

C IN

VBUS

1 mF

PMID

10 kW

SCL

SDA

STAT

OTG

10 kW

10 kW

HOST

I2C BUS

BOOT

10nF

PACK +

0.1 mF

PGND

4.7 mF

10 kW

CO

1 0mF

C BOOT

bq24150/1

C IN

VAUX

R SNS

SW

U1

+

CSIN

SCL

SDA

STAT

OTG

PACK -

CSOUT

AUXPWR

VREF

C AUXPWR

C VREF

1mF

1mF

1

2

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

I2C is a trademark of Philips Electronics.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2008–2010, Texas Instruments Incorporated

�Not Recommended For New Designs

bq24150

bq24151

SLUS824A – JUNE 2008 – REVISED JANUARY 2010

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more

susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

DESCRIPTION CONTINUED

During the charging process, the bq24150/1 monitors its junction temperature (TJ) and reduces the charge

current once TJ increases to approximately 125°C. To support USB OTG device, bq24150/1 provides VBUS

(approximately 5.05 V) by boosting the battery voltage. The bq24150/1 is available in 20-pin WCSP package.

WCSP PACKAGE

(Top View)

A1

A2

A3

A4

VBUS

VBUS

BOOT

SCL

B3

B4

PMID

B1

PMID

B2

PMID

SDA

C1

C2

C3

C4

SW

SW

SW

STAT

D1

D2

D3

D4

PGND

PGND

PGND

OTG

E1

E2

E3

E4

CSIN

AUX

PWR

VREF

CSOUT

TERMINAL FUNCTIONS

TERMINAL

I/O

DESCRIPTION

NAME

NO.

CSOUT

E4

I

Battery voltage and current sense input. Bypass it with a ceramic capacitor (minimum 0.1 mF) to

PGND if there are long inductive leads to battery.

VBUS

A1, A2

I

Charger input voltage. Bypass it with a 1-mF ceramic capacitor from VBUS to PGND.

PMID

B1, B2, B3

O

Connection point between reverse blocking MOSFET and high-side switching MOSFET. Bypass it

with a minimum of 3.3-mF capacitor from PMID to PGND.

SW

C1, C2, C3

O

Internal switch to output inductor connection.

O

Boot-strapped capacitor for the high-side MOSFET gate driver. Connect a 10-nF ceramic capacitor

(voltage rating above 10 V) from BOOT pin to SW pin.

BOOT

A3

PGND

D1, D2, D3

CSIN

E1

I

Charge current-sense input. Battery current is sensed via the voltage drop across an external sense

resistor. A 0.1-mF ceramic capacitor to PGND is required.

SCL

A4

I

I2C interface clock. Open drain output, connect a 10-kΩ pullup resistor

SDA

B4

I/O

I2C interface data. Open drain output, connect a 10-kΩ pullup resistor

STAT

C4

O

Charge status pin. Pull low when charge in progress. Open drain for other conditions. During faults, a

128-mS pulse is sent out. STAT pin can be disabled by the EN_STAT bit in control register. STAT can

be used to drive a LED or communicate with a host processor.

VREF

E3

O

Internal bias regulator voltage. Connect a 1-mF ceramic capacitor from this output to PGND. External

load on VREF is not allowed.

AUXPWR

E2

I

Auxiliary power supply, connected to the battery pack to provide power in high-impedance mode.

Bypass it with a 1-mF ceramic capacitor from this pin to PGND.

I

Boost mode enable control or input current limiting selection pin. When OTG is in active status,

bq24150/1 is forced to operate in boost mode. It has higher priority over I2C control and can be

disabled through control register. The logic voltage level at OTG active status can also be controlled.

At POR, the OTG pin is default to be used as the input current limiting selection pin. When OTG =

High, Iin – limit = 500mA and when OTG = Low, Iin – limit = 100mA, see the Control Register for

details.

OTG

2

Power ground

D4

Submit Documentation Feedback

Copyright © 2008–2010, Texas Instruments Incorporated

Product Folder Link(s): bq24150 bq24151

�Not Recommended For New Designs

www.ti.com

bq24150

bq24151

SLUS824A – JUNE 2008 – REVISED JANUARY 2010

PACKAGE DIMENSIONS

PACKAGE DEVICES

bq24150, bq24151

D

E

1.976 ± 0.05mm

1.946 ± 0.05mm

ORDERING INFORMATION (1)

PART NO.

bq24150YFFR

bq24150YFFT

bq24151YFFR

bq24151YFFT

(1)

MARKING

MEDIUM

QUANTITY

Automatic Charging

(VBUS Recycled, VBAT <

VLOWV, 32 Minutes Mode)

Part Number Bit

PN0, Control

Register 03H, bit 3

bq24150

Tape and

Reel

3000

Yes

1

bq24150

Tape and

Reel

250

Yes

1

bq24151

Tape and

Reel

3000

No

0

bq24151

Tape and

Reel

250

No

0

For the most current package information, see the Package Option Addendum at the end of this document, or see the TI website at

www.ti.com.

DISSIPATION RATINGS (1)

RqJA

RqJC

TA ≤ 25°C

POWER RATING

DERATING FACTOR

TA > 25°C

185°C/W (2)

1.57°C/W

0.54 W

0.0054 W/°C

PACKAGE

WSCP-20

(1)

(2)

(1)

Maximum power dissipation is a function of TJ(max), RqJA and TA. The maximum allowable power dissipation at any allowable ambient

temperature is PD = [TJ(max)-TA] / RqJA.

For PCB board with only top trace layer. For PCB board with four layers (top trace layer, buried ground layer, buried signal layer and

bottom layer), RqJA drops to 75.96°C/W

ABSOLUTE MAXIMUM RATINGS (1)

(2)

over operating free-air temperature range (unless otherwise noted)

VALUE

UNIT

–0.3 to 20 (3)

V

VSS

Supply voltage range (with

respect to PGND)

VBUS

VI

Input voltage range (with

respect to and PGND)

SCL, SDA, OTG, CSIN, CSOUT, AUXPWR

–0.3 to 7

V

PMID, STAT

–0.3 to 20

V

VO

Output voltage range (with

respect to and PGND)

VREF

SW, BOOT

6.5

V

–0.7 to 20

V

Voltage difference between CSIN and CSOUT inputs (V(CSIN) -V(CSOUT) )

±7

V

Output sink

STAT

10

mA

SW

IO

Output Current (average)

1.25

A

TA

Operating free-air temperature range

–40 to 85

°C

TJ

Junction temperature

–40 to 150

°C

Tstg

Storage temperature

–65 to 150

°C

(1)

(2)

(3)

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage

values are with respect to the network ground terminal unless otherwise noted.

All voltages are with respect to GND if not specified. Currents are positive into, negative out of the specified terminal.

The bq24150/1 family can withstand up to 10.6 V continuously and 20 V for a maximum of 432 hours.

Submit Documentation Feedback

Copyright © 2008–2010, Texas Instruments Incorporated

Product Folder Link(s): bq24150 bq24151

3

�Not Recommended For New Designs

bq24150

bq24151

SLUS824A – JUNE 2008 – REVISED JANUARY 2010

www.ti.com

RECOMMENDED OPERATING CONDITIONS

MIN

NOM

MAX

UNIT

VBUS

Supply voltage, VBUS

4

6 (1)

V

TJ

Operating junction temperature range

0

+125

°C

(1)

The inherent switching noise voltage spikes should not exceed the absolute maximum rating on either the BOOST or SW pins. A tight

layout minimizes switching noise.

ELECTRICAL CHARACTERISTICS

Circuit of Figure 1, VBUS = 5 V, HZ_MODE = 0, OPA_MODE = 0 (charger mode operation), TJ = 0°C to 125°C, TJ = 25°C for

typical values (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

INPUT CURRENTS

VBUS > VBUS(min), PWM switching

10

VBUS > VBUS(min), PWM NOT switching

I(VBUS)

VBUS supply current control

Ilkg

mA

5

0°C < TJ < 85°C, VBUS = 5 V, HZ_MODE = 1,

V(AUXPWR) > V(LOWV), SCL, SDA, OTG = 0 V or

1.8 V

20

mA

0°C < TJ < 85°C, VBUS = 5 V, HZ_MODE = 1,

V(AUXPWR) < V(LOWV), 32S mode, SCL, SDA, OTG

= 0 V or 1.8 V

35

mA

Leakage current from battery to

VBUS pin

0°C < TJ < 85°C, V(AUXPWR) = 4.2 V, High

Impedance mode

5

mA

Battery discharge current in High

Impedance mode, (CSIN,

CSOUT, AUXPWR, SW pins)

0°C < TJ < 85°C, V(AUXPWR) = 4.2 V, High

Impedance mode

SCL, SDA, OTG = 0 V or 1.8 V

20

mA

V

VOLTAGE REGULATION

V(OREG)

Output charge voltage

Voltage regulation accuracy

Operating in voltage regulation, programmable

TA = 25°C

3.5

4.44

–0.5%

0.5%

–1%

1%

CURRENT REGULATION (FAST CHARGE)

IO(CHARGE)

Output charge current

Regulation accuracy for charge

current across R(SNS)

V(IREG) = IO(CHARGE) × R(SNS)

V(LOWV) ≤ V(AUXPWR) < V(OREG), VBUS > V(SLP),

R(SNS) = 68 mΩ Programmable

550

1250

20 mV ≤ V(IREG) ≤ 40 mV

–5%

5%

40 mV < V(IREG)

–3%

3%

mA

WEAK BATTERY DETECTION

V(LOWV)

Weak battery voltage threshold

Programmable

Weak battery voltage accuracy

Hysteresis for V(LOWV)

Battery voltage falling

Deglitch time for weak battery

threshold

Rising voltage, 2-mV over drive, tRISE = 100 ns

3.4

3.7

–5%

5%

V

100

mV

30

ms

OTG PIN LOGIC LEVEL

VIL

Input low threshold level

VIH

Input high threshold level

0.4

1.3

V

V

CHARGE TERMINATION DETECTION

I(TERM)

Termination charge current

V(AUXPWR) > V(OREG) – V(RCH),

VBUS > V(SLP), R(SNS) = 68 mΩ Programmable

Deglitch time for charge

termination

Both rising and falling, 2-mV overdrive, tRISE, tFALL

= 100 ns

Voltage regulation accuracy for

termination current across R(SNS)

V(IREG_TERM) = IO(TERM) × R(SNS)

50

400

30

mA

ms

3 mV ≤ V(IREG_TERM) < 5 mV

–25%

25%

5 mV ≤ V(IREG_TERM) < 20 mV

–10%

10%

20 mV ≤ V(IREG_TERM) ≤ 40 mV

–5%

5%

INPUT POWER SOURCE DETECTION

Input voltage lower limit

Input power source detection

VIN(min)

Deglitch time for VBUS rising

above VIN(min)

Hysteresis for VIN(min)

Input voltage rising

tINT

Detection Interval

Input power source detection

4

3.6

Rising voltage, 2-mV overdrive, tRISE = 100 ns

Submit Documentation Feedback

3.8

4

30

100

200

2

V

ms

mV

S

Copyright © 2008–2010, Texas Instruments Incorporated

Product Folder Link(s): bq24150 bq24151

�Not Recommended For New Designs

www.ti.com

bq24150

bq24151

SLUS824A – JUNE 2008 – REVISED JANUARY 2010

ELECTRICAL CHARACTERISTICS (continued)

Circuit of Figure 1, VBUS = 5 V, HZ_MODE = 0, OPA_MODE = 0 (charger mode operation), TJ = 0°C to 125°C, TJ = 25°C for

typical values (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

INPUT CURRENT LIMITING

IIN

Input current limiting threshold

USB charge mode

IIN = 100 mA

88

93

98

IIN = 500 mA

450

475

500

mA

VREF BIAS REGULATOR

Vref

Internal bias regulator voltage

VBUS >VIN(min) or V(AUXPWR) > V(BAT)min,

I(VREF) = 1 mA, C(VREF) = 1 mF

2

Vref output short current limit

Voltage from BOOT pin to SW

pin

6.5

30

During charge or boost operation

V

mA

6.5

V

BATTERY RECHARGE THRESHOLD

V(RCH)

Recharge threshold voltage

Below V(OREG)

Deglitch time

V(AUXPWR) decreasing below threshold,

tFALL = 100 ns, 10-mV overdrive

Low-level output saturation

voltage, STAT

IO = 10 mA, sink current

High-level leakage current for

STAT

Voltage on STAT pin is 5 V

100

120

150

130

mV

ms

STAT OUTPUTS

VOL(STAT)

0.4

V

1

mA

0.4

V

I2C BUS LOGIC LEVELS AND TIMING CHARACTERISTICS

VOL

Output low threshold level

VIL

Input low threshold level

VIH

Input high threshold level

I(BIAS)

Input bias current

f(SCL)

SCL clock frequency

IO = 10 mA, sink current

0.4

1.2

V

V

V(pull-up) = 1.8 V, SDA and SCL

1

3.4

mA

MHz

BATTERY DETECTION

I(DETECT)

Battery detection current before

charge done (sink current) (1)

Begins after termination detected,

V(AUXPWR) ≤ V(OREG)

Battery detection time

–0.45

mA

262

ms

SLEEP COMPARATOR

V(SLP)

V(SLP_EXIT)

Sleep-mode entry threshold,

VBUS - VAUXPWR

2.3 V ≤ V(AUXPWR) ≤ V(OREG), VBUS falling

Sleep-mode exit hysteresis

2.3 V ≤ V(AUXPWR) ≤ V(OREG)

Deglitch time for VBUS rising

above V(SLP) + V(SLP_EXIT)

Rising voltage, 2-mV overdrive, tRISE = 100 ns

+0.0

+0.04

+0.1

V

40

100

160

mV

30

ms

UNDERVOLTAGE LOCKOUT

UVLO

IC active threshold voltage

VBUS rising

3.05

3.3

UVLO(HYS)

IC active hysteresis

VBUS falling from above UVLO

120

150

3.55

Internal top reverse blocking

MOSFET on-resistance

IIN(LIMIT) = 500 mA, Measured from VBUS to

PMID

180

250

Internal top N-channel Switching

MOSFET on-resistance

Measured from PMID to SW

120

250

Internal bottom N-channel

MOSFET on-resistance

Measured from SW to PGND

110

200

V

mV

PWM

f(OSC)

Oscillator frequency

3

Frequency accuracy

D(MAX)

Maximum duty cycle

D(MIN)

Minimum duty cycle

Synchronous mode to

non-synchronous mode transition

current threshold (2)

(1)

(2)

–10%

mΩ

MHz

10%

99.5%

0

Low side MOSFET cycle by cycle current sensing

100

mA

Negative charge current means the charge current flows from the battery to charger (discharging battery).

Bottom N-channel MOSFET always turns on for Ⅹ60 ns and then turns off if current is too low.

Submit Documentation Feedback

Copyright © 2008–2010, Texas Instruments Incorporated

Product Folder Link(s): bq24150 bq24151

5

�Not Recommended For New Designs

bq24150

bq24151

SLUS824A – JUNE 2008 – REVISED JANUARY 2010

www.ti.com

ELECTRICAL CHARACTERISTICS (continued)

Circuit of Figure 1, VBUS = 5 V, HZ_MODE = 0, OPA_MODE = 0 (charger mode operation), TJ = 0°C to 125°C, TJ = 25°C for

typical values (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

BOOST MODE OPERATION FOR VBUS (OPA_MODE = 1, HZ_MODE = 0)

Boost output voltage (to pin

VBUS)

2.5V < V(AUXPWR) < 4.5 V, Open loop

Boost output voltage accuracy

Including line and load regulation

I(BO)

Maximum output current for

boost

V(BUS_B) = 5.05 V, 2.5 V < V(AUXPWR) < 4.5 V

I(BLIMIT)

Cycle by cycle current limit for

boost

V(BUS_B) = 5.05 V, 2.5 V < V(AUXPWR) < 4.5 V

VBUS(OVP)

Overvoltage protection threshold

for boost (VBUS pin)

Threshold over VBUS to turn off converter during

boost

VBUS(OVP) hysteresis

VBUS falling from above VBUS(OVP)

Maximum battery voltage for

boost (CSOUT pin)

V(CSOUT) rising edge during boost

V(BUS_B)

V(BAT)MAX

V(BAT)MIN

5.05

–3%

V

3%

200

mA

1

5.8

6

A

6.2

125

4.75

4.9

V(BAT)MAX hysteresis

V(CSOUT) falling from above VBATMAX

200

Minimum battery voltage for

boost (AUXPWR pin)

During boosting

2.5

Before boost starts

2.9

Boost output resistance at

high-impedance mode (From

VBUS to PGND)

HZ_MODE = 1

165

Input VBUS OVP threshold

voltage

Threshold over VBUS to turn off converter during

charge

6.3

V(OVP_IN) hysteresis

VBUS falling from above V(OVP_IN)

Battery OVP threshold voltage

V(CSOUT) threshold over V(OREG) to turn off charger

during charge

V

mV

5.05

V

mV

V

3.05

V

kΩ

PROTECTION

V(OVP-IN)

V(OVP)

110

V(OVP) hysteresis

Lower limit for V(CSOUT) falling from above V(OVP)

Charge mode operation

1.5

Short-circuit voltage threshold

V(AUXPWR) falling

1.9

V(SHORT) hysteresis

V(AUXPWR) rising from below V(SHORT)

I(SHORT)

Short-circuit current

V(AUXPWR) ≤ V(SHORT)

T(SHTDWN)

Thermal trip

V(SHORT)

mV

121

2.3

3

2

2.1

100

5

10

%V

(OREG)

11

Thermal hysteresis

10

Thermal regulation threshold (3)

Charge current begins to reduce

T(32S)

Time constant for the 32 second

timer

32 Second mode

6

117

V

A

V

mV

15

mA

165

T(CF)

(3)

6.7

140

Cycle-by-cycle current limit for

charge

I(LIMIT)

6.5

°C

120

12

32

s

Verified by design

Submit Documentation Feedback

Copyright © 2008–2010, Texas Instruments Incorporated

Product Folder Link(s): bq24150 bq24151

�Not Recommended For New Designs

www.ti.com

bq24150

bq24151

SLUS824A – JUNE 2008 – REVISED JANUARY 2010

TYPICAL APPLICATION CIRCUITS

VBUS = 5 V, I(IN_LIMIT) = 500 mA, I(CHARGE) = 750 mA, VBAT = 3.5 V to 4.44 V (adjustable), Safety Timer = 32

minutes or 32 seconds.

LO 1.0 mH

V BUS

VBUS

C IN

bq24150 /1

C IN 4.7 mF

68 mW

C BOOT

U1

1 mF

R SNS

SW

V BAT

CO

10 mF

10 nF

PACK +

BOOT

PMID

CCSIN

PGND

VAUX

+

0.1 mF

CSIN

10 kW

10 kW 10 kW 10 kW

I

2C BUS

SDA

STAT

OTG

PACK -

CSOUT

SCL

SCL

SDA

STAT

AUXPWR

VREF

OTG

CAUXPWR

C VREF

1 mF

10 kW

1 mF

HOST

Figure 1. I2C Controlled 1-Cell Charger Application Circuit

VBUS = 5 V, I(IN_LIMIT) = 500 mA, VOUT = 3.5 V to 4.44V (adjustable), Safety Timer = 32 minutes or 32 seconds.

LO 1.0 mH

VBUS

VBUS

CIN

bq24150/1

CIN 4.7 mF

PMID

10 kW

SCL

SDA

STAT

2

10 kW 10 kW 10 kW I C BUS

OTG

VOUT

CO

10 mF

BOOT

CCSIN 0.1 mF

VSYS

CSIN

SCL

SDA

STAT

OTG

10 kW

HostControlled

Switch

10nF

PGND

VAUX

68 mW

CBOOT

U1

1 mF

RSNS

SW

PACK +

+

CSOUT

AUXPWR

VREF

CAUXPWR

C VREF

1 mF

CCSOUT

0.1 mF

PACK -

1 mF

HOST

Figure 2. I2C Controlled 1-Cell Pre-Regulator Application

Submit Documentation Feedback

Copyright © 2008–2010, Texas Instruments Incorporated

Product Folder Link(s): bq24150 bq24151

7

�Not Recommended For New Designs

bq24150

bq24151

SLUS824A – JUNE 2008 – REVISED JANUARY 2010

www.ti.com

TYPICAL CHARACTERISTICS

Using circuit shown in Figure 1, TA = 25°C, unless otherwise specified.

ADAPTER INSERTION

BATTERY INSERTION/REMOVAL

VBAT

2 V/div

VBUS

2 V/div

Vbus =5 V, Iin_limit = 500 mA,

32S Mode

VSW

5 V/div

VSW

5 V/div

Vbus = 0–5 V, Vbat = 3.5 V Charge mode

IBAT

0.5 A/div

IBAT

0.5 A/div

1S/div

500 mS/div

Figure 3.

Figure 4.

PWM CHARGING WAVEFORMS

POOR SOURCE DETECTION

VBUS

2 V/div

VSW

2 V/div

VSW

5 V/div

IL

0.5 A/div

Vbus = 5 V, Vbat = 2.6 V, Voreg = 4.2 V, Ichg = 1250 mA

IBUS

0.1 A/div

Vbus = 5 V @ 10 mA, Iin_limit = 100 mA,

Vbat = 3.2 V, Ichg = 550 mA

2 mS/div

100 nS/div

Figure 5.

Figure 6.

BATTERY DETECTION AT POWER UP

CYCLE BY CYCLE CURRENT LIMIT IN CHARGE MODE

VBUS

5 V/div

VIN = 0-5 V, No Battery,

COUT = 100 mF, RLOAD = 5 kW

VSW

2 V/div

VBAT

1 V/div

IL

0.5 A/div

OTG

5 V/div

Vbus = 5 V, Vbat = 3.6 V Charge mode

operation

IBAT

50 mA/div

2 mS/div

500 mS/div

Figure 7.

8

Figure 8.

Submit Documentation Feedback

Copyright © 2008–2010, Texas Instruments Incorporated

Product Folder Link(s): bq24150 bq24151

�Not Recommended For New Designs

www.ti.com

bq24150

bq24151

SLUS824A – JUNE 2008 – REVISED JANUARY 2010

TYPICAL CHARACTERISTICS (continued)

INPUT CURRENT CONTROL

CHARGER EFFICIENCY

92

Vbus = 5 V, Iin_limit = 100/500 mA,

(OTG Control, 32 Minute Mode),

VBUS = 5 V

Vbat = 4 V

2

Iin_limit = 100 mA (I C Control, 32 Second Mode)

90

Vbat = 3.6 V

OTG

5 V/div

32 Minute

Mode

32 Second

Mode

IBUS

0.2 A/div

Efficiency - %

88

86

84

Vbat = 3 V

82

0.5 S/div

80

0

100 200 300 400 500 600 700 800 900 10001100 1200 1300

Charge Current - mA

Figure 9.

Figure 10.

BOOST WAVEFORM (PWM MODE)

BOOST WAVEFORM (PFM MODE)

VBUS 100 mV/div, 5.06 V Offset

VBUS 10 mV/div, 5.08 V Offset

VBAT 10 mV/div, 3.52 V Offset

VBAT 100 mV/div, 3.5 V Offset

VSW

2 V/div

VSW

2 V/div

IL

0.2 A/div

IL

0.2 A/div

VBAT = 3.5 V, VBUS = 5.06 V, IBUS = 42 mA

VBAT = 3.5 V, VBUS = 5.07 V, IBUS = 215 mA

5 mS/div

100 nS/div

Figure 11.

Figure 12.

VBUS OVERLOAD WAVEFORMS (BOOST MODE)

VBUS

2 V/div

VBAT = 3.5 V, VBUS = 5.05 V, IBUS = 42 mA

LOAD STEP UP RESPONSE (BOOST MODE)

VBUS

100 mV/div,

5.06 V Offset

VBAT = 3.85 V, VBUS = 5.07 V, IBUS = 0-215 mA

VPMID

200 mV/div,

5.02 V Offset

VBAT

0.2 V/div,

3.8 V Offset

VSW

5 V/div

VSW

5 V/div

IBUS

0.2 A/div

IBAT

0.1 A/div

5 mS/div

100 mS/div

Figure 13.

Figure 14.

Submit Documentation Feedback

Copyright © 2008–2010, Texas Instruments Incorporated

Product Folder Link(s): bq24150 bq24151

9

�Not Recommended For New Designs

bq24150

bq24151

SLUS824A – JUNE 2008 – REVISED JANUARY 2010

www.ti.com

TYPICAL CHARACTERISTICS (continued)

LOAD STEP DOWN RESPONSE (BOOST MODE)

CYCLE BY CYCLE CURRENT LIMITING IN BOOST MODE

VBUS

100 mV/div,

5.06 V Offset

VBAT

0.2 A/div,

3.8 V Offset

Vbat = 3.6 V, Vbus = 4.11 V, Boost mode

overload operation

VBAT = 3.85 V, VBUS = 5.07 V, IBUS = 215 mA-0

VSW

2 V/div

VSW

5 V/div

IL

0.5 A/div

IBAT

0.1 A/div

100 mS/div

200 nS/div

Figure 15.

Figure 16.

BOOST TO CHARGE MODE TRANSITION (OTG CONTROL)

BOOST EFFICIENCY

95

VBUS

0.5 V/div,

4.5 V Offset

VBAT = 4 V

VBAT = 3.6 V

90

OTG

2 V/div

Efficiency - %

Vbus = 4.5 V, (Charge Mode)/5.1 V (Boost Mode),

Iin_limit = 500 mA, Vbat = 3.4 V, 32S Mode.

VSW

5 V/div

IL

0.5 A/div

85

VBAT = 2.5 V

80

75

0.5 mS/div

70

50

0

100

150

200

Load Current at VBUS - mA

Figure 17.

Figure 18.

LINE REGULATION FOR BOOST

LOAD REGULATION FOR BOOST

5.1

5.1

IBUS = 100 mA

5.09

5.09

IBUS = 200 mA

5.08

5.08

VBAT = 3.6 V

5.07

5.06

5.06

VBUS - V

VBUS - V

5.07

5.05

5.04

VBAT = 4 V

5.05

5.04

IBUS = 50 mA

5.03

5.03

5.02

5.02

5.01

VBAT = 2.5 V

5.01

5

4.99

2.5

5

2.7

2.9

3.1

3.3

3.5

VBAT - V

3.7

3.9

4.1

0

Figure 19.

10

50

100

150

Load Current at VBUS - mA

200

Figure 20.

Submit Documentation Feedback

Copyright © 2008–2010, Texas Instruments Incorporated

Product Folder Link(s): bq24150 bq24151

�Not Recommended For New Designs

www.ti.com

bq24150

bq24151

SLUS824A – JUNE 2008 – REVISED JANUARY 2010

FUNCTIONAL BLOCK DIAGRAM (Charge Mode)

PMID

bq24150/1

PMID

PMID

VPMID

NMOS

VBUS

NMOS

SW

SW

SW

VBUS

VBUS

Q2

Q1

VREF1

OSC

Charge

Pump

-

PWM

Controller

CBC

Current

Limiting

Q3

ILIMIT

-

TCF

+

TJ

-

VBUS

+

VOUT

+

+

IIN_LIMIT

NMOS

-

+

-

VBUS UVLO

VUVLO

-

VBUS

+

Poor Input

VBUS

+

VBUS OVP

VOVP_IN

-

CSOUT

VOREG

VCSIN

CSIN

IOCHARGE

PWM_CHG

VREF

REFERNCES

& BIAS

VREF

BOOT

VIN(MIN)

TJ

+

+

VOVP

-

VOREG-VRCH

VOUT

PGND

PGND

VOUT

VCSIN

ITERM

CHARGE CONTROL

,

TIMER and DISPLAY

LOGIC

VBAT

VREF

ISHORT

AUXPWR

VOUT

VBUS

Thermal

Shutdown

-

TSHTDWN

VBAT

VPMID

+

+

-

*

Battery OVP

*

LINEAR _CHG

Sleep

STAT

* Recharge

OTG

Termination

-

+

*

VBAT

+

-

*

VSHORT

-

(I2 C Control)

Decoder

DAC

PGND

SCL

SDA

PWM Charge

Mode

* Signal Deglitched

Figure 21. Function Block Diagram of bq24150/1 in Charge Mode

Submit Documentation Feedback

Copyright © 2008–2010, Texas Instruments Incorporated

Product Folder Link(s): bq24150 bq24151

11

�Not Recommended For New Designs

bq24150

bq24151

SLUS824A – JUNE 2008 – REVISED JANUARY 2010

www.ti.com

FUNCTIONAL BLOCK DIAGRAM (Boost Mode)

PMID

bq24150/1

PMID

VPMID

PMID

NMOS

VBUS

NMOS

SW

SW

SW

VBUS

VBUS

Q2

Q1

VREF1

OSC

Charge

Pump

PWM

Controller

CBC

Current

Limiting

Q3

PFM Mode

VBUS_FB

-

IBO

+

+

+

IBLIMIT

VREF

PWM_BOOST

+

VBUSOVP

-

TJ

+

REFERNCES

& BIAS

VREF

BOOT

VBUS OVP

VREF1

VPMID

Thermal

Shutdown

-

TSHTDWN

CSOUT

CSIN

75mA

VBUS_FB

VBUS

NMOS

VBAT

AUXPWR

PGND

PGND

VOUT

+

VBATMAX

-

VBAT

+

VBATMIN

-

*

Battery OVP

*

CHARGE CONTROL,

TIMER and DISPLAY

LOGIC

STAT

Low Battery

* Signal Deglitched

PGND

OTG

(I2C Control)

Decoder

DAC

SCL

SDA

Figure 22. Function Block Diagram of bq24150/1 in Boost Mode

12

Submit Documentation Feedback

Copyright © 2008–2010, Texas Instruments Incorporated

Product Folder Link(s): bq24150 bq24151

�Not Recommended For New Designs

www.ti.com

bq24150

bq24151

SLUS824A – JUNE 2008 – REVISED JANUARY 2010

OPERATIONAL FLOW CHART

VAUXPWRVUVLO

POR

Load I2C Registers

with Default Value

High Impedance Modeor Host

Controlled Operation Mode

No

Yes

Reset and Start

32-Minute Timer

Disable Charge

/CE=LOW

Charge Configure

Mode

/CE=HIGH

Any Charge State

Disable Charge

Wait Mode

Delay TINT

Indicate Power

not Good

Yes

No

Enable ISHORT

Yes

VAUXPWR