Product

Folder

Sample &

Buy

Support &

Community

Tools &

Software

Technical

Documents

Reference

Design

CDCE62005

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

CDCE62005 3:5 Clock Generator, Jitter Cleaner with Integrated Dual VCOs

1 Features

3 Description

•

The CDCE62005 is a high performance clock

generator and distributor featuring low output jitter, a

high degree of configurability via a SPI interface, and

programmable start up modes determined by on-chip

EEPROM. Specifically tailored for clocking data

converters and high-speed digital signals, the

CDCE62005 achieves jitter performance well under 1

ps RMS (10 kHz to 20 MHz integration bandwidth).

1

•

•

•

•

Superior Performance:

– Low Noise Clock Generator: 550 fs rms typical

(10 kHz to 20 MHz Integration Bandwidth),

FC = 100 MHz

– Low Noise Jitter Cleaner: 2.6 ps rms typical

(10 kHz to 20 MHz Integration Bandwidth),

FC = 100 MHz

Flexible Frequency Planning:

– 5 Fully Configurable Outputs: LVPECL, LVDS,

LVCMOS and Special High Swing Output

Modes

– Unique Dual-VCO Architecture Supports a

Wide Tuning Range: 1.750 GHz to 2.356 GHz

– Output Frequency Ranges from 4.25 MHz to

1.175 GHz in Synthesizer Mode

– Output Frequency up to 1.5 GHz in Fan-Out

Mode

– Independent Coarse Skew Control on all

Outputs

High Flexibility:

– Integrated EEPROM Determines Device

Configuration at Power-up

– Smart Input Multiplexer Automatically Switches

Between One of Three Reference Inputs

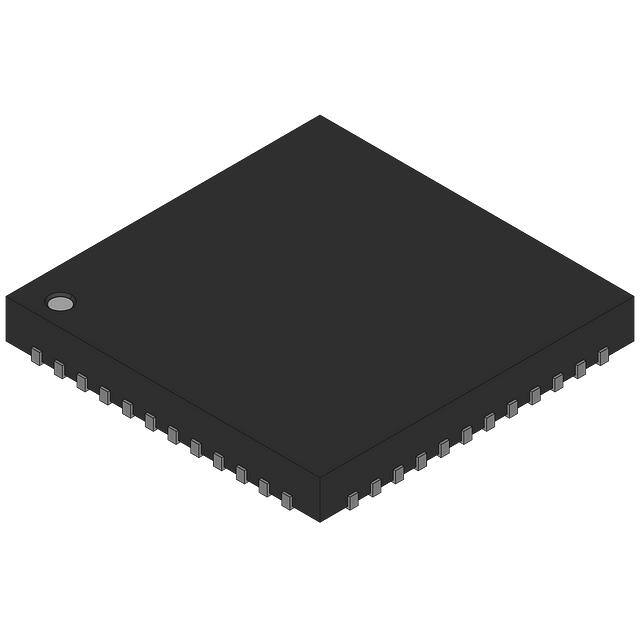

7-mm × 7-mm 48-Pin VQFN Package (RGZ)

–40°C to +85°C Temperature Range

2 Applications

•

•

•

•

•

Wireless Infrastructure

Switches and Routers

Medical Electronics

Military and Aerospace

Industrial

The CDCE62005 incorporates a synthesizer block

with partially integrated loop filter, a clock distribution

block including programmable output formats, and an

input block featuring an innovative smart multiplexer.

The clock distribution block includes five individually

programmable outputs that can be configured to

provide different combinations of output formats

(LVPECL, LVDS, LVCMOS). Each output can also be

programmed to a unique output frequency (up to 1.5

GHz) and skew relationship via a programmable

delay block (note that frequency range depends on

operational mode and output format selected). If all

outputs are configured in single-ended mode (for

example, LVCMOS), the CDCE62005 supports up to

ten outputs. Each output can select one of four clock

sources to condition and distribute including any of

the three clock inputs or the output of the frequency

synthesizer. The input block includes two universal

differential inputs which support frequencies in the

range of 40 kHz to 500 MHz and an auxiliary input

that can be configured to connect to an external

crystal via an on chip oscillator block.

The smart input multiplexer has two modes of

operation, manual and automatic. In manual mode,

the user selects the synthesizer reference via the SPI

interface. In automatic mode, the input multiplexer will

automatically select between the highest priority input

clock available.

Device Information(1)

PART NUMBER

CDCE62005

PACKAGE

VQFN (48)

BODY SIZE (NOM)

7.00 mm × 7.00 mm

(1) For all available packages, see the orderable addendum at

the end of the datasheet.

Application Example

Data

DSP

SerDes

Cleaned Clock

Recovered Clock

DSP Clock

CDCE62005

ADC Clock

ADC Clock

DAC Clock

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�CDCE62005

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

www.ti.com

Table of Contents

1

2

3

4

5

6

Features ..................................................................

Applications ...........................................................

Description .............................................................

Revision History.....................................................

Pin Configuration and Functions .........................

Specifications.........................................................

6.1

6.2

6.3

6.4

6.5

6.6

6.7

7

8

1

1

1

2

4

6

Absolute Maximum Ratings ...................................... 6

ESD Ratings.............................................................. 6

Thermal Information .................................................. 6

Electrical Characteristics........................................... 7

Timing Requirements .............................................. 11

SPI Bus Timing Characteristics .............................. 11

Typical Characteristics ............................................ 12

Parameter Measurement Information ................ 13

Detailed Description ............................................ 14

8.1 Overview ................................................................. 14

8.2 Functional Block Diagrams ..................................... 14

8.3

8.4

8.5

8.6

9

Feature Description.................................................

Device Functional Modes........................................

Programming...........................................................

Register Maps .........................................................

20

52

55

61

Application and Implementation ........................ 70

9.1 Application Information............................................ 70

9.2 Typical Application .................................................. 70

10 Power Supply Recommendations ..................... 74

11 Layout................................................................... 76

11.1 Layout Guidelines ................................................. 76

11.2 Layout Example .................................................... 76

12 Device and Documentation Support ................. 77

12.1

12.2

12.3

12.4

Trademarks ...........................................................

Documentation Support ........................................

Electrostatic Discharge Caution ............................

Glossary ................................................................

77

77

77

77

13 Mechanical, Packaging, and Orderable

Information ........................................................... 77

4 Revision History

Changes from Revision F (January 2015) to Revision G

•

Page

Removed minimum and maximum values and added typical value to on-chip load capacitance in Electrical

Characteristics ....................................................................................................................................................................... 7

Changes from Revision E (July 2014) to Revision F

Page

•

Added Low Noise Clock Generator: 550 fs rms typical (10 kHz to 20 MHz Integration Bandwidth), FC = 100 MHz in

Features section ..................................................................................................................................................................... 1

•

Added Low Noise Jitter Cleaner: 2.6 ps rms typical (10 kHz to 20 MHz Integration Bandwidth), FC = 100 MHz in

Features section ..................................................................................................................................................................... 1

Changes from Revision D (April 2011) to Revision E

Page

•

Changed Added, updated, or revised the following sections: Features; Application and Implementation; Power

Supply Recommendations ; Layout ; Device and Documentation Support ; Mechanical, Packaging, and Ordering

Information ............................................................................................................................................................................. 1

•

Changed Bit Name from LOCKW(3) to LOCKW(2).............................................................................................................. 48

•

Changed Bit Name from LOCKW(2) to LOCKW(1).............................................................................................................. 48

•

Changed Bit Name from LOCKW(1) to LOCKW(0).............................................................................................................. 48

•

Changed REGISTER.BIT from 5.26 to 5.25, from 5.25 to 5.24, from 5.24 to 5.23, from 5.23 to 5.22. .............................. 48

Changes from Revision C (February, 2010) to Revision D

Page

•

Changed 0 to 1 in SPI_LE description ................................................................................................................................... 4

•

Changed last sentence in Description column of Pin 46 and Pin 2 ....................................................................................... 5

•

Changed Outputs to Output 1 in PLVCMOS Test Conditions, changed PD to Power_Down in LVCMOS INPUT MODE,

and deleted (LVCMOS signals) from Input capacitance in Electrical Characteristics ............................................................ 7

•

Changed TIMING REQUIREMENTS table........................................................................................................................... 11

•

Added 1 row to TIMING Requirements table - Input Clock Slew Rate... ............................................................................. 11

2

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

�CDCE62005

www.ti.com

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

•

Added SPI CONTROL INTERFACE TIMING section .......................................................................................................... 11

•

Changed Functional Block Diagrams .................................................................................................................................. 14

•

Changed pin names in Figure 11 ......................................................................................................................................... 15

•

Changed Feedback Divider value in Figure 15 .................................................................................................................... 18

•

Changed are 25°C to (nominal conditions) in Table 3 ......................................................................................................... 21

•

Changed Poer Down state SPI Port status from ON to OFF in Table 4 .............................................................................. 22

•

Changed Figure 18 .............................................................................................................................................................. 23

•

Changed Table 5 ................................................................................................................................................................. 24

•

Added note to Table 7 .......................................................................................................................................................... 25

•

Changed AUXSEL from X to 0 in Table 7 ............................................................................................................................ 25

•

Added note to Table 21 ........................................................................................................................................................ 39

•

Added new sections Crystal Input Interface, VCO Calibration, and Startup Time Estimation. ............................................ 48

•

Changed Serial Peripheral Interface (SPI) section............................................................................................................... 55

•

Changed Table 6 to Table 38 in Writing to EEPROM section ............................................................................................. 60

•

Changed RAM bit 1 and RAM bit 2 in Table 43 ................................................................................................................... 64

•

Added note and changed Smart MUX description in Table 45 ............................................................................................ 66

•

Changed 1 to 0 in rows PRINVBB and SECINVB6 in the description column..................................................................... 66

•

Changed RAM bit 22 from 0 to 1 and changed RAM bit 24 from 0 to 1 in Table 47 ........................................................... 68

•

Changed Table 48 ............................................................................................................................................................... 69

Changes from Revision B (July, 2009) to Revision C

•

Page

Deleted LVCMOS INPUT MODE (AUX_IN) section from Electrical Characteristics table..................................................... 7

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

3

�CDCE62005

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

www.ti.com

5 Pin Configuration and Functions

SPI_LE

31

VCC_OUT

32

U0P

REF_SEL

33

U0N

VCC_OUT

34

TESTOUTA

TEST_MODE

35

VCC_OUT

VCC_VCO

36

VCC_VCO

GND_VCO

RGZ Package

48-Pin VQFN

Top View

30

29

28

27

26

25

PLL_LOCK

37

24

SPI_CLK

REG_CAP2

38

23

SPI_MOSI

VCC2_PLL

39

22

SPI_MISO

EXT_LFP

40

21

VCC_OUT

EXT_LFN

41

20

U1N

VCC2_PLL

42

19

U1P

AUX IN

43

18

VCC_OUT

VCC_AUXIN

44

17

U2N

PRI_REF+

45

16

U2P

PRI_REF-

46

15

VCC_AUXOUT

VCC_IN_PRI

47

14

SYNC

VBB

48

13

AUX OUT

9

10

11

12

Power_Down

8

VCC_OUT

REG_CAP1

7

U3N

SEC_REF+

6

U3P

SEC_REF-

5

VCC_OUT

4

U4N

3

U4P

2

VCC1_PLL

1

VCC_IN_SEC

CDCE62005

(Top View)

Pin Functions (1)

PIN

NAME

VCC_OUT

NO,

8, 11, 18, 21,

26, 29, 32

TYPE

Power

DESCRIPTION

3.3-V Supply for the Output Buffers and Output Dividers

VCC_AUXOUT

15

Power

VCC1_PLL

5

A. Power

3.3-V PLL Supply Voltage for the PLL circuitry. (Filter Required)

VCC2_PLL

39, 42

A. Power

3.3-V PLL Supply Voltage for the PLL circuitry. (Filter Required)

VCC_VCO

34, 35

A. Power

3.3-V VCO Input Buffer and Circuitry Supply Voltage. (Filter Required)

VCC_IN_PRI

47

A. Power

3.3-V References Input Buffer and Circuitry Supply Voltage.

VCC_IN_SEC

1

A. Power

3.3-V References Input Buffer and Circuitry Supply Voltage.

VCC_AUXIN

44

A. Power

3.3-V Crystal Oscillator Input Circuitry.

GND_VCO

GND

SPI_MISO

36

Ground

Ground that connects to VCO Ground. (VCO_GND is shorted to GND)

PAD

Ground

Ground is on Thermal PAD. See Layout recommendation

22

O

3-state LVCMOS Output that is enabled when SPI_LE is asserted low. It is the serial Data

Output to the SPI bus interface

I

LVCMOS input, control Latch Enable for Serial Programmable Interface (SPI), with

Hysteresis in SPI Mode. The input has an internal 150-kΩ pull-up resistor if left

unconnected it will default to logic level 1. The SPI_LE status also impacts whether the

device loads the EEPROM into the device registers at power up. SPI_LE has to be logic 1

before the Power_Down pin toggles low-to-high in order for the EEPROM to load properly.

SPI_LE

25

(1)

4

3.3-V to Power the AUX_OUT circuitry

Note: The internal memory (EEPROM and RAM) are sourced from various power pins. All VCC connections must be powered for proper

functionality of the device.

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

�CDCE62005

www.ti.com

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

Pin Functions(1) (continued)

PIN

TYPE

DESCRIPTION

24

I

LVCMOS input, serial Control Clock Input for the SPI bus interface, with Hysteresis. The

input has an internal 150-kΩ pull-up resistor if left unconnected it will default to logic level

1.

23

I

LVCMOS input, Master Out Slave In as a serial Control Data Input to CDCE62005 for the

SPI bus interface. The input has an internal 150-kΩ pull-up resistor if left unconnected it

will default to logic level 1.

33

I

This pin should be tied high or left unconnected.

I

If Auto Reference Select Mode is OFF this Pin acts as External Input Reference Select

Pin;

The REF_SEL signal selects one of the two input clocks:

REF_SEL [1]: PRI_REF is selected; REF_SEL [0]: SEC_REF is selected;

The input has an internal 150-kΩ pull-up resistor if left unconnected it will default to logic

level 1. If Auto Reference Select Mode in ON (for example, EECLKSEL bit -- Register 5

Bit 5 -- is 1 ), then REF_SEL pin input setting is ignored.

12

I

Active Low. Power down mode can be activated via this pin. See Table 4 for more details.

The input has an internal 150-kΩ pull-up resistor if left unconnected it will default to logic

level 1. SPI_LE has to be HIGH in order for the rising edge of Power_Down signal to load

the EEPROM.

14

I

Active Low. Sync mode can be activated via this pin. See Table 4 for more details. The

input has an internal 150-kΩ, pull-up resistor if left unconnected it will default to logic level

1.

43

I

Auxiliary Input is a single ended input including an on-board oscillator circuit so that a

crystal may be connected.

13

O

Auxiliary Output LVCMOS level that can be programmed via SPI interface to be driven by

Output 2 or Output 3.

45

I

Universal Input Buffer (LVPECL, LVDS, LVCMOS) positive input for the Primary

Reference Clock.

46

I

Universal Input Buffer (LVPECL, LVDS) negative input for the Primary Reference Clock.

In case of LVCMOS input on PRI_REF+, connect this pin through 1-kΩ resistor to GND.

3

I

Universal Input Buffer (LVPECL, LVDS, LVCMOS) positive input for the Secondary

Reference Clock.

2

I

Universal Input Buffer (LVPECL, LVDS,) negative input for the Secondary Reference

Clock. In case of LVCMOS input on SEC_REF+, connect this pin through 1-kΩ resistor to

GND.

TESTOUTA

30

Analog

Reserved. Pull Down to GND Via a 1-kΩ Resistor.

REG_CAP1

4

Analog

Capacitor for the internal Regulator. Connect to a 10-µF Capacitor (X5R or X7R)

REG_CAP2

38

Analog

Capacitor for the internal Regulator. Connect to a 10-µF Capacitor (X5R or X7R)

VBB

48

Analog

Capacitor for the internal termination Voltage. Connect to a 1-µF Capacitor (X5R or X7R)

EXT_LFP

40

Analog

External Loop Filter Input Positive

EXT_LFN

41

Analog

External Loop Filter Input Negative.

PLL_LOCK

37

O

Output that indicates PLL Lock Status. See Figure 31.

O

The Main outputs of CDCE62005 are user definable and can be any combination of up to

5 LVPECL outputs, 5 LVDS outputs or up to 10 LVCMOS outputs. The outputs are

selectable via SPI interface. The power-up setting is EEPROM configurable.

NAME

NO,

SPI_CLK

SPI_MOSI

TEST_MODE

REF_SEL

31

Power_Down

SYNC

AUX IN

AUX OUT

PRI_REF+

PRI_REF–

SEC_REF+

SEC_REF–

U0P:U0N

U1P:U1N

U2P:U2N

U3P:U3N

U4P:U4N

27, 28

19, 20

16,17

9, 10

6, 7

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

5

�CDCE62005

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

www.ti.com

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

MIN

MAX

UNIT

–0.5

4.6

V

–0.5

VCC + 0.5

V

–0.5

VCC + 0.5

V

Input Current (VI < 0, VI > VCC)

±20

mA

Supply voltage range (2)

VCC

(3)

VI

Input voltage range

VO

Output voltage range (3)

Output current for LVPECL/LVCMOS Outputs (0 < VO < VCC)

±50

mA

TJ

Junction temperature

125

°C

Tstg

Storage temperature

150

°C

(1)

(2)

(3)

–65

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute–maximum–rated conditions for extended periods may affect device reliability.

All supply voltages have to be supplied simultaneously.

The input and output negative voltage ratings may be exceeded if the input and output clamp–current ratings are observed.

6.2 ESD Ratings

MIN

V(ESD)

(1)

(2)

Electrostatic discharge

MAX

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all

pins (1)

2000

Charged device model (CDM), per JEDEC specification

JESD22-C101, all pins (2)

750

UNIT

V

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.3 Thermal Information (1) (2)

THERMAL METRIC (3)

RGZ

48 PINS

UNIT

28.9 (4)

RθJA

Junction-to-ambient thermal resistance

20.4 (5)

27.3 (6)

°C/W

20.3 (7)

RθJC(top)

Junction-to-case (top) thermal resistance

12.9

°C/W

RθJB

Junction-to-board thermal resistance

4.0

°C/W

ψJT

Junction-to-top characterization parameter

0.2

°C/W

ψJB

Junction-to-board characterization parameter

4.0

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

0.9

°C/W

2 (4)

θJP

2 (5)

Junction-to-pad (8)

2 (6)

°C/W

2 (7)

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

6

The package thermal impedance is calculated in accordance with JESD 51 and JEDEC2S2P (high-k board).

Connected to GND with 36 thermal vias (0,3 mm diameter).

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report, SPRA953.

JEDEC Compliant Board (6X6 VIAs on PAD), Ariflow = 0 LFM

JEDEC Compliant Board (6X6 VIAs on PAD) , Airflow = 100 LFM

Recommended Layout (7X7 VIAs on PAD), Airflow = 0 LFM

Recommended Layout (7X7 VIAs on PAD), Airflow = 100 LFM

θJP (Junction – Pad) is used for the QFN Package, because the main heat flow is from the Junction to the GND-Pad of the QFN.

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

�CDCE62005

www.ti.com

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

6.4 Electrical Characteristics

recommended operating conditions for the CDCE62005 device for under the specified Industrial temperature range of –40°C

to 85°C

PARAMETER

TEST CONDITIONS

MIN

TYP (1)

MAX

3

3.3

3.6

3

3.3

3.6

UNIT

POWER SUPPLY

VCC

Supply voltage

VCC_PLL,

VCC_IN,

Analog supply voltage

VCC_VCO,

VCCA

PLVPECL

REF at 30.72,MHz, Outputs are

LVPECL

PLVDS

REF at 30.72 MHz, Outputs are

LVDS

PLVCMOS

REF at 30.72 MHz, Outputs are

LVCMOS

POFF

REF at 30.72 MHz

PPD

V

Output 1 = 491.52 MHz

Output 2 = 245.76 MHz

Output 3 = 122.88 MHz

Output 4 = 61.44 MHz

Output 5 = 30.72 MHz

In case of LVCMOS

Output1 = 245.76 MHz

1.9

W

1.65

W

1.8

W

Dividers are disabled. Outputs are

disabled.

0.75

W

Device is powered down

20

mW

DIFFERENTIAL INPUT MODE (PRI_REF, SEC_REF)

VIN

Differential input amplitude (VIN –

V/IN)

0.1

1.3

V

VIC

Common-mode input voltage

1.0

VCC–0.3

V

IIH

Differential input current high (no

internal termination)

VI = VCC, VCC = 3.6 V

20

μA

IIL

Differential input current low (no

internal termination)

VI = 0 V, VCC = 3.6 V

20

μA

–20

Input Capacitance on PRI_REF,

SEC_REF

3

pF

CRYSTAL INPUT SPECIFICATIONS

On-chip load capacitance

10

Equivalent series resistance (ESR)

pF

50

Ω

LVCMOS INPUT MODE (SPI_CLK, SPI_MOSI, SPI_LE, Power_Down, SYNC, REF_SEL, PRI_REF, SEC_REF )

Low-level input voltage LVCMOS,

0

0.3 x VCC

V

High-level input voltage LVCMOS

0.7 x VCC

VCC

V

VIK

LVCMOS input clamp voltage

VCC = 3 V, II = –18 mA

IIH

LVCMOS input current

VI = VCC, VCC = 3.6 V

IIL

LVCMOS input (Except PRI_REF

and SEC_REF)

VI = 0 V, VCC = 3.6 V

IIL

LVCMOS input (PRI_REF and

SEC_REF)

VI = 0 V, VCC = 3.6 V

CI

Input capacitance

VI = 0 V or VCC

–1.2

V

20

μA

–10

–40

μA

–10

10

μA

3

pF

SPI OUTPUT (MISO) / PLL_LOCK OUTPUT

IOH

High-level output current

VCC = 3.3 V,

VO = 1.65 V

–30

mA

IOL

Low-level output current

VCC = 3.3 V,

VO = 1.65 V

33

mA

VOH

High-level output voltage for

LVCMOS outputs

VCC = 3 V,

IOH = −100 μA

VOL

Low-level output voltage for

LVCMOS outputs

VCC = 3 V,

IOL = 100 μA

CO

Output capacitance on MISO

VCC = 3.3 V; VO = 0 V or VCC (1)

3

3-state output current

VO = VCC

VO = 0 V

5

IOZH

IOZL

(1)

VCC–0.5

V

0.3

–5

V

pF

μA

All typical values are at VCC = 3.3 V, temperature = 25°C

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

7

�CDCE62005

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

www.ti.com

Electrical Characteristics (continued)

recommended operating conditions for the CDCE62005 device for under the specified Industrial temperature range of –40°C

to 85°C

PARAMETER

TEST CONDITIONS

MIN

TYP (1)

100

1000

MAX

UNIT

EEPROM

EEcy

Programming cycle of EEPROM

EEret

Data retention

Cycles

10

Years

VBB

VBB

Termination voltage for reference

inputs.

IBB = –0.2 mA, Depending on the

setting.

0.9

1.9

V

INPUT BUFFERS INTERNAL TERMINATION RESISTORS (PRI_REF and SEC_REF)

Termination resistance

Single ended

Ω

50

PHASE DETECTOR

fCPmax

Charge pump frequency

0.04

40

MHz

0

250

MHz

0.3

V

LVCMOS OUTPUT / AUXILIARY OUTPUT (1)

fclk

Output frequency (see Figure 7)

Load = 5 pF to GND

VOH

High-level output voltage for

LVCMOS outputs

VCC = min to max

IOH = –100 μA

VOL

Low-level output voltage for

LVCMOS outputs

VCC = min to max

IOL =100 µA

IOH

High-level output current

VCC = 3.3 V

VO = 1.65 V

–30

mA

IOL

Low-level output current

VCC = 3.3 V

VO = 1.65 V

33

mA

tpho

Reference (PRI_REF or SEC_REF) Outputs are set to 122.88 MHz,

to Output Phase offset

Reference at 30.72 MHz

0.35

ns

tpd(LH)/

tpd(HL)

Propagation delay from PRI_REF

or SEC_REF to Outputs

Crosspoint to VCC/2, Bypass Mode

4

ns

tsk(o)

Skew, output to output For Y0 to Y4

All Outputs set at 200 MHz, Reference

= 200 MHz

75

ps

CO

Output capacitance on Y0 to Y4

VCC = 3.3 V; VO = 0 V or VCC

5

pF

VO = VCC

5

μA

VO = 0 V

–5

IOZH

IOZL

IOPDH

IOPDL

3-State LVCMOS output current

Power Down output current

VO = VCC

VO = 0 V

Duty cycle LVCMOS

tslew-rate

8

VCC –0.5

45%

Output rise/fall slew rate

3.6

Submit Documentation Feedback

μA

25

μA

5

μA

55%

5.2

V/ns

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

�CDCE62005

www.ti.com

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

Electrical Characteristics (continued)

recommended operating conditions for the CDCE62005 device for under the specified Industrial temperature range of –40°C

to 85°C

PARAMETER

TEST CONDITIONS

MIN

TYP (1)

MAX

UNIT

0

800

MHz

270

550

mV

50

mV

LVDS OUTPUT (1) (2)

fclk

Output frequency (see Figure 8)

Configuration Load

|VOD|

Differential output voltage

RL = 100 Ω

ΔVOD

LVDS VOD magnitude change

Offset Voltage

ΔVOS

40°C to 85°C

1.24

VOS magnitude change

VOUT = 0

27

mA

Short circuit Vout– to ground

VOUT = 0

27

mA

tpd(LH)/tpd( Propagation delay from PRI_REF

or SEC_REF to outputs

HL)

tsk(o)

(3)

mV

Short circuit Vout+ to ground

Reference (PRI_REF or SEC_REF) Outputs are set to 491.52 MHz

to output phase offset

Reference at 30.72 MHz

tpho

V

40

Crosspoint to Crosspoint, Bypass

Mode

Skew, output to output For Y0 to Y4 All Outputs set at 200 MHz

1.65

ns

3.1

ns

25

ps

5

pF

CO

Output capacitance on Y0 to Y4

VCC = 3.3 V; VO = 0 V or VCC

IOPDH

Power down output current

VO = VCC

25

μA

IOPDL

Power down output current

VO = 0 V

5

μA

Duty cycle

tr / tf

Rise and fall time

45%

55%

20% to 80% of VOUT(PP)

110

160

190

ps

VCC/2 to Crosspoint. Output are at the

same output frequency and use the

same output divider configuration.

0.9

1.4

1.9

ns

LVCMOS-TO-LVDS (4)

tskP_c

Output skew between LVCMOS

and LVDS outputs

LVPECL OUTPUT

fclk

Output frequency, Configuration

load (see Figure 9 and Figure 10)

0

1500

VOH

LVPECL high-level output voltage

load

VCC –1.06

VCC –0.88

V

VOL

LVPECL low-level output voltage

load

VCC–2.02

VCC–1.58

V

|VOD|

Differential output voltage

610

970

tpho

Reference to Output Phase offset

Outputs are set to 491.52 MHz,

Reference at 30.72 MHz

tpd(LH)/

tpd(HL)

Propagation delay from PRI_REF

or SEC_REF to outputs

Crosspoint to Crosspoint, Bypass

Mode

tsk(o)

Skew, output to output For Y0 to Y4 All Outputs set at 200 MHz

CO

Output capacitance on Y0 to Y4

IOPDH

IOPDL

Power Down output current

VCC = 3.3 V; VO = 0 V or VCC

tr / tf

(2)

(3)

(4)

Rise and fall time

ns

3.4

ns

25

ps

5

pF

VO = 0 V

45%

20% to 80% of VOUT(PP)

55

mV

1.47

VO = VCC

Duty Cycle

MHz

25

μA

5

μA

55%

75

135

ps

The phase of LVCMOS is lagging in reference to the phase of LVDS.

The tsk(o) specification is only valid for equal loading of all outputs.

All typical values are at VCC = 3.3 V, temperature = 25°C

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

9

�CDCE62005

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

www.ti.com

Electrical Characteristics (continued)

recommended operating conditions for the CDCE62005 device for under the specified Industrial temperature range of –40°C

to 85°C

PARAMETER

TEST CONDITIONS

MIN

TYP (1)

MAX

0.9

1.1

1.3

ns

–150

260

700

ps

UNIT

LVDS-TO-LVPECL

tskP_C

Output skew between LVDS and

LVPECL outputs

Crosspoint to Crosspoint output

dividers are configured identically.

LVCMOS-TO-LVPECL

tskP_C

Output skew between LVCMOS

and LVPECL outputs

VCC/2 to Crosspoint output dividers

are configured identically.

LVPECL HI-SWING OUTPUT

VOH

LVPECL high-level output voltage

load

VCC –1.11

VCC –0.87

V

VOL

LVPECL low-level output voltage

load

VCC –2.06

VCC –1.73

V

|VOD|

Differential output voltage

760

1160

mV

tr / tf

Rise and fall time

135

ps

10

20% to 80% of VOUT(PP)

Submit Documentation Feedback

55

75

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

�CDCE62005

www.ti.com

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

6.5 Timing Requirements

over recommended ranges of supply voltage, load and operating free air temperature (unless otherwise noted)

MIN

NOM

MAX

UNIT

PRI_REF/SEC_REF REQUIREMENTS

Maximum Clock Frequency Applied to PRI_REF and SEC_REF in fan-out mode

fmax

1500

MHz

Maximum Clock Frequency Applied to Smart Multiplexer input Divider

500

MHz

Maximum Clock Frequency Applied to Reference Divider

250

MHz

250

MHz

For Single ended Inputs ( LVCMOS) on PRI_REF and SEC_REF

Duty cycle of PRI_REF or SEC_REF at VCC / 2

40%

Input Clock Slew Rate (Differential and Single ended)

60%

1

V/ns

Power_Down, SYNC, REF_SEL REQUIREMENTS

tr/ tf

Rise and fall time of the Power_Down, SYNC, REF_SEL signal from 20% to 80% of VCC

4

ns

6.6 SPI Bus Timing Characteristics

MIN NOM

MAX

UNIT

20

MHz

fClock

Clock Frequency for the

SPI_CLK

t1

SPI_LE to SPI_CLK setup time

See Figure 1 and Figure 2

10

ns

t2

SPI_MOSI to SPI_CLK setup

time

See Figure 1 and Figure 2

10

ns

t3

SPI_MOSI to SPI_CLK hold

time

See Figure 1 and Figure 2

10

ns

t4

SPI_CLK high duration

See Figure 1 and Figure 2

25

ns

t5

SPI_CLK low duration

See Figure 1 and Figure 2

25

ns

t6

SPI_CLK to SPI_LE Hold time

See Figure 1 and Figure 2

10

ns

t7

SPI_LE Pulse Width

See Figure 1 and Figure 2

20

t8

SPI_CLK to MISO data valid

See Figure 2

10

ns

t9

SPI_LE to SPI_MISO Data Valid See Figure 2

10

ns

t1

t4

ns

t5

SPI_CLK

t2

SPI_MOSI

Bit0

t3

Bit1

Bit29

Bit30

Bit31

t7

SPI_LE

t6

Figure 1. Timing Diagram for SPI Write Command

t4

t5

SPI_CLK

t2

SPI_MOSI

Bit30

t8

t3

Bit31

SPI_MISO

Bit0 = 0

Bit1

Bit2

t7

SPI_LE

t6

t9

Figure 2. Timing Diagram for SPI Read Command

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

11

�CDCE62005

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

www.ti.com

6.7 Typical Characteristics

V

12

Figure 3. LVPECL Output Swing Vs Frequency

Figure 4. Hi Swing LVPECL Output Swing vs Frequency

Figure 5. LVDS Output Swing vs Frequency

Figure 6. LVCMOS Output Swing vs Frequency

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

�CDCE62005

www.ti.com

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

7 Parameter Measurement Information

5 pF

LVCMOS

Figure 7. LVCMOS, 5 pF

100 Ω

Oscilloscope

Figure 8. LVDS DC Termination Test

50 Ω

50 Ω

150 Ω

150 Ω

Oscilloscope

Figure 9. LVPECL AC Termination Test

Oscilloscope

50 Ω

50 Ω

Vcc-2

Figure 10. LVPECL DC Termination Test

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

13

�CDCE62005

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

www.ti.com

8 Detailed Description

8.1 Overview

The CDCE62005 comprises of four primary blocks: the interface and control block, the input block, the output

block, and the synthesizer block. In order to determine which settings are appropriate for any specific

combination of input/output frequencies, a basic understanding of these blocks is required. The interface and

control block determines the state of the CDCE62005 at power-up based on the contents of the on-chip

EEPROM. In addition to the EEPROM, the SPI port is available to configure the CDCE62005 by writing directly

to the device registers after power-up. The input block selects which of the three input ports is available for use

by the synthesizer block and buffers all clock inputs. The output block provides five separate clock channels that

are fully programmable and configurable to select and condition one of four internal clock sources. The

synthesizer block multiplies and filters the input clock selected by the input block.

NOTE

This section provides a high-level description of the features of the CDCE62005 for

purpose of understanding its capabilities. For a complete description of device registers

and I/O, please refer to Device Configuration and Register Maps.

8.2 Functional Block Diagrams

PRI_REF

Output

Divider 0

SEC_REF

U0P

U0N

/1:/2:HiZ

/1:/2:HiZ

Reference

Divider

Output

Divider 1

XTAL /

AUX IN

EXT_LFP

EXT_LFN

Output

Divider 2

Input

Divider

Feedback

Divder

PFD /

CP

Prescaler

Output

Divider 3

Output

Divider 4

REF_SEL

Power_down

SYNC

SPI_LE

SPI_CLK

SPI_MISO

SPI_MOSI

14

Interface

&

Control

U1P

U1N

U2P

U2N

U3P

U3N

U4P

U4N

EEPROM

AUX

OUT

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

�CDCE62005

www.ti.com

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

Functional Block Diagrams (continued)

8.2.1 Interface and Control Block

The CDCE62005 is a highly flexible and configurable architecture and as such contains a number of registers so

that the user may specify device operation. The contents of nine 28-bit wide registers implemented in static RAM

determine device configuration at all times. On power-up, the CDCE62005 copies the contents of the EEPROM

into the RAM and the device begins operation based on the default configuration stored in the EEPROM.

Systems that do not have a host system to communicate with the CDCE62005 use this method for device

configuration. The CDCE62005 provides the ability to lock the EEPROM; enabling the designer to implement a

fault tolerant design. After power-up, the host system may overwrite the contents of the RAM via the SPI (Serial

Peripheral Interface) port. This enables the configuration and reconfiguration of the CDCE62005 during system

operation. Finally, the device offers the ability to copy the contents of the RAM into EEPROM, if the EEPROM is

unlocked.

Static RAM (Device Registers)

Register 8

Register 7

Register 6

REF_SEL

Power_Down

SYNC

SPI_LE

SPI_CLK

SPI_MISO

SPI_MOSI

Register 5

Interface

&

Control

Device

Hardware

Register 4

Register 3

Register 2

Register 1

Register 0

EEPROM (Default Configuration)

Register 7

Register 6

Register 5

Register 4

Register 3

Register 2

Register 1

Register 0

Figure 11. CDCE62005 Interface and Control Block

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

15

�CDCE62005

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

www.ti.com

Functional Block Diagrams (continued)

8.2.2 Input Block

The Input Block includes a pair of Universal Input Buffers and an Auxiliary Input. The Input Block buffers the

incoming signals and facilitates signal routing to the Internal Clock Distribution bus and the Synthesizer Block via

the smart multiplexer (called the Smart MUX). The Internal Clock Distribution Bus connects to all output blocks

discussed in the next section. Therefore, a clock signal present on the Internal Clock Distribution bus can appear

on any or all of the device outputs. The CDCE62005 routes the PRI_REF and SEC_REF inputs directly to the

Internal Clock Distribution Bus. Additionally, it can divide these signals via the dividers present on the inputs and

output of the first stage of the Smart MUX.

PRI_REF

1500 MHz

LVPECL: 1500 MHz

LVDS: 800 MHz

LVCMOS: 250 MHz

1500 MHz

Smart MUX

Control

REF_SEL

/1:/2:HiZ

Smart

MUX1

Reference Divider

/1 - /8

Smart

MUX2

Internal Clock Distribution Bus

SEC_REF

/1:/2:HiZ

Crystal: 2 MHz - 42 MHz

XTAL/

AUX IN

Figure 12. CDCE62005 Input Block

16

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

�CDCE62005

www.ti.com

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

Functional Block Diagrams (continued)

8.2.3 Output Block

Each of the five identical output blocks incorporates an output multiplexer, a clock divider module, and a

universal output array as shown.

Internal Clock Distribution Bus

Output

MUX

Control

Sync

Pulse

Digital Phase Adjust

PRI_REF

Output Buffer Control

Enable

(7 -bits )

UxP

SEC_REF

/1,2,3,4,5Clock Divider

/1 - /8 Module 0/2- 4

SMART_MUX

LVDS

UxN

SYNTH

LVPECL

Figure 13. CDCE62005 Output Block (1 of 5)

8.2.4 Clock Divider Module 0–4

The following shows a simplified version of a Clock Divider Module (CDM). If an individual clock output channel

is not used, then the user should disable the CDM and Output Buffer for the unused channel to save device

power. Each channel includes two 7-bit registers to control the divide ratio used and the clock phase for each

output. The output divider supports divide ratios from divide by 1 (bypass the divider) to divide by 80; the divider

does not support all integer values between 1 and 80. Refer to Table 13 for a complete list of divide ratios

supported.

Enable

Sync Pulse

(internally generated)

From

Output

MUX

Digital Phase Adjust (7-bits)

Output Divider

To

Output

Buffer

(7-bits)

Figure 14. CDCE62005 Output Divider Module (1 of 5)

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

17

�CDCE62005

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

www.ti.com

Functional Block Diagrams (continued)

8.2.5 Synthesizer Block

Internal Clock Distribution Bus

SMART_MUX

1.750 GHz –

2.356 GHz

Input Divider

/1 - /256

PFD/

CP

Feedback Divider

Prescaler

/2,/3,/4,/5

/1, /2, /5, /8, /10, /16, /20

/8 - /1280

Feedback Divider

Feedback Bypass Divider

SYNTH

Internal Clock Distribution Bus

Figure 15 presents a high-level overview of the Synthesizer Block on the CDCE62005.

Figure 15. CDCE62005 Synthesizer Block

8.2.6 Computing The Output Frequency

Figure 16 shows the block diagram of the CDCE62005 in synthesizer mode highlighting the clock path for a

single output. It also identifies the following regions containing dividers comprising the complete clock path

• R: Includes the cumulative divider values of all dividers included from the Input Ports to the output of the

Smart Multiplexer (see Input Block for more details)

• O: The output divider value (see Figure 18 in Output Block for more details)

• I: The input divider value (see Synthesizer Block for more details)

• P: The prescaler divider value (see Synthesizer Block for more details)

• F: The cumulative divider value of all dividers falling within the feedback divider (see Synthesizer Block for

more details)

18

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

�CDCE62005

www.ti.com

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

Functional Block Diagrams (continued)

O

Output

Divider 0

FIN

F OUT

U0N

R

/1:/2:HiZ

/1:/2:HiZ

U0P

Reference

Divider

Output

Divider 1

EXT_LFP

EXT_LFN

Output

Divider 2

U1P

U1N

U2P

U2N

I

Input

Divider

Feedback

Divider

P

PFD /

CP

Prescaler

Output

Divider 3

U3P

U3N

F

Output

Divider 4

U4P

U4N

AUX

OUT

Figure 16. CDCE62005 Clock Path – Synthesizer Mode

With respect to Figure 16, any output frequency generated by the CDCE62005 relates to the input frequency

connected to the Synthesizer Block by Equation 1.

F

FOUT = FIN ´

R ´I´ O

(1)

Equation 1 holds true when subject to the following constraints:

1.750 Ghz < O x P x FOUT< 2.356 GHz

(2)

The comparison frequency FCOMP is:

40 kHz ≤ FCOMP < 40 MHz

(3)

where:

FCOMP =

FIN

R ´I

(4)

NOTE

This device cannot output the frequencies between 785 MHz to 875 MHz

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

19

�CDCE62005

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

www.ti.com

8.3 Feature Description

8.3.1 Phase Noise Analysis

Table 1. Device Output Phase Noise for 30.72 MHz External Reference (1)

REFERENCE

30.72 MHz

LVPECL 491.52 MHz

LVDS 491.52 MHz

10 Hz

–108

–81

100 Hz

–130

–94

1 kHz

–134

10 kHz

100 kHz

PHASE NOISE

LVCMOS 122.88 MHz

UNIT

–81

–92

dBc/Hz

–96

–108

dBc/Hz

–106

–106

–118

dBc/Hz

–152

–119

–119

–132

dBc/Hz

–156

–121

–122

–134

dBc/Hz

1 MHz

–157

–131

–131

–143

dBc/Hz

10 MHz

—

–145

–144

–150

dBc/Hz

—

–145

–144

–150

dBc/Hz

193

(10 kHz – 1 MHz)

307

315

377

fs

20 MHz

Jitter(RMS) 10k~20

MHz

(1)

Phase Noise Specifications under following configuration: VCO = 1966.08 MHz, REF = 30.72 MHz,

PFD Frequency = 30.72 MHz, Charge Pump Current = 1.5 mA Loop BW = 400 kHz at 3.3 V and 25°C

Table 2. Device Output Phase Noise for 25 MHz Crystal Reference (1)

PHASE NOISE

LVPECL 500 MHz

LVDS 250 MHz

LVCMOS 125 MHz

UNIT

10 Hz

–57

100 Hz

–90

–62

–68

dBc/Hz

–95

–102

1 kHz

dBc/Hz

–107

–113

–119

dBc/Hz

10 kHz

–115

–122

–128

dBc/Hz

100 kHz

–118

–124

–130

dBc/Hz

1 MHz

–130

–137

–143

dBc/Hz

10 MHz

–145

–147

–150

dBc/Hz

20 MHz

–145

–147

–150

dBc/Hz

Jitter(RMS) 10k~20 MHz

389

405

437

fs

(1)

20

Phase Noise Specifications under following configuration: VCO = 2000.00 MHz, AUX IN = 25.00 MHz,

PFD Frequency = 25.00 MHz, Charge Pump Current = 1.5 mA Loop BW = 400 kHz at 3.3 V and 25°C

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

�CDCE62005

www.ti.com

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

8.3.2 Output To Output Isolation

Table 3. Output to Output Isolation (1)

(1)

SPUR

UNIT

Output 2

Measured Channel

In LVPECL Signaling 15.5 MHz

–67

db

Output 2

Measured Channel

In LVPECL Signaling 93 MHz

–60

db

Output 2

Measured Channel

In LVPECL Signaling 930 MHz

–59

db

Output 0

Aggressor Channel

LVPECL 22.14 MHz

Output 1

Aggressor Channel

LVPECL 22.14 MHz

Output 3

Aggressor Channel

LVPECL 22.14 MHz

Output 4

Aggressor Channel

LVPECL 22.14 MHz

The Output to Output Isolation was tested under following settings (nominal conditions)

8.3.3 Device Control

Figure 17 provides a conceptual explanation of the CDCE62005 Device operation. Table 4 defines how the

device behaves in each of the operational states.

Power

Applied

Power ON

Reset

Device

OFF

Delay Finished

Sleep

Sleep = OFF

Calibration

Hold

Power Down = OFF

Power Down = ON

CAL_Enabled

Sleep = ON

VCO

CAL

CAL Done

Manual

Recalibration = ON

Sync = ON

Power Down

Power Down = ON

Active Mode

Sync

Sync = OFF

Figure 17. CDCE62005 Device State Control Diagram

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

21

�CDCE62005

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

www.ti.com

Table 4. CDCE62005 Device State Definitions

STATUS

STATE

DEVICE BEHAVIOR

ENTERED VIA

EXITED VIA

SPI PORT

PLL

OUTPUT

DIVIDER

OUTPUT

BUFFER

After device power supply reaches

approximately 2.35 V, the contents of

EEPROM are copied into the Device

Registers within 100ns, thereby

initializing the device hardware.

Power applied to the device or upon exit

from Power Down State via the

Power_Down pin set HIGH.

Power On Reset and EEPROM loading delays

are finished OR the Power_Down pin is set

LOW.

OFF

Disabled

Disabled

OFF

Power-On

Reset

Delay process in the Power-On Reset

State is finished or Sleep Mode (Sleep bit

is in Register 8 bit 7) is turned OFF while

in the Sleep State. Power Down must be

OFF to enter the Calibration Hold State.

The device waits until either ENCAL_MODE

(Device Register 6 bit 27) is low (Start up

calibration enabled) or both ENCAL_MODE is

high (Manual Calibration Enabled) AND ENCAL

(Device Register 6 bit 22) transitions from a low

to a high signaling the device

ON

Enabled

Disabled

OFF

Calibration

Hold

The device waits until either

ENCAL_MODE (Device Register 6 bit

27) is low (Start up calibration enabled)

or both ENCAL_MODE is high (Manual

Calibration Enabled) AND ENCAL

(Device Register 6 bit 22) transitions

from a low to a high signaling the

device.

Calibration Process in completed

ON

Enabled

Disabled

OFF

VCO CAL

The voltage controlled oscillator is

calibrated based on the PLL settings

and the incoming reference clock. After

the VCO has been calibrated, the device

enters Active Mode automatically.

Calibration Hold: CAL Enabled becomes

true when either ENCAL_MODE (Device

Register 6 bit 27) is low or both

ENCAL_MODE is high AND ENCAL

(Device Register 6 bit 22) transitions from

a low to a high.

Active Mode: A Manual Recalibration is

requested. This is initiated by setting

ENCAL_MODE to HIGH (Manual

Calibration Enabled) AND initiating a

calibration sequence by applying a LOW to

HIGH transition on ENCAL.

Active Mode

Normal Operation

CAL Done (VCO calibration process

finished) or Sync = OFF (from Sync State).

Sync, Power Down, Sleep, or Manual

Recalibration activated.

ON

Enabled

Disabled or Enabled

HI-Z or Enabled

Power_Down pin is pulled LOW.

Power_Down pin is pulled HIGH.

OFF

Disabled

Disabled

HI-Z

Power Down

Used to shut down all hardware and

Resets the device after exiting the

Power Down State. Therefore, the

EEPROM contents will eventually be

copied into RAM after the Power Down

State is exited.

Identical to the Power Down State

except the EEPROM contents are not

copied into RAM.

Sleep bit in device register 8 bit 7 is set

LOW.

Sleep bit in device register 8 bit 7 is set HIGH.

ON

Disabled

Disabled

HI-Z

Sleep

Sync synchronizes all output dividers so

that they begin counting at the same

time. Note: this operation is performed

automatically each time a divider

register is accessed.

Sync Bit in device register 8 bit 8 is set

LOW or Sync pin is pulled LOW

Sync Bit in device register 8 bit 8 is set HIGH or

Sync pin is pulled HIGH

ON

Enabled

Disabled

HI-Z

Sync

22

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

�CDCE62005

www.ti.com

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

8.3.4 External Control Pins

REF_SEL

REF_SEL provides a way to switch between the primary and secondary reference inputs (PRI_REF

and SEC_REF) via an external signal. It works in conjunction with the smart multiplexer discussed

in Input Block.

Power_Down The Power_Down pin places the CDCE62005 into the power down state.

The CDCE62005 loads the contents of the EEPROM into RAM after the Power_Down pin is

de-asserted; therefore, it is used to initialize the device after power is applied. SPI_LE signal

has to be HIGH in order for EEPROM to load correctly during the rising edge of

Power_Down.

SYNC

The SYNC pin (Active LOW) has a complementary register location located in Device Register 8 bit

8.

When enabled, Sync synchronizes all output dividers so that they begin counting

simultaneously. Further, SYNC disables all outputs when in the active state.

NOTE

The output synchronization does not work for reference input frequencies less than

1 MHz.

8.3.5 Input Block

The Input Block includes two Universal Input Buffers, an Auxiliary Input, and a Smart Multiplexer. The Input Block

drives three different clock signals onto the Internal Clock Distribution Bus: buffered versions of both the primary

and secondary inputs (PRI_REF and SEC_REF) and the output of the Smart Multiplexer.

Universal Input Buffers

PRI_REF

LVPECL : Up to 1500 MHz

LVDS : Up to 800 MHz

LVCMOS : Up to 250 MHz

Register 6

12

9

8

Register 5

6 1 0

Register 5

5 4 3

2

Smart MUX

Control

REF _SEL

Register 0

1

Smart Multiplexer

0

/1:/2:HiZ

250 MHz

Reference Divider

/1 - /8

Register 1

Auxiliary Input

1

/1:/2:HiZ

Crystal : 2 MHz – 42 MHz

Smart

MUX 1

Smart

MUX2

Internal Clock Distribution Bus

SEC_REF

0

250 MHz

Register 3 Register 2

0

1 0

XTAL /

AUX IN

Figure 18. CDCE62005 Input Block With References to Registers

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

23

�CDCE62005

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

www.ti.com

8.3.5.1 Universal Input Buffers (UIB)

Figure 19 shows the key elements of a universal input buffer. A UIB supports multiple formats along with different

termination and coupling schemes. The CDCE62005 implements the UIB by including on board switched

termination, a programmable bias voltage generator, and an output multiplexer. The CDCE62005 provides a high

degree of configurability on the UIB to facilitate most existing clock input formats.

PRI_REF

PINV

PN

PP

50 Ω

50 Ω

Register 6

12

Vbb

50 Ω

50 Ω

SN

SP

NOTE: 1.2 V is measured with a LVPECL current load and

0.95 V without any load.

Register 5

10 9 8

Vbb

1 mF

Settings

5.1

5.0

5.6

Nominal

INBUFSELY INBUFSELX ACDCSEL

Vbb

1

0

0

1.9V

1

0

1

1.2V

1

1

0

1.2V

1

1

1

1.2V

Universal Input Control

7

6

1

0

SINV

5.0

INBUFSELX

0

X

X

X

SEC_REF

Settings

5.1

5.8, 6.12

INBUFSELY

TERMSEL

0

X

X

1

1

0

1

0

SWITCH Status

5.9,5.10

INVBB

X

X

0

1

P

OFF

OFF

ON

ON

N

OFF

OFF

ON

ON

INV

OFF

OFF

ON

OFF

Figure 19. CDCE62005 Universal Input Buffer

Switch PP and PN will be closed only if 5.8=0 and 5.0=1 or 5.1=1.

Switch PINV will be closed only if 5.9=0 and switch SINV will be closed only if R5.10=0.

Register 5.0 and 5.6 together pick the Vbb voltage.

Table 5 lists several settings for many possible clock input scenarios. Note that the two universal input buffers

share the Vbb generator. Therefore, if both inputs use internal termination, they must use the same configuration

mode (LVDS, LVPECL, or LVCMOS). If the application requires different modes (for example, LVDS and

LVPECL) then one of the two inputs must implement external termination.

Table 5. CDCE62005 Universal Input Buffer Configuration Matrix

PRI_REF CONFIGURATION MATRIX

Register.Bit →

Bit Name →

(1)

24

5.7

5.1

5.0

5.8

5.9

5.6

HYSTEN

INBUFSELY

INBUFSELX

PRI_TERMSEL

PRIINVBB

ACDCSEL

HYSTERESI

S

MODE

COUPLIN

G

1

0

0

X

X

X

ENABLED

LVCMOS

DC

N/A

—

1

1

0

0

0

0

ENABLED

LVPECL

AC

Internal

1.9V

1

1

0

0

0

1

ENABLED

LVPECL

DC

Internal

1.2V (1)

1

1

0

1

X

X

ENABLED

LVPECL

—

External

—

1

1

1

0

0

0

ENABLED

LVDS

AC

Internal

1.2V

1

1

1

0

0

1

ENABLED

LVDS

DC

Internal

1.2V

1

1

1

1

X

X

ENABLED

LVDS

—

External

—

0

X

X

X

X

X

OFF

—

—

—

—

1

X

X

X

X

X

ENABLED

—

—

—

—

TERMINATIO

N

Vbb

0.95V unloaded

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

�CDCE62005

www.ti.com

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

Table 5. CDCE62005 Universal Input Buffer Configuration Matrix (continued)

PRI_REF CONFIGURATION MATRIX

SEC_REF CONFIGURATION MATRIX

SETTINGS

Register.Bit →

Bit Name →

CONFIGURATION

5.7

5.1

5.0

6.12

5.10

5.6

HYSTEN

INBUFSELY

INBUFSELX

SEC_TERMSEL

SECINVBB

ACDCSEL

Hysteresis

Mode

Coupling

Termination

1

0

0

X

X

X

ENABLED

LVCMOS

DC

N/A

—

1

1

0

0

0

0

ENABLED

LVPECL

AC

Internal

1.9V

1

1

0

0

0

1

ENABLED

LVPECL

DC

Internal

1.2V (1)

1

1

0

1

X

X

ENABLED

LVPECL

—

External

—

1

1

1

0

0

0

ENABLED

LVDS

AC

Internal

1.2V

1

1

1

0

0

1

ENABLED

LVDS

DC

Internal

1.2V

1

1

1

1

X

X

ENABLED

LVDS

—

External

—

0

X

X

X

X

X

OFF

—

—

—

—

1

X

X

X

X

X

ENABLED

—

—

—

—

Vbb

8.3.5.2 LVDS Fail Safe Mode

Differential receivers can switch on noise in the absence of an input signal. This occurs when the clock driver is

turned off or the interconnect is damaged or missing. The traditional solution to this problem involves

incorporating an external resistor network on the receiver input. This network applies a steady-state bias voltage

to the input pins. The additional cost of the external components notwithstanding, the use of such a network

lowers input signal magnitude and thus reduces the differential noise margin. The CDCE62005 provides internal

failsafe circuitry on all LVDS inputs if enabled as shown in Table 6 for DC termination only.

Table 6. LVDS Failsafe Settings

BIT NAME →

REGISTER.BIT →

FAILSAFE

5.11

LVDS FAILSAFE

0

Disabled for all inputs

1

Enabled for all inputs

8.3.5.3 Smart Multiplexer Controls

The smart multiplexer implements a configurable switching mechanism suitable for many applications in which

fault tolerance is a design consideration. It includes the multiplexer itself along with three dividers. With respect to

the multiplexer control, Table 7 provides an overview of the configurations supported by the CDCE62005.

Table 7. CDCE62005 Smart Multiplexer Settings

REGISTER 5 SETTINGS

EECLKSEL

AUXSEL

SECSEL

PRISEL

5.5

5.4

5.3

5.2

1

0

0

1

Manual Mode: PRI_REF selected

1

0

1

0

Manual Mode: SEC_REF selected

1

1

0

0

Manual Mode: AUX IN selected

1

0

1

1

Auto Mode: PRI_REF then SEC_REF

1

1

1

1

Auto Mode: PRI_REF then SEC_REF then AUX IN (1)

0

0

1

1

REF_SEL pin selects PRI_REF or SEC_REF

(1)

SMART MULTIPLEXER MODE

For this mode of operation, a crystal must be connected to the AUX IN input pin.

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

25

�CDCE62005

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

www.ti.com

8.3.5.4 Smart Multiplexer Auto Mode

Smart Multiplexer Auto Mode switches automatically between clock inputs based on a prioritization scheme

shown in Table 7. If using the Smart Multiplexer Auto Mode, the frequencies of the clock inputs may differ by up

to 20%. The phase relationship between clock inputs has no restriction.

Upon the detection of a loss of signal on the highest priority clock, the smart multiplex switches its output to the

next highest priority clock on the first incoming rising edge of the next highest priority clock. During this switching

operation, the output of the smart multiplexer is low. Upon restoration of the higher priority clock, the smart

multiplexer waits until it detects four complete cycles from the higher priority clock prior to switching the output of

the smart multiplexer back to the higher priority clock. During this switching operation, the output of the smart

multiplexer remains high until the next falling edge as shown in Figure 20.

PRI _ REF

SEC _ REF

Internal

Reference Clock

Secondary Clock

Primary Clock

Primary Clock

Figure 20. CDCE62005 Smart Multiplexer Timing Diagram

8.3.5.5 Smart Multiplexer Dividers

Register 5

5 4 3

2

Smart MUX

Control

Register 0

1 0

/1:/2:HiZ

PRI_REF

Universal Input Buffers

SEC_REF

Register 1

1 0

/1:/2:HiZ

Smart Multiplexer

Smart

MUX1

Reference Divider

/1 - /8

Register 3 Register 2

0

1 0

XTAL /

AUX IN

Auxiliary Input

Smart

MUX2

Internal Clock Distribution Bus

REF_SEL

Figure 21. CDCE62005 Smart Multiplexer

26

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

�CDCE62005

www.ti.com

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

The CDCE62005 Smart Multiplexer Block provides the ability to divide the primary and secondary UIB or to

disconnect a UIB from the first state of the smart multiplexer altogether.

Table 8. CDCE62005 Pre-Divider Settings

PRIMARY

PRE-DIVIDER

BIT NAME →

REGISTER.BIT →

SECONDARY

PRE-DIVIDER

DIV2PRIY

0.1

DIV2PRIX

0.0

DIVIDE

RATIO

0

0

0

1

1

1

BIT NAME →

REGISTER.BIT →

DIV2SECY

1.1

DIV2SECX

1.0

DIVIDE

RATIO

Hi-Z

0

0

Hi-Z

/2

0

1

/2

0

/1

1

0

/1

1

Reserved

1

1

Reserved

The CDCE62005 provides a Reference Divider that divides the clock exiting the first multiplexer stage; thus

dividing the primary (PRI_REF) or the secondary input (SEC_REF).

Table 9. CDCE62005 Reference Divider Settings

REFERENCE

DIVIDER

BIT NAME →

REGISTER.BIT →

REFDIV2

3.0

REFDIV1

2.1

REFDIV0

2.0

DIVIDE RATIO

0

0

0

/1

0

0

1

/2

0

1

0

/3

0

1

1

/4

1

0

0

/5

1

0

1

/6

1

1

0

/7

1

1

1

/8

8.3.5.6 Output Block

The output block includes five identical output channels. Each output channel comprises an output multiplexer, a

clock divider module, and a universal output buffer as shown in Figure 22.

Registers 0 - 4

5

4

27 26 25 24 23 22 21

Output

MUX

Control

Internal Clock Distribution Bus

Registers 0 - 4

Sync

Pulse

Output Buffer Control

Enable

PRI_REF

UxP

SEC_REF

Clock Divider Module 0 - 4

SMART _MUX

LVDS

UxN

SYNTH

LVPECL

Figure 22. CDCE62005 Output Channel

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

27

�CDCE62005

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

www.ti.com

8.3.5.7 Output Multiplexer Control

The Clock Divider Module receives the clock selected by the output multiplexer. The output multiplexer selects

from one of four clock sources available on the Internal Clock Distribution. For a description of PRI_REF,

SEC_REF, and SMART_MUX, see Figure 18. For a description of SYNTH, see Figure 28.

Table 10. CDCE62005 Output Multiplexer Control Settings

OUTPUT MULTIPLEXER CONTROL

REGISTER n (n = 0,1,2,3,4)

CLOCK SOURCE SELECTED

OUTMUXnSELX

n.4

OUTMUXnSELY

n.5

0

0

PRI_REF

0

1

SEC_REF

1

0

SMART_MUX

1

1

SYNTH

8.3.5.8 Output Buffer Control

Each of the five output channels includes a programmable output buffer; supporting LVPECL, LVDS, and

LVCMOS modes. Table 11 lists the settings required to configure the CDCE62005 for each output type.

Registers 0 through 4 correspond to Output Channels 0 through 4 respectively.

Table 11. CDCE62005 Output Buffer Control Settings

OUTPUT BUFFER CONTROL

REGISTER n (n = 0,1,2,3,4)

OUTPUT TYPE

CMOSMODEnPX

CMOSMODEnPY

CMOSMODEnNX

CMOSMODEnNY

OUTBUFSELnX

OUTBUFSELnY

n.22

n.23

n.24

n.25

n.26

n.27

0

0

0

0

0

1

0

1

0

1

1

1

LVDS

0

0

LVCMOS

1

0

Disabled to High-Z

See LVCMOS Output Buffer Configuration Settings

0

1

0

1

LVPECL

8.3.5.9 Output Buffer Control – LVCMOS Configurations

A LVCMOS output configuration requires additional configuration data. In the single ended configuration, each

Output Channel provides a pair of outputs. The CDCE62005 supports four modes of operation for single ended

outputs as listed in Table 12.

Table 12. LVCMOS Output Buffer Configuration Settings

OUTPUT BUFFER CONTROL – LVCMOS CONFIGURATION

REGISTER n (n = 0,1,2,3,4)

OUTPUT

TYPE

PIN

0

LVCMOS

Negative

Active – Non-inverted

0

LVCMOS

Negative

Hi-Z

0

0

LVCMOS

Negative

Active – Non-inverted

1

0

0

LVCMOS

Negative

Low

X

X

0

0

LVCMOS

Positive

Active – Non-inverted

1

X

X

0

0

LVCMOS

Positive

Hi-Z

1

0

X

X

0

0

LVCMOS

Positive

Active – Non-inverted

1

1

X

X

0

0

LVCMOS

Positive

Low

CMOSMODEnPX

CMOSMODEnPY

CMOSMODEnNX

CMOSMODEnNY

OUTBUFSELnX

OUTBUFSELnY

n.22

n.23

n.24

n.25

n.26

n.27

X

X

0

0

0

X

X

0

1

0

X

X

1

0

X

X

1

0

0

0

28

Submit Documentation Feedback

OUTPUT MODE

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

�CDCE62005

www.ti.com

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

8.3.5.10 Output Dividers

Figure 23 shows that each output channel provides a 7-bit divider and digital phase adjust block. The Table 13

lists the divide ratios supported by the output divider for each output channel. Figure 24 illustrates the output

divider architecture in detail. The Prescaler provides an array of low noise dividers with duty cycle correction. The

Integer Divider includes a final divide by two stage which is used to correct the duty cycle of the /1–/8 stage. The

output divider’s maximum input frequency is limited to 1.175 GHz. If the divider is bypassed (divide ratio = 1)

then the maximum frequency of the output channel is 1.5 GHz.

Registers 0 - 4

Registers 0 - 4

12 11 10 9

8

7

6

20

Enable

Sync

Pulse

(internally generated )

Digital Phase Adjust (7-bits)

From

Output

MUX

To

Output

Buffer

Output Divider (7-bits)

Registers 0 - 4

19 18 17 16 15 14 13

Figure 23. CDCE62005 Output Divider and Phase Adjust

Registers 0 - 4

Registers 0 - 4

14 13

From

Output

MUX

Registers 0 - 4

19 18

17 16 15

/2-/5

/1 - /8

Prescaler

/2

00

To

Output

Buffer

Integer Divider

10

01

Figure 24. CDCE62005 Output Divider Architecture

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Product Folder Links: CDCE62005

29

�CDCE62005

SCAS862G – NOVEMBER 2008 – REVISED JULY 2016

www.ti.com

Table 13. CDCE62005 Output Divider Settings (1)

OUTPUT DIVIDER n SETTINGS REGISTER (n = 0,1,2,3,4)

MULTIPLEXER

OUTnDIVSEL6

INTEGER DIVIDER

OUTnDIVSEL5

OUTnDIVSEL4

OUTnDIVSEL3

OUTPUT

DIVIDE RATIO

PRESCALER

OUTnDIVSEL2

OUTnDIVSEL1

OUTnDIVSEL0

OUTnDIVSEL

OUTPUT

(1)

30

PRESCALER

SETTING

INTEGER

DIVIDER

SETTING

CHANNELS

AUXILIARY

0-4

OUTPUT

OFF

OFF

n.19

n.18

n.17

n.16