DRV8800, DRV8801

DRV8801

SLVS855K – JULY 2008 DRV8800,

– REVISED MARCH

2021

SLVS855K – JULY 2008 – REVISED MARCH 2021

www.ti.com

DRV880x DMOS Full-Bridge Motor Drivers

1 Features

3 Description

•

•

•

•

•

•

•

The DRV880x provides a versatile motor driver

solution with a variety of capabilities. The device

contains a full H-bridge which can be used to drive

a brushed DC motor, one winding of a stepper motor,

or other devices such as solenoids. A simple PHASEENABLE interface allows easy interfacing to controller

circuits.

H-Bridge Motor Driver

Low RDS(on) MOSFETs (0.4-Ω Typical)

Low-Power Sleep Mode

100% PWM Duty Cycle Supported

8-V to 36-V Operating Supply Voltage Range

Thermally Enhanced Surface-Mount Package

Protection Features:

– VBB Undervoltage Lockout (UVLO)

– Charge Pump Undervoltage (CPUV)

– Overcurrent Protection (OCP)

– Short-to-Supply Protection

– Short-to-Ground Protection

– Overtemperature Warning (OTW)

– Overtemperature Shutdown (OTS)

– Fault Condition Indication Pin (nFAULT)

2 Applications

•

•

•

Printers

Industrial Automation

Robotics

The output stages use N-channel power MOSFETs

configured as an H-bridge. The DRV880x is capable

of peak output currents up to ±2.8 A and operating

voltages up to 36 V. An internal charge pump

generates the needed gate drive voltages.

A low-power sleep mode is provided which shuts

down internal circuitry to achieve a very low quiescent

current draw. This sleep mode can be set using a

dedicated nSLEEP pin.

Internal protection functions are provided for

undervoltage, charge pump fault, overcurrent, shortto-supply, short-to-ground, and overtemperature. Fault

conditions are indicated through the nFAULT pin.

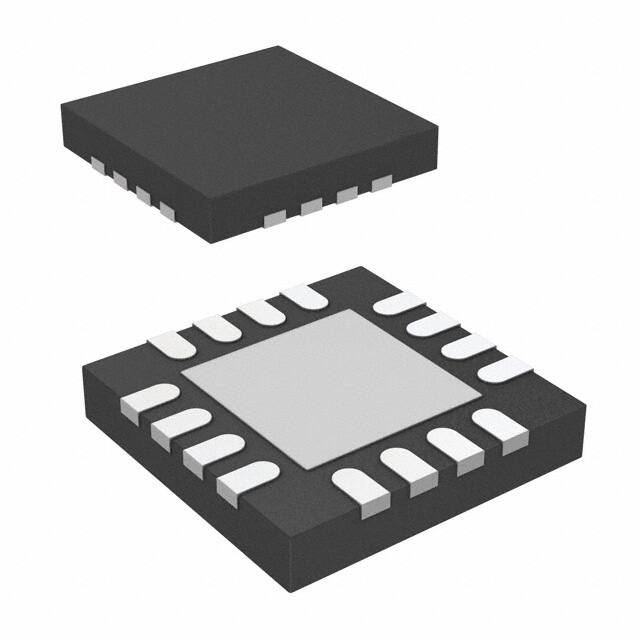

The DRV880x is packaged in a 16-pin WQFN

package with PowerPAD™ (Eco-friendly: RoHS & no

Sb/Br).

Device Information(1)

PART NUMBER

DRV8800

DRV8801

(1)

PACKAGE

BODY SIZE (NOM)

HTSSOP (16)

5.00 mm × 4.40 mm

WQFN (16)

4.00 mm × 4.00 mm

HTSSOP (16)

5.00 mm × 4.40 mm

WQFN (16)

4.00 mm × 4.00 mm

For all available packages, see the orderable addendum at

the end of the data sheet.

8 V to 36 V

Controller

PHASE

DRV8800/

DRV8801

ENABLE

nSLEEP

Brushed DC

Motor Driver

M

nFAULT

Protection

Simplified Schematic

An©IMPORTANT

NOTICEIncorporated

at the end of this data sheet addresses availability, warranty, changes, use in

safety-critical

applications,

Copyright

2021 Texas Instruments

Submit

Document

Feedback

intellectual property matters and other important disclaimers. PRODUCTION DATA.

Product Folder Links: DRV8800 DRV8801

1

�DRV8800, DRV8801

www.ti.com

SLVS855K – JULY 2008 – REVISED MARCH 2021

Table of Contents

1 Features............................................................................1

2 Applications..................................................................... 1

3 Description.......................................................................1

4 Revision History.............................................................. 2

5 Pin Configuration and Functions...................................3

6 Specifications.................................................................. 5

6.1 Absolute Maximum Ratings........................................ 5

6.2 ESD Ratings............................................................... 5

6.3 Recommended Operating Conditions.........................5

6.4 Thermal Information....................................................5

6.5 Electrical Characteristics.............................................6

6.6 Typical Characteristics................................................ 7

7 Parameter Measurement Information............................ 8

8 Detailed Description......................................................10

8.1 Overview................................................................... 10

8.2 Functional Block Diagrams....................................... 10

8.3 Feature Description...................................................11

8.4 Device Functional Modes..........................................13

9 Application and Implementation.................................. 16

9.1 Application Information............................................. 16

9.2 Typical Application.................................................... 16

9.3 Parallel Configuration ...............................................19

10 Power Supply Recommendations..............................23

10.1 Bulk Capacitance.................................................... 23

11 Layout........................................................................... 24

11.1 Layout Guidelines................................................... 24

11.2 Layout Example...................................................... 24

12 Device and Documentation Support..........................26

12.1 Related Links.......................................................... 26

12.2 Trademarks............................................................. 26

12.3 Electrostatic Discharge Caution..............................26

12.4 Glossary..................................................................26

13 Mechanical, Packaging, and Orderable

Information.................................................................... 26

4 Revision History

Changes from Revision J (July 2014) to Revision K (March 2021)

Page

• Added missing GND pin reference to Pin Functions Table ................................................................................3

• Added SENSE pin to Pin Functions Table ......................................................................................................... 3

• Improved description for pins nFAULT, nSLEEP, VBB and VCP in Pin Functions Table ................................... 3

• Added entries for VCP and CP2 pins in Absolute Maximum Ratings table........................................................ 5

• Added VDD pin voltage limits and device’s PWM frequency limits to Recommended Operation Conditions

table.................................................................................................................................................................... 5

• Changed SLEEP to nSLEEP in PWM Control Timing Figure............................................................................. 8

• Added equation for VPROPI to help when connecting pin’s output to ADC in Feature Description ................12

• Provide additional information on SENSE pin behavior....................................................................................13

• Added device specific details to Control Logic Table .......................................................................................13

• Added die temperature estimation equation utilizing junction to ambient thermal impedance in Application and

Implementation section.....................................................................................................................................18

• Added information on using motor driver’s pulse width modulating modes in Application and Implementation

section.............................................................................................................................................................. 18

Changes from Revision I (January 2014) to Revision J (July 2014)

Page

• Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and

Implementation section, Power Supply Recommendations section, Layout section, Device and

Documentation Support section, and Mechanical, Packaging, and Orderable Information section .................. 5

Changes from Revision H (November 2013) to Revision I (January 2014)

Page

• Added IOCP to ELECTRICAL CHARACTERISTICS........................................................................................... 6

• Changed Parameter Measurement Information ................................................................................................ 8

Changes from Revision G (October 2013) to Revision H (November 2013)

Page

• Changed maximum junction temperature from 190°C to 150°C.........................................................................5

• Changed VTRP description/test conditions........................................................................................................ 6

• Changed Protection Circuitry section................................................................................................................. 6

• Changed Note in SENSE section..................................................................................................................... 13

2

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: DRV8800 DRV8801

�DRV8800, DRV8801

www.ti.com

SLVS855K – JULY 2008 – REVISED MARCH 2021

nFAULT

VPROPI

VCP

14

13

VCP

13

15

VREG

14

MODE 1

nFAULT

15

16

MODE

16

5 Pin Configuration and Functions

PHASE

1

12

GND

PHASE

1

12

GND

GND

2

11

CP2

GND

2

11

CP2

nSLEEP

3

10

CP1

nSLEEP

3

10

CP1

ENABLE

4

9

OUT-

ENABLE

4

9

OUT-

PowerPAD

6

7

8

SENSE

VBB

8

VBB

OUT+

7

SENSE

5

6

OUT+

Figure 5-1. DRV8800 RTY Package 16-Pin WQFN

Top View

MODE 2

5

NC

PowerPAD

Figure 5-2. DRV8801 RTY Package 16-Pin WQFN

Top View

nFAULT

1

16

NC

nFAULT

1

16

MODE 2

MODE

2

15

VREG

MODE 1

2

15

VPROPI

PHASE

3

14

VCP

PHASE

3

14

VCP

GND

4

13

GND

GND

4

13

GND

PowerPAD

PowerPAD

nSLEEP

5

12

CP2

nSLEEP

5

12

CP2

ENABLE

6

11

CP1

ENABLE

6

11

CP1

OUT+

7

10

OUT-

OUT+

7

10

OUT-

SENSE

8

9

VBB

SENSE

8

9

VBB

Figure 5-3. DRV8800 PWP Package 16-Pin HTSSOP Figure 5-4. DRV8801 PWP Package 16-Pin HTSSOP

Top View

Top View

Table 5-1. Pin Functions

PIN

NAME

DRV8800

DRV8801

I/O

DESCRIPTION

WQFN

HTSSOP

WQFN

HTSSOP

CP1

10

11

10

11

P

Charge pump switching node. Connect a 0.1-μF

X7R ceramic capacitor rated for VBB between

CP1 and CP2.

CP2

11

12

11

12

P

Charge pump switching node. Connect a 0.1-μF

X7R ceramic capacitor rated for VBB between

CP1 and CP2.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: DRV8800 DRV8801

3

�DRV8800, DRV8801

www.ti.com

SLVS855K – JULY 2008 – REVISED MARCH 2021

Table 5-1. Pin Functions (continued)

PIN

NAME

ENABLE

GND

4

DRV8800

I/O

DRV8801

DESCRIPTION

WQFN

HTSSOP

WQFN

HTSSOP

4

6

4

6

I

Enable logic input. Set high to enable the Hbridge.

2,12

4, 13

2, 12

4, 13

P

Device ground

MODE

16

2

—

—

I

Mode logic input

MODE 1

—

—

16

2

I

Mode logic input

Mode 2 logic input

MODE 2

—

—

5

16

I

NC

5

16

—

—

NC

No connect

nFAULT

15

1

15

1

OD

Fault indication. Pulled logic low with fault

condition; open-drain output requires an external

pullup resistor.

nSLEEP

3

5

3

5

I

Sleep mode input. Logic high to enable device;

logic low to enter low-power sleep mode; internal

pulldown resistor.

OUT+

6

7

6

7

O

DMOS H-bridge output. Connect to motor

terminal.

OUT-

9

10

9

10

O

DMOS H-bridge output. Connect to motor

terminal.

WQFN Package: Phase logic input for direction

control.

HTSSOP Package: Phase logic input. Controls

the direction of the H-bridge.

PHASE

1

3

1

3

I

SENSE

7

8

7

8

O (DRV8800)

IO (DRV8801)

VBB

8

9

8

9

P

Driver supply voltage. Bypass to GND with 0.1-μF

ceramic capacitors plus a bulk capacitor rated for

VBB.

VCP

13

14

13

14

P

Charge pump reservoir capacitor pin. Connect a

X7R, 0.1-μF, 16-V ceramic capacitor to VBB.

VREG

14

15

—

—

P

Regulated voltage.

VPROPI

—

—

14

15

O

Voltage output proportional to winding current.

PowerPAD

—

—

—

—

—

Exposed pad for thermal dissipation. Connect to

ground.

Sense Power Return

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: DRV8800 DRV8801

�DRV8800, DRV8801

www.ti.com

SLVS855K – JULY 2008 – REVISED MARCH 2021

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

VBB

VCP and CP2

VSense

MIN

MAX

UNIT

Load supply voltage(2)

–0.3

40

V

Charge Pump Voltage

–0.3

VBB+17V

V

Output current

–2.8

2.8

A

Sense voltage

–500

500

mV

36

V

VBB to OUTx

OUTx to SENSE

PHASE, ENABLE, MODE, MODE1, MODE2, nSLEEP and nFAULT(2)

VDD

Continuous total power dissipation

TA

Operating free-air temperature

TJ

Maximum junction temperature

Tstg

Storage temperature

(1)

(2)

36

V

7

V

–0.3

See Section 6.4

–40

–40

85

°C

150

°C

125

°C

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating

Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltage values are with respect to network ground terminal.

6.2 ESD Ratings

VALUE

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all

V(ESD)

(1)

(2)

Electrostatic discharge

pins(1)

UNIT

±2000

Charged device model (CDM), per JEDEC specification JESD22-C101, all

pins(2)

V

±500

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions

MIN

NOM

32

MAX

UNIT

VIN

Input voltage, VBB

8

38

V

VDD

Logic Supply Voltage

0

5.5

V

f(PWM)

Applied PMW signal (PHASE and ENABLE)

0

100

kHz

TA

Operating free-air temperature

–40

85

°C

6.4 Thermal Information

DRV880x

THERMAL METRIC(1)

RTY (WQFN)

PWP (HTSSOP)

16 PINS

16 PINS

RθJA

Junction-to-ambient thermal resistance

38.1

43.9

RθJC(top)

Junction-to-case (top) thermal resistance

36.7

30.8

RθJB

Junction-to-board thermal resistance

16.1

25.3

ψJT

Junction-to-top characterization parameter

0.3

1.1

ψJB

Junction-to-board characterization parameter

16.2

25

RθJC(bot)

Junction-to-case (bottom) thermal resistance

4.1

5.6

(1)

UNIT

°C/W

For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: DRV8800 DRV8801

5

�DRV8800, DRV8801

www.ti.com

SLVS855K – JULY 2008 – REVISED MARCH 2021

6.5 Electrical Characteristics

over recommended operating conditions (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

fPWM < 50 kHz

IBB

Motor supply current

TYP

6

Charge pump on, Outputs disabled

VIH

0.8

2.7

nSLEEP input voltage

VIL

IIH

PHASE, MODE input current

IIL

IIH

ENABLE input current

IIL

IIH

nSLEEP input current

IIL

0.8

VIN = 2 V