ONET4251PA

www.ti.com

SLLS663A – SEPTEMBER 2005 – REVISED NOVEMBER 2005

1 Gbps to 4.25 Gbps Limiting Amplifier With LOS and RSSI

FEATURES

•

•

•

•

•

•

•

•

Multi-Rate Operation from 1 Gbps up to

4.25 Gbps

89-mW Power Consumption

Input Offset Cancellation

High Input Dynamic Range

Output Disable

CML Data Outputs

Receive Signal Strength Indicator (RSSI)

Loss of Signal Detection

•

•

•

Polarity Select

Single 3.3-V Supply

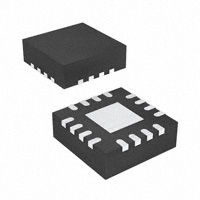

Surface Mount Small Footprint 3-mm × 3-mm

16-Pin QFN Package

APPLICATIONS

•

•

•

Cable Driver and Receiver

1.0625 Gbps, 2.125 Gbps, and 4.25 Gbps Fibre

Channel Receivers

Gigabit Ethernet Receivers

DESCRIPTION

The ONET4251PA is a versatile high-speed limiting amplifier for copper cable and fiber optic applications with

data rates up to 4.25 Gbps.

This device provides a gain of about 50 dB, which ensures a full 800-mVp-p differential output swing over its wide

input signal dynamic range.

The high input signal dynamic range ensures low jitter output signals even when overdriven with input signal

swings as high as 1200 mVp-p.

The ONET4251PA comprises a loss of signal detection as well as a received signal strength indicator.

The part is available in a small footprint 3-mm × 3-mm 16-pin QFN package. It requires a single 3.3-V supply.

This power efficient limiting amplifier dissipates less than 89 mW typical. It is characterized for operation from

–40°C to 85°C.

BLOCK DIAGRAM

A simplified block diagram of the ONET4251PA is shown in Figure 1.

This compact 3.3 V, low power 4.25 Gbps limiting amplifier consists of a high-speed data path with offset

cancellation block, a loss of signal and RSSI detection block, and a bandgap voltage reference and bias current

generation block.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2005, Texas Instruments Incorporated

�ONET4251PA

www.ti.com

SLLS663A – SEPTEMBER 2005 – REVISED NOVEMBER 2005

COC2

COC1

Bandgap Voltage

Reference and

Bias Current

Generation

Offset

Cancellation

OUTPOL

DIN+

+

+

+

+

+

DIN−

−

−

−

−

−

Gain Stage

Gain Stage

Input Buffer

Gain Stage

DOUT+

DOUT−

CML

Output

Buffer

Stage

Loss of Signal

and

RSSI Detection

VCC

GND

TH

DISABLE

LOS

RSSI

B0052-01

Figure 1. Simplified Block Diagram of the ONET4251PA

HIGH SPEED DATA PATH

The high-speed data signal is applied to the data path by means of the input signal pins DIN+/DIN–. The data

path consists of the input stage with 2 × 50-Ω on-chip line termination to VCC, three gain stages, which provide

the required typical gain of about 50 dB, and a CML output stage. The amplified data output signal is available at

the output pins DOUT+/DOUT–, which provide 2 × 50-Ω back-termination to VCC. The output stage also includes

a data polarity switching function, which is controlled by the OUTPOL input, and a disable function, controlled by

the signal applied to the DISABLE input pin.

An offset cancellation compensates for internal offset voltages and thus ensures proper operation even for very

small input data signals.

The low frequency cutoff is typically as low as 50 kHz with the built-in filter capacitor.

For applications which require even lower cutoff frequencies, an additional external filter capacitor may be

connected to the COC1/COC2 pins.

LOSS OF SIGNAL AND RSSI DETECTION

The output signal of the input buffer is monitored by the loss of signal and RSSI detection circuitry. In this block,

a signal is generated that is linear proportional to the input amplitude over a wide input voltage range. This signal

is available at the RSSI output pin.

Furthermore, this circuit block compares the input signal to a threshold which can be programmed by means of

an external resistor connected to the TH pin. If the input signal falls below the specified threshold, a loss of signal

is indicated at the LOS pin.

The relation between the LOS assert voltage VAST (in mVp-p) and the external resistor RTH (in kΩ) connected to

the TH pin can be approximated as given below:

2

�ONET4251PA

www.ti.com

SLLS663A – SEPTEMBER 2005 – REVISED NOVEMBER 2005

R

TH

V

�

AST

22.4 k�

�VAST�mVp�p � 1�

�

22.4 mV p�p

R

�k� � 0.56

TH

� 560 �

(1)

� 1 mV p�p

(2)

BANDGAP VOLTAGE AND BIAS GENERATION

The ONET4251PA limiting amplifier is supplied by a single 3.3-V ±10% supply voltage connected to the VCC

pins. This voltage is referred to ground (GND).

An on-chip bandgap voltage circuitry generates a supply voltage independent reference from which all other

internally required voltages and bias currents are derived.

PACKAGE

For the ONET4251PA a small footprint 3-mm × 3-mm 16-pin QFN package, with a lead pitch of 0,5 mm is used.

The pin out is shown in Figure 2.

2

RSSI

DIN+

COC1

1

COC2

VCC

GND

RGT PACKAGE

(TOP VIEW)

16

15

14

13

12

VCC

11

DOUT+

10

DOUT−

9

OUTPOL

4

5

6

7

8

GND

VCC

LOS

3

DISABLE

DIN−

TH

EP

P0019-01

Figure 2. Pinout of ONET4251PA in a 3 mm x 3 mm 16-Pin QFN Package (Top View)

TERMINAL FUNCTIONS

TERMINAL

NO.

NAME

TYPE

DESCRIPTION

3.3-V ±10% supply voltage

1, 4, 12

VCC

supply

2

DIN+

analog-in

Non-inverted data input. On-chip 50-Ω terminated to VCC.

3

DIN-

analog-in

Inverted data input. On-chip 50-Ω terminated to VCC.

5

TH

analog-in

LOS threshold adjustment with resistor to GND.

6

DISABLE

CMOS-in

Disables CML output stage when set to high level.

7

LOS

CMOS-out

8, 16, EP

GND

supply

OUTPOL

CMOS-in

Output data signal polarity select (internally pulled high). Setting to a high level or leaving the pin

open selects normal polarity. Low level selects inverted polarity.

10

DOUT-

CML-out

Inverted data output. On-chip 50-Ω back-terminated to VCC.

11

DOUT+

CML-out

Non-inverted data output. On-chip 50-Ω back-terminated to VCC

9

High level indicates that the input signal amplitude is below the programmed threshold level.

Circuit ground. Exposed die pad (EP) must be grounded.

3

�ONET4251PA

www.ti.com

SLLS663A – SEPTEMBER 2005 – REVISED NOVEMBER 2005

TERMINAL FUNCTIONS (continued)

TERMINAL

TYPE

DESCRIPTION

NO.

NAME

13

RSSI

analog-out

14

COC1

analog

Offset cancellation filter capacitor terminal 1. Connect an additional filter capacitor between this pin

and COC2 (pin 15).

To disable the offset cancellation loop connect COC1 and COC2 (pins 14 and 15).

15

COC2

analog

Offset cancellation filter capacitor terminal 2. Connect an additional filter capacitor between this pin

and COC1 (pin 14).

To disable the offset cancellation loop connect COC1 and COC2 (pins 14 and 15).

Analog output voltage proportional to the input data amplitude. Indicates the strength of the

received signal (RSSI).

ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted) (1)

VALUE/UNIT

(2)

VCC

Supply voltage

VDIN+, VDIN-

Voltage at DIN+, DIN– (2)

0.5 V to 4 V

VTH, VDISABLE, VLOS, VOUTPOL, VDOUT+,

VDOUT–, VRSSI, VCOC1, VCOC2

Voltage at TH, DISABLE, LOS, OUTPOL, DOUT+, DOUT-, RSSI,

COC1, COC2 (2)

–0.3 V to 4 V

VCOC,DIFF

Differential voltage between COC1 and COC2

VDIN,DIFF

Differential voltage between DIN+ and DIN–

ILOS

Current into LOS

IDIN+, IDIN–, IDOUT+, IDOUT–

Continuous current at inputs and outputs

ESD

ESD rating at all pins

TJ(max)

Maximum junction temperature

TSTG

Storage temperature range

–65 to 85°C

TA

Characterized free-air operating temperature range

–40 to 85°C

TLEAD

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds

(1)

(2)

–0.3 V to 4 V

±1 V

±2.5 V

– 1 to 9 mA

–25 mA to 25 mA

2 kV (HBM)

125°C

260°C

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating

conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltage values are with respect to network ground terminal.

RECOMMENDED OPERATING CONDITIONS

MIN

TYP

MAX

3.3

3.6

V

85

°C

VCC

Supply voltage

3.0

TA

Operating free-air temperature

–40

VIH

CMOS input high voltage

2.1

VIL

CMOS input low voltage

4

UNIT

V

0.6

V

�ONET4251PA

www.ti.com

SLLS663A – SEPTEMBER 2005 – REVISED NOVEMBER 2005

DC ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

PARAMETER

VCC

Supply voltage

IVCC

Supply current

VOD

Differential data output voltage swing

RIN, ROUT

Data input/output resistance

VRSSI

RSSI output voltage

RSSI Linearity

VIN(MIN)

Minimum data input voltage

VIN(MAX)

Data input overload

TEST CONDITIONS

MIN

TYP

MAX

3

3.3

3.6

V

27

40

mA

DISABLE = low (excludes CML output current)

DISABLE = high

DISABLE = low

600

Single-ended

0.25

10

760

1200

UNIT

mVp-p

Ω

50

Input = 8 mVp-p, RRSSI ≥ 10 kΩ

180

Input = 80 mVp-p, RRSSI ≥ 10 kΩ

1900

8 mVp-p ≤ VIN ≤ 80 mVp-p

±3%

mV

50

1200

LOS high voltage

ISOURCE = 30 µA

LOS low voltage

ISINK = 1 mA

mVp-p

mVp-p

2.4

V

0.4

V

AC ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted), typical operating condition is at VCC = 3.3 V and TA = 25°C

PARAMETER

Low frequency –3 dB bandwidth

TEST CONDITIONS

50

COC = 0.1 µF

0.8

UNIT

kHz

Gb/s

230

K28.5 pattern at 4.25 Gbps

Deterministic jitter

MAX

4.25

Input referred noise

DJ

TYP

COC = open

Data rate

vNI

MIN

µVRMS

6

19

K28.5 pattern at 2.125 Gbps

8

22

K28.5 pattern at 1.0625 Gbps

11

28

RJ

Random jitter

Input = 50 mVpp

tr

Output rise time

20% to 80%

35

70

ps

tf

Output fall time

20% to 80%

35

70

ps

LOS hysteresis

K28.5 pattern at 4.25 Gbps

RTH

LOS threshold adjustment resistor

See

VAST

LOS assert voltage

RTH = 4 kΩ K28.5 pattern at 4.25 Gbps

VDEA

LOS deassert voltage

RTH = 4 kΩ K28.5 pattern at 4.25 Gbps

tLOS

LOS assert/deassert time

tDIS

Disable response time

(1)

1

psp-p

2.5

(1)

3

psRMS

4.5

dB

4

kΩ

7

mVp-p

11

2

50

mVp-p

100

µs

20

ns

For a given external resistor connected to the TH pin, the LOS assert voltage value may vary due to part-to-part variations. If high

precision is required, adjustment of this resistor for each device is mandatory.

5

�ONET4251PA

www.ti.com

SLLS663A – SEPTEMBER 2005 – REVISED NOVEMBER 2005

TYPICAL CHARACTERISTICS

Typical operating condition is at VCC = 3.3 V and TA = 25°C (unless otherwise noted).

VOD − Differential Output Voltage − 160 mV/Div

OUTPUT EYE-DIAGRAM AT 4.25 GBPS

AND MAXIMUM INPUT VOLTAGE (1200 mVp-p)

VOD − Differential Output Voltage − 160 mV/Div

OUTPUT EYE-DIAGRAM AT 4.25 GBPS

AND MINIMUM INPUT VOLTAGE (50 mVp-p)

t − Time − 50 ps/Div

t − Time − 50 ps/Div

G005

G006

Figure 3.

Figure 4.

OUTPUT EYE-DIAGRAM AT 4.25 GBPS AND 85°C

AND MINIMUM INPUT VOLTAGE (50 mVp-p)

FREQUENCY RESPONSE

VOD − Differential Output Voltage − 160 mV/Div

60

55

50

Small Signal Gain − dB

45

40

35

30

25

20

15

10

5

0

10

t − Time − 50 ps/Div

G007

Figure 5.

6

100

1k

10k

f − Frequency − MHz

G004

Figure 6.

�ONET4251PA

www.ti.com

SLLS663A – SEPTEMBER 2005 – REVISED NOVEMBER 2005

TYPICAL CHARACTERISTICS (continued)

Typical operating condition is at VCC = 3.3 V and TA = 25°C (unless otherwise noted).

OUTPUT EYE-DIAGRAM AT 2.125 GBPS

AND MAXIMUM INPUT VOLTAGE (1200 mVp-p)

VOD − Differential Output Voltage − 160 mV/Div

VOD − Differential Output Voltage − 160 mV/Div

OUTPUT EYE-DIAGRAM AT 2.125 GBPS

AND MINIMUM INPUT VOLTAGE (50 mVp-p)

t − Time − 100 ps/Div

t − Time − 100 ps/Div

G008

G009

Figure 8.

OUTPUT EYE-DIAGRAM AT 1.0625 GBPS

AND MINIMUM INPUT VOLTAGE (50 mVp-p)

OUTPUT EYE-DIAGRAM AT 1.0625 GBPS

AND MAXIMUM INPUT VOLTAGE (1200 mVp-p)

VOD − Differential Output Voltage − 160 mV/Div

VOD − Differential Output Voltage − 160 mV/Div

Figure 7.

t − Time − 200 ps/Div

G010

Figure 9.

t − Time − 200 ps/Div

G011

Figure 10.

7

�ONET4251PA

www.ti.com

SLLS663A – SEPTEMBER 2005 – REVISED NOVEMBER 2005

TYPICAL CHARACTERISTICS (continued)

Typical operating condition is at VCC = 3.3 V and TA = 25°C (unless otherwise noted).

ASSERT/DEASSERT VOLTAGE

vs THRESHOLD RESISTANCE

DIFFERENTIAL INPUT RETURN GAIN

vs FREQUENCY

60

0

SDD11 − Differential Input Return Gain − dB

LOS Assert/Deassert Voltage − mVP-P

55

50

45

40

35

30

25

20

LOS Deassert Voltage

15

10

LOS Assert Voltage

5

0

1

2

3

4

5

6

7

RTH − Threshold Resistance − kΩ

SDD22 − Differential Input Return Gain − dB

−25

−30

−35

−40

−45

−50

−55

100

1k

G013

Figure 11.

Figure 12.

DIFFERENTIAL OUTPUT RETURN GAIN

vs FREQUENCY

RSSI VOLTAGE

vs INPUT AMPLITUDE

−5

−10

−15

−20

−25

−30

−35

−40

−45

−50

−55

100

1k

10k

G014

Figure 13.

10k

f − Frequency − MHz

f − Frequency − MHz

8

−20

G012

0

−60

10

−15

−60

10

8

RSSI − Receive Signals Strength Indicator Voltage − mV

0

−5

−10

2400

2200

2000

1800

1600

1400

1200

1000

800

600

400

200

0

0

10

20

30

40

50

60

70

80

90 100

VID − Differential Input Voltage − mVP-P

Figure 14.

G015

�ONET4251PA

www.ti.com

SLLS663A – SEPTEMBER 2005 – REVISED NOVEMBER 2005

APPLICATION INFORMATION

Figure 15 shows the ONET4251PA connected with an ac-coupled interface to the data signal source as well as

to the output load.

Besides the ac-coupling capacitors C1 through C4 in the input and output data signal lines, the only required

external component is the LOS threshold setting resistor RTH. In addition, if a low cutoff frequency is required, as

an option, an external filter capacitor COC may be used.

RSSI

RSSI

COC1

COC2

GND

COC

Optional

VCC

DIN−

DOUT+

ONET4251PA

16-Pin QFN

TH

VCC

DOUT−

VCC

C3

DOUT+

C4

DOUT−

OUTPOL

OUTPOL

GND

DIN+

LOS

DIN−

C2

VCC

DISABLE

DIN+

C1

DISABLE

LOS

RTH

Optional connection

for squelch function

S0072-01

Figure 15. Basic Application Circuit With AC Coupled I/Os

9

�PACKAGE OPTION ADDENDUM

www.ti.com

10-Dec-2020

PACKAGING INFORMATION

Orderable Device

Status

(1)

Package Type Package Pins Package

Drawing

Qty

Eco Plan

(2)

Lead finish/

Ball material

MSL Peak Temp

Op Temp (°C)

Device Marking

(3)

(4/5)

(6)

ONET4251PARGTR

ACTIVE

VQFN

RGT

16

3000

RoHS & Green

NIPDAU

Level-2-260C-1 YEAR

-40 to 85

451P

ONET4251PARGTT

ACTIVE

VQFN

RGT

16

250

RoHS & Green

NIPDAU

Level-2-260C-1 YEAR

-40 to 85

451P

(1)

The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

OBSOLETE: TI has discontinued the production of the device.

(2)

RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance

do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may

reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of