SN65HVD50-SN65HVD55

www.ti.com

SLLS666E – SEPTEMBER 2005 – REVISED OCTOBER 2009

HIGH OUTPUT FULL-DUPLEX RS-485 DRIVERS AND RECEIVERS

Check for Samples :SN65HVD50-SN65HVD55

•

•

•

•

•

•

•

•

(1)

1/8 Unit-Load Option Available (Up to 256

Nodes on the Bus)

Bus-Pin ESD Protection Exceeds 15 kV HBM

Optional Driver Output Transition Times for

SignalingRates(1) of 1 Mbps, 5 Mbps and

25 Mbps

Low-Current Standby Mode < 1 μA

Glitch-Free Power-Up and Power-Down Bus

I/Os

Bus Idle, Open, and Short Circuit Failsafe

Designed for RS-422 and RS485 Networks

3.3-V Devices Available, SN65HVD30-35

APPLICATIONS

•

•

•

•

•

Utility Meters

Chassis-to-Chassis Interconnects

DTE/DCE Interfaces

Industrial, Process, and Building Automation

Point-of-Sale (POS) Terminals and Networks

All devices are characterized for operation from

–40°C to 85°C.

The high output feature of the SN65HVD5x provides

more noise margin than the typical RS-485 drivers.

The extra noise margin makes applications in long

cable and harsh noise environments possible.

Differential Output Voltage |VOD|

R S485 M inimum |VO D |

R equirement

The signaling rate of a line is the number of voltage

transitions that are made per second expressed in the units

bps (bits per second).

The SN65HVD53, SN65HVD54, and SN65HVD55

have active-high driver enables and active-low

receiver enables. A low, less than 1 μA, standby

current is achieved by disabling both the driver and

receiver.

Over Com m on-M ode V oltage Range

-7 V to 12 V

FEATURES

1

VCC = 4.5V

1 VCC = 5V

Additional Noise

Margin

VCC = 5.5V

0.0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

Differential Output Voltage, |VOD| (V)

DESCRIPTION

The SN65HVD5X devices are 3-state differential line

drivers and differential-input line receivers that

operate with a 5-V power supply. Each driver and

receiver has separate input and output pins for

full-duplex bus communication designs. They are

designed for balanced transmission lines and

interoperation

with

ANSI

TIA/EIA-485A,

TIA/EIA-422-B, ITU-T v.11 and ISO 8482:1993

standard-compliant devices.

The SN65HVD50, SN65HVD51, and SN65HVD52

are fully enabled with no external enabling pins.

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2005–2009, Texas Instruments Incorporated

�SN65HVD50-SN65HVD55

SLLS666E – SEPTEMBER 2005 – REVISED OCTOBER 2009

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more

susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

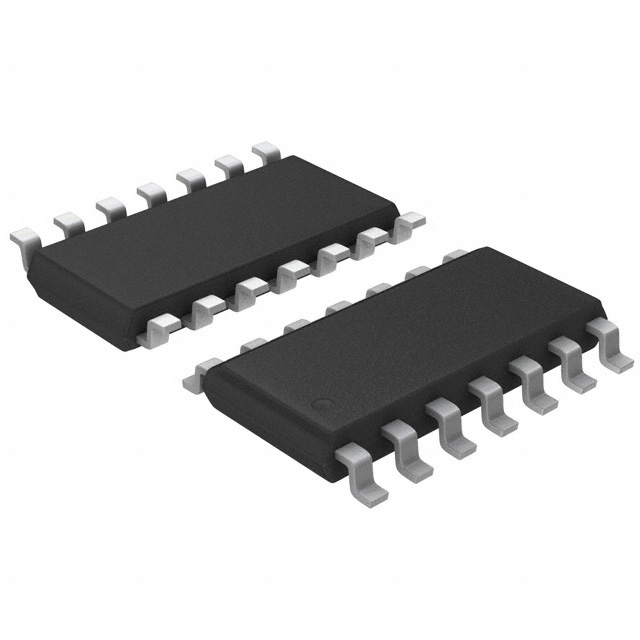

SN65HVD50, SN65HVD51, SN65HVD52

SN65HVD53, SN65HVD54, SN65HVD55

D PACKAGE (TOP VIEW)

VCC

R

D

GND

R

D

1

8

2

7

3

6

4

5

8

2

A

7

1

14

2

13

3

12

4

11

5

10

6

9

7

8

VCC

VCC

A

B

Z

Y

NC

NC - No internal connection

B

5

3

NC

R

RE

DE

D

GND

GND

A

B

Z

Y

Y

6

Z

AVAILABLE OPTIONS

SIGNALING RATE

UNIT LOADS

ENABLES

BASE

PART NUMBER

SOIC MARKING

25 Mbps

1/2

No

SN65HVD50

65HVD50

5 Mbps

1/8

No

SN65HVD51

65HVD51

1 Mbps

1/8

No

SN65HVD52

65HVD52

25 Mbps

1/2

Yes

SN65HVD53

65HVD53

5 Mbps

1/8

Yes

SN65HVD54

65HVD54

1 Mbps

1/8

Yes

SN65HVD55

65HVD55

ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted) (1)

(2)

UNIT

VCC

Supply voltage range

V(A), V(B), V(Y), V(Z)

Voltage range at any bus terminal (A, B, Y, Z)

–0.3 V to 6 V

–9 V to 14 V

V(TRANS)

Voltage input, transient pulse through 100 Ω. See Figure 12 (A, B, Y, Z)

VI

Voltage input range (D, DE, RE)

PD(cont)

Continuous total power dissipation

IO

Output current (receiver output only, R)

(1)

(2)

(3)

(4)

2

(3)

–50 to 50 V

-0.5 V to 7 V

Internally limited (4)

11 mA

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

This tests survivability only and the output state of the receiver is not specified.

The thermal shutdown typically occurs when the junction temperature reaches 165°C.

Submit Documentation Feedback

Copyright © 2005–2009, Texas Instruments Incorporated

Product Folder Link(s) :SN65HVD50-SN65HVD55

�SN65HVD50-SN65HVD55

www.ti.com

SLLS666E – SEPTEMBER 2005 – REVISED OCTOBER 2009

RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

MIN

VCC

Supply voltage

VI or VIC

Voltage at any bus terminal (separately or common mode)

1/tUI

Signaling rate

NOM

MAX

4.5

5.5

–7 (1)

12

SN65HVD50, SN65HVD53

25

SN65HVD51, SN65HVD54

5

SN65HVD52, SN65HVD55

1

Differential load resistance

VIH

High-level input voltage

D, DE, RE

2

VCC

VIL

Low-level input voltage

D, DE, RE

0

0.8

VID

Differential input voltage

-12

12

High-level output current

IOL

Low-level output current

TJ

(1)

(2)

(2)

Driver

V

Mbps

Ω

RL

IOH

54

UNIT

60

V

-60

Receiver

mA

–8

Driver

60

Receiver

mA

8

Junction temperature

–40

150

°C

The algebraic convention, in which the least positive (most negative) limit is designated as minimum is used in this data sheet.

See thermal characteristics table for information regarding this specification.

ELECTROSTATIC DISCHARGE PROTECTION

PARAMETER

TEST CONDITIONS

Human body model

Bus terminals and GND

Human body model (2)

Charged-device-model

(1)

(2)

(3)

(3)

MIN

TYP

(1)

MAX

UNIT

±16

All pins

±4

All pins

±1

kV

All typical values at 25°C and with a 5-V supply.

Tested in accordance with JEDEC Standard 22, Test Method A114-A.

Tested in accordance with JEDEC Standard 22, Test Method C101.

Copyright © 2005–2009, Texas Instruments Incorporated

Product Folder Link(s) :SN65HVD50-SN65HVD55

Submit Documentation Feedback

3

�SN65HVD50-SN65HVD55

SLLS666E – SEPTEMBER 2005 – REVISED OCTOBER 2009

www.ti.com

DRIVER ELECTRICAL CHARACTERISTICS

over recommended operating conditions unless otherwise noted

PARAMETER

VI(K)

TEST CONDITIONS

Input clamp voltage

II = –18 mA

4

2.6

RL = 100 Ω, See Figure 1 (RS-422)

2.4

3.2

Vtest = –7 V to 12 V, See Figure 2

1.6

Δ|VOD(SS)|

Change in magnitude of steady-state

differential output voltage between states

RL = 54 Ω, See Figure 1 and Figure 2

VOD(RING)

Differential Output Voltage overshoot

and undershoot

RL = 54 Ω, CL = 50 pF, See Figure 5

See Figure 3 for definition

VOC(PP)

Peak-to-peak

common-mode

output voltage

VOC(SS)

Steady-state common-mode

output voltage

IZ(Z) or IY(Z)

High-impedance state

output current

Short-circuit output current (3)

II

Input current

C(OD)

Differential output capacitance

4

V

0.5

See Figure 4

0.4

0.4

2.2

3.3

–0.1

0.1

See Figure 4

VCC = 0 V, VZ or VY = 12 V,

Other input at 0 V

VCC = 0 V, VZ or VY = –7 V,

Other input at 0 V

VCC = 5 V or 0 V,

DE = 0 V

VZ or VY = 12 V

VCC = 5 V or 0 V,

DE = 0 V

VZ or VY = –7 V

VZ or VY = –7 V

IZ(S) or IY(S)

UNIT

0.2

10% (2)

HVD52, HVD55

HVD53, HVD54,

HVD55

(1)

(2)

(3)

–0.2

HVD50, HVD53

HVD50, HVD51,

HVD52

MAX

VCC

1.7

Steady-state differential output voltage

Change in steady-state common-mode output

voltage

(1)

RL = 54 Ω, See Figure 1 (RS-485)

|VOD(SS)|

HVD51, HVD54

TYP

–1.5

IO = 0

ΔVOC(SS)

MIN

VZ or VY = 12 V

90

–10

90

μA

Other input

at 0 V

–10

Other input

at 0 V

D, DE

VOD = 0.4 sin (4E6πt) + 0.5 V,

DE at 0 V

–250

250

–250

250

0

100

16

mA

μA

pF

All typical values are at 25°C and with a 5-V supply.

10% of the peak-to-peak differential output voltage swing, per TIA/EIA-485

Under some conditions of short-circuit to negative voltages, output currents exceeding the ANSI TIA/EIA-485-A maximum current of 250

mA may occur. Continuous exposure may affect device reliability.

Submit Documentation Feedback

Copyright © 2005–2009, Texas Instruments Incorporated

Product Folder Link(s) :SN65HVD50-SN65HVD55

�SN65HVD50-SN65HVD55

www.ti.com

SLLS666E – SEPTEMBER 2005 – REVISED OCTOBER 2009

DRIVER SWITCHING CHARACTERISTICS

over recommended operating conditions unless otherwise noted

PARAMETER

Propagation delay time,

low-to-high-level output

tPLH

Propagation delay time,

high-to-low-level output

tPHL

Differential output signal

rise time

tr

TEST CONDITIONS

tsk(p)

tsk(pp)

tPZH1

(2)

Part-to-part skew

Propagation delay time,

high-impedance-to-highlevel output

Propagation delay time,

high-level-to-highimpedance output

tPHZ

tPZL1

tPZH2

tPZL2

MAX

8

12

HVD51, HVD54

20

29

46

HVD52, HVD55

90

143

230

HVD50, HVD53

4

8

12

HVD51, HVD54

20

30

46

HVD52, HVD55

90

143

230

HVD50, HVD53

3

6

12

HVD51, HVD54

20

34

60

120

197

300

3

6

11

HVD51, HVD54

20

33

60

HVD52, HVD55

120

192

300

RL = 54 Ω, CL = 50 pF,

See Figure 5

HVD50, HVD53

1.4

HVD51, HVD54

1.6

HVD52, HVD55

7.4

HVD50, HVD53

1

HVD51, HVD54

4

HVD52, HVD55

22

30

180

HVD53

HVD54

RL = 110 Ω, RE at 0 V,

See Figure 6

D = 3 V and S1 = Y,

D = 0 V and S1 = Z

ns

ns

ns

ns

380

16

40

HVD55

110

HVD53

Propagation delay time,

high-impedance-to-low-level HVD54

output

HVD55

23

RL = 110 Ω, RE at 0 V,

See Figure 7

D = 3 V and S1 = Z,

D = 0 V and S1 = Y

ns

ns

HVD54

HVD55

UNIT

ns

HVD53

HVD53

Propagation delay time,

low-level-to-high-impedance HVD54

output

HVD55

tPLZ

(1)

(2)

Pulse skew (|tPHL – tPLH|)

(1)

4

HVD50, HVD53

Differential output signal fall

time

TYP

HVD50, HVD53

HVD52, HVD55

tf

MIN

200

ns

ns

420

19

70

ns

160

Propagation delay time, standby-to-high-level output

RL = 110 Ω, RE at 3 V,

See Figure 6

D = 3 V and S1 = Y,

D = 0 V and S1 = Z

3300

ns

Propagation delay time, standby-to-low-level output

RL = 110 Ω, RE at 3 V,

See Figure 7

D = 3 V and S1 = Z,

D = 0 V and S1 = Y

3300

ns

All typical values are at 25°C and with a 5-V supply.

tsk(pp) is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices

operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

Copyright © 2005–2009, Texas Instruments Incorporated

Product Folder Link(s) :SN65HVD50-SN65HVD55

Submit Documentation Feedback

5

�SN65HVD50-SN65HVD55

SLLS666E – SEPTEMBER 2005 – REVISED OCTOBER 2009

www.ti.com

RECEIVER ELECTRICAL CHARACTERISTICS

over recommended operating conditions unless otherwise noted

PARAMETER

TEST CONDITIONS

VIT+

Positive-going differential input

threshold voltage

IO = –8 mA

VIT-

Negative-going differential input

threshold voltage

IO = 8 mA

Vhys

Hysteresis voltage (VIT+ - VIT-)

VIK

Enable-input clamp voltage

Output voltage

IO(Z)

High-impedance-state output

current

TYP

(1)

V

50

II = –18 mA

HVD51,

HVD52,

HVD54,

HVD55

IIH

Input current, RE

CID

Differential input capacitance

mV

–1.5

V

4

0.3

VO = 0 or VCC RE at VCC

–1

1

VA or VB = 12 V

0.19

0.3

VA or VB = 12 V, VCC = 0 V

0.24

0.4

VA or VB = -7 V

Other input

at 0 V

VA or VB = -7 V, VCC = 0 V

Bus input current

UNIT

–0.2

VID = –200 mV, IO = 8 mA, See Figure 8

HVD50,

HVD53,

MAX

–0.02

VID = 200 mV, IO = –8 mA, See Figure 8

VO

IA or IB

MIN

–0.35

–0.19

–0.25

–0.14

VA or VB = 12 V

VA or VB = 12 V, VCC = 0 V

VA or VB = -7 V

Other input

at 0 V

0.05

0.1

0.06

0.1

–0.1

–0.05

VA or VB = -7 V, VCC = 0 V

–0.1

–0.03

VIH = 2 V

–60

VIL = 0.8 V

–60

VID = 0.4 sin (4E6πt) + 0.5 V, DE at 0 V

V

μA

mA

mA

μA

μA

16

pF

Supply Current

HVD50

ICC

Supply current

D at 0 V or VCC and No Load

HVD53

HVD54,

HVD55

RE at 0 V, D at 0 V or VCC, DE at 0 V,

No load (Receiver enabled and

driver disabled)

HVD53,

HVD54,

HVD55

RE at VCC, D at VCC, DE at 0 V,

No load (Receiver disabled and

driver disabled)

HVD53

RE at 0 V, D at 0 V or VCC, DE at VCC,

No load (Receiver enabled and

driver enabled)

2.7

RE at VCC, D at 0 V or VCC, DE at VCC

No load (Receiver disabled and

driver enabled)

2.3

HVD54,

HVD55

HVD53

HVD54,

HVD55

(1)

6

2.7

HVD51,

HVD52

8

2.3

mA

2.9

0.08

1

μA

8

mA

7.7

All typical values are at 25°C and with a 5-V supply.

Submit Documentation Feedback

Copyright © 2005–2009, Texas Instruments Incorporated

Product Folder Link(s) :SN65HVD50-SN65HVD55

�SN65HVD50-SN65HVD55

www.ti.com

SLLS666E – SEPTEMBER 2005 – REVISED OCTOBER 2009

RECEIVER SWITCHING CHARACTERISTICS

over recommended operating conditions unless otherwise noted

(1)

MAX

HVD50, HVD53

24

40

HVD51, HVD52, HVD54,

HVD55

43

55

HVD50, HVD53

26

35

HVD51, HVD52, HVD54,

HVD55

47

60

PARAMETER

tPLH

Propagation delay time,

low-to-high-level output

tPHL

Propagation delay time,

high-to-low-level output

tsk(p)

Pulse skew (|tPHL - tPLH|)

tsk(pp)

(2)

TEST CONDITIONS

HVD50, HVD53

HVD51, HVD54

Part-to-part skew

MIN

TYP

VID = -1.5 V to 1.5 V,

CL = 15 pF,

See Figure 9

5

7

HVD50, HVD53

5

HVD51, HVD54

6

HVD52, HVD55

6

tr

Output signal rise time

2.3

tf

Output signal fall time

2.4

tPHZ

Output disable time from high level

tPZH1

Output enable time to high level

tPZH2

Propagation delay time, standby-to-high-level output

tPLZ

Output disable time from low level

tPZL1

Output enable time to low level

tPZL2

Propagation delay time, standby-to-low-level output

(1)

(2)

DE at 3 V, CL = 15 pF

See Figure 10

DE at 0 V, CL = 15 pF

See Figure 10

DE at 3 V, CL = 15 pF

See Figure 11

DE at 0 V, CL = 15 pF

See Figure 11

UNIT

ns

4

4

17

10

3300

13

10

3300

All typical values are at 25°C and with a 5-V supply

.tsk(pp) is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices

operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

Copyright © 2005–2009, Texas Instruments Incorporated

Product Folder Link(s) :SN65HVD50-SN65HVD55

Submit Documentation Feedback

7

�SN65HVD50-SN65HVD55

SLLS666E – SEPTEMBER 2005 – REVISED OCTOBER 2009

www.ti.com

THERMAL CHARACTERISTICS

over operating free-air temperature range unless otherwise noted (1)

PARAMETER

TEST CONDITIONS

Junction−to−ambient

thermal resistance (2)

Low-K board (3), No airflow

Junction−to−ambient

thermal resistance (2)

High-K board (4), No airflow

θJA

Junction−to−board

thermal resistance

θJB

High-K board

Junction−to−case

thermal resistance

θJC

PD

No board

Device power dissipation

(3)

(4)

162.6

HVD50, HVD51, HVD52

135.1

HVD53, HVD54, HVD55

92.1

HVD50, HVD51, HVD55

44.4

HVD53, HVD54, HVD55

61.1

HVD50, HVD51, HVD52

43.5

HVD53, HVD54, HVD55

58.6

UNIT

°C/W

RL= 60Ω, CL = 50 pF,

HVD53 (25Mbps)

DE at VCC RE at 0 V,

HVD54 (10Mbps)

Input to D a 50% duty cycle square

HVD55 (1Mbps)

wave at indicated signaling rate

420

High-K board, No airflow

(1)

(2)

HVD53, HVD54, HVD55

MAX

420

Ambient air temperature

TJSD

TYP

230.8

HVD50 (25Mbps)

RL= 60Ω, CL = 50 pF,

Input to D a 50% duty cycle square HVD51 (10Mbps)

wave at indicated signaling rate

HVD52 (1Mbps)

Low-K board, No airflow

TA

MIN

HVD50, HVD51, HVD52

404

383

mW

404

383

HVD50

–40

55

HVD51, HVD52

–40

84

HVD53, HVD54, HVD55

–40

85

HVD50, HVD51, HVD52

–40

85

HVD53, HVD54, HVD55

–40

Thermal shutdown junction temperature

°C

85

165

See Application Information section for an explanation of these parameters.

The intent of θJA specification is solely for a thermal performance comparison of one package to another in a standardized environment.

This methodology is not meant to and will not predict the performance of a package in an application-specific environment.

In accordance with the Low-K thermal metric definitions of EIA/JESD51-3.

In accordance with the High-K thermal metric definitions of EIA/JESD51-7.

PARAMETER MEASUREMENT INFORMATION

VCC

II

DE

375 Ω ±1%

VCC

Y

IY

DE

VOD

0 or 3 V

Z

RL

IZ

D

Y

VOD

0 or 3 V

60 Ω ±1%

+

_ −7 V < V(test) < 12 V

Z

VI

VZ

375 Ω ±1%

VY

Figure 1. Driver VOD Test Circuit: Voltage and

Current Definitions

8

Submit Documentation Feedback

Figure 2. Driver VOD With Common-Mode Loading

Test Circuit

Copyright © 2005–2009, Texas Instruments Incorporated

Product Folder Link(s) :SN65HVD50-SN65HVD55

�SN65HVD50-SN65HVD55

www.ti.com

SLLS666E – SEPTEMBER 2005 – REVISED OCTOBER 2009

PARAMETER MEASUREMENT INFORMATION (continued)

VOD(RING) is measured at four points on the output waveform, corresponding to overshoot and undershoot from

the VOD(H) and VOD(L) steady state values.

VOD(SS)

VOD(RING)

0 V Differential

VOD(RING)

-VOD(SS)

Figure 3. VOD(RING) Waveform and Definitions

VCC

DE

Input

D

27 Ω ± 1%

Y

Y

VY

Z

VZ

VOC(PP)

Z

27 Ω ± 1%

CL = 50 pF ±20%

VOC

∆VOC(SS)

VOC

CL Includes Fixture and

Instrumentation Capacitance

Input: PRR = 500 kHz, 50% Duty Cycle,t r