TPS25947

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

TPS25947xx, 2.7-V–23-V, 5.5-A, 28-mΩ True Reverse Current Blocking eFuse with

Input Reverse Polarity Protection

1 Features

3 Description

•

The TPS25947xx family of eFuses is a highly

integrated circuit protection and power management

solution in a small package. The devices provide

multiple protection modes using very few external

components and are a robust defense against

overloads, short-circuits, voltage surges, reverse

polarity and excessive inrush current. With integrated

back-to-back FETs, reverse current flow from output

to input is blocked at all times, making the devices

well suited for power MUX/ORing applications as

well as systems which need load side energy hold

up storage in case input power supply fails. The

devices use linear ORing based scheme to ensure

almost zero DC reverse current and emulate ideal

diode behavior with minimum forward voltage drop

and power dissipation.

•

•

•

•

•

•

•

•

•

•

•

•

Wide operating input voltage range: 2.7 V to 23 V

– 28-V absolute maximum

– Withstands negative voltages up to –15 V

Integrated back-to-back FETs with low onresistance: RON = 28.3 mΩ (typ.)

Ideal diode operation with true reverse current

blocking

Fast overvoltage protection

– Overvoltage clamp (OVC) with pin-selectable

threshold (3.8 V, 5.7 V, 13.8 V) and 5-μs (typ.)

response time OR

– Adjustable overvoltage lockout (OVLO) with

1.2-μs (typ.) response time

Overcurrent protection with load current monitor

output (ILM)

– Active current limit OR circuit-breaker options

– Adjustable threshold (ILIM) 0.5 A–6 A

• ±10% accuracy for ILIM > 1 A

– Adjustable transient blanking timer (ITIMER) to

allow peak currents up to 2 × ILIM

– Output load current monitor accuracy: ±6%

(IOUT ≥ 1 A)

Fast-trip response for short-circuit protection

– 500-ns (typ.) response time

– Adjustable (2 × ILIM) and fixed thresholds

Active high enable input with adjustable

undervoltage lockout threshold (UVLO)

Adjustable output slew rate control (dVdt)

Overtemperature protection

Digital outputs

– Priority power MUX control (AUXOFF) and fault

indication (FLT) or

– Power Good indication (PG) with adjustable

threshold (PGTH)

UL 2367 recognition

– File No. E339631

– RILM ≥ 750 Ω

IEC 62368-1 CB certified

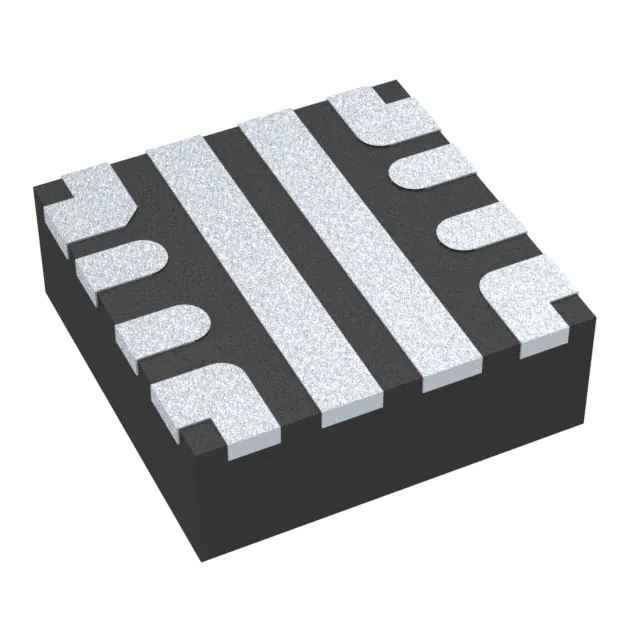

Small footprint: QFN 2 mm × 2 mm, 0.45-mm pitch

2 Applications

Output slew rate and inrush current can be adjusted

using a single external capacitor. Loads are protected

from input overvoltage conditions either by clamping

the output to a safe fixed maximum voltage (pin

selectable), or by cutting off the output if input

exceeds an adjustable overvoltage threshold. The

devices respond to output overload by actively limiting

the current or breaking the circuit. The output current

limit threshold as well as the transient overcurrent

blanking timer are user adjustable. The current limit

control pin also functions as an analog load current

monitor.

The devices are available in a 2-mm × 2-mm,

10-pin HotRod QFN package for improved thermal

performance and reduced system footprint.

The devices are characterized for operation over a

junction temperature range of –40°C to +125°C.

Device Information

PART NUMBER

PACKAGE(1)

BODY SIZE (NOM)

TPS25947xxRPW

QFN (10)

2 mm × 2 mm

(1)

For all available packages, see the orderable addendum at

the end of the data sheet.

VIN = 2.7 to 23 V

•

•

•

•

•

•

Power MUX/ORing

Adapter input protection

USB PD protection – PC, notebook, monitors,

docks

Server, PC motherboard, and add-on cards

Enterprise storage – RAID/HBA/SAN/eSSD

Patient monitors

VOUT

IN

OUT

VLOGIC

COUT

EN/UV LO

TPS25 9470x

AUXOFF

OVL O

FLT

ITIMER

CITIMER

dVd t

GND

CDVD T

ILM

R ILM

Simplified Schematic

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

Table of Contents

1 Features............................................................................1

2 Applications..................................................................... 1

3 Description.......................................................................1

4 Revision History.............................................................. 2

5 Device Comparison Table...............................................3

6 Pin Configuration and Functions...................................4

7 Specifications.................................................................. 6

7.1 Absolute Maximum Ratings........................................ 6

7.2 ESD Ratings............................................................... 6

7.3 Recommended Operating Conditions.........................7

7.4 Thermal Information....................................................7

7.5 Electrical Characteristics.............................................8

7.6 Timing Requirements................................................ 10

7.7 Switching Characteristics.......................................... 11

7.8 Typical Characteristics.............................................. 12

8 Detailed Description......................................................21

8.1 Overview................................................................... 21

8.2 Functional Block Diagram......................................... 22

8.3 Feature Description...................................................25

8.4 Device Functional Modes..........................................39

9 Application and Implementation.................................. 40

9.1 Application Information............................................. 40

9.2 Single Device, Self-Controlled.................................. 40

9.3 Typical Application.................................................... 41

9.4 Active ORing............................................................. 44

9.5 Priority Power MUXing..............................................46

9.6 USB PD Port Protection............................................53

9.7 Parallel Operation..................................................... 55

10 Power Supply Recommendations..............................58

10.1 Transient Protection................................................ 58

10.2 Output Short-Circuit Measurements....................... 59

11 Layout........................................................................... 60

11.1 Layout Guidelines................................................... 60

11.2 Layout Example...................................................... 61

12 Device and Documentation Support..........................63

12.1 Documentation Support.......................................... 63

12.2 Receiving Notification of Documentation Updates..63

12.3 Support Resources................................................. 63

12.4 Trademarks............................................................. 63

12.5 Electrostatic Discharge Caution..............................63

12.6 Glossary..................................................................63

13 Mechanical, Packaging, and Orderable

Information.................................................................... 64

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision A (March 2021) to Revision B (March 2022)

Page

• Updated the UIL/IEC certification status.............................................................................................................1

• Corrected the ESD Ratings to show CDM testing was per JS-002.................................................................... 6

• Updated image formatting................................................................................................................................ 12

• Updated Table 8-5 ........................................................................................................................................... 37

Changes from Revision * (October 2020) to Revision A (March 2021)

Page

• Changed status from "Advance Information" to "Production Data".....................................................................1

2

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

5 Device Comparison Table

Part Number

TPS259470ARPW

TPS259470LRPW

TPS259472ARPW

TPS259472LRPW

TPS259474ARPW

TPS259474LRPW

Overvoltage

Response

Overcurrent

Response

Adjustable OVLO

AUXOFF or PG

FLT or PGTH

AUXOFF

FLT

Auto-Retry

Latch-Off

Active Current Limit

Auto-Retry

Pin Selectable OVC

(3.8 V/5.7 V/13.8 V)

PG

Adjustable OVLO

Response to Fault

Circuit Breaker

PGTH

Latch-Off

Auto-Retry

Latch-Off

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

3

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

6 Pin Configuration and Functions

IN

OUT

EN/UVLO

1

10

OVLO/

OVCSEL

2

9

ILM

5

ITIMER

6

PG/

AUXOFF

3

8

GND

PGTH/

FLT

4

7

DVDT

Figure 6-1. TPS25947xx RPW Package 10-Pin QFN Top View

Table 6-1. Pin Functions

PIN

TYPE

DESCRIPTION

Analog

Input

Active High Enable for the device. A Resistor Divider on this pin from input supply to GND

can be used to adjust the Undervoltage Lockout threshold. Do not leave floating. Refer to

Section 8.3.2 for details.

Analog

Input

TPS259470x, TPS259474x: A Resistor Divider on this pin from supply to GND can be

used to adjust the Overvoltage Lockout threshold. This pin can also be used as an Active

Low Enable for the device. Do not leave floating. Refer to Section 8.3.3 for details.

OVCSEL

Analog

Input

TPS259472x: Overvoltage Clamp Threshold Select Pin. Refer to Section 8.3.4 for details.

PG

Digital

Output

TPS259472x, TPS259474x: Power Good indication. This pin is an Open Drain signal

which is asserted High when the internal powerpath is fully turned ON and PGTH input

exceeds a certain threshold. Refer to Section 8.3.11 for more details.

AUXOFF

Digital

Output

TPS259470x: Auxiliary channel control signal. This pin is an Open Drain signal which

is asserted High when the input supply is valid and channel has completed inrush

sequence. This can be used to enable/disable the auxiliary supply eFuse to facilitate

smooth switchover in a Priority power MUXing configuration. Refer to Section 8.3.10 for

more details.

FLT

Digital

Output

TPS259470x: Active low Fault event indicator. This pin is an Open Drain signal which will

be pulled low when a fault is detected. Refer to Section 8.3.9 for more details.

Analog

Input

TPS259472x, TPS259474x: Power Good Threshold. Refer to Section 8.3.11 for more

details.

NAME

NO.

EN/UVLO

1

OVLO

2

3

4

PGTH

4

IN

5

Power

Power input

OUT

6

Power

Power output

DVDT

7

Analog

Output

A capacitor from this pin to GND sets the output turn on slew rate. Leave this pin floating

for the fastest turn on slew rate. Refer to Section 8.3.5.1 for details.

GND

8

Ground

This pin is the ground reference for all internal circuits and must be connected to system

GND.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

Table 6-1. Pin Functions (continued)

PIN

TYPE

DESCRIPTION

NAME

NO.

ILM

9

Analog

Output

This pin is a dual function pin used to limit and monitor the output current. An external

resistor from this pin to GND sets the output current limit threshold during start-up as well

as steady state. The pin voltage can also be used as analog output load current monitor

signal. Do not leave floating. Refer to Section 8.3.5.2 or Section 8.3.5.3 for more details.

10

Analog

Output

A capacitor from this pin to GND sets the overcurrent blanking interval during which the

output current can temporarily exceed set current limit (but lower than fast-trip threshold)

before the device overcurrent response takes action. Leave this pin open for fastest

response to overcurrent events. Refer to Section 8.3.5.2 or Section 8.3.5.3 for more

details.

ITIMER

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

5

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

Parameter

Pin

Maximum Input Voltage Range, –40℃ ≤ TJ ≤ 125℃

VIN

IN

Maximum Input Voltage Range, –10℃ ≤ TJ ≤ 125℃

Maximum Output Voltage Range, –40℃ ≤ TJ ≤ 125℃

VOUT

Maximum Output Voltage Range, –10℃ ≤ TJ ≤ 125℃

MIN

MAX

max(–15, VOUT –

21)

28

V

max(–15, VOUT –

22)

28

V

–0.3

min (28, VIN + 21)

–0.3

min (28, VIN + 22)

OUT

UNIT

VOUT,PLS

Minimum Output Voltage Pulse (< 1 µs)

OUT

–0.8

VEN/UVLO

Maximum Enable Pin Voltage Range (2)

EN/UVLO

–0.3

6.5

V

(2)

OVLO

–0.3

6.5

V

VOVCSEL

Maximum OVCSEL Pin Voltage Range (TPS259472x)

OVCSEL

Internally Limited

V

VdVdT

Maximum dVdT Pin Voltage Range

dVdt

Internally Limited

V

VITIMER

Maximum ITIMER Pin Voltage Range

ITIMER

Internally Limited

V

VPGTH

(2)

PGTH

–0.3

6.5

V

VAUXOFF

Maximum AUXOFF Pin Voltage Range (TPS259470x)

AUXOFF

–0.3

6.5

V

VPG

Maximum PG Pin Voltage Range (TPS259472x/4x)

PG

–0.3

6.5

V

–0.3

6.5

V

VOVLO

Maximum OVLO Pin Voltage Range (TPS259470x/4x)

Maximum PGTH Pin Voltage Range (TPS259472x/4x)

(2)

VFLTB

Maximum FLT Pin Voltage Range (TPS259470x)

VILM

Maximum ILM Pin Voltage Range

ILM

Internally Limited

IMAX

Maximum Continuous Switch Current

IN to OUT

Internally Limited

A

TJ

Junction temperature

Internally Limited

°C

TLEAD

Maximum Lead Temperature

TSTG

Storage temperature

(1)

(2)

FLT

–65

V

300

°C

150

°C

Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply

functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions.

If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully

functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

If this pin has a pull-up up to VIN, it is recommended to use a resistance of 350 kΩ or higher to limit the current under conditions where

IN can be exposed to reverse polarity.

7.2 ESD Ratings

VALUE

V(ESD)

(1)

(2)

6

Electrostatic discharge

Human body model (HBM), per ANSI/ESDA/JEDEC

JS-001(1)

±2000

Charged device model (CDM), ANSI/ESDA/JEDEC JS-002(2)

±500

UNIT

V

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

Parameter

Pin

VIN

Input Voltage Range

IN

VOUT

Output Voltage Range

OUT

VEN/UVLO

Enable Pin Voltage Range

EN/UVLO

VOVLO

OVLO Pin Voltage Range (TPS259470x/4x)

OVLO

VdVdT

dVdt Capacitor Voltage Rating

dVdt

MIN

MAX

UNIT

2.7

23 (1)

V

min (23, VIN + 20)

V

5 (2)

V

1.5

V

0.5

VIN + 5 V (3)

V

(4)

V

VFLTB

FLT Pin Voltage Range (TPS259470x)

FLT

5

VPGTH

PGTH Pin Voltage Range (TPS259472x/4x)

PGTH

5 (4)

V

(4)

V

VAUXOFF

AUXOFF Pin Voltage Range (TPS259470x)

AUXOFF

5

VPG

PG Pin Voltage Range (TPS259472x/4x)

PG

5 (4)

V

VITIMER

ITIMER Pin Capacitor Voltage Rating

ITIMER

RILM

ILM Pin Resistance

ILM

549

6650

Ω

IMAX

Continuous Switch Current, TJ ≤ 125℃

IN to OUT

5.5

A

TJ

Junction temperature

–40

125

°C

(1)

(2)

(3)

(4)

4

V

For TPS259472x variants, the input operating voltage should be limited to the selected Output Voltage Clamp threshold as listed in the

Electrical Characteristics section

For supply voltages below 5V, it is okay to pull up the EN pin to IN directly. For supply voltages greater than 5V or systems which can

be exposed to reverse polarity on input supply, it is recommended to use a pull-up resistor with a minimum value of 350 kΩ.

In a PowerMUX/ORing scenario with unequal supplies, the dVdt capacitor rating for each device should be chosen based on the

highest of the 2 rails.

For systems which can be exposed to reverse polarity on input supply, if this pin is referred to input supply, it is recommended to use a

pull-up resistor with a minimum value of 350 kΩ to limit the current through the pin.

7.4 Thermal Information

TPS25947xx

THERMAL METRIC

(1)

RPW (QFN)

UNIT

10 PINS

RθJA

Junction-to-ambient thermal resistance

ΨJT

Junction-to-top characterization parameter

ΨJB

(1)

(2)

(3)

Junction-to-board characterization parameter

41.7 (2)

°C/W

74.5 (3)

°C/W

1

°C/W

20 (2)

27.6

(3)

°C/W

°C/W

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report.

Based on simulations conducted with the device mounted on a custom 4-layer PCB (2s2p) with 8 thermal vias under device

Based on simulations conducted with the device mounted on a JEDEC 4-layer PCB (2s2p) with no thermal vias under device

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

7

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

7.5 Electrical Characteristics

(Test conditions unless otherwise noted) –40°C ≤ TJ ≤ 125°C, VIN = 12 V, OUT = Open, VEN/UVLO = 2 V, VOVLO = 0 V for

TPS259470x/4x, OVCSEL = 390 kΩ to GND for TPS259472x, RILM = 549 Ω , dVdT = Open, ITIMER = Open, AUXOFF =

Open for TPS259470x, FLT = Open for TPS259470x, PGTH = Open for TPS259472x/4x, PG = Open for TPS259472x/4x. All

voltages referenced to GND.

Test

Parameter

Description

MIN

TYP

MAX

UNITS

V

INPUT SUPPLY (IN)

VUVP(R)

IN Supply UVP Rising threshold

2.44

2.53

2.64

VUVP(F)

IN Supply UVP Falling threshold

2.35

IQ(ON)

2.42

2.55

V

IN Supply Quiescent Current (TPS259470x)

428

610

µA

IN Supply Quiescent Current (TPS259472x)

426

610

µA

IN Supply Quiescent Current (TPS259474x)

428

610

µA

IN Supply Quiescent Current during RCB, VOUT = VIN + 1 V

193

IN Supply Current during OVC (TPS259472x)

445

µA

625

µA

IQ(OFF)

IN Supply disabled State Current (VSD(F) < VEN < VUVLO(F))

73

130

µA

ISD

IN Supply Shutdown Current (VEN < VSD(F))

4.4

28.7

µA

IQ(OVLO)

IN Supply OFF Current (OVLO condition), VOUT = VIN + 1 V

190

267

µA

IINLKG(IRPP)

IN Supply Leakage Current (VIN = –14 V, VOUT = 0 V)

–3.7

IOUTLKG(OVLO) OUT Leakage Current (OVLO condition), VOUT > VIN

319

µA

443

µA

ON RESISTANCE (IN - OUT)

VIN = 12 V, IOUT = 3 A, TJ = 25℃

RON

28.2

2.7 ≤ VIN ≤ 23 V, IOUT = 3 A, –40℃ ≤ TJ ≤ 125℃

mΩ

45

mΩ

ENABLE/UNDERVOLTAGE LOCKOUT (EN/UVLO)

VUVLO(R)

UVLO Rising threshold

1.183

1.20

1.223

V

VUVLO(F)

UVLO Falling threshold

1.076

1.09

1.116

V

VSD(F)

EN/UVLO Falling Threshold for lowest shutdown current

0.45

0.74

IENLKG

EN/UVLO leakage current

–0.1

V

0.1

µA

OVERVOLTAGE LOCKOUT (OVLO) - TPS259470x/4x

VOV(R)

OVLO Rising threshold

1.183

1.20

1.223

V

VOV(F)

OVLO Falling threshold

1.076

1.09

1.116

V

IOVLKG

OVLO pin leakage current, 0.5 V < VOVLO < 1.5 V

0.1

µA

–0.1

OUTPUT VOLTAGE CLAMP (OUT) - TPS259472x

VOVC

VCLAMP

Overvoltage Clamp Threshold, OVCSEL = Shorted to GND

3.65

3.88

4.1

V

Overvoltage Clamp Threshold, OVCSEL = Open

5.25

5.74

6.2

V

Overvoltage Clamp Threshold, OVCSEL = 390 kΩ to GND

13.2

13.85

14.5

V

Output Voltage During Clamping, OVCSEL = Shorted to

GND, IOUT = 10 mA

3.2

3.82

4.2

V

Output Voltage During Clamping, OVCSEL = Open, IOUT =

10 mA

5.0

5.68

6.12

V

13.0

13.79

14.6

V

Overcurrent Threshold, RILM = 6.65 kΩ

0.425

0.500

0.575

A

Overcurrent Threshold, RILM = 3.32 kΩ

0.850

1.007

1.150

A

Overcurrent Threshold, RILM = 1.65 kΩ

1.800

2.028

2.200

A

Overcurrent Threshold, RILM = 750 Ω

3.960

4.452

4.840

A

Overcurrent Threshold, RILM = 549 Ω

5.400

6.068

6.600

A

Output Voltage During Clamping, OVCSEL = 390 kΩ to

GND, IOUT = 10 mA

OVERCURRENT PROTECTION (OUT)

ILIM

8

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

7.5 Electrical Characteristics (continued)

(Test conditions unless otherwise noted) –40°C ≤ TJ ≤ 125°C, VIN = 12 V, OUT = Open, VEN/UVLO = 2 V, VOVLO = 0 V for

TPS259470x/4x, OVCSEL = 390 kΩ to GND for TPS259472x, RILM = 549 Ω , dVdT = Open, ITIMER = Open, AUXOFF =

Open for TPS259470x, FLT = Open for TPS259470x, PGTH = Open for TPS259472x/4x, PG = Open for TPS259472x/4x. All

voltages referenced to GND.

Test

Parameter

IFLT

Description

MIN

TYP

Circuit Breaker Threshold, ILM Pin Open (Single point

failure)

0.1

Circuit Breaker Threshold, ILM Pin Shorted to GND (Single

point failure)

1.1

MAX

UNITS

A

2.1

A

ISCGain

Scalable Fast Trip Threshold (ISC) : ILIM Ratio

201

%

IFT

Fixed Fast-trip current threshold

22.2

A

VFB

VOUT threshold to exit Current Limit Foldback

1.9

V

OVERCURRENT FAULT TIMER (ITIMER)

VINT

ITIMER pin internal pull-up voltage

RITIMER

ITIMER pin internal pull-up resistance

2.3

IITIMER

ITIMER pin internal discharge current, IOUT > ILIM

ΔVITIMER

ITIMER discharge differential voltage threshold

2.57

2.72

15

V

kΩ

1.2

1.8

2.5

µA

1.286

1.51

1.741

V

Analog Load Current Monitor Gain (IMON : IOUT), IOUT = 0.5 A

to 1 A, IOUT < ILIM

165

182

200

µA/A

Analog Load Current Monitor Gain (IMON : IOUT), IOUT = 1 A to

5.5 A, IOUT < ILIM

165

182

200

µA/A

4.7

16.9

–36.45

–29.3

–22.3

mV

83

104.1

125

mV

OUTPUT LOAD CURRENT MONITOR (ILM)

GIMON

REVERSE CURRENT BLOCKING (IN - OUT)

VFWD

VIN – VOUT Forward regulation voltage, IOUT = 10 mA

mV

VREVTH

VIN – VOUT threshold for fast BFET turn off (enter reverse

current blocking)

VFWDTH

VIN – VOUT threshold for fast BFET turn on (exit reverse

current blocking)

IREVLKG(OFF)

OUT Leakage Current during unpowered condition (VOUT =

12 V, VIN = 0 V)

4.86

µA

IREVLKG

Reverse leakage current, (VOUT – VIN) = 21.5 V

10.1

µA

IOUTLKG(RCB)

OUT Leakage Current during ON state with RCB, VOUT =

VIN + 1 V

234

µA

POWER GOOD INDICATION (PG) - TPS259472x/4x or AUXILIARY CHANNEL CONTROL (AUXOFF) - TPS259470x

VPGD

IPGLKG

PG/AUXOFF pin voltage while de-asserted. VIN < VUVP(F),

VEN < VSD(F), Weak pull-up (IPG = 26 μA)

0.67

1

V

PG/AUXOFF pin voltage while de-asserted, VIN < VUVP(F),

VEN < VSD(F), Strong pull-up (IPG = 242 μA)

0.79

1

V

PG/AUXOFF pin voltage while de-asserted, VIN > VUVP(R)

0

PG/AUXOFF Pin leakage current, PG/AUXOFF asserted

0.9

3

µA

V

POWERGOOD THRESHOLD (PGTH) - TPS259472x/4x

VPGTH(R)

PGTH Rising threshold

1.183

1.20

1.223

V

VPGTH(F)

PGTH Falling threshold

1.076

1.09

1.116

V

IPGTHLKG

PGTH leakage current

–0.1

0.3

µA

–1

1

µA

FAULT INDICATION (FLT) - TPS259470x

IFLTLKG

FLT leakage current

RFLT

FLT Internal Pull down resistance

12.3

Ω

154

°C

OVERTEMPERATURE PROTECTION (OTP)

TSD

Thermal Shutdown Rising Threshold, TJ↑

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

9

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

7.5 Electrical Characteristics (continued)

(Test conditions unless otherwise noted) –40°C ≤ TJ ≤ 125°C, VIN = 12 V, OUT = Open, VEN/UVLO = 2 V, VOVLO = 0 V for

TPS259470x/4x, OVCSEL = 390 kΩ to GND for TPS259472x, RILM = 549 Ω , dVdT = Open, ITIMER = Open, AUXOFF =

Open for TPS259470x, FLT = Open for TPS259470x, PGTH = Open for TPS259472x/4x, PG = Open for TPS259472x/4x. All

voltages referenced to GND.

Test

Parameter

TSDHYS

Description

MIN

TYP

Thermal Shutdown Hysteresis, TJ↓

MAX

10

UNITS

°C

DVDT

IdVdt

dVdt Pin Charging Current

0.81

2.21

3.82

µA

7.6 Timing Requirements

PARAMETER

TEST CONDITIONS

MIN

tOVLO

Overvoltage lock-out response time

(TPS259470x/4x)

VOVLO > VOV(R) to VOUT↓

tOVC

Overvoltage clamp response time

(TPS259472x)

VIN > VOVC to VOUT↓

tCB

Circuit-Breaker response time (TPS259474x) IOUT > 1.2 × ILIM & ITIMER expired to IOUT↓

tLIM

I

> 1.2 × ILIM & ITIMER expired to IOUT

Current limit response time (TPS259470x/2x) OUT

settling to within 5 % of ILIM

tSC

Scalable fast-trip response time

tFT

Fixed fast-trip response time

tRST

Auto-Retry Interval after fault (TPS25947xA)

tSWOV

OVLO fast recovery response

time (TPS259470x)

tSWRCB

TYP MAX

UNIT

1.2

µs

5

µs

2

µs

400

µs

IOUT > 3 × ILIM to IOUT↓

500

ns

IOUT > IFT to IOUT↓

500

ns

110

ms

VOVLO < VOV(F) to VOUT↑

90

µs

Reverse Current Blocking recovery time

(VIN – VOUT) > VFWDTH to VOUT ↑

50

µs

tRCB

Reverse Current Blocking comparator

response time

(VOUT – VIN) > 1.3 × VREVTH to BFET OFF

1

µs

tPGA

PG Assertion de-glitch (TPS259472x/4x)

12

µs

tPGD

PG De-assertion de-glitch (TPS259472x/4x)

12

µs

10

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

7.7 Switching Characteristics

The output rising slew rate is internally controlled and constant across the entire operating voltage range to ensure the

turn on timing is not affected by the load conditions. The rising slew rate can be adjusted by adding capacitance from

the dVdt pin to ground. As CdVdt is increased it will slow the rising slew rate (SR). See Slew Rate and Inrush Current

Control (dVdt) section for more details. The Turn-Off Delay and Fall Time, however, are dependent on the RC time constant

of the load capacitance (COUT) and Load Resistance (RL). The Switching Characteristics are only valid for the power-up

sequence where the supply is available in steady state condition and the load voltage is completely discharged before the

device is enabled.Typical Values are taken at TJ = 25°C unless specifically noted otherwise. RL = 100 Ω, COUT = 1 µF

PARAMETER

SRON

tD,ON

tR

tON

tD,OFF

VIN

Output Rising slew rate

Turn on delay

Rise time

Turn on time

Turn off delay

CdVdt = Open

CdVdt = 1800 pF

CdVdt =

3300 pF

2.7 V

12.14

0.87

0.5

12 V

28.1

1.09

0.61

23 V

44.78

1.25

0.71

2.7 V

0.09

0.6

0.97

12 V

0.1

1.32

2.35

23 V

0.11

1.99

3.69

2.7 V

0.17

2.51

4.33

12 V

0.35

8.1

15.37

23 V

0.40

14.4

25.89

2.7 V

0.27

3.11

5.31

12 V

0.45

10.08

17.72

23 V

0.50

16.41

29.57

2.7 V

64.44

64.44

64.44

12 V

25.32

25.32

25.32

23 V

23.02

23.02

23.02

UNIT

V/ms

ms

ms

ms

µs

VEN/UVLO

VUVLO(R)

EN/UVLO

VUVLO(F)

0

tD,OFF

tON

VIN

90%

SRON

OUT

0V

10%

tR

tD,ON

tF

Time

Figure 7-1. TPS25947xx Switching Times

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

11

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

7.8 Typical Characteristics

30.9

IOUT (A)

1

3

4

5.5

30.6

30.3

RON (m:)

30

29.7

29.4

29.1

28.8

28.5

28.2

27.9

2.5

5

7.5

10

12.5 15

VIN (V)

17.5

20

22.5

25

D007

Figure 7-3. Forward Voltage Drop vs Load Current

Figure 7-2. ON-Resistance vs Supply Voltage

445

480

VIN (V)

3.3

5

12

440

460

435

430

425

VIN (V)

2.7

5

12

23

420

400

IQ(ON) (PA)

IQ(ON) (PA)

440

420

415

410

405

380

400

360

395

340

-40

385

-40

390

-20

0

20

40

60

TA (qC)

80

100

120

140

Figure 7-4. IN Quiescent Current vs Temperature (TPS259470x,

TPS2594704x Variants)

12

40

60

TA (qC)

80

100

120

140

D012

10

VIN (V)

2.7

5

12

23

80

75

8

6

70

4

65

2

60

55

-40

-20

0

20

40

60

TA (qC)

80

100

120

140

0

-40

-20

D014

Figure 7-6. IN OFF State (UVLO) Current vs Temperature

12

20

14

VIN (V)

2.7

5

12

23

ISD (PA)

IQ(OFF) (PA)

85

0

Figure 7-5. IN Quiescent Current vs Temperature (TPS259472x

Variant)

95

90

-20

D011

0

20

40

60

TA (qC)

80

100

120

140

D013

Figure 7-7. IN Shutdown Current vs Temperature

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

7.8 Typical Characteristics (continued)

1.204

VIN (V)

2.7

5

12

23

VUVLO(R) (V)

1.203

1.202

1.201

1.2

-40

Figure 7-8. IN Undervoltage Threshold vs Temperature

0

20

40

60

TA (C)

80

100

120

140

Figure 7-9. EN/UVLO Rising Threshold vs Temperature

0.825

1.097

VIN (V)

2.7

5

12

23

1.095

VIN (V)

2.7

5

12

23

0.8

0.775

0.75

VSD(F) (V)

1.096

VUVLO(F) (V)

-20

0.725

0.7

0.675

0.65

0.625

1.094

0.6

0.575

1.093

-40

-20

0

20

40

60

TA (C)

80

100

120

0.55

-40

140

Figure 7-10. EN/UVLO Falling Threshold vs Temperature

20

40

60

TA (C)

80

100

120

140

1.097

VIN (V)

2.7

12

23

1.202

1.201

VIN (V)

2.7

12

23

1.096

VOV(F) (V)

1.203

VOV(R) (V)

0

Figure 7-11. EN/UVLO Shutdown Falling Threshold vs

Temperature

1.204

1.2

-40

-20

1.095

1.094

-20

0

20

40

60

TA (C)

80

100

120

140

Figure 7-12. OVLO Rising Threshold vs Temperature

1.093

-40

-20

0

20

40

60

TA (C)

80

100

120

140

Figure 7-13. OVLO Falling Threshold vs Temperature

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

13

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

7.8 Typical Characteristics (continued)

7000

18

Min

Max

6000

12

ILIM error (%)

5000

ILIM (A)

4000

3000

2000

0

-6

-12

1000

0

0.5

6

-18

1

1.5

2

2.5

3

3.5 4 4.5

RILM (k:)

5

5.5

6

6.5

7

0

Figure 7-14. Overcurrent Threshold vs ILM Resistor

ISFT/ILIM Ratio (%)

GIMON error (%)

5000

6000

VIN (V)

2.7

5

12

23

202.5

6

4

2

0

-2

202

201.5

201

200.5

-4

-6

200

-40

1

1.5

2

2.5

3

3.5

4

4.5

5

5.5

IOUT (A)

Figure 7-16. Analog Current Monitor Gain Accuracy

-20

0

20

40

60

TA (C)

80

100

120

140

Figure 7-17. Scalable Fast-Trip Threshold: Current Limit

Threshold (ILIM) Ratio vs Temperature

20

26

VIN (V)

2.7

5

12

23

25

24

19.5

19

VFWD (mV)

23

IFT (A)

3000

4000

ILIM (mA)

203

Min

Max

8

22

21

20

VIN (V)

2.7

5

12

23

18.5

18

17.5

19

17

18

17

-40

2000

Figure 7-15. Overcurrent Threshold Accuracy (Across Process,

Voltage and Temperature)

10

-8

0.5

1000

D005

16.5

-40

-20

0

20

40

60

TA (qC)

80

100

120

140

D030

-20

0

20

40

60

TA (C)

80

100

120

140

Figure 7-19. RCB - Forward Regulation Voltage vs Temperature

Figure 7-18. Steady State Fixed Fast-Trip Current Threshold vs

Temperature

14

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

7.8 Typical Characteristics (continued)

120

-28.5

VIN (V)

2.7

5

12

23

-29

115

-30

VFWDTH (mV)

VREVTH (mV)

-29.5

-30.5

-31

VIN (V)

2.7

5

12

23

-31.5

-32

-32.5

-40

-20

0

20

40

60

TA (C)

80

100

120

110

105

100

95

-40

140

-20

0

20

40

60

TA (C)

80

100

120

140

Figure 7-20. RCB - Reverse Comparator Threshold vs

Temperature

Figure 7-21. RCB - Forward Comparator Threshold vs

Temperature

Figure 7-22. OUT Leakage Current During ON-State Reverse

Current Blocking

Figure 7-23. Reverse Leakage Current During OFF-State

14

14

13

13.95

OVCSEL

GND

OPEN

392 k: to GND

11

VOVC (V)

10

13.9

13.85

VCLAMP (V)

12

TA (C)

-40

25

85

105

125

9

8

7

13.8

13.75

13.7

13.65

6

13.6

5

13.55

4

13.5

3

-40

0

-20

0

20

40

60

TA (qC)

80

100

120

140

D038

Figure 7-24. OVC Threshold vs Temperature

100

200

300

400 500 600

IOUT (mA)

700

800

900 1000

Figure 7-25. OVC Clamping Voltage (OVCSEL = 392 kΩ to GND)

vs Load Current

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

15

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

7.8 Typical Characteristics (continued)

4

5.85

3.95

3.9

VCLAMP (V)

3.85

3.8

3.75

5.75

5.55

5.5

5.45

100

200

300

400 500 600

IOUT (mA)

700

800

900 1000

Figure 7-26. OVC Clamping Voltage (OVCSEL = GND) vs Load

Current

0

1.514

1.82

1.815

IITIMER (PA)

1.51

1.508

700

800

900 1000

1.81

1.805

1.795

1.504

1.79

1.502

-40

-20

0

20

40

60

TA (qC)

80

100

120

1.785

-40

140

-20

0

20

D041

Figure 7-28. ITIMER Discharge Differential Voltage Threshold vs

Temperature

40

60

TA (qC)

80

100

120

140

D043

Figure 7-29. ITIMER Discharge Current vs Temperature

3

18.5

VIN (V)

2.7

5

12

23

2.9

2.8

2.7

VINT (V)

16.5

16

15.5

15

VIN (V)

2.7

5

12

23

2.6

2.5

2.4

2.3

14.5

2.2

14

2.1

13.5

13

-40

400 500 600

IOUT (mA)

1.8

1.506

17

300

VIN (V)

2.7

5

12

23

1.825

1.512

17.5

200

1.83

VIN (V)

2.7

5

12

23

1.516

18

100

Figure 7-27. OVC Clamping Voltage (OVCSEL = Open) vs Load

Current

1.518

'VITIMER (V)

5.6

3.7

0

RITIMER (k:)

5.7

5.65

3.65

3.6

-20

0

20

40

60

TA (qC)

80

100

120

140

D044

Figure 7-30. ITIMER Internal Pullup Resistance vs Temperature

16

TA (C)

-40

25

85

105

125

5.8

VCLAMP (V)

TA (C)

-40

25

85

105

125

2

-40

-20

0

20

40

60

TA (C)

80

100

120

140

Figure 7-31. ITIMER Internal Pullup Voltage vs Temperature

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

7.8 Typical Characteristics (continued)

2.7

VIN (V)

2.7

5

12

23

2.6

IDVDT (PA)

2.5

2.4

2.3

2.2

2.1

2

1.9

-40

-20

0

20

40

60

TA (qC)

80

100

120

140

D029

Figure 7-33. PGTH Threshold vs Temperature

Figure 7-32. DVDT Charging Current vs Temperature

0.9

19

IPG (A)

26

242

0.85

18

17

16

0.75

RFLTB (:)

VPGD (V)

0.8

0.7

0.65

15

14

13

0.6

12

0.55

11

0.5

-40

VIN (V)

2.7

12

23

10

-20

0

20

40

60

TA (C)

80

100

120

140

9

-40

-20

0

20

40

60

TA (qC)

80

100

120

140

Figure 7-34. PG Low Voltage Without Input Supply vs

Temperature

Figure 7-35. FLTb Pin Pulldown Resistance vs Temperature

Figure 7-36. Time to Thermal Shut-Down During Inrush State

Figure 7-37. Time to Thermal Shut-Down During Steady State

D028

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

17

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

7.8 Typical Characteristics (continued)

VIN

VOUT

EN

IIN

VIN = 12 V, COUT = 30 μF, CdVdt = Open, VEN/UVLO stepped up

to 1.4 V

Figure 7-38. Start-Up with Enable

VEN/UVLO = 3.3 V, COUT = 30 μF, CdVdt = Open, VIN ramped up

to 12 V

Figure 7-39. Start-Up with Supply

EN

VOUT

PG

IIN

COUT = 220 μF, CdVdt = 10 nF, EN/UVLO connected to IN

through resistor ladder, 12 V hot-plugged to IN

Figure 7-40. Input Hot-Plug

VIN = 12 V, COUT = 470 μF, CdVdt = 3300 pF, VEN/UVLO stepped

up to 1.4 V

Figure 7-41. Inrush Current with Capacitive Load

VIN

VIN

VOUT

VOUT

PG

PG

IIN

VIN = 12 V, COUT = 470 μF, ROUT = 5 Ω, CdVdt = 3300 pF,

VEN/UVLO stepped up to 1.4 V

COUT = 220 μF, PG pulled up to 3 V, -15 V hot-plugged to IN

Figure 7-43. Input Reverse Polarity Protection - Fast Ramp

Figure 7-42. Inrush Current with Resistive and Capacitive Load

18

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

7.8 Typical Characteristics (continued)

VIN

VIN

VOUT

VOUT

OVLO

PG

IIN

COUT = 220 μF, PG pulled up to 3 V, VIN ramped down from 0

V to -15 V and then ramped up to 0 V

Figure 7-44. Input Reverse Polarity Protection - Slow Ramp

COUT = 220 μF, ROUT = 20 Ω, VIN Overvoltage threshold set to

13.2 V, VIN ramped up from 12 V to 16 V

Figure 7-45. Overvoltage Lockout Response - TPS259470x/4x

VIN

VOUT

VIN

VOUT

PG

PG

ROVCSEL = GND, COUT = 220 μF, IOUT = 120 mA, VIN ramped

up from 3.3 V to 6 V

Figure 7-46. Overvoltage Clamp Response - TPS259472x

ROVCSEL = Open, COUT = 220 μF, IOUT = 150 mA, VIN ramped

up from 5 V to 8 V

Figure 7-47. Overvoltage Clamp Response - TPS259472x

VIN

VOUT

VIN

VOUT

IIN

PG

FLTb

ROVCSEL = 390 kΩ, COUT = 220 μF, IOUT = 300 mA, VIN

ramped up from 12 V to 16.5 V

Figure 7-48. Overvoltage Clamp Response - TPS259472x

VIN = 12 V, CITIMER = 2.2 nF, COUT = 220 μF, RILM = 549 Ω,

IOUT stepped from 3 A → 9 A → 3 A within 5 ms

Figure 7-49. Active Current Limit Response - TPS259470x

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

19

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

7.8 Typical Characteristics (continued)

VIN

VOUT

VIN

VOUT

ITIMER

IIN

FLTb

IIN

VIN = 12 V, CITIMER = 2.2 nF, COUT = 220 μF, RILM = 549 Ω,

IOUT stepped from 3 A → 9 A

VIN = 12 V, CITIMER = 2.2 nF, COUT = 470 μF, RILM = 549 Ω,

IOUT ramped from 4 A → 8 A→ 4 A within 1 ms

Figure 7-50. Active Current Limit Response Followed by TSD TPS259470x

Figure 7-51. Transient Overcurrent Blanking Timer Response TPS259474x

VIN

VIN

VOUT

VOUT

PG

IIN

IOUT

VIN = 12 V, CITIMER = 2.2 nF, COUT = 470 μF, RILM = 549 Ω,

IOUT ramped from 4 A → 8 A

VIN = 12 V, RILM = 549 Ω, VEN/UVLO = 3.3 V, OUT stepped from

Open → Short-circuit to GND

Figure 7-52. Circuit Breaker Response - TPS259474x

Figure 7-53. Output Short-Circuit During Steady State

VIN

VIN

VOUT

VOUT

FLTb

IOUT

IIN

VIN = 12 V, RILM = 549 Ω, VEN/UVLO = 3.3 V, OUT stepped from

Open → Short-circuit to GND

Figure 7-54. Output Short-Circuit During Steady State (Zoomed

In)

20

VIN = 12 V, COUT = Open, OUT short-circuit to GND, RILM =

1650 Ω, VEN/UVLO stepped from 0 V to 3.3 V

Figure 7-55. Power Up into Short-Circuit

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

8 Detailed Description

8.1 Overview

The TPS25947xx is an eFuse with integrated power path that is used to ensure safe power delivery in a system.

The device starts its operation by monitoring the IN bus. When the input supply voltage (VIN) exceeds the

Undervoltage Protection threshold (VUVP), the device samples the EN/UVLO pin. A high level (> VUVLO) on

this pin enables the internal power path (BFET+HFET) to start conducting and allow current to flow from IN to

OUT. When EN/UVLO is held low (< VUVLO), the internal power path is turned off. In case of reverse voltages

appearing at the input, the power path remains OFF thereby protecting the output load.

After a successful start-up sequence, the device now actively monitors its load current and input voltage, and

controls the internal HFET to ensure that the user adjustable overcurrent limit threshold (ILIM) is not exceeded

and overvoltage spikes are either safely clamped to the selected threshold voltage (VOVC) or cut-off after they

cross the user adjustable overvoltage lockout threshold (VOVLO). The device also provides fast protection against

severe overcurrent during short-circuit events. This keeps the system safe from harmful levels of voltage and

current. At the same time, a user adjustable overcurrent blanking timer allows the system to pass moderate

transient peaks in the load current profile without tripping the eFuse. This ensures a robust protection solution

against real faults which is also immune to transients, thereby ensuring maximum system uptime.

The device has integrated reverse current blocking FET (BFET) which operates like an ideal diode. The BFET

is linearly regulated to maintain a small constant forward drop (VFWD) in forward conduction mode and turned off

completely to block reverse current if output voltage exceeds the input voltage.

The device also has a built-in thermal sensor based shutdown mechanism to protect itself in case the device

temperature (TJ) exceeds the recommended operating conditions.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

21

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

8.2 Functional Block Diagram

FFT

TPS25 9470x

-

+

-

+

16.9 mV

353 .9 mV

Temp S ense &

Overtemperature

protection

IN

TSD

6

OUT

7

DVDT

9

ILM

10

ITIMER

8

GND

5

INRUSH_DONE

BFET

HFE T

IRP P

CP

2.8 V

+

2.53 V9

2

1.20 V9

SC

HFE T Control

+

OC

UVLOb

-

1x

+

SWEN

SD

+

TSD

R

S

/Q

Q

110 ms

TIMER #

ILM Pin Sh ort

1.06 V; 2.57 V

15 kŸ

SD

UVPb

RETRY #

Sho rt

Detect

INRUSH_DONE

UVLOb

OVL Ob

RETRY #

INRUSH_DONE

ITIMER_EXPIRED

1.09 V;

0.74 V;

2x

-

1.20 V9

+

BFET Con trol

Curren t Limit Amplifier

+

1

FFT

GHI

OVL Ob

1.09 V;

EN/UV LO

A/A

GHI

RCB

-

OVL O

UVPb

-

2.42 V;

-

+

A

+

ITIMER_EXPIRED

FLT

-

ILM Pin Sh ort

RCB

ITIMER_EXPIRED

OC

A

4

3

FLT

AUXOFF

# Not appl icab le to Latch-off variants (TPS 259470 L)

Figure 8-1. TPS259470x Block Diagram

22

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

FFT

TPS25 9472x

-

+

-

+

16.9 mV

353 .9 mV

Temp S ense &

Overtemperature

protection

IN

TSD

5

6

OUT

7

DVDT

9

ILM

INRUSH_DONE

BFET

HFE T

IRP P

CP

-

2.42 V;

FFT

OVC

2

OVC Threshold

Sele ct

A/A

GHI

+

OVCSE L

-

A

UVPb

+

+

2.53 V9

2.8 V

GHI

-

SC

RCB

HFE T Control

+

BFET Con trol

Curren t Limit Amplifier

+

1

1.20 V9

OC

UVLOb

+

PG_ int

INRUSH_DONE

SD

ITIMER_EXPIRED

SWEN

Sho rt

Detect

ILM Pin Sh ort

1.06 V; 2.57 V

TSD

R

+

ITIMER_EXPIRED

/Q

RCB

PG_ int

S

Q

15 kŸ

OVC

INRUSH_DONE

SD

UVPb

RETRY #

1x

+

1.09 V;

0.74 V;

-

-

EN/UV LO

2x

10

-

FLT

ITIMER

OC

PG_ int

ILM Pin Sh ort

A

R

S

Q

/Q

8

GND

+

110 ms

TIMER #

-

RETRY #

1.2 V9

1.09 V;

3

4

PG

PGTH

# Not appl icab le to Latch-off variants (TPS 259472 L)

Figure 8-2. TPS259472x Block Diagram

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

23

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

FFT

TPS25 9474x

-

+

-

+

16.9 mV

353 .9 mV

Temp S ense &

Overtemperature

protection

IN

TSD

5

6

OUT

7

DVDT

9

ILM

10

ITIMER

8

GND

INRUSH_DONE

BFET

HFE T

IRP P

CP

2.8 V

+

UVPb

2.42 V;

1.20 V9

GHI

SC

OVL Ob

HFE T Control

+

2

Curren t Limit Amplifier

+

1.20 V9

2x

OC

UVLOb

-

1x

+

-

1

+

BFET Con trol

1.09 V;

EN/UV LO

FFT

RCB

-

OVL O

A/A

GHI

-

2.53 V9

-

+

A

1.09 V;

SWEN

Sho rt

Detect

INRUSH_DONE

SD

-

ILM Pin Sh ort

+

0.74 V;

PG_ int

1.06 V; 2.57 V

INRUSH_DONE

15 kŸ

+

SD

UVPb

RETRY #

R

/Q

ITIMER_EXPIRED

RCB

PG_ int

TSD

ILM Pin Sh ort

S

Q

-

FLT

PG_ int

ITIMER_EXPIRED

OC

A

R

S

Q

/Q

+

110 ms

TIMER #

-

RETRY #

1.2 V9

1.09 V;

3

4

PG

PGTH

# Not appl icab le to Latch-off variants (TPS 259474 L)

Figure 8-3. TPS259474x Block Diagram

24

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

8.3 Feature Description

The TPS25947xx eFuse is a compact, feature rich power management device that provides detection, protection

and indication in the event of system faults.

8.3.1 Input Reverse Polarity Protection

The TPS25947xx device is internally protected against steady state negative voltages applied at the input supply

pin. The device blocks the negative voltage from appearing at the output, thereby protecting the load circuits.

There’s no reverse current flowing from output to the input in this condition. The lowest negative voltage the

device can handle at the input is limited to -15 V or VOUT – 21 V, whichever is higher. It’s also recommended

that all signal pins (e.g. EN/UVLO, OVLO, PGTH) which are connected to input supply must have a sufficiently

large pull-up resistor to limit the current flowing out of these pins during reverse polarity conditions. Please refer

to Absolute Maximum Ratings table for more details.

8.3.2 Undervoltage Lockout (UVLO and UVP)

The TPS25947xx implements Undervoltage Protection on IN in case the applied voltage becomes too low for the

system or device to properly operate. The Undervoltage Protection has a default lockout threshold of VUVP which

is fixed internally. Also, the UVLO comparator on the EN/UVLO pin allows the Undervoltage Protection threshold

to be externally adjusted to a user defined value. The Figure 8-4 and Equation 1 show how a resistor divider can

be used to set the UVLO set point for a given voltage supply.

Power

Supply

IN

R1

EN/UVLO

R2

GND

Figure 8-4. Adjustable Undervoltage Protection

VIN(UV) =

VUVLO × (R1 + R2)

R2

(1)

8.3.3 Overvoltage Lockout (OVLO)

The TPS259470x/4x variants allow the user to implement Overvoltage Lockout to protect the load from input

overvoltage conditions. The OVLO comparator on the OVLO pin allows the Overvoltage Protection threshold to

be adjusted to a user defined value. After the voltage at the OVLO pin crosses the OVLO rising threshold VOV(R),

the device turns off the power to the output. Thereafter, the devices wait for the voltage at the OVLO pin to

fall below the OVLO falling threshold VOV(F) before the output power is turned ON again. The rising and falling

thresholds are slightly different to provide hysterisis. The Figure 8-5 and Equation 2 show how a resistor divider

can be used to set the OVLO set point for a given voltage supply.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

25

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

Power

Supply

IN

R1

OVLO

R2

GND

Figure 8-5. Adjustable Overvoltage Protection

VIN(OV) =

VOV × (R1 + R2)

R2

(2)

While recovering from a OVLO event, the TPS259470x variants bypass the inrush control (dVdt) and start up in

a current limited manner to provide faster turn ON and minimize power supply droop.

Input Overvoltage Event

Input Overvoltage Removed

IN

0

VOV(R)

VOV(F)

OVLO

tOVLO

0

tSWOV

OUT

Current Limited

Start-up

0

VFLT

FLT

0

VAUXOFF

AUXOFF

0

Time

Figure 8-6. TPS259470x Overvoltage Lockout and Recovery

While recovering from a OVLO event, the TPS259474x variants start up with inrush control (dVdt).

26

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

Input Overvoltage Event

Input Overvoltage Removed

IN

0

OVLO

VOV(R)

VOV(F)

tOVLO

0

dVdt Limited

Start-up

OUT

0

tPGA

tPGD

VPG

PG

0

Time

Figure 8-7. TPS259474x Overvoltage Lockout and Recovery

8.3.4 Overvoltage Clamp (OVC)

The TPS259472x variants implement a voltage clamp on the output to protect the system in the event of input

overvoltage. When the device detects the input has exceeded the Overvoltage Clamp Threshold (VOVC), it

quickly responds within tOVC and stops the output from rising further and then regulates the HFET linearly to

clamp the output voltage below VCLAMP as long as an overvoltage condition is present on the input.

If the part stays in clamping state for an extended period of time, there is a higher power dissipation inside the

part which can eventually lead to thermal shut-down (TSD). After the part shuts down due to TSD fault, it can

either stay latched off (TPS259472L variant) or restart automatically after a fixed delay (TPS259472A variant).

See Overtemperature Protection (OTP) for more details on device response to overtemperature.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

27

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

Input Overvoltage Event

IN

Input Overvoltage Removed

VOVC

Thermal

Shutdown

Retry Timer Expired (1)

0

tOVC

tRST

VCLAMP

dVdt Limited

Start-up

OUT

0

tPGA

tPGD

VPG

PG

0

TSD

TSDHY S

TJ

(1)

Time

Applicable only for TPS259472A (Auto-retry variant)

Figure 8-8. TPS259472x Overvoltage Response (Auto-Retry)

There are 3 available overvoltage clamp threshold options which can be configured using the OVCSEL pin.

Table 8-1. TPS259472x Overvoltage Clamp Threshold Selection

OVCSEL Pin Connection

Overvoltage Clamp Threshold

Shorted to GND

3.8 V

Open

5.7 V

Connected to GND through a 390-kΩ resistor

13.8 V

8.3.5 Inrush Current, Overcurrent, and Short Circuit Protection

TPS25947xx incorporates four levels of protection against overcurrent:

1.

2.

3.

4.

Adjustable slew rate (dVdt) for inrush current control

Adjustable threshold (ILIM) for overcurrent protection during start-up or steady-state

Adjustable threshold (ISC) for fast-trip response to severe overcurrent during start-up or steady-state

Fixed threshold (IFT) for fast-trip response to quickly protect against hard output short-circuits during steadystate

8.3.5.1 Slew Rate (dVdt) and Inrush Current Control

During hot-plug events or while trying to charge a large output capacitance at start-up, there can be a large

inrush current. If the inrush current is not managed properly, it can damage the input connectors and/or cause

the system power supply to droop leading to unexpected restarts elsewhere in the system. The inrush current

during turn-on is directly proportional to the load capacitance and rising slew rate. Equation 3 can be used to find

the slew rate (SR) required to limit the inrush current (IINRUSH) for a given load capacitance (COUT):

SR (V/ms) =

IINRUSH (mA)

COUT (µF)

(3)

A capacitor can be connected to the dVdt pin to control the rising slew rate and lower the inrush current during

turn-on. The required CdVdt capacitance to produce a given slew rate can be calculated using Equation 4.

28

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

�TPS25947

www.ti.com

CdVdt (pF) =

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

2000

SR (V/ms)

(4)

The fastest output slew rate is achieved by leaving the dVdt pin open.

Note

For CdVdt > 10 nF, TI recommends to add a 100-Ω resistor in series with the capacitor on the dVdt pin.

8.3.5.2 Circuit-Breaker

The TPS259474x (Circuit-Breaker) variants respond to output overcurrent conditions by turning off the output

after a user adjustable transient fault blanking interval. When the load current exceeds the set overcurrent

threshold (ILIM) set by the ILM pin resistor (RILM), but stays lower than the fast-trip threshold (2 x ILIM), the device

starts discharging the ITIMER pin capacitor using an internal 1.8-μA pull-down current. If the load current drops

below ILIM before the ITIMER pin capacitor (CITIMER) discharges by ΔVITIMER, the ITIMER is reset by pulling it

up to VINT internally and the circuit breaker action is not engaged. This allows short load transient pulses to

pass through the device without tripping the circuit. If the overcurrent condition persists, the CITIMER continues to

discharge and after it discharges by ΔVITIMER, the circuit breaker action turns off the HFET immediately. At the

same time, the CITIMER is charged up to VINT again so that it is at its default state before the next overcurrent

event. This ensures the full blanking timer interval is provided for every overcurrent event. Equation 5 can be

used to calculate the RILM value for a overcurrent threshold.

RILM :À; =

3334

ILIM :A;

(5)

Note

1. Leaving the ILM pin open sets the current limit to nearly zero and results in the part breaking the

circuit with the slightest amount of loading at the output.

2. Shorting the ILM pin to ground at any point during normal operation is detected as a fault and the

part shuts down. There is a minimum current (IFLT) which the part allows in this condition before

the pin short condition is detected.

The duration for which transients are allowed can be adjusted using an appropriate capacitor value from ITIMER

pin to ground. The CITIMER value needed to set the desired transient overcurrent blanking interval can be

calculated using Equation 6.

tITIMER (ms) =

¿VITIMER (V) × CITIMER (nF)

IITIMER (µA)

(6)

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

29

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

Transient Overcurrent

Persistent Output Overload

ITIMER expired

2 x ILIM

Circuit-Breaker

operation

IOUT

ILIM

0

tITIMER

VINT

¨VITIMER

ITIMER

0

VIN

OUT

0

VPGTH

PGTH

0

VPG

tPGD

PG

0

TSD

TSDHY S

TJ

TJ

Time

Figure 8-9. TPS259474x Overcurrent Response

Note

1. Leave the ITIMER pin open to allow the part to break the circuit with the minimum possible delay.

2. Shorting the ITIMER pin to ground results in minimum overcurrent response delay (similar

to ITIMER pin open condition), but increases the device current consumption. This is not a

recommended mode of operation.

3. Increasing the ITIMER cap value extends the overcurrent blanking interval, but it also extends

the time needed for the ITIMER cap to recharge up to VINT. If the next overcurrent event occurs

before the ITIMER cap is recharged fully, it takes lesser time to discharge to the ITIMER expiry

threshold, thereby providing a shorter blanking interval than intended.

After the part shuts down due to a Circuit Breaker fault, it can either stay latched off (TPS259474L variant) or

restart automatically after a fixed delay (TPS259474A variant).

8.3.5.3 Active Current Limiting

The TPS259470x/2x (Active Current Limit) variants respond to output overcurrent conditions by actively limiting

the current after a user adjustable transient fault blanking interval. When the load current exceeds the set

overcurrent threshold (ILIM) set by the ILM pin resistor (RILM), but stays lower than the short-circuit threshold (2 ×

ILIM), the device starts discharging the ITIMER pin capacitor using an internal 1.8-μA pulldown current. If the load

current drops below the overcurrent threshold before the ITIMER capacitor (CITIMER) discharges by ΔVITIMER,

the ITIMER is reset by pulling it up to VINT internally and the current limit action is not engaged. This allows

30

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

short load transient pulses to pass through the device without getting current limited. If the overcurrent condition

persists, the C ITIMER continues to discharge and after it discharges by ΔVITIMER, the current limit starts regulating

the HFET to actively limit the current to the set overcurrent threshold (ILIM). At the same time, the CITIMER is

charged up to VINT again so that it is at its default state before the next overcurrent event. This ensures the

full blanking timer interval is provided for every overcurrent event. Equation 7 can be used to calculate the RILM

value for a desired overcurrent threshold.

RILM :À; =

3334

ILIM :A;

(7)

Note

1. Leaving the ILM pin open sets the current limit to nearly zero and results in the part entering

current limit with the slightest amount of loading at the output.

2. The current limit circuit employs a foldback mechanism. The current limit threshold in the foldback

region (0 V < VOUT < VFB) is lower than the steady state current limit threshold (ILIM).

3. Shorting the ILM pin to ground at any point during normal operation is detected as a fault and the

part shuts down. There’s a minimum current (IFLT) which the part allows in this condition before

the pin short condition is detected.

The duration for which transients are allowed can be adjusted using an appropriate capacitor value from ITIMER

pin to ground. The CITIMER value needed to set the desired transient overcurrent blanking interval can be

calculated using Equation 8 below.

tITIMER (ms) =

¿VITIMER (V) × CITIMER (nF)

IITIMER (µA)

(8)

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

31

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

Transient Overcurrent

Persistent Output Overload

ITIMER expired

Overload Removed

Persistent Output Overload

ITIMER expired

Thermal shutdown

2 x ILIM

tLIM

tLIM

Current limiting

operation

Current limiting

operation

ILIM

IOUT

0

tITIMER

tITIMER

VINT

¨VITIMER

ITIMER

0

VIN

OUT

0

1.2 V

(1)

PGTH

tPGD

0

VPG

tPGA

tPGD

(1)

PG

0

VFLT

FLT

(2)

0

TSD

TSDHY S

TJ

TJ

Time

(1)

(2)

Applicable only to TPS259472x/4x variants

Applicable only to TPS259470x variants

Figure 8-10. TPS259470x/2x Active Current Limit Response

1.

2.

3.

4.

5.

Note

Leave the ITIMER pin open to allow the part to limit the current with the minimum possible delay.

Shorting the ITIMER pin to ground results in minimum overcurrent response delay (similar

to ITIMER pin open condition), but increases the device current consumption. This is not a

recommended mode of operation.

Active current limiting based on RILM is active during start-up for both TPS259470x/2x (Current

Limit) and TPS259474x (Circuit-Breaker) variants. In case the start-up current exceeds ILIM, the

device regulates the current to the set limit. However, during start-up the current limit is engaged

without waiting for the ITIMER delay.

For the TPS259472x variants, during overvoltage clamp condition, if an overcurrent event occurs,

the current limit is engaged without waiting for the ITIMER delay.

Increasing the CITIMER value extends the overcurrent blanking interval, but it also extends the time

needed for the CITIMER to recharge up to VINT. If the next overcurrent event occurs before the

CITIMER is recharged fully, it takes less time to discharge to the ITIMER expiry threshold, thereby

providing a shorter blanking interval than intended.

During active current limit, the output voltage drops resulting in increased device power dissipation across the

HFET. If the device internal temperature (TJ) exceeds the thermal shutdown threshold (TSD), the HFET is turned

off. After the part shuts down due to TSD fault, it can either stay latched off (TPS25947xL variants) or restart

automatically after a fixed delay (TPS25947xA variants). See Overtemperature Protection (OTP) for more details

on device response to overtemperature.

32

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

8.3.5.4 Short-Circuit Protection

During an output short-circuit event, the current through the device increases very rapidly. When a severe

overcurrent condition is detected, the device triggers a fast-trip response to limit the current to a safe level.

The internal fast-trip comparator employs a scalable threshold (ISC) which is equal to 2 × ILIM. This enables the

user to adjust the fast-trip threshold rather than using a fixed threshold which can be too high for some low

current systems. The device also employs a fixed fast-trip threshold (IFT) to protect fast protection against hard

short-circuits during steady state. The fixed fast-trip threshold is higher than the maximum recommended user

adjustable scalable fast-trip threshold. After the current exceeds ISC or IFT, the HFET is turned off completely

within tFT. Thereafter, the devices tries to turn the HFET back on after a short de-glitch interval (30 μs) in a

current limited manner instead of a dVdt limited manner. This ensures that the HFET has a faster recovery after

a transient overcurrent event and minimizes the output voltage droop. However, if the fault is persistent, the

device stays in current limit causing the junction temperature to rise and eventually enter thermal shutdown. See

Overtemperature Protection (OTP) section for details on the device response to overtemperature.

Transient Severe Overcurrent

Persistent Severe Overcurrent

Thermal Shutdown

Overcurrent Removed

Retry Timer Elapsed (3)

Output Hard Short-circuit to ground

Thermal Shutdown

Short-circuit Removed

Retry Timer Elapsed (3)

VIN

IN

0

IFT

tSC

tFT

tSC

2 x ILIM

IOUT

ILIM

0

VIN

OUT

dVdt Limited

Start-up

dVdt Limited

Start-up

Current Limited

Start-up

0

tPGD

tPGD

tPGD

VPG

PG (1)

0

VFLT

FLT (2)

0

tRST

TSD

tRST

TSDHYS

TJ

Time

(1)

Applicable only to TPS259472x/4x variants

(2)

Applicable only to TPS259470x variants

(3)

Applicable only to TPS25947xA variants

Figure 8-11. TPS25947xx Short-Circuit Response

8.3.6 Analog Load Current Monitor

The device allows the system to accurately monitor the output load current by providing an analog current sense

output on the ILM pin which is proportional to the current through the FET. The user can sense the voltage (VILM)

across the RILM to get a measure of the output load current.

IOUT (A) =

VILM (µV)

RILM :À; × GIMON (µA/A)

(9)

The waveform below shows the ILM signal response to a load step at the output.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS25947

33

�TPS25947

www.ti.com

SLVSFC9B – OCTOBER 2020 – REVISED MARCH 2022

VIN

VOUT

VILM

IIN

VIN = 12 V, COUT = 22 μF, RILM = 1150 Ω, IOUT varied dynamically between 0A and 3.5 A

Figure 8-12. Analog Load Current Monitor Response

Note

The ILM pin is sensitive to capacitive loading. Careful design and layout is needed to ensure the

parasitic capacitive loading on the ILM pin is < 50 pF for stable operation.

8.3.7 Reverse Current Protection

The device functions like an ideal diode and blocks reverse current flow from OUT to IN under all conditions.

The device has integrated back-to-back MOSFETs connected in a common drain configuration. The voltage