TPS6521815

TPS6521815

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY

2021

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

www.ti.com

TPS6521815 User-Programmable Power Management IC (PMIC) With 6 DC/DC

Converters, 1 LDO, and 3 Load Switches

1 Features

•

•

•

•

•

•

•

Three Adjustable Step-Down Converters With

Integrated Switching FETs (DCDC1, DCDC2, and

DCDC3):

– Up to 1.8-A output current

– VIN Range From 2.7 V to 5.5 V

– Adjustable Output Voltage Range 0.85 V to

1.675 V (DCDC1 and DCDC2)

– Adjustable Output Voltage Range 0.9 V to 3.4 V

(DCDC3)

– Power Save Mode at Light Load Current

– 100% Duty Cycle for Lowest Dropout

– Active Output-Discharge When Disabled

One Adjustable Buck-Boost Converter With

Integrated Switching FETs (DCDC4):

– Up to 1.6-A output current

– VIN Range from 2.7 V to 5.5 V

– Adjustable Output Voltage Range from 1.175 V

to 3.4 V

– Active Output-Discharge When Disabled

Two Low-Quiescent Current, High Efficiency StepDown Converters for Battery Backup Domain

(DCDC5, DCDC6)

– DCDC5: 1-V Output

– DCDC6: 1.8-V Output

– VIN Range from 2.2 V to 5.5 V

– Supplied From System Power or Coin-Cell

Backup Battery

Adjustable General-Purpose LDO (LDO1)

– LDO1: 1.8-V Default up to 400 mA

– VIN Range from 1.8 V to 5.5 V

– Adjustable Output Voltage Range from 0.9 V to

3.4 V

– Active Output-Discharge When Disabled

Low-Voltage Load Switch (LS1) With 350-mA

Current Limit

– VIN Range From 1.2 V to 3.6 V

– 110-mΩ (Max) Switch Impedance at 1.35 V

5-V Load Switch (LS2) With 100-mA or 500-mA

Selectable Current Limit

– VIN Range From 3 V to 5.5 V

– 500-mΩ (Max) Switch Impedance at 5 V

High-Voltage Load Switch (LS3) With 100-mA or

500-mA Selectable Current Limit

– VIN Range From 1.8 V to 10 V

•

•

– 500-mΩ (Max) Switch Impedance

Supervisor With Built-in Supervisor Function

Monitors

– DCDC1, DCDC2 ±4% Tolerance

– DCDC3, DCDC4 ±5% Tolerance

– LDO1 ±5% Tolerance

Protection, Diagnostics, and Control:

– Undervoltage Lockout (UVLO)

– Always-on Push-Button Monitor

– Overtemperature Warning and Shutdown

– Separate Power-Good Output for Backup and

Main Supplies

– I2C Interface (Address 0x24) (See Timing

Requirements for I2C Operation at 400 kHz)

2 Applications

•

•

•

•

•

•

•

Grid Infrastructure

Appliances

Building Security Systems

Human-Machine Interface (HMI)

Industrial Automation

Electronic Point of Sale (ePOS)

Test and Measurement

3 Description

The TPS6521815 is a single chip, powermanagement IC (PMIC) that is user-programmable to

power a variety of SoCs and FPGAs. The device is

characterized across a –40°C to +105°C temperature

range, making it suitable for various industrial

applications.

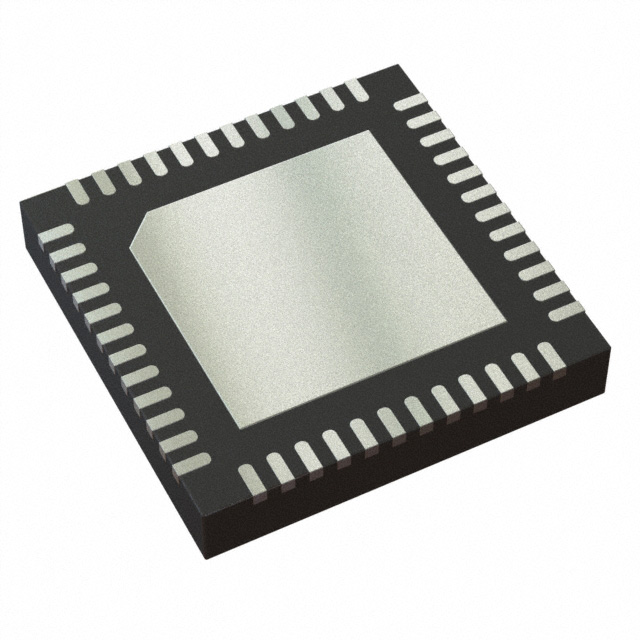

Device Information (1)

PART NUMBER

TPS6521815

(1)

PACKAGE

VQFN (48)

BODY SIZE (NOM)

6.00 mm × 6.00 mm

For all available packages, see the orderable addendum at

the end of the data sheet.

An©IMPORTANT

NOTICEIncorporated

at the end of this data sheet addresses availability, warranty, changes, use in

safety-critical

applications,

Copyright

2021 Texas Instruments

Submit

Document

Feedback

intellectual property matters and other important disclaimers. PRODUCTION DATA.

Product Folder Links: TPS6521815

1

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

3.1 Simplified Schematic

+

10 …F

VIO

VIO

1 …F

4.7 …F

CC

GPIO3

IN_BU

NC

NC

LS1

IN_LS1

IN_LS2

LS2

GPO2

IN_BIAS

INT_LDO

100 k

100 k

4.7 …F

4.7 …F

1.5 µH

VDD_18

(DCDC6)

100 k

10 …F

1.5 µH

L3

L6

FB3

FB6

nWAKEUP

FB5

FB2

L5

L2

100 k

100 k

22 …F

DC34_SEL

nINT

PFI

PWR_EN

DCDC4

FB1

IN_DCDC4

GPIO1

L4A

VIO

100 k

100 k

nPFO

AC_DET

VIO

PGOOD

100 k

IN_BIAS

VIO

10 …F

10 …F

LS3

100 k

IN_LS3

IN_LDO1

LDO1

100 k

SCL

SDA

VIO

VIO

4.7 …F

47 …F

1.5 µH

L1

1.5 µH

100 nF

L4B

100 k

10 …F

1.5 µH

IN_nCC

IN_DCDC1

VIO

100 k

22 …F

PGOOD_BU

PB

IN_BIAS

10 µH

TPS65218xx

IN_DCDC2

4.7 …F

1 …F

SYS_BU

IN_DCDC3

10 …F

±

10

10 …F

4.7 …F

4.7 …F

Copyright © 2019, Texas Instruments Incorporated

2

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

Table of Contents

1 Features............................................................................1

2 Applications..................................................................... 1

3 Description.......................................................................1

3.1 Simplified Schematic...................................................2

4 Revision History.............................................................. 3

5 Description (continued).................................................. 4

6 Pin Configuration and Functions...................................5

7 Specifications.................................................................. 7

7.1 Absolute Maximum Ratings........................................ 7

7.2 ESD Ratings............................................................... 7

7.3 Recommended Operating Conditions.........................8

7.4 Thermal Information....................................................8

7.5 Electrical Characteristics.............................................9

7.6 Timing Requirements................................................ 18

7.7 Typical Characteristics.............................................. 19

8 Detailed Description......................................................20

8.1 Overview................................................................... 20

8.2 Functional Block Diagram......................................... 21

8.3 Feature Description...................................................22

8.4 Device Functional Modes..........................................43

8.5 Programming............................................................ 45

8.6 Register Maps...........................................................46

9 Application and Implementation.................................. 73

9.1 Application Information............................................. 73

9.2 Typical Application.................................................... 75

10 Power Supply Recommendations..............................79

11 Layout........................................................................... 79

11.1 Layout Guidelines................................................... 79

11.2 Layout Example...................................................... 79

12 Device and Documentation Support..........................81

12.1 Documentation Support.......................................... 81

12.2 Receiving Notification of Documentation Updates..81

12.3 Support Resources................................................. 81

12.4 Trademarks............................................................. 81

12.5 Electrostatic Discharge Caution..............................81

12.6 Glossary..................................................................81

13 Mechanical, Packaging, and Orderable

Information.................................................................... 81

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision * (November 2019) to Revision A (February 2021)

Page

• Updated the numbering format for tables, figures, and cross-references throughout the document..................1

• Removed medical equipment from applications section.....................................................................................1

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

3

�TPS6521815

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

www.ti.com

5 Description (continued)

Three hysteretic step-down converters are targeted at providing power for the processor core, MPU, and DDRx

memory. The default output voltages for each converter can be adjusted through the I2C interface. DCDC1 and

DCDC2 feature dynamic voltage scaling to provide power at all operating points of the processor. DCDC1 and

DCDC2 also have programmable slew rates to help protect processor components. DCDC3 remains powered

while the processor is in sleep mode to maintain power to DDRx memory. Backup power provides two step-down

converters for the tamper, RTC, or both domains of the processor if system power fails or is disabled. If both

system power and coin-cell battery are connected to the PMIC, power is not drawn from the coin-cell battery. A

separate power good signal monitors the backup converters. A battery backup monitor determines the power

level of the coin-cell battery.

4

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

6 Pin Configuration and Functions

L1

FB1

PWR_EN

nINT

PB

IN_DCDC2

L2

FB2

nWAKEUP

FB3

L3

IN_DCDC3

48

47

46

45

44

43

42

41

40

39

38

37

Figure 6-1 shows the 48-pin RSL Plastic Quad Flatpack No-Lead.

IN_DCDC1

1

36

IN_BIAS

SDA

2

35

INT_LDO

SCL

3

34

GPO2

LDO1

4

33

LS2

IN_LDO1

5

32

IN_LS2

IN_LS3

6

31

IN_LS1

LS3

7

30

LS1

PGOOD

8

29

N/C

AC_DET

9

28

N/C

nPFO

10

27

IN_BU

GPIO1

11

26

GPIO3

IN_DCDC4

12

25

CC

Thermal

13

14

15

16

17

18

19

20

21

22

23

24

L4A

L4B

DCDC4

PFI

DC34_SEL

IN_nCC

PGOOD_BU

L5

FB5

FB6

L6

SYS_BU

Pad

Not to scale

Figure 6-1. 48-Pin RSL VQFN With Exposed Thermal Pad (Top View, 6 mm × 6 mm × 1 mm With 0.4-mm

Pitch)

Table 6-1. Pin Functions

PIN

NO.

NAME

TYPE

DESCRIPTION

1

IN_DCDC1

P

2

SDA

I/O

Input supply pin for DCDC1.

3

SCL

I

Clock input for the I2C interface. Connect to pullup resistor.

4

LDO1

O

Output voltage pin for LDO1. Connect to capacitor.

5

IN_LDO1

P

Input supply pin for LDO1.

6

IN_LS3

P

Input supply pin for load switch 3.

7

LS3

O

Output voltage pin for load switch 3. Connect to capacitor.

8

PGOOD

O

Power-good output (configured as open drain). Pulled low when either DCDC1-4 or LDO1 are out of

regulation. Load switches and DCDC5-6 do not affect PGOOD pin.

9

AC_DET

I

AC monitor input and enable for DCDC1-4, LDO1 and load switches. See Section 8.4.1 for details. Tie pin to

IN_BIAS if not used.

10

nPFO

O

Power-fail comparator output, deglitched (open drain). Pin is pulled low when PFI input is below power-fail

threshold.

11

GPIO1

I/O

Pin configured as DDR reset-input (driving GPO2) or as general-purpose, open-drain output. See Section

8.3.1.14 for more information.

12

IN_DCDC4

P

Input supply pin for DCDC4.

13

L4A

P

Switch pin for DCDC4. Connect to inductor.

14

L4B

P

Switch pin for DCDC4. Connect to inductor.

15

DCDC4

P

Output voltage pin for DCDC4. Connect to capacitor.

16

PFI

I

Power-fail comparator input. Connect to resistor divider.

17

DC34_SEL

I

Power-up default selection pin for DCDC3 or DCDC4. Power-up default is programmed by a resistor

connected to ground. See Section 8.3.1.13 for resistor options.

Data line for the I2C interface. Connect to pullup resistor.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

5

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

Table 6-1. Pin Functions (continued)

PIN

NO.

6

NAME

TYPE

DESCRIPTION

18

IN_nCC

O

Output pin indicates if DCDC5 and DCDC6 are powered from main supply (IN_BU) or coin-cell battery (CC).

Pin is push-pull output. Pulled low when PMIC is powered from coin cell battery. Pulled high when PMIC is

powered from main supply (IN_BU).

19

PGOOD_BU

O

Power-good, push-pull output for DCDC5 and DCDC6. Pulled low when either DCDC5 or DCDC6 is out of

regulation. Pulled high (to DCDC6 output voltage) when both rails are in regulation.

20

L5

P

Switch pin for DCDC5. Connect to inductor.

21

FB5

I

Feedback voltage pin for DCDC5. Connect to output capacitor.

22

FB6

I

Feedback voltage pin for DCDC6. Connect to output capacitor.

23

L6

P

Switch pin for DCDC6. Connect to inductor.

24

SYS_BU

P

System voltage pin for battery-backup supply power path. Connect to 1-µF capacitor. Connecting any

external load to this pin is not recommended.

25

CC

P

Coin cell battery input. Serves as the supply to DCDC5 and DCDC6 if no voltage is applied to IN_BU. Tie this

pin to ground if it is not in use.

26

GPIO3

I/O

Pin can be configured as warm reset (negative edge) for DCDC1 and DCDC2 or as a general-purpose, opendrain output. See Section 8.3.1.14 for more details.

27

IN_BU

P

Default input supply pin for battery backup supplies (DCDC5 and DCDC6).

28

N/C

29

N/C

—

No connect. Leave pin floating.

30

LS1

O

Output voltage pin for load switch 1. Connect to capacitor.

31

IN_LS1

P

Input supply pin for load switch 1.

32

IN_LS2

P

Input supply pin for load switch 2.

33

LS2

O

Output voltage pin for load switch 2. Connect to capacitor.

34

GPO2

O

Pin configured as DDR reset signal (controlled by GPIO1) or as general-purpose output. Buffer can be

configured as push-pull or open-drain.

35

INT_LDO

P

Internal bias voltage. Connect to a 1-μF capacitor. TI does not recommended connecting any external load to

this pin.

36

IN_BIAS

P

Input supply pin for reference system.

37

IN_DCDC3

P

Input supply pin for DCDC3.

38

L3

P

Switch pin for DCDC3. Connect to inductor.

39

FB3

I

Feedback voltage pin for DCDC3. Connect to output capacitor.

40

nWAKEUP

O

Signal to SOC to indicate a power on event (active low, open-drain output).

41

FB2

I

Feedback voltage pin for DCDC2. Connect to output capacitor.

42

L2

P

Switch pin for DCDC2. Connect to inductor.

43

IN_DCDC2

P

Input supply pin for DCDC2.

44

PB

I

Push-button monitor input. Typically connected to a momentary switch to ground (active low). See Section

8.4.1 for details.

45

nINT

O

Interrupt output (active low, open drain). Pin is pulled low if an interrupt bit is set. The pin returns to Hi-Z state

after the bit causing the interrupt has been read. Interrupts can be masked.

46

PWR_EN

I

Power enable input for DCDC1-4, LDO1 and load switches. See Section 8.4.1 for details.

47

FB1

I

Feedback voltage pin for DCDC1. Connect to output capacitor.

48

L1

P

Switch pin for DCDC1. Connect to inductor.

—

Thermal Pad

P

Power ground and thermal relief. Connect to ground plane.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

7 Specifications

7.1 Absolute Maximum Ratings

Operating under free-air temperature range (unless otherwise noted).(1)

IN_BIAS, IN_LDO1, IN_LS2, IN_DCDC1, IN_DCDC2,

IN_DCDC3, IN_DCDC4

Supply voltage

TA

MIN

MAX

–0.3

7

IN_LS1, CC

–0.3

3.6

IN_LS3

–0.3

11.2

IN_BU

–0.3

5.8

Output voltage

All pins unless specified separately

–0.3

7

Source or sink

current

GPO2

6

PGOOD_BU, IN_nCC

1

Sink current

PGOOD, nWAKEUP, nINT, nPFO, SDA, GPIO1, GPIO3

Operating ambient temperature

–40

UNIT

V

V

mA

6

mA

105

°C

TJ

Junction temperature

–40

125

°C

Tstg

Storage temperature

–65

150

°C

(1)

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating

Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

7.2 ESD Ratings

VALUE

V(ESD)

(1)

(2)

Electrostatic

discharge

Human-body model (HBM), per ANSI/ESDA/JEDEC

JS-001(1)

Charged-device model (CDM), per JEDEC specification JESD22-C101(2)

±2000

±500

UNIT

V

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

7

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

7.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted).

MIN

NOM

MAX

UNIT

Supply voltage, IN_BIAS

2.7

5.5

V

Input voltage for DCDC1, DCDC2, DCDC3, and DCDC4

2.7

5.5

V

Supply voltage, IN_BU

2.2

5.5

V

Supply voltage, CC

2.2

3.3

V

Input voltage for LDO1

1.8

5.5

V

Input voltage for LS1

1.2

3.6

V

Input voltage for LS2

3

5.5

V

Input voltage for LS3

1.8

10

V

Output voltage for DCDC1

0.85

1.675

V

Output voltage for DCDC2

0.85

1.675

V

Output voltage for DCDC3

0.9

3.4

V

Output voltage for DCDC4

1.175

Output voltage for DCDC5

3.4

1

Output voltage for DCDC6

1.8

Output voltage for LDO1

Output current for DCDC1, DCDC2, and DCDC3

Output current for DCDC4

V

V

V

0.9

3.4

V

0

1.8

A

VIN_DCDC4 = 2.8 V

1

VIN_DCDC4 = 3.6 V

1.3

VIN_DCDC4 = 5 V

1.6

A

Output current for DCDC5 and DCDC6

0

25

mA

Output current for LDO1

0

400

mA

Output current for LS1

0

300

mA

Output current for LS2

0

920

mA

VIN_LS3 > 2.3 V

0

900

VIN_LS3 ≤ 2.3 V

0

475

Output current for LS3

mA

7.4 Thermal Information

TPS6521815

THERMAL METRIC(1)

RSL (VQFN)

UNIT

48 PINS

RθJC(top)

Junction-to-case (top)

RθJB

RθJA

°C/W

Junction-to-board

5.8

°C/W

Thermal resistance, junction-to-ambient. JEDEC 4-layer, high-K board.

30.6

°C/W

ΨJT

Junction-to-package top

0.2

°C/W

ΨJB

Junction-to-board

5.6

°C/W

RθJC(bot)

Junction-to-case (bottom)

1.5

°C/W

(1)

8

17.2

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

7.5 Electrical Characteristics

Over operating free-air temperature range (unless otherwise noted).

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX UNIT

INPUT VOLTAGE AND CURRENTS

VIN_BIAS

Input supply voltage range

Normal operation

2.7

5.5

EEPROM programming

4.5

5.5

Deglitch time

IOFF

OFF state current, total current

into IN_BIAS, IN_DCDCx,

IN_LDO1, IN_LS

ISUSPEND

VIN = 3.6 V; DCDC3 enabled, low-power mode, no

SUSPEND current, total current

load.

into IN_BIAS, IN_DCDCx,

All other rails disabled.

IN_LDO1, IN_LS

TJ = 0°C to 105°C

VIN = 3.6 V; All rails disabled.

TJ = 0°C to 85°C

V

5

ms

5

µA

220

µA

SYS_BU

VSYS_BU

SYS_BU voltage range

Powered from VIN_BU or VCC

CSYS_BU

Recommended SYS_BU

capacitor

Ceramic, X5R or X7R, see Table 9-3.

Tolerance

Ceramic, X5R or X7R, rated voltage ≥ 6.3 V

2.2

5.5

1

–20%

V

µF

20%

INT_LDO

VINT_LDO

Output voltage

2.5

DC accuracy

IOUT < 10 mA

IOUT

Output current range

Maximum allowable external load

ILIMIT

Short circuit current limit

Output shorted to GND

Hold-up time

Measured from VINT_LDO = to VINT_LDO = 1.8 V

All rails enabled before power off,

IN_BIAS tied to IN_DCDC1-4, IN_LDO1

VIN_BIAS = 2.8 V to 0 V in < 5 µs

No external load on INT_LDO

CINT_LDO = 1 µF, see Table 9-3.

tHOLD

COUT

Nominal output capacitor value

Ceramic, X5R or X7R, see Table 9-3.

Tolerance

Ceramic, X5R or X7R, rated voltage ≥ 6.3 V

V

–2%

2%

0

10

23

mA

150

0.1

mA

ms

1

–20%

22

µF

20%

DCDC1 (1.1-V BUCK)

VIN_DCDC1

VDCDC1

IOUT

IQ

RDS(ON)

ILIMIT

Input voltage range

VIN_BIAS > VUVLO

I2C

Output voltage range

Adjustable through

DC accuracy

2.7 V ≤ VIN ≤ 5.5 V; 0 A ≤ IOUT ≤ 1.8 A

Continuous output current

VIN_DCDC1 > 2.7 V

Quiescent current

Total current from IN_DCDC1 pin; Device not switching,

no load

High-side FET on resistance

5.5

V

0.85

1.675

V

–2%

2%

1.8

A

25

50

µA

VIN_DCDC1 = 3.6 V

230

355

Low-side FET on resistance

VIN_DCDC1 = 3.6 V

90

145

High-side current limit

VIN_DCDC1 = 3.6 V

2.8

Low-side current limit

VIN_DCDC1 = 3.6 V

3.1

mΩ

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

A

9

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

7.5 Electrical Characteristics (continued)

Over operating free-air temperature range (unless otherwise noted).

PARAMETER

Power-good threshold

Hysteresis

VPG

TEST CONDITIONS

MIN

TYP

88.5%

90%

STRICT = 1b

96%

96.5%

97%

STRICT = 0b

3.8%

4.1%

4.4%

STRICT = 0b

VOUT falling

VOUT rising

VOUT falling

Deglitch

VOUT rising

STRICT = 1b

0.25%

STRICT = 0b

1

STRICT = 1b

50

µs

STRICT = 0b

10

µs

STRICT = 1b

10

µs

5

ms

Time-out

Overvoltage detection threshold VOUT rising, STRICT = 1b

VOV

Hysteresis

IINRUSH

RDIS

Discharge resistor

L

103%

0.25%

Deglitch

VOUT rising, STRICT = 1b

50

Inrush current

VIN_DCDC1 = 3.6 V; COUT = 10 µF to 100 µF

Output capacitance value

ms

104%

µs

500

See Table 9-2.

Tolerance

COUT

103.5%

VOUT falling, STRICT = 1b

Nominal inductor value

MAX UNIT

91.5%

mA

150

250

350

Ω

1

1.5

2.2

µH

22

100(8)

µF

–30%

30%

Ceramic, X5R or X7R, see Table 9-3.

10

VIN_BIAS > VUVLO

2.7

5.5

V

0.85

1.675

V

–2%

2%

DCDC2 (1.1-V BUCK)

VIN_DCDC2

VDCDC2

IOUT

IQ

RDS(ON)

ILIMIT

Input voltage range

I2C

Output voltage range

Adjustable through

DC accuracy

2.7 V ≤ VIN ≤ 5.5 V; 0 A ≤ IOUT ≤ 1.8 A

Continuous output current

VIN_DCDC2 > 2.7 V

Quiescent current

Total current from IN_DCDC2 pin; device not switching,

no load

1.8

A

25

50

µA

High-side FET on resistance

VIN_DCDC2 = 3.6 V

230

355

Low-side FET on resistance

VIN_DCDC2 = 3.6 V

90

145

High-side current limit

VIN_DCDC2 = 3.6 V

2.8

Low-side current limit

VIN_DCDC2 = 3.6 V

3.1

Power-good threshold

VOUT falling

Hysteresis

VOUT rising

VPG

88.5%

90%

91.5%

STRICT = 1b

96%

96.5%

97%

STRICT = 0b

3.8%

4.1%

4.4%

0.25%

STRICT = 0b

1

ms

STRICT = 1b

50

µs

STRICT = 0b

10

µs

STRICT = 1b

10

µs

Occurs at enable of DCDC2 and after DCDC2

register write (register 0x17).

5

ms

VOUT falling

Deglitch

VOUT rising

Time-out

Overvoltage detection threshold VOUT rising, STRICT = 1b

103%

103.5%

VOV

Hysteresis

VOUT falling, STRICT = 1b

0.25%

Deglitch

VOUT rising, STRICT = 1b

50

IINRUSH

Inrush current

VIN_DCDC2 = 3.6 V; COUT = 10 µF to 100 µF

RDIS

Discharge resistor

L

10

Nominal inductor value

A

STRICT = 0b

STRICT = 1b

mΩ

See Table 9-2.

Tolerance

µs

500

mA

150

250

350

Ω

1

1.5

2.2

µH

–30%

Submit Document Feedback

104%

30%

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

7.5 Electrical Characteristics (continued)

Over operating free-air temperature range (unless otherwise noted).

PARAMETER

COUT

Output capacitance value

TEST CONDITIONS

MIN

TYP

Ceramic, X5R or X7R, see Table 9-3.

10

22

VIN_BIAS > VUVLO

MAX UNIT

100(8)

µF

2.7

5.5

V

0.9

3.4

V

–2%

2%

DCDC3 (1.2-V BUCK)

VIN_DCDC3

Input voltage range

I2C

Output voltage range

Adjustable through

DC accuracy

2.7 V ≤ VIN ≤ 5.5 V; 0 A ≤ IOUT ≤ 1.8 A,

VIN_DCDC3 ≥ (VDCDC3 + 700 mV)

IOUT

Continuous output current

VIN_DCDC3 > 2.7 V

IQ

Quiescent current

Total current from IN_DCDC3 pin;

Device not switching, no load

High-side FET on resistance

Low-side FET on resistance

VDCDC3

RDS(ON)

ILIMIT

1.8

A

25

50

µA

VIN_DCDC3 = 3.6 V

230

345

VIN_DCDC3 = 3.6 V

100

150

High-side current limit

VIN_DCDC3 = 3.6 V

2.8

Low-side current limit

VIN_DCDC3 = 3.6 V

3

Power-good threshold

VOUT falling

Hysteresis

VPG

VOUT rising

STRICT = 0b

88.5%

90%

STRICT = 1b

95%

95.5%

96%

STRICT = 0b

3.8%

4.1%

4.4%

0.25%

1

STRICT = 1b

50

µs

STRICT = 0b

10

µs

STRICT = 1b

10

µs

Occurs at enable of DCDC3 and after DCDC3

register write (register 0x18).

5

ms

VOUT rising

Overvoltage detection threshold VOUT rising, STRICT = 1b

104%

104.5%

Hysteresis

VOUT falling, STRICT = 1b

0.25%

Deglitch

VOUT rising, STRICT = 1b

50

IINRUSH

Inrush current

VIN_DCDC3 = 3.6 V; COUT = 10 µF to 100 µF

RDIS

Discharge resistor

L

COUT

Nominal inductor value

See Table 9-2.

Tolerance

Output capacitance value

91.5%

STRICT = 0b

Deglitch

VOV

A

STRICT = 1b

VOUT falling

Time-out

mΩ

150

250

1.0

1.5

–30%

Ceramic, X5R or X7R, see Table 9-3.

10

ms

105%

µs

500

mA

350

Ω

2.2

µH

30%

22

100

µF

DCDC4 (3.3-V BUCK-BOOST) / ANALOG AND I/O

Output voltage ripple

PFM mode enabled;

4.2 V ≤ VIN ≤ 5.5 V;

0 A ≤ IOUT ≤ 1.6 A

VOUT = 3.3 V

150 mVpp

Minimum duty cycle in stepdown mode

IOUT

Continuous output current

IQ

Quiescent current

fSW

Switching frequency

18%

VIN_DCDC4 = 2.8 V, VOUT = 3.3 V

1

VIN_DCDC4 = 3.6 V, VOUT = 3.3 V

1.3

VIN_DCDC4 = 5 V, VOUT = 3.3 V

1.6

Total current from IN_DCDC4 pin; Device not

switching, no load.

25

2400

50

A

µA

kHz

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

11

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

7.5 Electrical Characteristics (continued)

Over operating free-air temperature range (unless otherwise noted).

PARAMETER

High-side FET on resistance

TEST CONDITIONS

VIN_DCDC3 = 3.6 V

RDS(ON)

ILIMIT

Low-side FET on resistance

VIN_DCDC3 = 3.6 V

Average switch current limit

VIN_DCDC4 = 3.6 V

Power-good threshold

VOUT falling

Hysteresis

VOUT rising

VPG

VOUT falling

Deglitch

Hysteresis

L4B to DCDC4

149

L4A to GND

142

190

144

190

L4B to GND

3000

88.5%

90%

91.5%

STRICT = 1b

95%

95.5%

96%

STRICT = 0b

3.8%

4.1%

4.4%

STRICT = 1b

0.25%

STRICT = 0b

1

ms

STRICT = 1b

50

µs

STRICT = 0b

10

µs

10

µs

Occurs at enable of DCDC4 and after DCDC4

register write (register 0x19)

5

ms

104%

104.5%

0.25%

Deglitch

VOUT rising, STRICT = 1b

50

IINRUSH

Inrush current

VIN_DCDC4 = 3.3 V ≤ VINDCDC4 ≤ 5.5 V; 40 µF ≤ COUT

≤ 100 µF

RDIS

Discharge resistor

L

See Table 9-2.

Tolerance

COUT

Output capacitance value

mΩ

mA

STRICT = 0b

VOUT falling, STRICT = 1b

Nominal inductor value

MAX UNIT

166

Overvoltage detection threshold VOUT rising, STRICT = 1b

VOV

TYP

STRICT = 1b

VOUT rising

Time-out

MIN

IN_DCDC4 to L4A

105%

µs

500

mA

150

250

350

Ω

1.2

1.5

2.2

µH

–30%

Ceramic, X5R or X7R, see Table 9-3.

40

VIN_BU = 0 V

30%

80

100

µF

2.2

3.3

V

2.2

5.5

V

DCDC5 and DCDC6 POWER PATH

VCC

DCDC5 and DCDC6 input

voltage range.

VIN_BU

DCDC5 and DCDC6 input

voltage range(1)

tRISE

VCC, VIN_BU rise time

VCC = 0 V to 3.3 V, VIN_BU = 0 V to 5.5 V

Power path switch impedance

CC to SYS_BU

VCC = 2.4 V, VIN_BU = 0 V

14.5

Power path switch impedance

IN_BU to SYS_BU

VIN_BU = 3.6 V

10.5

Forward leakage current

Into CC pin;

VCC = 3.3 V, VIN_BU = 0 V;

OFF state; FSEAL = 0b;

over full temperature range

Reverse leakage current

Out of CC pin;

VCC = 1.5 V; VIN_BU = 5.5 V;

over full temperature range

RCC

Acceptable CC source

impedance

IOUT, DCDC5 < 10 µA;

IOUT, DCDC6 < 10 µA

IQ

Quiescent current

Average current into CC pin; RECOVERY or OFF

state; VIN_BU = 0 V; VCC = 2.4 V; DCDC5 and

DCDC6 enabled, no load TJ = 25°C

350

nA

QINRUSH

Inrush charge

VIN_BIAS = decaying; CC = 3 V; CSYS_BU = 1 µF;

SYS_BU = 2.3 V to 3 V; CCseries_resist = 10 Ω CCC =

4.7 µF

720

nC

RDS(ON)

ILEAK

12

Submit Document Feedback

30

µs

Ω

50

300

nA

500

1000

Ω

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

7.5 Electrical Characteristics (continued)

Over operating free-air temperature range (unless otherwise noted).

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX UNIT

DCDC5 (1-V BATTERY BACKUP SUPPLY)

Output voltage

VDCDC5

DC accuracy

1

–2.5%

2.5%

2.7 V ≤ VIN_BU ≤ 5.5 V

1.5 µA ≤ IOUT ≤ 25 mA

0°C ≤ TA < 105°C

–2%

2%

–2.5%

2.5%

2.2 V ≤ VCC ≤ 3.3 V; VIN_BU = 0;

1.5 µA ≤ IOUT ≤ 100 µA

Output voltage ripple

IOUT

Continuous output current

L = 10 µH; COUT = 22 µF; 100-µA load, occurs during

band-gap sampling

32(9) mVpp

2.2 V ≤ VCC ≤ 3.3 V

VIN_BU = 0 V

10

100

µA

25

mA

2.7 V ≤ VIN_BU ≤ 5.5 V

RDS(ON)

ILIMIT

VPG

L

COUT

V

2.7 V ≤ VIN_BU ≤ 5.5 V;

1.5 µA ≤ IOUT ≤ 25 mA

–40°C ≤ TA < 0°C

High-side FET on resistance

VIN_BU = 2.8 V

2.5

3.5

Low-side FET on resistance

VIN_BU = 2.8 V

2

3

High-side current limit

VIN_BU = 2.8 V

50

Power-good threshold

VOUT falling

Hysteresis

VOUT rising

Nominal inductor value

Chip inductor, see Table 9-3.

Tolerance

Output capacitance value

Ceramic, X5R or X7R, see Table 9-3.

Tolerance

79%

85%

Ω

mA

91%

6%

4.7

10

22

–30%

30%

20(10)

47

–20%

20%

µH

µF

DCDC6 (1.8-V BATTERY BACKUP SUPPLY)

VDCDC6

Output voltage

VDCDC6

Output voltage ripple

L = 10 µH; COUT = 22 µF; 100-µA load

1.8

IOUT

Continuous output current

2.2 V ≤ VCC ≤ 3.3 V

VIN_BU = 0 V

10

100

µA

25

mA

2.7 V ≤ VIN_BU ≤ 5.5 V

RDS(ON)

ILIMIT

VPG

L

COUT

V

30(9) mVpp

High-side FET on resistance

VIN_BU = 3 V

2.5

3.5

Low-side FET on resistance

VIN_BU = 3 V

2

3

High-side current limit

VIN_BU = 3 V

50

Power-good threshold

VOUT falling

Hysteresis

VOUT rising

Nominal inductor value

Chip inductor, see Table 9-3

Tolerance

Output capacitance value

87%

Tolerance

mA

95%

3%

4.7

–30%

Ceramic, X5R or X7R, see Table 9-3

91%

Ω

10

22

µH

30%

20(10)

47

–20%

20%

µF

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

13

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

7.5 Electrical Characteristics (continued)

Over operating free-air temperature range (unless otherwise noted).

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX UNIT

LDO1 (1.8-V LDO)

VIN_LDO1

Input voltage range

VIN_BIAS > VUVLO

IQ

Quiescent current

No load

Output voltage range

Adjustable through I2C

DC accuracy

VOUT + 0.2 V ≤ VIN ≤ 5.5 V; 0 A ≤ IOUT ≤ 200 mA

VOUT

200

400

Short circuit current limit

Output shorted to GND

Dropout voltage

IOUT = 100 mA, VIN = 3.6 V

VOUT falling

Power-good threshold

Hysteresis, VOUT rising

VOUT falling

Deglitch

VOUT rising

445

Deglitch

RDIS

Discharge resistor

COUT

Output capacitance value

550

STRICT = 0b

86%

90%

94%

STRICT = 1b

95%

95.5%

96%

STRICT = 0b

3%

4%

5%

STRICT = 1b

V

mA

mA

200

mV

0.25%

STRICT = 0b

1

ms

STRICT = 1b

50

µs

STRICT = 0b

10

µs

STRICT = 1b

10

µs

5

ms

Occurs at enable of LDO and after LDO register

write (register 0x1B)

Overvoltage detection threshold VOUT rising, STRICT = 1b

VOV

3.4

2%

0

VDO

Hysteresis

0.9

–2%

0

ILIMIT

V

µA

VIN_LDO1 > 2.7 V, VOUT = 1.8 V

Output current range

Time-out

5.5

35

VIN_LDO1 – VDO = VOUT

IOUT

VPG

1.8

104%

104.5%

105%

VOUT falling, STRICT = 1b

0.25%

VOUT rising, STRICT = 1b

50

µs

VOUT falling, STRICT = 1b

1

ms

150

Ceramic, X5R or X7R

250

380

Ω

22

100

µF

3.6

V

LOAD SWITCH 1 (LS1)

VIN_LS1

RDS(ON)

Input voltage range

Static on resistance

VIN_BIAS > VUVLO

110

VIN_LS1 = 1.8 V, IOUT = 300 mA,

DDR2, LPDDR, MDDR at 266 MHz over full

temperature range

110

VIN_LS1 = 1.5 V, IOUT = 300 mA,

DDR3 at 333 MHz over full temperature range

110

VIN_LS1 = 1.35 V, IOUT = 300 mA,

DDR3L at 333 MHz over full temperature range

110

VIN_LS1 = 1.2 V, IOUT = 200 mA,

LPDDR2 at 333 MHz over full temperature range

150

ILIMIT

Short circuit current limit

Output shorted to GND

tBLANK

Interrupt blanking time

Output shorted to GND until interrupt is triggered.

RDIS

Internal discharge resistor at

output(2)

LS1DCHRG = 1

TOTS

COUT

14

1.2

VIN_LS1 = 3.3 V, IOUT = 300 mA, over full temperature

range

Overtemperature shutdown(3)

350

Nominal output capacitance

value

mA

15

ms

150

250

380

125

132

139

Hysteresis

10

Ceramic, X5R or X7R, see Table 9-3.

Submit Document Feedback

10

mΩ

100

Ω

°C

µF

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

7.5 Electrical Characteristics (continued)

Over operating free-air temperature range (unless otherwise noted).

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX UNIT

LOAD SWITCH 2 (LS2)

VIN_LS2

VUVLO

RDS(ON)

Input voltage range

VIN_BIAS > VUVLO

Undervoltage lockout

Measured at IN_LS2. Supply falling(4)

3

Hysteresis

Input voltage rising

Static on resistance

VIN_LS2 = 5 V, IOUT = 500 mA, over full temperature

range

2.48

2.6

5.5

V

2.7

V

170

mV

500

LS2ILIM[1:0] = 00b

94

126

ILIMIT

Short circuit current limit

Output shorted to GND; VIN_LS2 LS2ILIM[1:0] = 01b

≥4V

LS2ILIM[1:0] = 10b

188

251

465

631

LS2ILIM[1:0] = 11b

922

ILEAK

Reverse leakage current

VLS2 > VIN_LS2 + 1 V

12

tBLANK

Interrupt blanking time

Output shorted to GND until interrupt is triggered

15

RDIS

Internal discharge resistor at

output(2)

LS2DCHRG = 1b

TOTS

COUT

Overtemperature shutdown(4)

Nominal output capacitance

value

30

µA

ms

250

380

125

132

139

10

Ceramic, X5R or X7R, see Table 9-3.

mA

1290

150

Hysteresis

mΩ

Ω

°C

1

100

µF

1.8

10

V

LOAD SWITCH 3 (LS3)

VIN_LS3

RDS(ON)

Input voltage range

Static on resistance

VIN_BIAS > VUVLO

VIN_LS3 = 9 V, IOUT= 500 mA, over full temperature

range

440

VIN_LS3 = 5 V, IOUT= 500 mA, over full temperature

range

526

VIN_LS3 = 2.8 V, IOUT= 200 mA, over full temperature

range

656

VIN_LS3 = 1.8 V, IOUT= 200 mA, over full temperature

range

910

LS3ILIM[1:0] = 00b

VIN_LS3 > 2.3 V,

Output shorted to GND

ILIMIT

Short circuit current limit

VIN_LS3 ≤ 2.3 V,

Output shorted to GND

98

126

LS3ILIM[1:0] = 01b

194

253

LS3ILIM[1:0] = 10b

475

738

LS3ILIM[1:0] = 11b

900

1234

LS3ILIM[1:0] = 00b

98

126

LS3ILIM[1:0] = 01b

194

253

LS3ILIM[1:0] = 10b

475

738

tBLANK

Interrupt blanking time

Output shorted to GND until interrupt is triggered.

RDIS

Internal discharge resistor at

output(2)

LS3DCHRG = 1

TOTS

COUT

mΩ

Overtemperature shutdown(4)

15

ms

650

1000

1500

Ω

125

132

139

°C

Hysteresis

Nominal output capacitance

value

10

Ceramic, X5R or X7R, see Table 9-3.

mA

1

100

°C

220

µF

BACKUP BATTERY MONITOR

VTH

Comparator threshold

Ideal level

3

V

Good level

2.6

V

Low level

Accuracy

2.3

–3%

V

3%

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

15

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

7.5 Electrical Characteristics (continued)

Over operating free-air temperature range (unless otherwise noted).

PARAMETER

TEST CONDITIONS

RLOAD

Load impedance

Applied from CC to GND during comparison.

tDLY

Measurement delay

RLOAD is connected during delay time. Measurement

is taken at the end of delay.

MIN

TYP

70

100

MAX UNIT

130

600

kΩ

ms

I/O LEVELS AND TIMING CHARACTERISTICS

PGDLY

PGOOD delay time

PGDLY[1:0] = 00b

10

PGDLY[1:0] = 01b

20

PGDLY[1:0] = 10b

50

PGDLY[1:0] = 11b

PB input

AC_DET input

tDG

Deglitch time

PWR_EN input

GPIO1

GPIO3

tRESET

Reset time

PB input held low

150

Rising edge

100

ms

Falling edge

50

ms

Rising edge

100

µs

Falling edge

10

ms

Rising edge

10

ms

Falling edge

100

µs

Rising edge

1

ms

Falling edge

1

ms

Rising edge

5

µs

Falling edge

5

µs

TRST = 0b

8

TRST = 1b

15

SCL, SDA, GPIO1, and GPIO3

VIH

High level input voltage

Low level input voltage

VOH

0.66 ×

IN_BIAS

AC_DET, PB

Low level output voltage

SCL, SDA, PWR_EN, AC_DET, PB, GPIO1, and

GPIO3

0

0.4

GPO2; ISOURCE = 5 mA; GPO2_BUF = 1

VIN_LS1 –

0.3

VIN_LS1

PGOOD_BU; ISOURCE = 100 µA

VDCDC6 –

10 mV

Hysteresis

0

0.3

nPFO; ISINK = 2 mA

0

0.35

PGOOD_BU; ISINK = 100 µA

0

Deglitch

IDC34_SEL

16

DC34_SEL bias current

V

0.3

800

Input rising

Accuracy

V

V

nWAKEUP, nINT, SDA, PGOOD, GPIO1, GPO2, and

GPIO3; ISINK = 2 mA

Power-fail comparator threshold Input falling

VPFI

V

1.3

High level output voltage

VOL

s

1.3

PWR_EN

VIL

ms

mV

40

–4%

mV

4%

Input falling

25

µs

Input rising

10

ms

Enabled only at power-up.

Submit Document Feedback

9.05

10

11.93

µA

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

7.5 Electrical Characteristics (continued)

Over operating free-air temperature range (unless otherwise noted).

PARAMETER

VDC34_SEL

RDC34_SEL

DCDC3 and DCDC4 power-up

default selection thresholds

DCDC3 and DCDC4 power-up

default selection resistor values

IBIAS

Input bias current

ILEAK

Pin leakage current

TEST CONDITIONS

MIN

TYP

Threshold 1

100

Threshold 2

163

Threshold 3

275

Threshold 4

400

Threshold 5

575

Threshold 6

825

Threshold 7

1200

MAX UNIT

mV

Setting 0

0

0

7.7

Setting 1

11.8

12.1

12.4

Setting 2

19.5

20

20.5

Setting 3

30.9

31.6

32.3

Setting 4

44.4

45.3

46.3

Setting 5

64.8

66.1

67.3

Setting 6

93.6

95.3

97.2

Setting 7

146

150

SCL, SDA, GPIO1(5), GPIO3 (5); VIN = 3.3 V

0.01

kΩ

1

µA

PB, AC_DET, PFI; VIN = 3.3 V

500

nA

nINT, nWAKEUP, nPFO, PGOOD, PWR_EN,

GPIO1(6), GPO2(7), GPIO3(6)

VOUT = 3.3 V

500

nA

OSCILLATOR

Oscillator frequency

ƒOSC

Frequency accuracy

2400

TJ = –40°C to +105°C

–12%

kHz

12%

OVERTEMPERATURE SHUTDOWN

TOTS

TWARN

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

(10)

Overtemperature shutdown

Increasing junction temperature

Hysteresis

Decreasing junction temperature

High-temperature warning

Increasing junction temperature

Hysteresis

Decreasing junction temperature

135

145

155

20

90

100

15

110

°C

°C

IN_BU has priority over CC input.

Discharge function disabled by default.

Switch is temporarily turned OFF if temperature exceeds OTS threshold.

Switch is temporarily turned OFF if input voltage drops below UVLO threshold.

Configured as input.

Configured as output.

Configured as open-drain output.

500-µF of remote capacitance can be supported for DCDC1 and DCDC2.

For PHP package: 160 mVpp at -40°C, and 120 mVpp from 25°C to 105°C.

For PHP package: 40 µF.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

17

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

7.6 Timing Requirements

MIN

Serial clock frequency

tHD;STA

Hold time (repeated) START condition. After this period, the

first clock pulse is generated.

tLOW

LOW period of the SCL clock

tHIGH

HIGH period of the SCL clock

tSU;STA

Set-up time for a repeated START condition

tHD;DAT

Data hold time

tSU;DAT

Data set-up time

tr

Rise time of both SDA and SCL signals

tf

Fall time of both SDA and SCL signals

tSU;STO

Set-up time for STOP condition

tBUF

Bus free time between STOP and START condition

tSP

Pulse width of spikes which must be suppressed by the input

filter

Cb

Capacitive load for each bus line

18

MAX

100

fSCL

(1)

(2)

NOM

UNIT

kHz

400

SCL = 100 kHz

4

µs

SCL = 400 kHz

600

ns

SCL = 100 kHz

4.7

SCL = 400 kHz

1.3

SCL = 100 kHz

4

SCL = 400 kHz(1)

1

µs

µs

SCL = 100 kHz

4.7

µs

SCL = 400 kHz

600

ns

SCL = 100 kHz

0

3.45

µs

SCL = 400 kHz

0

900

ns

SCL = 100 kHz

250

SCL = 400 kHz

100

ns

SCL = 100 kHz

1000

SCL = 400 kHz

300

SCL = 100 kHz

300

SCL = 400 kHz

300

ns

ns

SCL = 100 kHz

4

µs

SCL = 400 kHz

600

ns

SCL = 100 kHz

4.7

SCL = 400 kHz

1.3

SCL = 100 kHz

—(2)

—(2)

SCL = 400 kHz

0

50

µs

SCL = 100 kHz

400

SCL = 400 kHz

400

ns

pF

The SCL duty cycle at 400 kHz must be > 40%.

The inputs of I2C devices in Standard-mode do not require spike suppression.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

7.7 Typical Characteristics

0.3%

0.25%

0.2%

0.15%

0.1%

0.05%

0

-0.05%

-0.1%

-0.15%

-0.2%

-0.25%

-0.3%

-0.35%

-0.4%

VIN = 3.6 V

VIN = 5 V

Accuracy

Accuracy

At TJ = 25°C unless otherwise noted.

0

0.2

0.4

0.6

0.8

1

1.2

Output Current (A)

1.4

1.6

0.15%

0.1%

0.05%

0

-0.05%

-0.1%

-0.15%

-0.2%

-0.25%

-0.3%

-0.35%

-0.4%

-0.45%

-0.5%

-0.55%

VIN = 3.6 V

VIN = 5 V

0

1.8

0.2

0.4

D001

1.6

1.8

D002

Figure 7-2. DCDC2 Accuracy

Figure 7-1. DCDC1 Accuracy

0.75%

0.1%

VIN = 3.6 V

VIN = 5 V

0.05%

VIN = 3.6 V

VIN = 5 V

0.5%

0.25%

Accuracy

0

Accuracy

1.4

VOUT = 1.1 V

VOUT = 1.1 V

-0.05%

-0.1%

-0.15%

0

-0.25%

-0.5%

-0.75%

-0.2%

-1%

-0.25%

-1.25%

0

0.2

0.4

0.6

0.8

1

1.2

Output Current (A)

1.4

1.6

1.8

0

0.2

0.4

D003

1.4%

VIN = 3.6 V

VIN = 5 V

1%

0.8%

Accuracy

0.6%

0.4%

0.2%

0

-0.2%

-0.4%

-0.6%

-0.8%

0

0.005

0.01

0.015

Output Current (A)

1.2

1.4

1.6

D004

Figure 7-4. DCDC4 Accuracy

Figure 7-3. DCDC3 Accuracy

1.2%

0.6

0.8

1

Output Current (A)

VOUT = 3.3 V

VOUT = 1.2 V

Accuracy

0.6

0.8

1

1.2

Output Current (A)

0.02

0.025

0.05%

0

-0.05%

-0.1%

-0.15%

-0.2%

-0.25%

-0.3%

-0.35%

-0.4%

-0.45%

-0.5%

-0.55%

-0.6%

VIN = 3.6 V

VIN = 5 V

0

0.005

D005

0.01

0.015

Output Current (A)

0.02

0.025

D006

VOUT = 1.8 V

VOUT = 1 V

Figure 7-5. DCDC5 Accuracy

Figure 7-6. DCDC6 Accuracy

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

19

�TPS6521815

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

www.ti.com

8 Detailed Description

8.1 Overview

The TPS6521815 provides three step-down converters, three load switches, three general-purpose I/Os, two

battery backup supplies, one buck-boost converter, and one LDO. The system can be supplied by a regulated 5V supply. A coin-cell battery can be added to supply the two always-on backup supplies. The device is

characterized across a –40°C to +105°C temperature range, which makes it suitable for various industrial

applications.

The I2C interface provides comprehensive features for using TPS6521815. All rails, load switches , and GPIOs

can be enabled and disabled. Voltage thresholds for the UVLO and supervisor can be customized. Power-up

and power-down sequences can also be programmed through I2C. Interrupts for overtemperature, overcurrent,

and undervoltage can be monitored for the load-switches (LSx).

The integrated voltage supervisor monitors DCDC 1-4 and LDO1. It has two settings; the standard settings only

monitor for undervoltage, while the strict settings implement tight tolerances on both undervoltage and

overvoltage. A power-good signal is provided to report the regulation state of the five rails.

The three hysteretic step-down converters can each supply up to 1.8 A of current. The default output voltages for

each converter can be adjusted through the I2C interface. DCDC1 and DCDC2 features dynamic voltage scaling

with an adjustable slew rate. The step-down converters operate in a low power mode at light load, and can be

forced into power mode (PWM) operation for noise sensitive applications.

The battery backup supplies consist of two low power step-down converters optimized for very light loads and

are monitored with a separate power-good signal (PGOOD_BU). The converters can be configured to operate as

always-on supplies with the addition of a coin cell battery. The state of the battery can be monitored over I2C.

20

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

8.2 Functional Block Diagram

PGOOD_BU

To SOC

VDD_10 (1 V)

Battery-backup

22 …F domain supply

L5 10 µH

DCDC6 (1.8 V)

DCDC5_PG

DCDC6_PG

DCDC5

FB5

DCDC6 (1.8 V)

IN_nCC

To SOC

DCDC6

FB6

IN_BU

2.7-V to 5.5-V

system power

10

Coin

cell

CC

SYS_BU

+

1 …F

4.7 …F 4.7 …F

±

From 1.8-V to 5.5-V

supply

IN_LDO1

0.9-V to 3.3-V analog supply

(adjustable, default 1.8 V)

LDO1

Always-on coin-cell battery backup supplies

LS2

LDO1

IN_LS2

From 3-V to 5.5-V

supply

LS2

100-mA / 500-mA

load switch

10 …F

10 …F

IN_LS1

From 1.2-V to 3.3-V

supply

LS1

200-mA load switch

LS3

LS1

IN_LS3

From 1.8-V to 10-V

supply

LS3

500-mA load

switch

10 …F

10 …F

IN_DCDC3

From 2.7-V to 5.5-V

system power

IN_DCDC1

4.7 …F

4.7 …F

FB3

10 …F

DCDC3

DCDC1

IN_DCDC4

From 2.7-V to 5.5-V

system power

4.7 …F

FB1

1.1-V core supply

(adjustable)

10 …F

IN_DCDC2

From 2.7-V to 5.5-V

system power

4.7 …F

L4A

L2 10 µH

L4B

DCDC4

DCDC2

FB2

1.1-V MPU supply

(adjustable)

10 …F

DCDC4

3.3-V I/O supply

(adjustable)

IN_BIAS

47 …F

VSELECT

Input Power

VIO

VREF

10

1 …F

Supervisor

and up,

down

sequencer

VIO VDD_18

(1.8 V / (DCDC6)

3.3 V)

+

±

OD

2

10

SDA

PWR_EN

IC

GPIO1

AC_DET

IN_BIAS

100 k

VIO

(1.8 V /

3.3 V)

To SOC

To SOC

To SOC

DIGITAL

IN_LS1

Momentary push-button

VIO

(1.8 V /

3.3 V)

To SOC

nWAKEUP

nINT

OD

100 k

IN_BIAS

100 k

nPFO

PGOOD

OD

SCL

From SOC

From SOC

INT_LDO

BIAS

VDCDC1

VDCDC2

VDCDC3

VDCDC4

LDO1

OD

PFI

VIO

From 2.7-V to 5.5-V

system power

100 nF

DC34_SEL

From external

charger

From 2.7-V to 5.5-V

system power

L1 10 µH

L3

1.5-V DDR3 supply

(adjustable)

From SOC

VDD_18 (1.8 V)

Battery-backup

domain supply

22 …F

L6 10 µH

OD

GPIO2

OD

GPIO3

PB

From SOC

To DDR3 memory

From SOC

OD

Thermal

Pad

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

21

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

8.3 Feature Description

8.3.1 Wake-Up and Power-Up and Power-Down Sequencing

The TPS6521815 has a predefined power-up and power-down sequence, which does not change in a typical

application. The user can define custom sequences with I2C. The power-up sequence is defined by a series of

ten strobes and nine delay times. Each output rail is assigned to a strobe to determine the order of enabling

rails. A single rail is assigned to only one strobe, but multiple rails can be assigned to the same strobe. The

delay times between strobes are between 2 ms and 5 ms.

8.3.1.1 Power-Up Sequencing

When the power-up sequence initiates, STROBE 1 occurs, and any rail assigned to this strobe is enabled. After

a delay time of DLY1, STROBE 2 occurs and the rail assigned to this strobe is powered up. The sequence

continues until all strobes occur and all DLYx times execute. Strobe assignments and delay times are defined in

the SEQx registers, and are changed under I2C control. The power-up sequence executes if one of the following

events occurs:

• From the OFF state:

– The push-button (PB) is pressed (falling edge on PB) or

– The AC_DET pin is pulled low (falling edge) or

– The PWR_EN is asserted (driven to high-level) or

– The main power is connected (IN_BIAS) and AC_DET is grounded and

– The device is not in undervoltage lockout (UVLO) or overtemperature shutdown (OTS).

• From the PRE_OFF state:

– The PB is pressed (falling edge on PB) or

– The AC_DET pin is pulled low (falling edge) or

– The PWR_EN is asserted (driven to high-level) and

– The device is not in UVLO or OTS.

• From the SUSPEND state:

– The PB is pressed (falling edge on PB) or

– The AC_DET pin is pulled low (falling edge) or

– The PWR_EN pin is pulled high (level sensitive) and

– The device is not in UVLO or OTS.

When a power-up event is detected, the device enters a WAIT_PWR_EN state and triggers the power-up

sequence. The device remains in WAIT_PWR_EN as long as the PWR_EN and either the PB or AC_DET pin

are held low. If both, the PB and AC_DET return to logic-high state and the PWR_EN pin has not been asserted

within 20 s of entering WAIT_PWR_EN state, the power-down sequence is triggered and the device returns to

OFF state. Once PWR_EN is asserted, the device advances to ACTIVE state, which is functionally equivalent to

WAIT_PWR_EN. However, the AC_DET pin is ignored and power-down is controlled by the PWR_EN pin only.

Rails not assigned to a strobe (SEQ = 0000b) are not affected by power-up and power-down sequencing and

remain in their current ON or OFF state regardless of the sequencer. A rail can be enabled and disabled at any

time by setting the corresponding enable bit in the ENABLEx register, with the exception that the ENABLEx

register cannot be accessed while the sequencer is active. Enable bits always reflect the current enable state of

the rail. For example, the sequencer sets and resets the enable bits for the rails under its control.

Note

The power-up sequence is defined by strobes and delay times, and can be triggered by the PB,

AC_DET (not shown, same as PB), or PWR_EN pin.

22

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

PB (input)

nWAKEUP

(output)

PWR_EN

(input)

DLY1

DLY2

DLY3

DLY4

DLY5

DLY6

DLY7

DLY8

DLY9

STROBE 1

STROBE 2

STROBE 3

STROBE 4

STROBE 5

STROBE 6

STROBE 7

STROBE 8

STROBE 9 STROBE 10

SEQ = 0001b SEQ = 0010b SEQ = 0011b SEQ = 0100b SEQ = 0101b SEQ = 0110b SEQ = 0111b SEQ = 1000b SEQ = 1001b SEQ = 1010b

Push-button deglitch time is not shown.

Figure 8-1. Power-Up Sequences from OFF or SUSPEND State; PB is Power-Up Event

PB (input)

nWAKEUP

(output)

PWR_EN

(input)

DLY1

DLY2

DLY3

DLY4

DLY5

DLY6

DLY7

DLY8

DLY9

STROBE 1

STROBE 2

STROBE 3

STROBE 4

STROBE 5

STROBE 6

STROBE 7

STROBE 8

STROBE 9 STROBE 10

SEQ = 0001b SEQ = 0010b SEQ = 0011b SEQ = 0100b SEQ = 0101b SEQ = 0110b SEQ = 0111b SEQ = 1000b SEQ = 1001b SEQ = 1010b

Figure 8-2. Power-Up Sequences from SUSPEND State; PWR_EN is Power-Up Event

FAULT Recovery

PB (input)

nWAKEUP

(output)

PWR_EN

(input)

DLY1

DLY2

DLY3

DLY4

DLY5

DLY6

DLY7

DLY8

DLY9

STROBE 1

STROBE 2

STROBE 3

STROBE 4

STROBE 5

STROBE 6

STROBE 7

STROBE 8

STROBE 9 STROBE 10

SEQ = 0001b SEQ = 0010b SEQ = 0011b SEQ = 0100b SEQ = 0101b SEQ = 0110b SEQ = 0111b SEQ = 1000b SEQ = 1001b SEQ = 1010b

Figure 8-3. Power-Up Sequences from RECOVERY State

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

23

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

8.3.1.2 Power-Down Sequencing

By default, the power-down sequence follows the reverse of the power-up sequence. When the power-down

sequence is triggered, STROBE 10 occurs and any rail assigned to STROBE 10 is shut down and its discharge

circuit is enabled. After a delay time of DLY9, STROBE 9 occurs and any rail assigned to it is shut down and its

discharge circuit is enabled. The sequence continues until all strobes occur and all DLYx times execute. The

DLYx times are extended by a factor of 10x to provide ample time for discharge, and preventing output voltages

from crossing during shut-down. The DLYFCTR bit is applied globally to all power-down delay times. Regardless

of the DLYx and DLYFCTR settings, the PMIC enters OFF, SUSPEND, or RECOVERY state 500 ms after the

power-down sequence initiates, to ensure that the discharge circuits remain enabled for a minimum of 150 ms

before the next power-up sequence starts.

A power-down sequence executes if one of the following events occurs:

• The device is in the WAIT_PWR_EN state, the PB and AC_DET pins are high, PWR_EN is low, and the 20-s

timer has expired.

• The device is in the ACTIVE state and the PWR_EN pin is pulled low.

• The device is in the WAIT_PWR_EN, ACTIVE, or SUSPEND state and the push-button is held low for > 8 s

(15 s if TRST = 1b).

• A fault occurs in the device (OTS, UVLO, PGOOD failure).

When transitioning from ACTIVE to SUSPEND state, the rails not controlled by the power-down sequencer

maintains the same ON/OFF state in SUSPEND state that it had in ACTIVE state. This allows for the selected

power rails to remain powered up when in the SUSPEND state.

When transitioning to the OFF or RECOVERY state, rails not under sequencer control are shut-down as follows:

• DCDC1, DCDC2, DCDC3, DCDC4, LDO1, and LS1 shut down at the beginning of the power-down

sequence, if not under sequencer control (SEQ = 0b).

• LS2 and LS3 shut down as the state machine enters an OFF or RECOVERY state; 500 ms after the powerdown sequence is triggered.

If the supply voltage on IN_BIAS drops below 2.5 V, the digital core is reset and all power rails are shut down

instantaneously and are pulled low to ground by their internal discharge circuitry (DCDC1-4, and LDO1). The

amount of time the discharge circuitry remains active is a function of the INT_LDO hold up time (see Section

8.3.1.6 for more details).

8.3.1.3 Strobe 1 and Strobe 2

STROBE 1 and STROBE 2 are dedicated to DCDC5 and DCDC6 which are always-on; powered up as soon as

the device exits the OFF state, and ON in any other state. STROBE 1 and STROBE 2 options are available only

for DCDC5 and DCDC6, not for any other rails.

STROBE 1 and STROBE 2 occur in every power-up sequence, regardless if the rail is already powered up. If the

rail is not to be powered up, its respective strobe setting must be set to 0x00.

When a power-down sequence initiates, STROBE 1 and STROBE 2 occur only if the FSEAL bit is 0b.

Otherwise, both strobes are omitted and DCDC5 and DCDC6 maintain state.

Note

The power-down sequence follows the reverse of the power-up sequence. STROBE2 and STROBE1

are executed only if FSEAL bit is 0b.

24

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

PB (input)

nWAKEUP

(output)

PWR_EN

(input)

DLY9

DLY8

DLY7

DLY6

DLY5

DLY4

DLY3

DLY2

DLY1

STROBE 10 STROBE 9

STROBE 8

STROBE 7

STROBE 6

STROBE 5

STROBE 4

STROBE 3

STROBE 2

STROBE 1

SEQ = 1010b SEQ = 1001b SEQ = 1000b SEQ = 0111b SEQ = 0110b SEQ = 0101b SEQ = 0100b SEQ = 0011b SEQ = 0010b SEQ = 0001b

Figure 8-4. Power-Down Sequences to OFF State; PWR_EN is Power-Down Event; FSEAL = 0b

PB (input)

nWAKEUP

(output)

PWR_EN

(input)

DLY9

DLY8

DLY7

DLY6

DLY5

DLY4

DLY3

STROBE 10 STROBE 9

STROBE 8

STROBE 7

STROBE 6

STROBE 5

STROBE 4

STROBE 3

SEQ = 1010b SEQ = 1001b SEQ = 1000b SEQ = 0111b SEQ = 0110b SEQ = 0101b SEQ = 0100b SEQ = 0011b

STROBE2 and STROBE1 are not shown.

Figure 8-5. Power-Down Sequences to SUSPEND State; PWR_EN is Power-Down Event; FSEAL = 1b

PB (input)

PWR_EN

(input)

FAULT

nWAKEUP

(output)

DLY9

DLY8

DLY7

DLY6

DLY5

DLY4

DLY3

STROBE 10 STROBE 9

STROBE 8

STROBE 7

STROBE 6

STROBE 5

STROBE 4

STROBE 3

SEQ = 1010b SEQ = 1001b SEQ = 1000b SEQ = 0111b SEQ = 0110b SEQ = 0101b SEQ = 0100b SEQ = 0011b

STROBE2 and STROBE1 are not shown.

Figure 8-6. Power-Down Sequences to RECOVERY State; TSD or UV is Power-Down Event; FSEAL = 1b

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

25

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

8.3.1.4 Supply Voltage Supervisor and Power-Good (PGOOD)

Power-good (PGOOD) is an open-drain output of the built-in voltage supervisor that monitors DCDC1, DCDC2,

DCDC3, DCDC4, and LDO1. The output is Hi-Z when all enabled rails are in regulation and driven low when one

or more rails encounter a fault which brings the output voltage outside the specified tolerance range. In a typical

application PGOOD drives the reset signal of the SOC.

The supervisor has two modes of operation, controlled by the STRICT bit. With the STRICT bit set to 0, all

enabled rails of the five regulators are monitored for undervoltage only with relaxed thresholds and deglitch

times. With the STRCT bit set to 1, all enabled rails of the five regulators are monitored for undervoltage and

overvoltage with tight limits and short deglitch times. Table 8-1 summarizes these details.

Table 8-1. Supervisor Characteristics Controlled by the STRICT Bit

PARAMETER

Undervoltage

monitoring

Overvoltage

monitoring

STRICT = 0b (TYP)

STRICT =1b (TYP)

Threshold (output falling)

90%

96.5% (DCDC1 and DCDC2)

95.5% (DCDC3, DCDC4, and LDO1)

Deglitch (output falling)

1 ms

50 µs

Deglitch (output rising)

10 µs

10 µs

Threshold (output falling)

N/A

103.5% (DCDC1 and DCDC2)

104.5% (DCDC3, DCDC4, and

LDO1)

Deglitch (output falling)

N/A

1 ms

Deglitch (output rising)

N/A

50 µs

Overvoltage threshold

(output rising)

LDO1

Hysteresis

Undervoltage threshold

(output falling)

Hysteresis

Power-good comparator

output (internal signal)

Voltage droop has no effect on

PGOOD output if duration is

less than deglitch time.

Voltage droop has no effect on

PGOOD output if duration is

less than deglitch time.

PGOOD

Deglitch time

Figure 8-7. Definition of Undervoltage, Overvoltage Thresholds, Hysteresis, and Deglitch Times

The following rules apply to the PGOOD output:

• The power-up default state for THE PGOOD is low. When all rails are disabled, the PGOOD output is driven

low.

• Only enabled rails are monitored. Disabled rails are ignored.

• Power-good monitoring of a particular rail starts 5 ms after the rail is enabled and is continuously monitored

thereafter. This allows the rail to power-up.

• The PGOOD is delayed by PGDLY time after the sequencer is finished and the last rail is enabled.

• If an enabled rail is continuously outside the monitoring threshold for longer than the deglitch time, then the

PGOOD is pulled low, and all rails are shut-down following the power-down sequence. PGDLY does not

apply.

• Disabling a rail manually by resetting the DCx_EN or LDO1_EN bit has no effect on the PGOOD pin. If all

rails are disabled, the PGOOD is driven low as the last rail is disabled.

• If the power-down sequencer is triggered, PGOOD is driven low.

• The PGOOD is driven low in the SUSPEND state, regardless of the number of rails that are enabled.

26

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

Figure 8-8 shows a typical power-up sequence and PGOOD timing.

VSYS

5 s (maximum)

PB

nWAKEUP

PWR_EN

(deglitched)

LDO1

DLY1 + DLY2

5 ms

DLY4 + DLY3

PG LDO1

(internal)

DCDC3

FAULT

DLY3 + DLY4

5 ms

DLY6 + DLY5

PG DCDC3

(internal)

DCDC4

DLY5 + DLY6

5 ms

DLY7

PG DCDC4

(internal)

DCDC1

DLY7

5 ms

DLY8

PG DCDC1

(internal)

DLY8

DCDC2

5 ms

DLY9

PG DCDC2

(internal)

PG_DLY

PGOOD

A. Sequence shown for TPS65218D0 variant. For other TPS65218xx variants, refer to registers SEQ1-7 in Section 8.6.4 for factoryprogrammed sequence order and timing.

Figure 8-8. Typical Power-Up Sequence of the Main Output Rails for TPS65218D0

8.3.1.5 Backup Supply Power-Good (PGOOD_BU)

PGOOD_BU is a push-pull output indicating if DCDC5 and DCDC6 are in regulation. The output is driven to high

when both rails are in regulation, and driven low if at least one of the rails is below the power-good threshold.

The output-high level is equal to the output voltage of DCDC6.

PGOOD_BU is the logical and between PGOOD (DCDC5) and PGOOD (DCDC6), and has no delay time builtin. Unlike the main power-good, a fault on DCDC5 or DCDC6 does not trigger the power-down sequencer, does

not disable any of the rails in the system, and has no effect on the PGOOD pin. DCDC5 and DCDC6 recover

automatically once the fault is removed.

Note

In this example, the power-down is triggered by a fault on DCDC3.

This timing diagram assumes each rail powers up within the strobe delay time. If a rail takes longer

than the strobe delay time to power up, the next rail will wait for the previous rail to reach its PGOOD

voltage, and then may wait an additional 1 ms until it is enabled.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS6521815

27

�TPS6521815

www.ti.com

SLDS261A – NOVEMBER 2019 – REVISED FEBRUARY 2021

VSYS

5 s (maximum)

PB

nWAKEUP

PWR_EN

(deglitched)

DCDC6

PG DCDC6

(internal)

DCDC5

DLY1

PG DCDC5

(internal)

PGOOD_BU

A. Sequence shown for TPS65218D0 and TPS6521825 variants. For TPS6521815 variant, order and timing of DCDC5 and DCDC6 can be

modified using registers SEQ1-2 and SEQ5 in Section 8.6.4 .

Figure 8-9. Typical Power-Up Sequence of DCDC5 and DCDC6

8.3.1.6 Internal LDO (INT_LDO)

The internal LDO provides a regulated voltage to the internal digital core and analog circuitry. The internal LDO

has a nominal output voltage of 2.5 V and can support up to 10 mA of external load. During EEPROM

programming, the output voltage is elevated to 3.6 V as described in Section 8.5.1. Therefore, any external

circuitry connected to INT_LDO must be capable of supporting that voltage.