内置 EEPROM 增强 A/D 型单片机

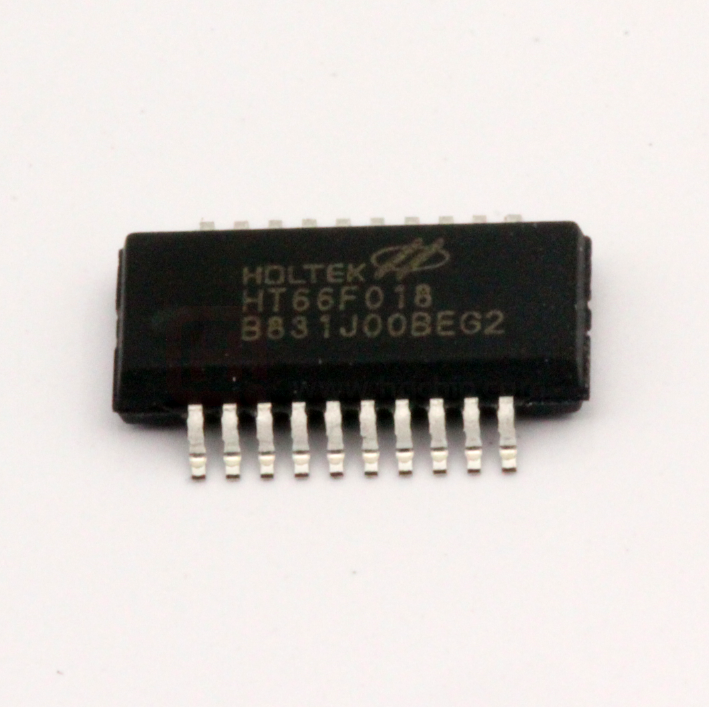

HT66F018

版本 : V1.50

日期 : 2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

目录

特性 .................................................................................................................................6

CPU 特性 ............................................................................................................................... 6

周边特性 ................................................................................................................................ 6

概述 .................................................................................................................................7

方框图 .............................................................................................................................7

引脚图 .............................................................................................................................8

引脚说明 .........................................................................................................................8

极限参数 .......................................................................................................................10

直流电气特性 ............................................................................................................... 11

交流电气特性 ...............................................................................................................14

ADC 电气特性 ..............................................................................................................15

LVD&LVR 电气特性 ...................................................................................................16

比较器电气特性 ...........................................................................................................17

上电复位特性 ...............................................................................................................17

带隙参考电压 (VBG) 特性曲线 ....................................................................................18

系统结构 .......................................................................................................................18

时序和流水线结构 .............................................................................................................. 18

程序计数器 .......................................................................................................................... 19

堆栈 ...................................................................................................................................... 20

算术逻辑单元 – ALU .......................................................................................................... 20

Flash 程序存储器 ........................................................................................................21

结构 ...................................................................................................................................... 21

特殊向量 .............................................................................................................................. 21

查表 ...................................................................................................................................... 21

查表范例 .............................................................................................................................. 22

在线烧录 .............................................................................................................................. 22

片上调试 .............................................................................................................................. 23

数据存储器 ...................................................................................................................24

结构 ...................................................................................................................................... 24

特殊功能寄存器 ...........................................................................................................25

间接寻址寄存器 – IAR0,IAR1 ........................................................................................ 25

间接寻址指针 – MP0,MP1............................................................................................... 25

存储区指针 – BP ................................................................................................................. 26

累加器 – ACC ...................................................................................................................... 26

程序计数器低字节寄存器 – PCL ....................................................................................... 26

表格寄存器 – TBLP,TBHP,TBLH ................................................................................ 26

状态寄存器 – STATUS ........................................................................................................ 27

Rev. 1.50

2

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

EEPROM 数据寄存器 .................................................................................................29

EEPROM 数据寄存器结构 ................................................................................................. 29

EEPROM 寄存器 ................................................................................................................. 29

从 EEPROM 中读取数据 .................................................................................................... 31

写数据到 EEPROM ............................................................................................................. 31

写保护 .................................................................................................................................. 31

EEPROM 中断 ..................................................................................................................... 31

编程注意事项 ...................................................................................................................... 31

振荡器 ...........................................................................................................................33

振荡器概述 .......................................................................................................................... 33

系统时钟配置 ...................................................................................................................... 33

外部晶体 / 陶瓷振荡器 – HXT ........................................................................................... 34

内部 RC 振荡器 – HIRC ..................................................................................................... 34

外部 32.768kHz 晶体振荡器 – LXT ................................................................................... 35

内部 32kHz 振荡器 – LIRC ................................................................................................ 36

辅助振荡器 .......................................................................................................................... 36

工作模式和系统时钟 ...................................................................................................37

系统时钟 .............................................................................................................................. 37

系统工作模式 ...................................................................................................................... 38

控制寄存器 .......................................................................................................................... 39

快速唤醒 .............................................................................................................................. 40

工作模式切换 ...................................................................................................................... 41

静态电流的注意事项 .......................................................................................................... 45

唤醒 ...................................................................................................................................... 45

编程注意事项 ...................................................................................................................... 45

看门狗定时器 ...............................................................................................................46

看门狗定时器时钟源 .......................................................................................................... 46

看门狗定时器控制寄存器 .................................................................................................. 46

看门狗定时器操作 .............................................................................................................. 47

复位和初始化 ...............................................................................................................48

复位功能 .............................................................................................................................. 48

复位初始状态 ...................................................................................................................... 50

输入 / 输出端口 ............................................................................................................53

上拉电阻 .............................................................................................................................. 53

PA 口唤醒 ........................................................................................................................... 54

输入 / 输出端口控制寄存器 ............................................................................................... 55

输入 / 输出引脚结构 ........................................................................................................... 56

编程注意事项 ..................................................................................................................... 57

定时器模块 – TM .........................................................................................................57

简介 ..................................................................................................................................... 57

TM 操作 .............................................................................................................................. 58

TM 时钟源 .......................................................................................................................... 58

TM 中断 .............................................................................................................................. 58

TM 外部引脚 ....................................................................................................................... 58

Rev. 1.50

3

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

TM 输入 / 输出引脚控制寄存器 ........................................................................................ 59

编程注意事项 ...................................................................................................................... 60

简易型 TM ....................................................................................................................61

简易型 TM 操作 ................................................................................................................. 61

简易型 TM 寄存器介绍 ...................................................................................................... 62

简易型 TM 工作模式 ......................................................................................................... 66

标准型 TM – STM .......................................................................................................72

标准型 TM 操作 .................................................................................................................. 72

标准型 TM 寄存器介绍 ..................................................................................................... 73

标准型 TM 工作模式 ......................................................................................................... 76

周期型 TM – PTM .......................................................................................................86

周期型 TM 操作 .................................................................................................................. 86

周期型 TM 寄存器介绍 ...................................................................................................... 87

周期型 TM 工作模式 .......................................................................................................... 91

A/D 转换器..................................................................................................................100

A/D 简介 ............................................................................................................................ 100

A/D 转换寄存器介绍 ........................................................................................................ 100

A/D 操作 ............................................................................................................................ 105

A/D 输入引脚 .................................................................................................................... 106

A/D 转换步骤 .................................................................................................................... 106

编程注意事项 .................................................................................................................... 107

A/D 转换功能 .................................................................................................................... 107

A/D 转换应用范例 ............................................................................................................ 108

比较器 ......................................................................................................................... 110

比较器操作 ........................................................................................................................ 110

比较器中断 .........................................................................................................................111

编程注意事项 .....................................................................................................................111

中断 ............................................................................................................................. 112

中断寄存器 ........................................................................................................................ 112

中断操作 ............................................................................................................................ 116

外部中断 ............................................................................................................................ 117

比较器中断 ........................................................................................................................ 117

多功能中断 ........................................................................................................................ 118

A/D 转换器中断 ................................................................................................................ 118

时基中断 ............................................................................................................................ 118

EEPROM 中断 ................................................................................................................... 119

LVD 中断 ........................................................................................................................... 120

TM 中断 ............................................................................................................................. 120

中断唤醒功能 .................................................................................................................... 120

编程注意事项 .................................................................................................................... 120

低电压检测 – LVD .....................................................................................................121

LVD 寄存器 ....................................................................................................................... 121

LVD 操作 ........................................................................................................................... 122

配置选项 .....................................................................................................................122

Rev. 1.50

4

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

应用电路 .....................................................................................................................123

指令集 .........................................................................................................................124

简介 .................................................................................................................................... 124

指令周期 ............................................................................................................................ 124

数据的传送 ........................................................................................................................ 124

算术运算 ............................................................................................................................ 124

逻辑和移位运算 ................................................................................................................ 124

分支和控制转换 ................................................................................................................ 125

位运算 ................................................................................................................................ 125

查表运算 ............................................................................................................................ 125

其它运算 ............................................................................................................................ 125

指令集概要 .................................................................................................................126

惯例 .................................................................................................................................... 126

指令定义 .....................................................................................................................129

封装信息 .....................................................................................................................141

16-pin NSOP (150mil) 外形尺寸 ....................................................................................... 142

20-pin SOP (300mil) 外形尺寸.......................................................................................... 143

20-pin SSOP (150mil) 外形尺寸 ....................................................................................... 144

Rev. 1.50

5

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

特性

CPU 特性

● 工作电压:

♦ fSYS=8MHz:2.2V~5.5V

♦ fSYS=12MHz:2.7V~5.5V

♦ fSYS=16MHz:3.3V~5.5V

♦ fSYS=20MHz:4.5V~5.5V

● VDD=5V,系统时钟为 20MHz 时,指令周期为 0.2μs

● 提供暂停和唤醒功能,以降低功耗

● 四种振荡器类型:

♦ 外部晶振 – HXT

♦ 外部 32.768kHz 晶振 – LXT

♦ 内部 RC – HIRC

♦ 内部 32kHz RC – LIRC

● 多种工作模式:正常、低速、空闲和休眠

● 内部集成 8/12/16MHz 振荡器,无需外接元件

● 所有指令都可在 1 或 2 个指令周期内完成

● 查表指令

● 63 条指令

● 8 层堆栈

● 位操作指令

周边特性

● Flash 程序存储:4K×16

● RAM 数据存储:192×8

● EEPROM 存储器:64×8

● 看门狗定时器功能

● 18 个双向 I/O 口

● 2 个引脚与外部中断口共用

● 多个定时器模块用于时间测量、捕捉输入、比较匹配输出、PWM 输出及单脉

冲输出

● 比较器功能

● 双时基功能可提供固定时间的中断信号

● 8 通道 12-bit 的 A/D 转换器

● 低电压复位功能

● 低电压检测功能

● Flash 程序存储器烧录可达 100,000 次

● Flash 程序存储器数据可保存 10 年以上

● EEPROM 数据存储器烧录可达 1,000,000 次

● EEPROM 数据存储器数据可保存 10 年以上

● 封装类型:16-pin NSOP,20-pin SOP/SSOP

Rev. 1.50

6

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

概述

该单片机是 8 位高性能精简指令集的 Flash 型单片机,具有一系列功能和特性,

其 Flash 存储器可多次编程的特性给用户提供了极大的方便。存储器方面,还

包含了一个 RAM 数据存储器和一个可用于存储序列号、校准数据等非易失性

数据的 EEPROM 存储器。

在模拟特性方面,该单片机包含一个多通道 12 位 A/D 转换器和比较器功能。

还带有多个使用灵活的定时器模块,可提供定时功能、脉冲产生功能及 PWM

产生等功能。内部看门狗定时器、低电压复位和低电压检测等内部保护特性,

外加优秀的抗干扰和 ESD 保护性能,确保单片机在恶劣的电磁干扰环境下可靠

地运行。

该单片机提供了丰富的 HXT、LXT、HIRC 和 LIRC 振荡器功能选项,且内建

完整的系统振荡器,无需外接元件。其在不同工作模式之间动态切换的能力,

为用户提供了一个优化单片机操作和减少功耗的手段。

外加时基功能、I/O 使用灵活等其它特性,使这款单片机可以广泛应用于各种

产品中,例如电子测量仪器、环境监控、手持式测量工具、家庭应用、电子控

制工具、马达控制等方面。

方框图

Rev. 1.50

7

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

引脚图

VSS&AVSS

1

16

VDD&AVDD

PC0/OSC1

2

15

PB0/INT0/AN0/XT1

PC1/OSC2

3

14

PB1/INT1/AN1/XT2

PC2

4

13

PB2/TCK0/AN2

PA0/TP0/ICPDA/OCDSDA

5

12

PA4/TCK1/AN3

PA1

6

11

PA5/AN4/VREF

PA2/ICPCK/OCDSCK

7

10

PA6/TCK2/AN5

PA3/CX

8

9

PA7/TP1/AN6

HT66F018

16 NSOP-A

VSS&AVSS

1

20

VDD&AVDD

PC0/OSC1

2

19

PB0/INT0/AN0/XT1

PC1/OSC2

3

18

PB1/INT1/AN1/XT2

PC2

4

17

PB2/TCK0/AN2

PA0/TP0/ICPDA/OCDSDA

5

16

PA4/TCK1/AN3

PA1

6

15

PA5/AN4/VREF

PA2/ICPCK/OCDSCK

7

14

PA6/TCK2/AN5

PA3/CX

8

13

PA7/TP1/AN6

PB6/C+

9

12

PB3/TP2/AN7

PB5/C-

10

11

PB4/CLO

HT66F018

20 SOP-A/SSOP-A

注:1. 若共用引脚同时有多种输出,“/”号右侧的引脚名具有更高的优先级。

2. VDD&AVDD 指的是 VDD 和 AVDD 为同一个引脚。

3. VSS&AVSS 指的是 VSS 和 AVSS 为同一个引脚。

引脚说明

除了电源引脚外,该系列单片机的所有引脚都以它们的端口名称进行标注,例

如 PA0、PA1 等,用于描述这些引脚的数字输入 / 输出功能。然而,这些引脚

也与其它功能共用,如模数转换器、定时器模块等。每个引脚的功能如下表所

述,而引脚配置的详细内容见规格书其它章节。

引脚名称

功能

OP

I/T

O/T

引脚说明

PAPU

通用 I/O 口,可通过寄存器设置上拉电阻

ST CMOS

PA0

PAWU

和唤醒功能

TP0

TMPC ST CMOS TM0 输出

PA0/TP0/ICPDA/

OCDSDA

ICPDA

—

ST CMOS 在线烧录地址 / 数据输入 / 输出

OCDS 地址 / 数据输入 / 输出,仅对于

OCDSDA

—

ST CMOS

EV 芯片

PAPU

通用 I/O 口,可通过寄存器设置上拉电阻

PA1

ST CMOS

PA1

PAWU

和唤醒功能

PAPU

通用 I/O 口,可通过寄存器设置上拉电阻

PA2

ST CMOS

PAWU

和唤醒功能

PA2/ICPCK /

OCDSCK

ICPCK

—

ST

—

在线烧录时钟输入引脚

OCDSCK

—

ST

—

OCDS 时钟输入引脚,只对于 EV 芯片

Rev. 1.50

8

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

引脚名称

PA3/CX

功能

PA3

CX

PA4

PA4/TCK1/AN3

TCK1

AN3

PA5

PA5/AN4/VREF

AN4

VREF

PA6

PA6/TCK2/AN5

TCK2

AN5

PA7

PA7/TP1/AN6

TP1

AN6

PB0

PB0/INT0/AN0 /

XT1

INT0

PB1/INT1/AN1 /

XT2

INT1

PB2/TCK0/AN2

PB3/TP2/AN7

PB4/CLO

PB5/CPB6/C+

Rev. 1.50

AN0

XT1

PB1

AN1

XT2

PB2

TCK0

AN2

PB3

TP2

AN7

PB4

CLO

PB5

CPB6

C+

OP

I/T

O/T

引脚说明

PAPU

通用 I/O 口,可通过寄存器设置上拉电阻

ST CMOS

PAWU

和唤醒功能

CPC

— CMOS 比较器输出

PAPU

通用 I/O 口,可通过寄存器设置上拉电阻

ST CMOS

PAWU

和唤醒功能

TM1C0 ST

—

TM1 输入引脚

ACERL AN

—

A/D 通道 3

PAPU

通用 I/O 口,可通过寄存器设置上拉电阻

ST CMOS

PAWU

和唤醒功能

ACERL AN

—

A/D 通道 4

ADCR1 AN

—

ADC 参考电压输入引脚

PAPU

通用 I/O 口,可通过寄存器设置上拉电阻

ST CMOS

PAWU

和唤醒功能

TM2C0 ST

—

TM2 输入引脚

ACERL AN

—

A/D 通道 5

PAPU

通用 I/O 口,可通过寄存器设置上拉电阻

ST CMOS

PAWU

和唤醒功能

TMPC ST CMOS TM1 输出引脚

ACERL AN

—

A/D 通道 6

PBPU

ST CMOS 通用 I/O 口,可通过寄存器设置上拉电阻

INTC0

ST

—

外部中断 0

INTEG

ACERL AN

—

A/D 通道 0

CO

LXT

—

LXT 引脚

PBPU

ST CMOS 通用 I/O 口,可通过寄存器设置上拉电阻

INTC2

ST

—

外部中断 1

INTEG

ACERL AN

—

A/D 通道 1

—

LXT LXT 引脚

CO

PBPU

ST CMOS 通用 I/O 口,可通过寄存器设置上拉电阻

TM0C0 ST

—

TM0 输入

ACERL AN

—

A/D 通道 2

PBPU

ST CMOS 通用 I/O 口,可通过寄存器设置上拉电阻

TMPC ST CMOS TM2 输出引脚

ACERL AN

—

A/D 通道 7

PBPU

ST CMOS 通用 I/O 口,可通过寄存器设置上拉电阻

TMPC ST CMOS 系统时钟输出

PBPU

ST CMOS 通用 I/O 口,可通过寄存器设置上拉电阻

CPC

AN

—

比较器负极输入

PBPU

ST CMOS 通用 I/O 口,可通过寄存器设置上拉电阻

CPC

AN

—

比较器正极输入

9

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

引脚名称

PC0/OSC1

PC1/OSC2

PC2

VDD*

AVDD*

VSS**

AVSS**

功能

PC0

OSC1

PC1

OSC2

PC2

VDD

AVDD

VSS

AVSS

OP

PCPU

CO

PCPU

CO

PCPU

—

—

—

—

I/T

O/T

引脚说明

ST CMOS 通用 I/O 口,可通过寄存器设置上拉电阻

HXT

—

HXT 引脚

ST CMOS 通用 I/O 口,可通过寄存器设置上拉电阻

—

HXT HXT 引脚

ST CMOS 通用 I/O 口,可通过寄存器设置上拉电阻

PWR

—

电源电压正极

PWR

—

ADC 电压正极

PWR

—

电源电压负极,接地

PWR

—

ADC 电压接地端

注:I/T:输入类型;

O/T:输出类型

OP:通过寄存器或配置选项(CO)设置

PWR:电源;

CO:配置选项;

ST:施密特触发输入

CMOS:CMOS 输出;

AN:模拟输入脚

HXT:高频晶体振荡器

LXT:低频晶体振荡器

*:VDD 是单片机电源电压,而 AVDD 是 ADC 电源电压。AVDD 与 VDD 在内部是同一个引脚。

**:VSS 是单片机地引脚,而 AVSS 是 ADC 地引脚。AVS 与 VSS 在内部是同一个引脚。

极限参数

电源供应电压 ................................................................................VSS-0.3V~VSS+6.0V

输入电压 ........................................................................................VSS-0.3V~VDD+0.3V

储存温度 ...................................................................................................-50˚C~150˚C

工作温度 .....................................................................................................-40˚C~85˚C

IOH 总电流 ......................................................................................................... -100mA

IOL 总电流.......................................................................................................... 100mA

总功耗 ................................................................................................................500mW

注:这里只强调额定功率,超过极限参数所规定的范围将对芯片造成损害,无

法预期芯片在上述标示范围外的工作状态,而且若长期在标示范围外的条

件下工作,可能影响芯片的可靠性。

Rev. 1.50

10

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

直流电气特性

Ta=25˚C

符号

参数

VDD

工作电压

(HXT, HIRC)

IDD1

工作电流,正常模式

fSYS=fH (HXT)

测试条件

条件

VDD

fSYS=8MHz

fSYS=12MHz

─

fSYS=16MHz

fSYS=20MHz

3V 无负载 , fH=4MHz,

5V ADC off, WDT 使能

3V 无负载 , fH=8MHz,

5V ADC off, WDT 使能

最小

典型

2.2

2.7

3.3

4.5

─

─

─

─

─

─

─

─

─

─

─

─

0.7

1.8

1.0

2.5

1.5

3.5

2.0

4.5

5.5

5.5

5.5

5.5

1.1

2.7

1.5

4.0

2.5

5.5

3.0

7.0

V

V

V

V

mA

mA

mA

mA

mA

mA

mA

mA

─

5.5

8.5

mA

─

─

─

─

─

─

2.0

3.0

3.0

4.5

4.0

6.0

2.8

4.5

4.2

6.7

5.6

9.0

mA

mA

mA

mA

mA

mA

3V 无负载 , fSYS=LXT,

ADC off, WDT 使能 ,

5V LXTLP=1

─

10

20

μA

─

30

50

μA

3V 无负载 , fSYS=LXT,

ADC off, WDT 使能 ,

5V LXTLP=0

─

10

20

μA

─

40

60

μA

3V 无负载 , fSYS=LXT,

ADC off, WDT 使能 ,

5V LXTLP=1

─

10

20

μA

─

40

60

μA

3V 无负载 , fSYS=LXT,

ADC off, WDT 使能 ,

5V LXTLP=0

─

10

20

μA

─

40

60

μA

─

─

─

─

10

30

10

40

20

50

20

60

μA

μA

μA

μA

3V

5V

3.3V

5V

5V

IDD2

IDD3

IDD4

工作电流,正常模式

fSYS=fH (HIRC)

工作电流,低速模式

fSYS=fL=LXT, fSUB=LXT

工作电流,低速模式

fSYS=fL=LXT, fSUB=LIRC

IDD5

工作电流,低速模式

fSYS=fL=LIRC, fSUB=LIRC

IDD6

工作电流,低速模式

fSYS=fL=LIRC, fSUB=LXT

Rev. 1.50

3V

5V

3V

5V

3.3V

5V

3V

5V

3V

5V

无负载 , fH=12MHz,

ADC off, WDT 使能

无负载 , fH=16MHz,

ADC off, WDT 使能

无负载 , fH=20MHz,

ADC off, WDT 使能

无负载 , fH=8MHz,

ADC off, WDT 使能

无负载 , fH=12MHz,

ADC off, WDT 使能

无负载 , fH=16MHz,

ADC off, WDT 使能

无负载 , fSYS=LIRC,

ADC off, WDT 使能

无负载 , fSYS=LIRC,

ADC off, WDT 使能

11

最大 单位

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

符号

IDD7

IDD8

参数

工作电流,正常模式

fH=8MHz (HIRC)

工作电流,正常模式

fH=12MHz (HXT)

IIDLE01

IDLE0 模式静态电流

(LXT on)

IIDLE02

IDLE0 模式静态电流

(LIRC on)

IIDLE03

IDLE0 模式静态电流

(LXT & LIRC on)

IIDLE11

IDLE1 模式静态电流

(HXT)

Rev. 1.50

VDD

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

3V

5V

测试条件

条件

无负载 , fSYS=fH/2,

ADC off, WDT 使能

无负载 , fSYS=fH/4,

ADC off, WDT 使能

无负载 , fSYS=fH/8,

ADC off, WDT 使能

无负载 , fSYS=fH/16,

ADC off, WDT 使能

无负载 , fSYS=fH/32,

ADC off, WDT 使能

无负载 , fSYS=fH/64,

ADC off, WDT 使能

无负载 , fSYS=fH/2,

ADC off, WDT 使能

无负载 , fSYS=fH/4,

ADC off, WDT 使能

无负载 , fSYS=fH/8,

ADC off, WDT 使能

无负载 , fSYS=fH/16,

ADC off, WDT 使能

无负载 , fSYS=fH/32,

ADC off, WDT 使能

无负载 , fSYS=fH/64,

ADC off, WDT 使能

无负载 , ADC off,

WDT 使能 , LXTLP=0

无负载 , ADC off,

WDT 使能 , LXTLP=1

无负载 , ADC off,

WDT 使能 , LVR 除能

无负载 , ADC off,

WDT 使能 , LXTLP=0

无负载 , ADC off,

WDT 使能 , LXTLP=1

无负载 , ADC off,

WDT 使能 , fSYS=8MHz on

12

最小

典型

最大 单位

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

─

1.7

2.6

1.6

2.4

1.5

2.2

1.4

2.0

1.3

1.8

1.2

1.6

0.9

2.5

0.7

2.0

0.6

1.6

0.5

1.5

0.49

1.45

0.47

1.4

5

16

5

16

1.3

2.2

6

18

6

18

0.5

1.0

2.4

4.4

2.4

4.0

2.2

3.6

2.0

3.2

1.8

2.8

1.6

2.4

1.5

3.75

1.0

3.0

0.9

2.4

0.75

2.25

0.74

2.18

0.71

2.1

10

32

10

32

3.0

5.0

12

36

12

36

1.0

2.0

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

μA

μA

μA

μA

μA

μA

μA

μA

μA

μA

mA

mA

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

符号

IIDLE12

参数

IDLE1 模式静态电流

(HIRC)

VDD

3V

5V

3V

5V

3.3V

5V

3V

5V

3.3V

5V

测试条件

条件

无负载 , ADC off,

WDT 使能 , fSYS=8MHz on

无负载 , ADC off,

WDT 使能 , fSYS=12MHz on

无负载 , ADC off,

WDT 使能 , fSYS=16MHz on

典型

最大 单位

─

─

─

─

─

─

─

─

─

─

0.8

1.0

1.2

1.5

1.6

2.0

0.6

1.2

1.0

2.0

1.6

2.0

2.4

3.0

3.2

4.0

1.2

2.4

2.0

4.0

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

─

2.5

5.0

mA

IIDLE13

IDLE1 模式静态电流

(HXT)

IIDLE14

IDLE1 模式静态电流

(HXT)

IIDLE15

IDLE1 模式静态电流

(HXT)

5V

ISLEEP0

SLEEP0 模式静态电流

(LIRC off)

3V 无负载 , ADC off,

5V WDT 除能 , LVR 除能

─

─

0.1

0.3

1.0

2.0

μA

μA

SLEEP1 模式静态电流

(LXT on)

3V 无负载 , ADC off,

WDT 使能 , LXTLP=1,

5V LVR 除能

─

5

10

μA

ISLEEP1

─

16

32

μA

SLEEP1 模式静态电流

(LXT on)

3V 无负载 , ADC off,

WDT 使能 , LXTLP=0,

5V LVR 除能

─

5

10

μA

─

15

30

μA

ISLEEP3

SLEEP1 模式静态电流

(LIRC on)

3V 无负载 , ADC off,

5V WDT 使能 , LVR 除能

─

─

1.3

2.2

5.0

10

μA

μA

输入 / 输出口或除 PC2 脚

以外的输入引脚低电平输

入电压

5V

─

0

─

1.5

V

VIL1

─

─

0

─

0.2VDD

V

输入 / 输出口或除 PC2 脚

以外的输入引脚低电平输

入电压

5V

─

3.5

─

5.0

V

─

─

0.8VDD

─

VDD

V

VIL2

VIH2

低电平输入电压 (PC2)

高电平输入电压 (PC2)

─

─

IOL

输入 / 输出口灌电流

IOH

输入 / 输出口源电流

RPH

输入 / 输出口上拉电阻

─

─

3V

5V

3V

5V

3V

5V

0

─ 0.4VDD

0.9VDD ─

VDD

8

16

─

16

32

─

-3.75 -7.5

─

-7.5

-15

─

20

60

100

10

30

50

ISLEEP2

VIH1

Rev. 1.50

无负载 , ADC off,

WDT 使能 , fSYS=12MHz on

最小

无负载 , ADC off,

WDT 使能 , fSYS=16MHz on

无负载 , ADC off,

WDT 使能 , fSYS=20MHz on

VOL=0.1VDD

VOL=0.1VDD

VOH=0.9VDD

VOH=0.9VDD

─

─

13

V

V

mA

mA

mA

mA

kΩ

kΩ

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

交流电气特性

Ta=25˚C

符号

参数

fCPU

工作时钟

fSYS

系统时钟 (HXT)

fHIRC

系统时钟 (HIRC)

fLIRC

系统时钟 (LIRC)

tINT

tTCK

中断脉宽

TCKn 输入脉宽

系统复位延迟时间

( 上电复位,LVR 复位,

LVR 软件复位 (LVRC),

WDT 软件复位 (WDTC) )

系统复位延迟时间

(WDT 正常复位 )

tRSTD

tSST

tEERD

tEEWR

系统启动时间

( 由 HALT 模式唤醒,

fSYS 在 HALT 模式关闭 )

系统启动时间

( 由 HALT 模式唤醒,

fSYS 在 HALT 模式开启 )

EEPROM 读周期

EEPROM 写周期

测试条件

VDD

条件

2.2V~5.5V

2.7V~5.5V

─

3.3V~5.5V

4.5V~5.5V

2.2V~5.5V

2.7V~5.5V

─

3.3V~5.5V

4.5V~5.5V

3V/5V

Ta=25˚C

3V/5V

Ta=25˚C

3.3V/5V Ta=25˚C

3V/5V

Ta=0˚C~70˚C

3V/5V

Ta=0˚C~70˚C

3.3V/5V Ta=0˚C~70˚C

2.2V~5.5V Ta=0˚C~70˚C

2.2V~5.5V Ta=0˚C~70˚C

3.3V~5.5V Ta=0˚C~70˚C

2.2V~5.5V Ta=-40˚C~85˚C

2.2V~5.5V Ta=-40˚C~85˚C

3.3V~5.5V Ta=-40˚C~85˚C

5V

Ta=25˚C

2.2V~5.5V Ta=-40˚C~85˚C

─

─

─

─

最小 典型

最大 单位

DC

DC

DC

DC

0.4

0.4

0.4

0.4

-2%

-2%

-2%

-5%

-5%

-5%

-7%

-7%

-7%

-10%

-10%

-10%

-10%

-30%

10

0.3

─

─

─

─

─

─

─

─

8

12

16

8

12

16

8

12

16

8

12

16

32

32

─

─

8

12

16

20

8

12

16

20

+2%

+2%

+2%

+5%

+5%

+5%

+7%

+7%

+7%

+10%

+10%

+10%

+10%

+60%

─

─

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

kHz

kHz

μs

μs

─

─

25

50

100

ms

─

─

8.3

16.7

33.3

ms

─

─

─

fSYS=HXT

fSYS=HIRC

fSYS=LIRC

512

16

2

─

─

─

─

─

─

tSYS

tSYS

tSYS

─

─

2

─

─

tSYS

─

─

─

─

─

─

2

2

4

4

tSYS

ms

注:1. tSYS=1/fSYS。

2. 为保证 HIRC 振荡器频率的精确度,建议在 VDD 和 VSS 之间连接一个 0.1μF 的电容,并尽可能靠

近单片机。

Rev. 1.50

14

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

ADC 电气特性

Ta=25˚C

符号

AVDD

VADI

VREF

VBG

参数

A/D 转换器工作电压

A/D 转换器输入电压

A/D 输入参考电压

带隙参考缓冲电压

DNL1 A/D 非线性微分误差

测试条件

条件

—

—

—

—

VDD

—

—

—

—

3V VREF=AVDD=VDD

5V tADCK=0.5μs,Ta=25˚C

最小 典型 最大 单位

2.7 —

5.5

V

0

— VREF mA

2

— AVDD V

-3% 1.25 +3% V

-3

—

+3

LSB

DNL2 A/D 非线性微分误差

3V VREF=AVDD=VDD,

5V tADCK=0.5μs,Ta=-40˚C~85˚C

-6

—

+6

LSB

INL1 A/D 非线性积分误差

3V VREF=AVDD=VDD

5V tADCK=0.5μs,Ta=25˚C

-4

—

+4

LSB

INL2 A/D 非线性积分误差

3V VREF=AVDD=VDD

5V tADCK=0.5μs,Ta=-40˚C~85˚C

-8

—

+8

LSB

3V

无负载 (tADCK=0.5μs)

5V

—

—

—

—

—

—

—

0.5

0.9

1.2

200

—

1.35

1.8

300

10

mA

mA

μA

μs

— 12-bit ADC

—

16

—

tADCK

—

2

200

4

—

—

—

—

—

tADCK

μs

μs

IADC

打开 A/D 增加的功耗

IBG

tADCK

使用 VBG 增加的功耗

A/D 转换器时钟周期

A/D 转换时间

( 包括采样和保持时间 )

A/D 转换器采样时间

A/D 转换器 On-to-Start 时间

VBG 开启到稳定的时间

tADC

tADS

tON2ST

tBGS

—

—

—

—

—

—

注:A/D 转换时间(tADC)=n×(ADC 位 )+ 4×( 采样时间),每一位的转换需要一个 ADC 时钟周期(tADCK)。

Rev. 1.50

15

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

LVD&LVR 电气特性

Ta=25˚C

符号

VLVR1

VLVR2

VLVR3

VLVR4

VLVD1

VLVD2

VLVD3

VLVD4

VLVD5

VLVD6

VLVD7

VLVD8

ILVR

ILVD

tLVR

tLVD

tLVDS

tSRESET

测试条件

条件

VDD

LVR 使能,VLVR=2.10V

LVR 使能,VLVR=2.55V

低电压复位电压

—

LVR 使能,VLVR=3.15V

LVR 使能,VLVR=3.80V

LVDEN=1,VLVD=2.0V

LVDEN=1,VLVD=2.2V

LVDEN=1,VLVD=2.4V

LVDEN=1,VLVD=2.7V

低电压检测电压

—

LVDEN=1,VLVD=3.0V

LVDEN=1,VLVD=3.3V

LVDEN=1,VLVD=3.6V

LVDEN=1,VLVD=4.0V

3V

使用 LVR 增加的功耗

LVR 除能 → LVR 使能

5V

3V

LVD 除能 → LVD 使能 (LVR 除能 )

5V

使用 LVD 增加的功耗

3V

LVD 除能 → LVD 使能 (LVR 使能 )

5V

低电压复位脉宽

—

—

低电压中断脉宽

—

—

— LVR 使能,LVD off→on

LVDO 稳定时间

— LVR 除能,LVD off→on

软件复位脉宽

—

—

Rev. 1.50

参数

16

最小 典型 最大 单位

-5%

-5%

—

—

—

—

—

—

120

20

15

15

45

2.10

2.55

+5%

3.15

3.80

2.00

2.20

2.40

2.70

+5%

3.00

3.30

3.60

4.00

30

45

60

90

40

60

75 115

30

45

60

90

240 480

45

90

—

—

—

—

90 120

V

V

V

V

V

V

V

V

V

V

V

V

μA

μA

μA

μA

μA

μA

μs

μs

μs

μs

μs

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

比较器电气特性

Ta=25˚C

符号

参数

VCMP

比较器工作电压

ICMP

比较器工作电流

VCMPOS

VHYS

VCM

AOL

tPD

比较器输入失调电压

迟滞宽度

比较器共模电压范围

比较器开环增益

比较器响应时间

VDD

─

3V

5V

─

─

─

─

─

测试条件

条件

─

─

─

─

─

─

─

100mV 偏置 ( 注 )

最小

典型

最大

单位

2.2

─

─

-10

20

VSS

60

─

─

37

130

─

40

─

80

370

5.5

56

200

+10

60

VDD-1.4V

─

560

V

μA

μA

mV

mV

V

dB

ns

注:测量方式为:当一只输入脚的输入电压为 VCM=(VDD-1.4)/2 时,另一只输入脚的输入电压从 VSS 到

(VCM+100mV) 或从 VDD 到 (VCM-100mV) 转变。

上电复位特性

Ta=25˚C

符号

VPOR

参数

上电复位电压

RRVDD 上电复位电压速率

tPOR

VDD 保持为 VPOR 的最小时间

Rev. 1.50

VDD

测试条件

条件

最小

典型

最大

单位

—

—

—

—

100

mV

—

—

0.035

—

—

V/ms

—

—

1

—

—

ms

17

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

带隙参考电压 (VBG) 特性曲线

系统结构

内部系统结构是盛群单片机具有良好性能的主要因素。由于采用 RISC 结构,

此单片机具有高运算速度和高性能的特点。通过流水线的方式,指令的取得和

执行同时进行,此举使得除了跳转和调用指令外,其它指令都能在一个指令周

期内完成。8 位 ALU 参与指令集中所有的运算,它可完成算术运算、逻辑运算、

移位、递增、递减和分支等功能,而内部的数据路径则是以通过累加器和 ALU

的方式加以简化。有些寄存器在数据存储器中被实现,且可以直接或间接寻址。

简单的寄存器寻址方式和结构特性,确保了在提供具有最大可靠度和灵活性的

I/O 和 A/D 控制系统时,仅需要少数的外部器件。使得这些单片机适用于低成

本和大批量的控制应用。

时序和流水线结构

主系统时钟由 HXT,LXT,HIRC 或 LIRC 振荡器提供,它被细分为 T1~T4 四

个内部产生的非重叠时序。在 T1 时间,程序计数器自动加一并抓取一条新的

指令。剩下的时间 T2~T4 完成译码和执行功能,因此,一个 T1~T4 时钟周期构

成一个指令周期。虽然指令的抓取和执行发生在连续的指令周期,但单片机流

水线结构会保证指令在一个指令周期内被有效执行。除非程序计数器的内容被

改变,如子程序的调用或跳转,在这种情况下指令将需要多一个指令周期的时

间去执行。

Rev. 1.50

18

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

系统时序和流水线

如果指令牵涉到分支,例如跳转或调用等指令,则需要两个指令周期才能完成

指令执行。需要一个额外周期的原因是程序先用一个周期取出实际要跳转或调

用的地址,再用另一个周期去实际执行分支动作,因此用户需要特别考虑额外

周期的问题,尤其是在执行时间要求较严格的时候。

指令捕捉

程序计数器

在程序执行期间,程序计数器用来指向下一个要执行的指令地址。除了“JMP”

和“CALL”指令需要跳转到一个非连续的程序存储器地址之外,它会在每条

指令执行完成以后自动加一。只有较低的 8 位,即所谓的程序计数器低字节寄

存器 PCL,可以被用户直接读写。

当执行的指令要求跳转到不连续的地址时,如跳转指令、子程序调用、中断或

复位等,单片机通过加载所需要的地址到程序寄存器来控制程序,对于条件跳

转指令,一旦条件符合,在当前指令执行时取得的下一条指令将会被舍弃,而

由一个空指令周期来取代。

程序计数器

程序计数器高字节

PCL 寄存器

PCL7~PCL0

PC11~PC8

程序计数器的低字节,即程序计数器的低字节寄存器 PCL,可以通过程序控制,

且它是可以读取和写入的寄存器。通过直接写入数据到这个寄存器,一个程序

短跳转可直接执行,然而只有低字节的操作是有效的,跳转被限制在存储器的

当前页中,即 256 个存储器地址范围内,当这样一个程序跳转要执行时,会插

入一个空指令周期。程序计数器的低字节可由程序直接进行读取,PCL 的使用

可能引起程序跳转,因此需要额外的指令周期。

Rev. 1.50

19

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

堆栈

堆栈是一个特殊的存储空间,用来存储程序计数器中的内容。此单片机有 8 层

堆栈,堆栈既不是数据部分也不是程序空间部分,而且它既不是可读取也不是

可写入的。当前层由堆栈指针 (SP) 加以指示,同样也是不可读写的。在子程序

调用或中断响应服务时,程序计数器的内容被压入到堆栈中。当子程序或中断

响应结束时,返回指令 (RET 或 RETI) 使程序计数器从堆栈中重新得到它以前

的值。当一个芯片复位后,堆栈指针将指向堆栈顶部。

如果堆栈已满,且有非屏蔽的中断发生,中断请求标志会被置位,但中断响应

将被禁止。当堆栈指针减少 ( 执行 RET 或 RETI),中断将被响应。这个特性提

供程序设计者简单的方法来预防堆栈溢出。然而即使堆栈已满,CALL 指令仍

然可以被执行,而造成堆栈溢出。使用时应避免堆栈溢出的情况发生,因为这

可能导致不可预期的程序分支指令执行错误。若堆栈溢出,则首个存入堆栈的

程序计数器数据将会丢失。

算术逻辑单元 – ALU

算术逻辑单元是单片机中很重要的部分,执行指令集中的算术和逻辑运算。

ALU 连接到单片机的数据总线,在接收相关的指令码后执行需要的算术与逻辑

操作,并将结果存储在指定的寄存器,当 ALU 计算或操作时,可能导致进位、

借位或其它状态的改变,而相关的状态寄存器会因此更新内容以显示这些改变,

ALU 所提供的功能如下:

● 算术运算:ADD,ADDM,ADC,ADCM,SUB,SUBM,SBC,SBCM,DAA

● 逻辑运算:AND,OR,XOR,ANDM,ORM,XORM,CPL,CPLA

● 移位运算:RRA,RR,RRCA,RRC,RLA,RL,RLCA,RLC

● 递增和递减:INCA,INC,DECA,DEC

● 分支判断:JMP,SZ,SZA,SNZ,SIZ,SDZ,SIZA,SDZA,CALL,RET,

RETI

Rev. 1.50

20

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

Flash 程序存储器

程序存储器用来存放用户代码即储存程序。程序存储器为 FLASH 类型意味着

可以多次重复编程,方便用户使用同一芯片进行程序的修改。使用适当的单片

机编程工具,此单片机提供用户灵活便利的调试方法和项目开发规划及更新。

结构

程序存储器的容量为 4K×16 位,程序存储器用程序计数器来寻址,其中也包含

数据、表格和中断入口。数据表格可以设定在程序存储器的任何地址,由表格

指针来寻址。

程序存储器结构

特殊向量

程序存储器内部某些地址保留用做诸如复位和中断入口等特殊用途。地址 000H

是芯片复位后的程序起始地址。在芯片复位之后,程序将跳到这个地址并开始

执行。

查表

程序存储器中的任何地址都可以定义成一个表格,以便储存固定的数据。使用

表格时,表格指针必须先行设定,其方式是将表格的地址放在表格指针寄存器

TBLP 和 TBHP 中。这些寄存器定义表格总的地址。

在设定完表格指针后,表格数据可以使用“TABRD [m]”或“TABRDL [m]”

指令从程序存储器页来查表读取。当这些指令执行时,程序存储器中表格数据

低字节,将被传送到使用者所指定的数据存储器 [m],程序存储器中表格数据

的高字节,则被传送到 TBLH 特殊寄存器,而高字节中未使用的位将被读取为

“0”。

下图是查表中寻址 / 数据流程:

Rev. 1.50

21

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

查表范例

以下范例说明在该单片机中,表格指针和表格数据如何被定义和执行。这个例

子使用的表格数据用 ORG 伪指令储存在存储器的最后一页。ORG 指令“F00H”

指向的地址是 4K 程序存储器中最后一页的起始地址。表格指针的初始值设为

“06H”,这可保证从数据表格读取的第一笔数据位于程序存储器地址 F06H,

即最后一页起始地址后的第六个地址。值得注意的是,假如“TABRD [m]”指

令被使用,则表格指针指向 TBHP+TBLP 位址。在这个例子中,表格数据的

高字节等于零,而当“TABRD [m]”指令被执行时,此值将会自动的被传送到

TBLH 寄存器。

TBLH 寄存器为只读寄存器,不能重新储存,若主程序和中断服务程序都使用

表格读取指令,应该注意它的保护。使用表格读取指令,中断服务程序可能会

改变 TBLH 的值,若随后在主程序中再次使用这个值,则会发生错误,因此建

议避免同时使用表格读取指令。然而在某些情况下,如果同时使用表格读取指

令是不可避免的,则在执行任何主程序的表格读取指令前,中断应该先除能,

另外要注意的是所有与表格相关的指令,都需要两个指令周期去完成操作。

表格读取程序范例

tempreg1

db ? ; temporary register #1

tempreg2

db ? ; temporary register #2

:

:

mov a,06h

; initialize low table pointer – note that this address

; is referenced

mov tblp,a

; to the last page or present page

mov a,0Fh

; initialise high table pointer

mov tbhp,a

:

:

tabrd tempreg1

; transfers value in table referenced by table pointer

; to tempreg1 data at prog. memory address F06H

; transferred to tempreg1 and TBLH

dec tblp

; reduce value of table pointer by one

tabrd tempreg2

; transfers value in table referenced by table pointer

; to tempreg2

; data at prog. memory address F05H transferred to

; tempreg2 and TBLH

; in this example the data "1AH" is transferred

; to tempreg1 and data "0FH" to register tempreg2

; the value “00H” will be transferred to the high byte

; register TBLH

:

:

org F00h

; sets initial address of last page

dc 00Ah, 00Bh, 00Ch, 00Dh, 00Eh, 00Fh, 01Ah, 01Bh

:

在线烧录

Flash 型程序存储器提供用户便利地对同一芯片进行程序的更新和修改。另外,

HOLTEK 单片机提供 4 线接口的在线烧录方式。用户可将进行过烧录或未经过

烧录的单片机芯片连同电路板一起制成,最后阶段进行程序的更新和程序的烧

录,在无需去除或重新插入芯片的情况下方便地保持程序为最新版。

Holtek Flash MCU 与烧录器引脚对应表如下:

Rev. 1.50

22

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

Holtek 烧录器引脚名称 MCU 在线烧录引脚名称

ICPDA

PA0

ICPCK

PA2

VDD

VDD

VSS

VSS

功能

串行数据 / 地址烧录

时钟烧录

电源

地

芯片内部程序存储器和 EEPROM 存储器都可以通过 4 线的接口在线进行烧录。

其中一条用于数据串行下载或上传,一条用于串行时钟输入输出,两条用于提

供电源。芯片在线烧写的详细使用说明超出此文档的描述范围,将由专门的参

考文献提供。

在烧录过程中,PA0 和 PA2 脚进行数据和时钟烧录,用户必须确保这两个引脚

没有连接到其它输出脚。

注:* 可能为电阻或电容。若为电阻则其值必须大于 1kΩ,若为电容则其必须小于 1nF。

片上调试

EV 芯 片 用 于 单 片 机 仿 真。 此 EV 芯 片 提 供 片 上 调 试 功 能(OCDS—On-chip

Debug Support)用于开发过程中的单片机调试。除了片上调试功能方面,EV

IC 和实际 MCU 在功能上几乎是兼容的。用户可将 OCDSDA 和 OCDSCK 引脚

连接至 Holtek HT-IDE 开发工具,从而实现 EV IC 对实际 IC 的仿真。OCDSDA

引脚为 OCDS 数据 / 地址输入 / 输出脚,OCDSCK 引脚为 OCDS 时钟输入脚。

当用户用 EV IC 进行调试时,实际单片机 OCDSDA 和 OCDSCK 引脚上的其它

共用功能无效。关于 OCDS 功能的详细描述,请参考“Holtek e-Link for 8-bit

MCU OCDS User’s Guide”文件。

Holtek e-Link 引脚名称 EV IC 引脚名称

OCDSDA

OCDSDA

OCDSCK

OCDSCK

VDD

VDD

VSS

VSS

Rev. 1.50

23

功能

片上调试串行数据 / 地址输入 / 输出

片上调试时钟输入

电源

地

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

数据存储器

数据存储器是内容可更改的 8 位 RAM 内部存储器,用来储存临时数据。RAM

数据存储器的容量为 192×8 位

结构

数据存储器分为两个区,第一部分是特殊功能数据存储器。这些寄存器有固定

的地址且与单片机的正确操作密切相关。大多特殊功能寄存器都可在程序控制

下直接读取和写入,但有些被加以保护而不对用户开放。第二部分数据存储器

是做一般用途使用,都可在程序控制下进行读取和写入。

总的数据存储器被分为两个区。大部分特殊功能数据寄存器均可在所有 Bank

被访问,处于“40H”地址的 EEC 寄存器却只能在 Bank 1 中被访问到。切换不

同区域可通过设置区域指针(BP)实现。所有单片机的数据存储器的起始地址

都是“00H”。

容量

Banks

0:A0H~FFH

1:A0H~FFH

192×8

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � � � �� ������� � � � ��

��

�

� � �

��

�

� � �

� �

� � �

� �

�

�

�

�

� � �

� � � �

� � � �

� � �

�� � �

�� � �

�� � �

�� � �

� � ��

� � ��

� � ��

� �

� � �

� � � �

� � � �

� �

� � �

� � �

� �

�

�

�

� � �

� � �

� �

� �

�

� � �

�

� � �

�

� � �

� � � � �� ������� � � � ��

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� � �

� �

� � �

� � � �

� � � �

� � � �

� � �

� � � �

� � �

� � � �

� �

�

� � � �

� � � �

� � �

� � � �

� � �

� � � �

� �

�

� � � �

� � � �

� � �

� � � �

� � �

� � � �

� �

�

� �

� �

� � �

� �

� � � � �

� � �

� � � �

� �

� � �

� � � �

特殊功能数据存储器

Rev. 1.50

24

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

特殊功能寄存器

大部分特殊功能寄存器的细节将在相关功能章节描述,但有几个寄存器需在此

章节单独描述。

间接寻址寄存器 – IAR0,IAR1

间接寻址寄存器 IAR0 和 IAR1 的地址虽位于数据存储区,但其并没有实际的物

理地址。间接寻址的方法准许使用间接寻址指针做数据操作,以取代定义实际

存储器地址的直接存储器寻址方法。在间接寻址寄存器(IAR0 和 IAR1)上的

任何动作,将对间接寻址指针 (MP0 和 MP1) 所指定的存储器地址产生对应的读

/ 写操作。它们总是成对出现,可以共同访问数据存储器。因为这些间接寻址寄

存器不是实际存在的,直接读取将返回“00H”的结果,而直接写入此寄存器

则不做任何操作。

间接寻址指针 – MP0,MP1

该单片机提供两个间接寻址指针,即 MP0 和 MP1。由于这些指针在数据存储

器中能像普通的寄存器一般被操作,因此提供了一个寻址和数据追踪的有效方

法。当对间接寻址寄存器进行任何操作时,单片机指向的实际地址是由间接寻

址指针所指定的地址。MP0,IAR0 用于访问 Bank 0,而 MP1 和 IAR1 可通过

BP 寄存器访问所有的 Bank。仅 Bank 0 可使用直接寻址,其它所有 Bank 仅可

使用 MP1 和 IAR1 进行间接寻址。

以下例子说明如何清除一个具有 4 RAM 地址的区块,它们已事先定义成地址

adres1 到 adres4。

间接寻址程序举例

data .section ´data´

adres1

db ?

adres2

db ?

adres3

db ?

adres4

db ?

block

db ?

code .section at 0 ´code´

org 00h

start:

mov a,04h

mov block,a

mov a,offset adres1

mov mp0,a

loop:

clr IAR0

inc mp0

sdz block

jmp loop

continue:

; setup size of block

; Accumulator loaded with first RAM address

; setup memory pointer with first RAM address

; clear the data at address defined by mp0

; increment memory pointer

; check if last memory location has been cleared

在上面的例子中有一点值得注意,即并没有确定 RAM 地址。

Rev. 1.50

25

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

存储区指针 – BP

数据存储器被分为两个部分,即 Bank 0 和 Bank 1。可以通过设置存储区指针

(Bank Pointer)值来访问不同的数据存储区。BP 指针的 bit 0 用于选择数据存

储区的 Bank 0 或 Bank 1。。

复位后,数据存储器会初始化到 Bank 0,但是在空闲 / 休眠模式下的 WDT 溢

出复位,不会改变通用数据存储器的存储区号。应该注意的是特殊功能数据存

储器不受存储区的影响,也就是说,不论是在哪一个存储区,都能对特殊功能

寄存器进行读写操作。数据存储器的直接寻址总是访问 Bank 0,不影响存储区

指针的值。要访问 Bank 1,则必须要使用间接寻址方式。

BP 寄存器

Bit

Name

R/W

POR

7

—

—

—

6

—

—

—

5

—

—

—

4

—

—

—

Bit 7~1

未使用,读为“0”

Bit 0

DMBP0:数据存储区选择位

0:Bank 0

1:Bank 1

3

—

—

—

2

—

—

—

1

—

—

—

0

DMBP0

R/W

0

累加器 – ACC

对任何单片机来说,累加器是相当重要的,且与 ALU 所完成的运算有密切关

系,所有 ALU 得到的运算结果都会暂时存在 ACC 累加器里。若没有累加器,

ALU 必须在每次进行如加法、减法和移位的运算时,将结果写入到数据存储器,

这样会造成程序编写和时间的负担。另外数据传送也常常牵涉到累加器的临时

储存功能,例如在使用者定义的一个寄存器和另一个寄存器之间传送数据时,

由于两寄存器之间不能直接传送数据,因此必须通过累加器来传送数据。

程序计数器低字节寄存器 – PCL

为了提供额外的程序控制功能,程序计数器低字节设置在数据存储器的特殊功

能区域内,程序员可对此寄存器进行操作,很容易的直接跳转到其它程序地址。

直接给 PCL 寄存器赋值将导致程序直接跳转到程序存储器的某一地址,然而由

于寄存器只有 8 位长度,因此只允许在本页的程序存储器范围内进行跳转,而

当使用这种运算时,要注意会插入一个空指令周期。

表格寄存器 – TBLP,TBHP,TBLH

这三个特殊功能寄存器对存储在程序存储器中的表格进行操作。TBLP 和 TBHP

为表格指针,指向表格数据存储的地址。它们的值必须在任何表格读取指令执

行前加以设定,由于它们的值可以被如“INC”或“DEC”的指令所改变,这

就提供了一种简单的方法对表格数据进行读取。表格读取数据指令执行之后,

表格数据高字节存储在 TBLH 中。其中要注意的是,表格数据低字节会被传送

到使用者指定的地址。

Rev. 1.50

26

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

状态寄存器 – STATUS

这 8 位的状态寄存器由零标志位 (Z)、进位标志位 (C)、辅助进位标志位 (AC)、

溢出标志位 (OV)、暂停标志位 (PDF) 和看门狗定时器溢出标志位 (TO) 组成。

这些算术 / 逻辑操作和系统运行标志位是用来记录单片机的运行状态。

除了 PDF 和 TO 标志外,状态寄存器中的位像其它大部分寄存器一样可以被改

变。任何数据写入到状态寄存器将不会改变 TO 或 PDF 标志位。另外,执行不

同的指令后,与状态寄存器有关的运算可能会得到不同的结果。TO 标志位只会

受系统上电、看门狗溢出或执行“CLR WDT”或“HALT”指令影响。PDF 标

志位只会受执行“HALT”或“CLR WDT”指令或系统上电影响。

Z、OV、AC 和 C 标志位通常反映最近运算的状态。

● C:当加法运算的结果产生进位,或减法运算的结果没有产生借位时,则 C

被置位,否则 C 被清零,同时 C 也会被带进位的移位指令所影响。

● AC:当低半字节加法运算的结果产生进位,或高半字节减法运算的结果没有

产生借位时,AC 被置位,否则 AC 被清零。

● Z: 当算术或逻辑运算结果是零时,Z 被置位,否则 Z 被清零。

● OV:当运算结果高两位的进位状态异或结果为 1 时,OV 被置位,否则 OV

被清零。

● PDF:系统上电或执行“CLR WDT”指令会清零 PDF,而执行“HALT”指

令则会置位 PDF。

● TO:系统上电或执行“CLR WDT”或“HALT”指令会清零 TO,而当 WDT

溢出则会置位 TO。

另外,当进入一个中断程序或执行子程序调用时,状态寄存器不会自动压入到

堆栈保存。假如状态寄存器的内容是重要的且子程序可能改变状态寄存器的话,

则需谨慎的去做正确的储存。

Rev. 1.50

27

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

STATUS 寄存器

Bit

Name

R/W

POR

7

—

—

—

6

—

—

—

5

TO

R

0

4

PDF

R

0

3

OV

R/W

×

2

Z

R/W

×

1

AC

R/W

×

0

C

R/W

×

“×”为未知

Rev. 1.50

Bit 7~6

未使用,读为“0”

Bit 5

TO:看门狗溢出标志位

0:系统上电或执行“CLR WDT”或“HALT”指令后

1:看门狗溢出发生

Bit 4

PDF:暂停标志位

0:系统上电或执行“CLR WDT”指令后

1:执行“HALT”指令

Bit 3

OV:溢出标志位

0:无溢出

1:运算结果高两位的进位状态异或结果为 1

Bit 2

Z:零标志位

0:算术或逻辑运算结果不为 0

1:算术或逻辑运算结果为 0

Bit 1

AC:辅助进位标志位

0:无辅助进位

1:在加法运算中低四位产生了向高四位进位,或减法运算中低四位不发生从

高四位借位

Bit 0

C:进位标志位

0:无进位

1:如果在加法运算中结果产生了进位,或在减法运算中结果不发生借位

C 也受循环移位指令的影响。

28

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

EEPROM 数据寄存器

此 单 片 机 的 一 个 特 性 是 内 建 EEPROM 数 据 存 储 器。“Electrically Erasable

Programmable Read Only Memory”为电可擦可编程只读存储器,由于其非易失

的存储结构,即使在电源掉电的情况下存储器内的数据仍然保存完好。这种存

储区扩展了 ROM 空间,对设计者来说增加了许多新的应用机会。EEPROM 可

以用来存储产品编号、校准值、用户特定数据、系统配置参数或其它产品信息

等。EEPROM 的数据读取和写入过程也会变的更简单。

EEPROM 数据寄存器结构

EEPROM 数据寄存器容量为 64×8。由于映射方式与程序存储器和数据存储器

不同,因此不能像其它类型的存储器一样寻址。使用 Bank 0 中的一个地址寄存

器和一个数据寄存器以及 Bank 1 中的一个控制寄存器,可以实现对 EEPROM

的单字节读写操作。

容量

64×8

地址

00H~3FH

EEPROM 寄存器

有三个寄存器控制内部 EEPROM 数据存储器总的操作。地址寄存器 EEA、数

据寄存器 EED 及控制寄存器 EEC。EEA 和 EED 位于 Bank 0 中,它们能像其它

特殊功能寄存器一样直接被访问。EEC 位于 Bank 1 中,不能被直接访问,仅能

通过 MP1 和 IAR1 进行间接读取或写入。由于 EEC 控制寄存器位于 Bank 1 中

的“40H”,在 EEC 寄存器上的任何操作被执行前,MP1 必须先设为“40H”,

BP 被设为“01H”。

寄存器

名称

EEA

EED

EEC

位

7

—

D7

—

6

—

D6

—

5

D5

D5

—

4

D4

D4

—

3

D3

D3

WREN

2

D2

D2

WR

1

D1

D1

RDEN

0

D0

D0

RD

2

D2

R/W

0

1

D1

R/W

0

0

D0

R/W

0

EEPROM 寄存器列表

EEA 寄存器

Bit

Name

R/W

POR

Rev. 1.50

7

—

—

—

6

—

—

—

5

D5

R/W

0

Bit 7~6

未定义,读为“0”

Bit 5~0

数据 EEPROM 地址

数据 EEPROM 地址 Bit 5~Bit 0

29

4

D4

R/W

0

3

D3

R/W

0

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

EED 寄存器

Bit

Name

R/W

POR

Bit 7~0

7

D7

R/W

0

6

D6

R/W

0

5

D5

R/W

0

4

D4

R/W

0

3

D3

R/W

0

2

D2

R/W

0

1

D1

R/W

0

0

D0

R/W

0

4

—

—

—

3

WREN

R/W

0

2

WR

R/W

0

1

RDEN

R/W

0

0

RD

R/W

0

EEPROM 数据

EEPROM 数据 Bit 7~Bit 0

EEC 寄存器

Bit

Name

R/W

POR

Rev. 1.50

7

—

—

—

6

—

—

—

5

—

—

—

Bit 7~4

未定义,读为“0”

Bit 3

WREN:数据 EEPROM 写使能位

0:除能

1:使能

此位为数据 EEPROM 写使能位,向数据 EEPROM 写操作之前需将此位置高。

将此位清零时,则禁止向数据 EEPROM 写操作。

Bit 2

WR:EEPROM 写控制位

0:写周期结束

1:写周期有效

此位为数据 EEPROM 写控制位,由应用程序将此位置高将激活写周期。写周期

结束后,硬件自动将此位清零。当 WREN 未先置高时,此位置高无效。

Bit 1

RDEN:数据 EEPROM 读使能位

0:除能

1:使能

此位为数据 EEPROM 读使能位,向数据 EEPROM 读操作之前需将此位置高。

将此位清零时,则禁止向数据 EEPROM 读操作。

Bit 0

RD:EEPROM 读控制位

0:读周期结束

1:读周期有效

此位为数据 EEPROM 读控制位,由应用程序将此位置高将激活读周期。读周期

结束后,硬件自动将此位清零。当 RDEN 未首先置高时,此位置高无效。

注:在同一条指令中 WREN、WR、RDEN 和 RD 不能同时置为“1”。WR 和

RD 不能同时置为“1”。

30

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

从 EEPROM 中读取数据

从 EEPROM 中读取数据,EEC 寄存器中的读使能位 RDEN 先置为高以使能读

功能,EEPROM 中读取数据的地址放入 EEA 寄存器中。若 EEC 寄存器中的

RD 位被置高,一个读周期将开始。若 RD 位已置为高而 RDEN 位还未被设置

则不能开始读操作。若读周期结束,RD 位将自动清除为“0”,数据可以从

EED 寄存器中读取。数据在其它读或写操作执行前将一直保留在 EED 寄存器

中。应用程序将轮询 RD 位以确定数据可以有效地被读取。

写数据到 EEPROM

写数据至 EEPROM,EEPROM 中写入数据的地址要先放入 EEA 寄存器中。写

入的数据要存入 EED 寄存器中。写数据至 EEPROM,EEC 寄存器中的写使能

位 WREN 先置为高以使能写功能。之后将 WR 位置为高,初始化一个写周期。

这两个指令必须连续执行。在执行任何写操作之前,总中断位 EMI 要先清零,

写周期开始后,再将 EMI 置为高。需要注意的是若 WR 位已置为高而 WREN

位还未被设置则不能开始写操作。由于控制 EEPROM 写周期是一个内部时钟,

与单片机的系统时钟异步,所以数据写入 EEPROM 的时间将有所延迟。可通过

轮询 EEC 寄存器中的 WR 位或判断 EEPROM 中断以侦测写周期是否完成。若

写周期完成,WR 位将自动清除为“0”,通知用户数据已写入 EEPROM。因此,

应用程序将轮询 WR 位以确定写周期是否结束。

写保护

防止误写入的写保护有以下几种。单片机上电后控制寄存器中的写使能位将被

清除以杜绝任何写入操作。上电后 BP 将重置为“0”,这意味着数据存储区

Bank 0 被选中。由于 EEPROM 控制寄存器位于 Bank 1 中,这增加了对写操作

的保护措施。在正常程序操作中确保控制寄存器中的写使能位被清除将能防止

不正确的写操作。

EEPROM 中断

EEPROM 写周期结束后将产生 EEPROM 写中断,需先通过设置相关中断寄存

器的 DEE 位使能 EEPROM 中断。由于 EEPROM 中断包含在多功能中断中,相

应的多功能中断使能位需被设置。当 EEPROM 写周期结束,DEF 请求标志位

及其相关多功能中断请求标志位将被置位。若总中断,EEPROM 和多功能中断

使能且堆栈未满的情况下将跳转到相应的多功能中断向量中执行。当中断被响

应,只有多功能中断标志位将自动复位,而 EEPROM 中断标志将通过应用程序

手动复位。更多细节将在中断章节讲述。

编程注意事项

必须注意的是数据不会无意写入 EEPROM。在没有写动作时写使能位被正常清

零可以增强保护功能。BP 指针也可以正常清零以阻止进入 EEPROM 控制寄存

器存在的 Bank 1。尽管没有必要,写一个简单的读回程序以检查新写入的数据

是否正确还是应该考虑的。WREN 位置位后,EEC 寄存器中的 WR 位需立即置

位,否则 EEPROM 写周期将不能被执行。

写数据时,WREN 位置为“1”后,WR 须立即设置为高,以确保正确地执行写

周期。写周期执行前总中断位 EMI 应先清零,写周期开始执行后再将此位重新

使能。

Rev. 1.50

31

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

程序举例

从 EEPROM 中读取数据 — 轮询法

MOV A, EEPROM_ADRES

MOV EEA, A

MOV A, 040H

MOV MP1, A

MOV A, 01H

MOV BP, A

SET IAR1.1

SET IAR1.0

BACK:

SZ IAR1.0

JMP BACK

CLR IAR1

CLR BP

MOV A, EED

MOV READ_DATA, A

; user defined address

; setup memory pointer MP1

; MP1 points to EEC register

; setup Bank Pointer

; set RDEN bit, enable read operations

; start Read Cycle - set RD bit

; check for read cycle end

; disable EEPROM read/write

; move read data to register

写数据到 EEPROM — 轮询法

MOV A, EEPROM_ADRES

MOV EEA, A

MOV A, EEPROM_DATA

MOV EED, A

MOV A, 040H

MOV MP1, A

MOV A, 01H

MOV BP, A

SET IAR1.3

SET IAR1.2

BACK:

SZ IAR1.2

JMP BACK

CLR IAR1

CLR BP

Rev. 1.50

; user defined address

; user defined data

; setup memory pointer MP1

; MP1 points to EEC register

; setup Bank Pointer

; set WREN bit, enable write operations

; start Write Cycle - set WR bit

; check for write cycle end

; disable EEPROM read/write

32

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

振荡器

不同的振荡器选择可以让使用者在不同的应用需求中实现更大范围的功能。振

荡器的灵活性使得在速度和功耗方面可以达到最优化。振荡器选择是通过寄存

器完成的。

振荡器概述

振荡器除了作为系统时钟源,还作为看门狗定时器和时基功能的时钟源。外部

振荡器需要一些外围器件,而集成的两个内部振荡器不需要任何外围器件。它

们提供高速和低速系统振荡器。所有振荡器选择通过配置选项选择。较高频率

的振荡器提供更高的性能,但要求有更高的功率,反之亦然。动态切换快慢系

统时钟的能力使单片机具有灵活而优化的性能 / 功耗比,此特性对功耗敏感的

应用领域尤为重要。

类型

外部晶振

内部高速 RC

外部低速晶振

内部低速 RC

名称

HXT

HIRC

LXT

LIRC

频率

400kHz~20MHz

8, 12, 16MHz

32.768kHz

32kHz

引脚

OSC1/OSC2

—

XT1/XT2

—

振荡器类型

系统时钟配置

此单片机有四个系统振荡器,包括两个高速振荡器和两个低速振荡器。高速

振荡器有外部 RC 振荡器和内部 8MHz, 12MHz, 16MHz RC 振荡器 -HIRC。两

个低速振荡器包括外部 32.768kHz 振荡器和内部 32kHz 振荡器。使用高速或

低速振荡器作为系统时钟的选择是通过设置 SMOD 寄存器中的 HLCLK 位及

CKS2~CKS0 位决定的,系统时钟可动态选择。

高速或低速振荡器的实际时钟源经由配置选项选择。低速或高速系统时钟频率

由 SMOD 寄存器的 HLCLK 位及 CKS2~CKS0 位决定的。请注意,两个振荡器

必须做出选择,即一个高速和一个低速振荡器。系统必须选择一个低速或高速

的振荡器。OSC1/OSC2 和 XT1/XT2 脚用于连接外部晶振和外部低速晶振等元

件。

High Speed

Oscillator

HXT

fH

6-stage Prescaler

HIRC

High Speed Oscillator

Configuration Option

fH/2

fH/4

fH/8

fH/16

fH/32

fH/64

fSYS

fSUB

HLCLK,

CKS2~CKS0 bits

LXT

fSUB

Fast Wake-up from SLEEP

Mode or IDLE Mode Control

(for HXT only)

LIRC

Low Speed Oscillator

Configuration Option

系统时钟配置

Rev. 1.50

33

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

外部晶体 / 陶瓷振荡器 – HXT

外部高频晶体 / 陶瓷振荡器可通过配置选项选择。对于晶体振荡器,只要简单

地将晶体连接至 OSC1 和 OSC2,则会产生振荡所需的相移及反馈,而不需其

它外部器件。为保证某些低频率的晶体振荡和陶瓷谐振器的振荡频率更精准,

建议连接两个小容量电容 C1 和 C2 到 VSS,具体数值与客户选择的晶体 / 陶瓷

晶振有关。

为了确保振荡器的稳定性及减少噪声和串扰的影响,晶体振荡器及其相关的电

阻和电容以及他们之间的连线都应尽可能的接近单片机。

晶体 / 陶瓷振荡器 -- HXT

晶体振荡器 C1 和 C2 值

晶体频率

C1

C2

12MHz

0pF

0pF

8 MHz

0pF

0pF

4 MHz

0pF

0pF

1 MHz

100pF

100pF

注:C1 和 C2 数值仅作参考用

晶体振荡器电容推荐值

内部 RC 振荡器 – HIRC

内部 RC 振荡器是一个集成的系统振荡器,不需其它外部器件。内部 RC 振荡器

具有三种固定的频率: 8MHz,12MHz,16MHz。芯片在制造时进行调整且内

部含有频率补偿电路,使得振荡频率因 VDD、温度以及芯片制成工艺不同的影

响减至最低程度。如果选择了该内部时钟,无需额外的引脚。在电源电压为 3V

或 5V 及温度为 25˚C 的条件下,8MHz, 12MHz, 16MHz 频率的容差为 2%。如果

选择了该内部时钟,无需额外的引脚。 PC0 和 PC1 可以作为通用 I/O 口使用。

Rev. 1.50

34

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

外部 32.768kHz 晶体振荡器 – LXT

外部 32.768kHz 晶体振荡器是一个低频振荡器,经由配置选项选择。时钟频率

固定为 32.768kHz,此时 XT1 和 XT2 间引脚必须连接 32.768kHz 的晶体振荡器。

需要外部电阻和电容连接到 32768Hz 晶振以帮助起振。对于那些要求精确频率

的场合中,可能需要这些元件来对由制程产生的误差提供频率补偿。在系统上

电期间,LXT 振荡器启动需要一定的延时。

当系统进入空闲 / 休眠模式,系统时钟关闭以降低功耗。然而在某些应用,比

如空闲 / 休眠模式下要保持内部定时器功能,必须提供额外的时钟,独立于系

统时钟。

然而,对于一些晶体,为了保证系统频率的启动与精度要求,需要外接两个小

容量电容 C1 和 C2,具体数值与客户选择的晶体规格有关。外部并联的反馈电

阻 RP,是必需的。

一些配置选项决定是否 XT1/XT2 脚是用于 LXT 还是作为普通 I/O 口使用。

● 若 LXT 振荡器未被用于任何时钟源,XT1/XT2 脚能被用作一般 I/O 口使用。

● 若 LXT 振荡器被用于一些时钟源,32.768kHz 晶体应被连接至 XT1/XT2 脚。

为了确保振荡器的稳定性及减少噪声和串扰的影响,晶体振荡器及其相关的电

阻和电容以及他们之间的连线都应尽可能的接近单片机。

外部 LXT 振荡器

LXT 振荡器 C1 和 C2 值

晶体频率

C1

32.768kHz

10pF

C2

10pF

注:1、C1 和 C2 数值仅作参考用

2、RP 的建议值为 5M~10MΩ

32.768kHz 振荡器电容推荐值

Rev. 1.50

35

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

LXT 振荡器低功耗功能

LXT 振荡器可以工作在快速启动模式或低功耗模式,可通过设置 TBC 寄存器

中的 LXTLP 位进行模式选择。

LXTLP 位

0

1

LXT 模式

快速启动

低功耗

系统上电时会清零 LXTLP 位来快速启动 LXT 振荡器。在快速启动模式,LXT

振荡器将起振并快速稳定下来。LXT 振荡器完全起振后,可以通过设置 LXTLP

位为高进入低功耗模式。振荡器可以继续运行,其间耗电将少于快速启动模式。

在功耗敏感的应用领域如电池应用方面,功耗必须限制为一个最小值。为了降

低功耗,建议系统上电 2 秒后,在应用程序中将 LXTLP 位设为“1”。应注意

的是,无论 LXTLP 位是什么值,LXT 振荡器会正常运作,不同的只是在低功

耗模式时启动时间更长。

内部 32kHz 振荡器 – LIRC

内部 32kHz 系统振荡器也是一个低频振荡器,经由配置选项选择。这种单片机

有一个完全集成 RC 振荡器,它在 5V 电压下运行的典型频率值为 32kHz 且无

需外部元件。芯片在制造时进行调整且内部含有频率补偿电路,使得振荡器因

电源电压、温度及芯片制成工艺不同的影响减至最低。因此,内部 32kHz 振荡

器频率在 25˚C 温度 5V 电压下的精度保持在 10% 以内。

辅助振荡器

低速振荡器除了提供一个系统时钟源外,也用来为看门狗定时器,时基,定时

器模块中断提供时钟来源。

Rev. 1.50

36

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

工作模式和系统时钟

现今的应用要求单片机具有较高的性能及尽可能低的功耗,这种矛盾的要求在

便携式电池供电的应用领域尤为明显。高性能所需要的高速时钟将增加功耗,

反之亦然。此单片机提供高、低速两种时钟源,它们之间可以动态切换,用户

可通过优化单片机操作来获得最佳性能 / 功耗比。

系统时钟

单片机为 CPU 和外围功能操作提供了多种不同的时钟源。用户使用配置选项和

寄存器编程可获取多种时钟,进而使系统时钟获取最大的应用性能。

主系统时钟可来自高频时钟源 fH 或低频时钟源 fSUB,通过 SMOD 寄存器中的

HLCLK 位及 CKS2~CKS0 位进行选择。高频时钟来自 HIRC 或 HXT 振荡器 ,

可通过配置选项选择,低频系统时钟源来自内部时钟 fSUB,若 fSUB 被选择,可

通过配置选项设定为 LXT 或 LIRC 振荡器。其它系统时钟还有高速系统振荡器

的分频 fH/2~fH/64。

另外两个内部时钟用于外围电路,次时钟源 fSUB 和时基时钟 fTBC。这两个时钟

源来自 LXT 或 LIRC 振荡器,通过配置选项选择。快速唤醒发生后,fSUB 为单

片机提供一个次时钟。

High Speed

Oscillator

HXT

fH

6-stage Prescaler

HIRC

High Speed Oscillator

Configuration Option

Low Speed

Oscillator

LXT

fH/2

fH/4

fH/8

fH/16

fH/32

fH/64

fSYS

fSUB

LIRC

HLCLK,

CKS2~CKS0 bits

Low Speed Oscillator

Configuration Option

Fast Wake-up from

SLEEP or IDLE Mode

Control (for HXT only)

fSUB

fSYS/4

fTB

fTBC

Time Base

TBCK

fS

Watchdog Timer

系统时钟选项

注:当系统时钟源 fSYS 由 fH 到 fSUB 转换时,高速振荡器将停止以节省耗电。因此,没有为外

围电路提供 fH~fH/64 的频率。

Rev. 1.50

37

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

系统工作模式

单片机有 6 种不同的工作模式,每种有它自身的特性,根据应用中不同的性能

和功耗要求可选择不同的工作模式。单片机正常工作有两种模式:正常模式和

低速模式。剩余的 4 种工作模式:休眠模式 0、休眠模式 1、空闲模式 0 和空闲

模式 1 用于单片机 CPU 关闭时以节省耗电。

工作模式

正常模式

低速模式

空闲模式 0

空闲模式 1

休眠模式 0

休眠模式 1

CPU

On

On

Off

Off

Off

Off

fSYS

fH~fH/64

fSUB

Off

On

Off

Off

说明

fSUB

On

On

On

On

Off

On

fS

On

On

On

On

Off

On

fTBC

On

On

On

On

Off

Off

正常模式

顾名思义,这是主要的工作模式之一,单片机的所有功能均可在此模式中实现

且系统时钟由一个高速振荡器提供。该模式下单片机正常工作的时钟源来自

HXT 或 HIRC 振荡器。高速振荡器频率可被分为 1~64 的不等比率,实际的比

率由 SMOD 寄存器中的 CKS2~CKS0 位及 HLCLK 位选择的。单片机使用高速

振荡器分频作为系统时钟可减少工作电流。

低速模式

此模式的系统时钟虽为低速时钟源,但单片机仍能正常工作。该低速时钟源可

来自 fSUB。单片机在此模式中运行所耗工作电流较低。在低速模式下,fH 关闭。

休眠模式 0

在 HALT 指令执行后且 SMOD 寄存器中 IDLEN 位为低时,系统进入休眠模式。

在休眠模式 0 中,CPU、fSUB 及 fS 停止运行,看门狗定时器功能除能。在该模

式中 LVDEN 位需置为“0”,否则将不能进入休眠模式 0 中。

休眠模式 1

在 HALT 指令执行后且 SMOD 寄存器中 IDLEN 位为低时,系统进入休眠模式。

在休眠模式 1 中,CPU 停止运行。然而若 LVDEN 位为“1”或看门狗定时器功

能使能时,fSUB 及 fS 继续运行。

空闲模式 0

执 行 HALT 指 令 后 且 SMOD 寄 存 器 中 IDLEN 位 为 高,CTRL 寄 存 器 中

FSYSON 位为低时,系统进入空闲模式 0。在空闲模式 0 中,CPU 停止,但一

些外围功能如看门狗定时器和 TMs 将继续工作。在空闲模式 0 中,系统振荡器

停止。

空闲模式 1

执 行 HALT 指 令 后 且 SMOD 寄 存 器 中 IDLEN 位 为 高,WDTC 寄 存 器 中

FSYSON 位为高时,系统进入空闲模式 1。在空闲模式 1 中,CPU 停止,但会

提供一个时钟源给一些外围功能如看门狗定时器和 TMs。在空闲模式 1 中,系

统振荡器继续运行,该系统振荡器可以为高速或低速系统振荡器。

Rev. 1.50

38

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

控制寄存器

寄存器 SMOD 用于控制单片机内部时钟。

SMOD 寄存器

Bit

7

Name CKS2

R/W

R/W

POR

0

Bit 7~5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Rev. 1.50

6

CKS1

R/W

0

5

CKS0

R/W

0

4

FSTEN

R/W

0

3

LTO

R

0

2

HTO

R

0

1

0

IDLEN HLCLK

R/W

R/W

1

1

CKS2~CKS0:当 HLCLK 为“0”时系统时钟选择位

000:fSUB(fLXT 或 fLIRC)

001:fSUB (fLXT 或 fLIRC)

010:fH/64

011:fH/32

100:fH/16

101:fH/8

110:fH/4

111:fH/2

这三位用于选择系统时钟源。除了 LIRC 或 LXT 振荡器提供的系统时钟源外,

也可使用高频振荡器的分频作为系统时钟。

FSTEN:快速唤醒控制位(仅用于 HXT)

0:除能

1:使能

此位为快速唤醒控制位,用于决定单片机被唤醒后 fSUB 是否开始工作。此位为

高电平且 fSUB 可用时,fSUB 时钟源可作为临时时钟,为系统提供一个较快速的唤

醒时间。

LTO:低速振荡器就绪标志位

0:未就绪

1:就绪

此位为低速系统振荡器就绪标志位,用于表明低速系统振荡器在系统上电复位

或经唤醒后何时稳定下来。当系统处于 SLEEP0 模式时,该标志为低。若系统

时钟来自 LXT 振荡器,系统唤醒后该位转换为高需 128 个时钟周期;若系统时

钟来自 LIRC 振荡器,该位转换为高需 1~2 个时钟周期。

HTO:高速振荡器就绪标志位

0:未就绪

1:就绪

此位为高速系统振荡器就绪标志位,用于表明高速系统振荡器何时稳定下来。

此标志在系统上电后经硬件清零,高速系统振荡器稳定后变为高电平。因此,

此位在单片机上电后由应用程序读取的总为“1”。该标志由休眠模式或空闲模

式 0 中唤醒后会处于低电平状态,若使用 HXT 振荡器,该位将在 512 个时钟周

期后变为高电平状态,若 HIRC 振荡器则只需 15~16 个时钟周期即可。

IDLEN:空闲模式控制位

0:除能

1:使能

此位为空闲模式控制位,用于决定 HALT 指令执行后发生的动作。若此位为

高,当指令 HALT 执行后,单片机进入空闲模式。若 FSYSON 位为高,在空闲

模式 1 中 CPU 停止运行,系统时钟将继续工作以保持外围功能继续工作;若

FSYSON 为低,在空闲模式 0 中 CPU 和系统时钟都将停止运行。若此位为低,

单片机将在 HALT 指令执行后进入休眠模式。

HLCLK:系统时钟选择位

0:fH/2~fH/64 或 fSUB

1:fH

此位用于选择 fH 或 fH/2~fH/64 还是 fSUB 作为系统时钟。该位为高时选择 fH 作为

系统时钟,为低时则选择 fH/2~fH/64 或 fSUB 作为系统时钟。当系统时钟由 fH 时

钟向 fSUB 时钟转换时,fH 将自动关闭以降低功耗。

39

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

快速唤醒

单片机进入休眠模式或空闲模式 0 后,系统时钟将停止以降低功耗。然而单片

机再次唤醒,原来的系统时钟重新起振、稳定且恢复正常工作需要一定的时

间。为确保单片机能够尽快的开始工作,系统提供了一个快速唤醒功能。需提

供一个临时时钟源 fSUB 先驱动系统直至原系统振荡器稳定,这个临时时钟可来

自 LXT 或 LIRC 振荡器。快速启动功能的时钟源为 fSUB,该功能仅在休眠模式

1 和空闲模式 0 中有效。当单片机由休眠模式 0 唤醒时,因 fSUB 已停止,故快

速唤醒功能不受影响。快速唤醒功能使能 / 除能由 SMOD 寄存器中 FSTEN 位

控制的。

若 HXT 振荡器作为正常模式的系统时钟,且快速唤醒功能使能,系统唤醒将需

1~2 个 tSUB 时钟周期。系统开始在 fSUB 时钟源下运行直至 512 个 HXT 时钟周期

后 HTO 标志转换为高,系统将切换到 HXT 振荡器运行。

若系统振荡器选用 HIRC,将系统从休眠模式或空闲模式 0 中唤醒需 15~16 个

时钟周期;若选用 LIRC,则需 1~2 个周期。快速唤醒位 FSTEN 在这些情况下

不受影响。

系统

振荡器

HXT

HIRC

LIRC

LXT

FSTEN

唤醒时间

位

(休眠模式 0)

0

128 个 HXT 周期

1

×

×

×

唤醒时间

唤醒时间

(休眠模式 1) (空闲模式 0)

128 个 HXT 周期

1~2 个 fSUB 周期

( 系统在 fSUB 下运行 512 个 HXT

128 个 HXT 周期

周期后切换到 HXT 振荡器运行 )

15~16 个 HIRC 周期 15~16 个 HIRC 周期

1~2 个 LIRC 周期

1~2 个 LIRC 周期

1~2 个 LXT 周期

128 个 LXT 周期

唤醒时间

(空闲模式 1)

1~2 个 HXT 周期

1~2 个 HXT 周期

1~2 个 HIRC 周期

1~2 个 LIRC 周期

1~2 个 LXT 周期

唤醒时间

注:若看门狗定时器除能,意味着 LXT 和 LIRC 都关闭,当单片机由休眠模式 0 中唤醒时快速唤醒功能

不可用。

Rev. 1.50

40

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

工作模式切换

单片机可在各个工作模式间自由切换,使得用户可根据所需选择最佳的性能 /

功耗比。用此方式,对单片机工作的性能要求不高的情况下,可使用较低频时

钟以减少工作电流,在便携式应用上延长电池的使用寿命。

简单来说,正常模式和低速模式间的切换仅需设置 SMOD 中的 HLCLK 位及

CKS2~CKS0 位即可实现,而正常模式 / 低速模式与休眠模式 / 空闲模式间的切

换经由 HALT 指令实现。当 HALT 指令执行后,单片机是否进入空闲模式或休

眠模式由 SMOD 寄存器中的 IDLEN 位和 CTRL 寄存器中的 FSYSON 位决定的。

当 HLCLK 位变为低电平时,时钟源将由高速时钟源 fH 转换成时钟源 fH/2~fH/64

或 fSUB。若时钟源来自 fSUB,高速时钟源将停止运行以节省耗电。此时须注意,

fH/16 和 fH/64 内部时钟源也将停止运行,由此会影响到内部功能如 TMs 的工作。

所附流程图显示了单片机在不同工作模式间切换时的变化。

Rev. 1.50

41

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

正常模式切换到低速模式

系统运行在正常模式时使用高速系统振荡器,因此较为耗电。可通过设置

SMOD 寄存器中的 HLCLK 位为“0”及 CKS2~CKS0 位为“000”或“001”使

系统时钟切换至运行在低速模式下。此时将使用低速系统振荡器以节省耗电。

用户可在对性能要求不高的操作中使用此方法以减少耗电。

低速模式的时钟源来自 LIRC 或 LXT 振荡器,因此要求这些振荡器在所有模式

切换动作发生前稳定下来。该动作由 SMOD 寄存器中 LTO 位控制。

Rev. 1.50

42

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

低速模式切换到正常模式

在低速模式系统使用 LIRC 或 LXT 低速振荡器。切换到使用高速系统时钟振

荡 器 的 正 常 模 式 需 设 置 HLCLK 位 为“1”, 也 可 设 置 HLCLK 位 为“0” 但

CKS2~CKS0 需设为“010”、“011”、“100”、“101”、“110”或“111”。

高频时钟需要一定的稳定时间,通过检测 HTO 位的状态可进行判断。高速振荡

器的稳定时间由所使用高速系统振荡器的类型决定。

Rev. 1.50

43

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

进入休眠模式 0

进入休眠模式 0 的方法仅有一种——应用程序中执行“HALT”指令前需设置寄

存器 SMOD 中 IDLEN 位为“0”且 WDT 和 LVD 功能除能。在上述条件下执

行该指令后,将发生的情况如下:

● 系统时钟、WDT 时钟和时基时钟停止运行,应用程序停止在“HALT”指令

处。

● 数据存储器中的内容和寄存器将保持当前值。

● WDT 被清除并停止运行。

● 输入 / 输出口将保持当前值。

● 状态寄存器中暂停标志 PDF 将被置起,看门狗溢出标志 TO 将被清除。

进入休眠模式 1

进入休眠模式 1 的方法仅有一种——应用程序中执行“HALT”指令前需设置寄

存器 SMOD 中 IDLEN 位为“0”且 WDT 或 LVD 功能使能。在上述条件下执

行该指令后,将发生的情况如下:

● 系统时钟和时基时钟停止运行,应用程序停止在“HALT”指令处。WDT 或

LVD 继续运行,其时钟源来自 fSUB。

● 数据存储器中的内容和寄存器将保持当前值。

● 若 WDT 使能,WDT 将被清零并重新开始计数。

● 输入 / 输出口将保持当前值。

● 状态寄存器中暂停标志 PDF 将被置起,看门狗溢出标志 TO 将被清除。

进入空闲模式 0

进入空闲模式 0 的方法仅有一种——应用程序中执行“HALT”指令前需设置寄

存器 SMOD 中 IDLEN 位为“1”且 CTRL 寄存器中的 FSYSON 位为“0”。在

上述条件下执行该指令后,将发生的情况如下:

● 系统时钟停止运行,应用程序停止在“HALT”指令处,时基时钟 fTBC 和 fSUB

时钟将继续运行。

● 数据存储器中的内容和寄存器将保持当前值。

● 若 WDT 使能,WDT 将被清零并重新开始计数

● 输入 / 输出口将保持当前值。

● 状态寄存器中暂停标志 PDF 将被置起,看门狗溢出标志 TO 将被清除。

进入空闲模式 1

进入空闲模式 1 的方法仅有一种——应用程序中执行“HALT”指令前需设置寄

存器 SMOD 中 IDLEN 位为“1”且 CTRL 寄存器中的 FSYSON 位为“1”。在

上述条件下执行该指令后,将发生的情况如下:

● 系统时钟、时基时钟和 fSUB 开启,应用程序停止在“HALT”指令处。

● 数据存储器中的内容和寄存器将保持当前值。

● 若 WDT 使能,WDT 将被清零并重新开始计数。

● 输入 / 输出口将保持当前值。

● 状态寄存器中暂停标志 PDF 将被置起,看门狗溢出标志 TO 将被清除。

Rev. 1.50

44

2016-07-01

�HT66F018

内置 EEPROM 增强 A/D 型单片机

静态电流的注意事项

由于单片机进入休眠或空闲模式的主要原因是将 MCU 的电流降低到尽可能低,

可能到只有几个微安的级别(空闲模式 1 除外),所以如果要将电路的电流降

到最低,电路设计者还应有其它的考虑。应该特别注意的是单片机的输入 / 输

出引脚。所有高阻抗输入脚都必须连接到固定的高或低电平,因为引脚浮空会

造成内部振荡并导致耗电增加。这也应用于有不同封装的单片机,因为它们可

能含有未引出的引脚,这些引脚也必须设为输出或带有上拉电阻的输入。

另外还需注意单片机设为输出的 I/O 引脚上的负载。应将它们设置在有最小拉

电流的状态或将它们和其它的 CMOS 输入一样接到没有拉电流的外部电路上。

还应注意的是,如果使能配置选项中的 LXT 或 LIRC 振荡器,会导致耗电增加。

在空闲模式 1 中,系统时钟开启。若系统时钟来自高速系统振荡器,额外的静

态电流也可能会有几百微安。

唤醒

系统进入休眠或空闲模式之后,可以通过以下几种方式唤醒:

● PA 口下降沿

● 系统中断

● WDT 溢出

若由 WDT 溢出唤醒,则会发生看门狗定时器复位。这种唤醒方式会使系统复

位,可以通过状态寄存器中 TO 和 PDF 位来判断它的唤醒源。系统上电或执行

清除看门狗的指令,会清零 PDF;执行 HALT 指令,PDF 将被置位。看门狗计

数器溢出将会置位 TO 标志并唤醒系统,这种复位会重置程序计数器和堆栈指

针,其它标志保持原有状态。

PA 口中的每个引脚都可以通过 PAWU 寄存器使能下降沿唤醒功能。PA 端口唤

醒后,程序将在“HALT”指令后继续执行。如果系统是通过中断唤醒,则有两

种可能发生。第一种情况是:相关中断除能或是中断使能且堆栈已满,则程序

会在“HALT”指令之后继续执行。这种情况下,唤醒系统的中断会等到相关中

断使能或有堆栈层可以使用之后才执行。第二种情况是:相关中断使能且堆栈

未满,则中断可以马上执行。 如果在进入休眠或空闲模式之前中断标志位已经

被设置为“1”,则相关中断的唤醒功能将无效。

编程注意事项

高速和低速振荡器使用相同的 SST 计数器。例如,若系统从休眠模式 0 中唤醒,