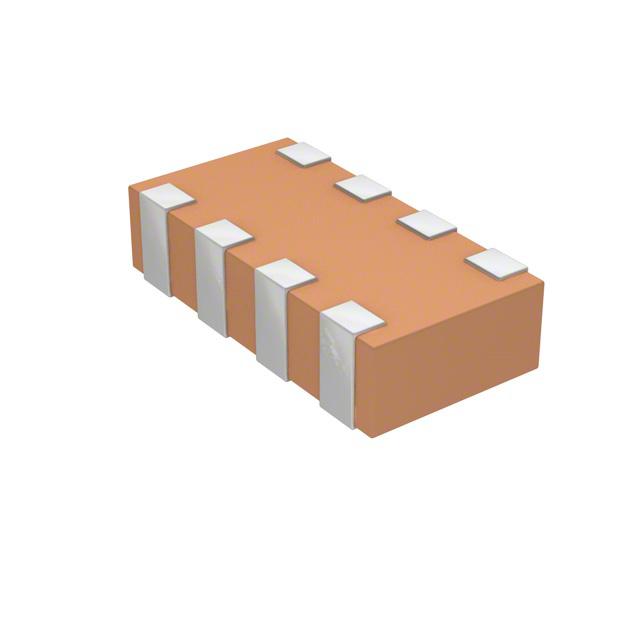

Surface Mount Multilayer Ceramic Chip Capacitors (SMD MLCCs)

Capacitor Array, X7R Dielectric, 10 – 200 VDC

(Commercial & Automotive Grade)

Overview

KEMET’s Ceramic Chip Capacitor Array in X7R dielectric is an

advanced passive technology where multiple capacitor elements

are integrated into one common monolithic structure. Array

technology promotes reduced placement costs and increased

throughput. This is achieved by alternatively placing one device

rather than two or four discrete devices. Use of capacitor arrays

also saves board space which translates into increased board

density and more functions per board. Arrays consume only a

portion of the space required for standard chips resulting in savings

in inventory and pick/place machine positions.

Electronics Industries Alliance (EIA) characterizes X7R dielectric

DV�D�&ODVV�,,�PDWHULDO��&RPSRQHQWV�RI�WKLV�FODVVL¿�FDWLRQ�DUH�¿�[HG��

ceramic dielectric capacitors suited for bypass and decoupling

applications or for frequency discriminating circuits where Q and

stability of capacitance characteristics are not critical. X7R exhibits

a predictable change in capacitance with respect to time and

voltage and boasts a minimal change in capacitance with reference

to ambient temperature. Capacitance change is limited to ±15%

from -55°C to +125°C.

KEMET automotive grade array capacitors meet the demanding

$XWRPRWLYH�(OHFWURQLFV�&RXQFLO

V�$(&±4����TXDOL¿�FDWLRQ�

requirements.

KEMET’s X7R dielectric features a 125°C maximum operating

temperature and is considered “temperature stable.” The

%HQHÀ�WV

•

•

•

•

•

•

-55°C to +125°C operating temperature range

Saves both circuit board and inventory space

Reduces placement costs and increases throughput

RoHS Compliant

EIA 0508 (2-element) and 0612 (4-element) case sizes

DC voltage ratings of 10 V, 16 V, 25 V, 50 V, 100 V, and 200 V

Ordering Information

CA

06

4

C

Ceramic Case Size Number of 6SHFL¿�FDWLRQ�

Array

(L" x W")1 Capacitors

Series

05 = 0508

06 = 0612

2=2

4=4

104

K

4

R

Capacitance

Code (pF)

Capacitance

Tolerance

Voltage

Dielectric

C = Standard

��6LJQL¿�FDQW�

X = Flexible Digits + Number

Termination

of Zeros

J = ±5%

K = ±10%

M = ±20%

8 = 10 V R = X7R

4 = 16 V

3 = 25 V

5 = 50 V

1 = 100 V

2 = 200 V

A

C

TU

Failure Rate/ Termination

Design

Finish2

A = N/A

C = 100%

Matte Sn

L = SnPb

(5%

minimum)

Packaging/Grade

(C-Spec)3

Blank = Bulk

TU = 7" Reel

Unmarked

TM = 7" Reel Marked

AUTO = Automotive

Grade

All previous reference to metric case dimension "1632" has been replaced with an inch standard reference of "0612". Please reference all new designs using the

"0612" nomenclature. "CA064" replaces "C1632" in the ordering code.

2

$GGLWLRQDO�WHUPLQDWLRQ�¿�QLVK�RSWLRQV�PD\�EH�DYDLODEOH��&RQWDFW�.(0(7�IRU�GHWDLOV��

2,3

6Q3E�WHUPLQDWLRQ�¿�QLVK�RSWLRQ�LV�QRW�DYDLODEOH�RQ�DXWRPRWLYH�JUDGH�SURGXFW�

3

Additional reeling or packaging options may be available. Contact KEMET for details.

1

One world. One KEMET

© KEMET Electronics Corporation • P.O. Box 5928 • Greenville, SC 29606 (864) 963-6300 • www.kemet.com

CC101_COMM_SMD • 11/25/2013

60

�Surface Mount Multilayer Ceramic Chip Capacitors (SMD MLCCs)

Capacitor Array, X7R Dielectric, 10 – 200 VDC (Commercial & Automotive Grade)

Dimensions – Millimeters (Inches)

EIA

Size

Code

Metric

Size

Code

L

Length

W

Width

BW

Bandwidth

BL

Bandlength

0508

1220

1.30 (0.051)

±0.15 (0.006)

2.10 (0.083)

±0.15 (0.006)

0.53 (0.021)

±0.08 (0.003)

0.30 (0.012)

±0.20 (0.008)

0612

1632

1.60 (0.063)

±0.20 (0.008)

3.20 (0.126)

±0.20 (0.008)

0.40 (0.016)

±0.20 (0.008)

0.30 (0.012)

±0.20 (0.008)

T

Thickness

See Table 2 for

Thickness

P

Pitch

P

Reference

1.00 (0.039)

±0.10 (0.004)

0.50 (0.020)

±0.10 (0.004)

0.80 (0.031)

±0.10 (0.004)

0.40 (0.016)

±0.05 (0.002)

%HQHÀ�WV�FRQW

G

•

•

•

�

Capacitance offerings ranging from 330 pF – 0.22 μF

Available capacitance tolerances of ±5%, ±10%, and ±20%

Non-polar device, minimizing installation concerns

�����SXUH�PDWWH�WLQ�SODWHG�WHUPLQDWLRQ�¿�QLVK�DOORZLQJ�IRU�

excellent solderability

� 6Q3E�WHUPLQDWLRQ�¿�QLVK�RSWLRQ�DYDLODEOH�XSRQ�UHTXHVW�����

minimum)

• Flexible termination option available upon request

• Commercial and Automotive (AEC–Q200) grades available

Applications

7\SLFDO�DSSOLFDWLRQV�LQFOXGH�WKRVH�WKDW�FDQ�EHQH¿�W�IURP�ERDUG�DUHD�VDYLQJV��FRVW�VDYLQJV�DQG�RYHUDOO�YROXPHWULF�UHGXFWLRQ�VXFK�DV�

telecommunications, computers, handheld devices and automotive.

4XDOLÀ�FDWLRQ�&HUWLÀ�FDWLRQ

&RPPHUFLDO�*UDGH�SURGXFWV�DUH�VXEMHFW�WR�LQWHUQDO�TXDOL¿�FDWLRQ��'HWDLOV�UHJDUGLQJ�WHVW�PHWKRGV�DQG�FRQGLWLRQV�DUH�UHIHUHQFHG�LQ�

Table 4, Performance & Reliability.

Automotive Grade products meet or exceed the requirements outlined by the Automotive Electronics Council. Details regarding test

PHWKRGV�DQG�FRQGLWLRQV�DUH�UHIHUHQFHG�LQ�GRFXPHQW�$(&±4�����6WUHVV�7HVW�4XDOL¿�FDWLRQ�IRU�3DVVLYH�&RPSRQHQWV��)RU�DGGLWLRQDO�

information regarding the Automotive Electronics Council and AEC–Q200, please visit their website at www.aecouncil.com.

© KEMET Electronics Corporation • P.O. Box 5928 • Greenville, SC 29606 (864) 963-6300 • www.kemet.com

CC101_COMM_SMD • 11/25/2013

61

�Surface Mount Multilayer Ceramic Chip Capacitors (SMD MLCCs)

Capacitor Array, X7R Dielectric, 10 – 200 VDC (Commercial & Automotive Grade)

Environmental Compliance

3E�)UHH�DQG�5R+6�&RPSOLDQW��H[FOXGLQJ�6Q3E�WHUPLQDWLRQ�¿�QLVK�RSWLRQ���

(OHFWULFDO�3DUDPHWHUV�&KDUDFWHULVWLFV

Item

3DUDPHWHUV�&KDUDFWHULVWLFV

Operating Temperature Range

-55°C to +125°C

Capacitance Change with Reference to +25°C and 0 VDC Applied (TCC

±15%

Aging Rate (Maximum % Capacitance Loss/Decade Hour)

3.0%

Dielectric Withstanding Voltage (DWV)

Dissipation Factor (DF) Maximum Limit @ 25ºC

Insulation Resistance (IR) Limit @ 25°C

250% of rated voltage

(5 ±1 seconds and charge/discharge not exceeding 50 mA)

5%(10 V), 3.5%(16 V and 25 V) and 2.5%(50 V to 200 V)

������PHJRKP�PLFURIDUDGV�RU�����*ȍ

(Rated voltage applied for 120 ±5 seconds @ 25°C)

Regarding aging rate: Capacitance measurements (including tolerance) are indexed to a referee time of 1,000 hours.

7R�REWDLQ�,5�OLPLW��GLYLGH�0ȍ�)�YDOXH�E\�WKH�FDSDFLWDQFH�DQG�FRPSDUH�WR�*ȍ�OLPLW��6HOHFW�WKH�ORZHU�RI�WKH�WZR�OLPLWV�

Capacitance and dissipation factor (DF) measured under the following conditions:

�

��N+]����+]�DQG���������9UPV�LI�FDSDFLWDQFH�����)

�

����+]����+]�DQG���������9UPV�LI�FDSDFLWDQFH�!����)

Note: When measuring capacitance it is important to ensure the set voltage level is held constant. The HP4284 and Agilent E4980 have a feature known as

Automatic Level Control (ALC). The ALC feature should be switched to "ON."

Post Environmental Limits

High Temperature Life, Biased Humidity, Moisture Resistance

Dielectric

Rated DC

Voltage

Capacitance

Value

> 25

X7R

16/25

< 16

Dissipation Factor

(Maximum %)

Capacitance

Shift

Insulation

Resistance

±20%

10% of Initial Limit

3.0

All

5.0

7.5

© KEMET Electronics Corporation • P.O. Box 5928 • Greenville, SC 29606 (864) 963-6300 • www.kemet.com

CC101_COMM_SMD • 11/25/2013

62

�Surface Mount Multilayer Ceramic Chip Capacitors (SMD MLCCs)

Capacitor Array, X7R Dielectric, 10 – 200 VDC (Commercial & Automotive Grade)

7DEOH���²�&DSDFLWDQFH�5DQJH�6HOHFWLRQ�:DWHUIDOO�������²������&DVH�6L]HV��

&DVH�6L]H���6HULHV C0508 (CA052C 2-Cap Case Size)

Capacitance

Capacitance

Code

330 pF

390 pF

470 pF

560 pF

680 pF

820 pF

1,000 pF

1,200 pF

1,500 pF

1,800 pF

2,200 pF

2,700 pF

3,300 pF

3,900 pF

4,700 pF

5,600 pF

6,800 pF

8,200 pF

10,000 pF

12,000 pF

15,000 pF

18,000 pF

22,000 pF

27,000 pF

33,000 pF

39,000 pF

47,000 pF

56,000 pF

68,000 pF

82,000 pF

0.10 uF

0.15 uF

0.22 uF

331

391

471

561

681

821

102

122

152

182

222

272

332

392

472

562

682

822

103

123

153

183

223

273

333

393

473

563

683

823

104

154

224

Capacitance

Capacitance Code

Voltage Code

8

4

3

Rated Voltage (VDC)

10

16

25

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

Rated Voltage (VDC)

10

16

Voltage Code

8

4

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

J

Capacitance

Tolerance

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

K

&DVH�6L]H���6HULHV

5

1

C0612 (CA064C 4-Cap Case Size)

8

4

3

50

100

10

16

25

Product Availability and Chip Thickness Codes

See Table 2 for Chip Thickness Dimensions

5

1

2

50

100

200

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

PA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

MA

25

50

100

10

16

25

50

100

200

3

5

1

8

4

3

5

1

2

C0508

C0612

7DEOH���²�&KLS�7KLFNQHVV���3DFNDJLQJ�4XDQWLWLHV

Paper Quantity

Plastic Quantity

Thickness

Code

Case

Size

Thickness ±

Range (mm)

7" Reel

13" Reel

7" Reel

13" Reel

PA

MA

0508

0612

0.80 ± 0.10

0.80 ± 0.10

0

0

0

0

4,000

4,000

10,000

10,000

3DFNDJH�TXDQWLW\�EDVHG�RQ�¿QLVKHG�FKLS�WKLFNQHVV�VSHFL¿FDWLRQV�

© KEMET Electronics Corporation • P.O. Box 5928 • Greenville, SC 29606 (864) 963-6300 • www.kemet.com

CC101_COMM_SMD • 11/25/2013

63

�Surface Mount Multilayer Ceramic Chip Capacitors (SMD MLCCs)

Capacitor Array, X7R Dielectric, 10 – 200 VDC (Commercial & Automotive Grade)

Table 3 – Chip Capacitor Array Land Pattern Design Recommendations per IPC–7351

EIA SIZE

CODE

METRIC

SIZE

CODE

Density Level A:

Maximum (Most) Land

Protrusion (mm)

Density Level B:

Median (Nominal) Land

Protrusion (mm)

Density Level C:

Minimum (Least) Land

Protrusion (mm)

C

Y

X

P

V1

V2

C

Y

X

P

V1

V2

C

Y

X

P

V1

V2

0508/CA052

1220

1.60

1.00

0.55

1.00

3.50

3.30

1.50

0.90

0.50

1.00

2.90

2.80

1.40

0.75

0.45

1.00

2.40

2.50

0612/CA064

1632

1.80

1.10

0.50

0.80

3.90

4.40

1.80

0.95

0.50

0.80

3.30

3.90

1.70

0.85

0.40

0.80

2.80

3.60

Density Level A: )RU�ORZ�GHQVLW\�SURGXFW�DSSOLFDWLRQV��3URYLGHV�D�ZLGHU�SURFHVV�ZLQGRZ�IRU�UHÀ�RZ�VROGHU�SURFHVVHV��

Density Level B: )RU�SURGXFWV�ZLWK�D�PRGHUDWH�OHYHO�RI�FRPSRQHQW�GHQVLW\��3URYLGHV�D�UREXVW�VROGHU�DWWDFKPHQW�FRQGLWLRQ�IRU�UHÀ�RZ�VROGHU�SURFHVVHV�

Density Level C: )RU�KLJK�FRPSRQHQW�GHQVLW\�SURGXFW�DSSOLFDWLRQV��%HIRUH�DGDSWLQJ�WKH�PLQLPXP�ODQG�SDWWHUQ�YDULDWLRQV�WKH�XVHU�VKRXOG�SHUIRUP�TXDOL¿�FDWLRQ�

testing based on the conditions outlined in IPC Standard 7351 (IPC–7351).

V2

P

V1

C

X

Y

Grid Placement Courtyard

Soldering Process

Recommended Soldering Technique:

� �6ROGHU�UHÀ�RZ�RQO\

5HFRPPHQGHG�6ROGHULQJ�3UR¿�OH�

• KEMET recommends following the guidelines outlined in IPC/JEDEC J–STD–020

© KEMET Electronics Corporation • P.O. Box 5928 • Greenville, SC 29606 (864) 963-6300 • www.kemet.com

CC101_COMM_SMD • 11/25/2013

64

�Surface Mount Multilayer Ceramic Chip Capacitors (SMD MLCCs)

Capacitor Array, X7R Dielectric, 10 – 200 VDC (Commercial & Automotive Grade)

Table 4 – Performance & Reliability: Test Methods and Conditions

Stress

Reference

Test or Inspection Method

Terminal Strength

JIS–C–6429

Appendix 1, Note: Force of 1.8 kg for 60 seconds.

Board Flex

JIS–C–6429

Appendix 2, Note: Standard termination system – 2.0 mm (minimum) for all except 3 mm for C0G.

Flexible termination system – 3.0 mm (minimum).

0DJQL¿�FDWLRQ����;��&RQGLWLRQV�

Solderability

J–STD–002

a) Method B, 4 hours @ 155°C, dry heat @ 235°C

b) Method B @ 215°C category 3

c) Method D, category 3 @ 260°C

Temperature Cycling

JESD22 Method JA–104

1,000 Cycles (-55°C to +125°C). Measurement at 24 hours +/- 2 hours after test conclusion.

Load Humidity: 1,000 hours 85°C/85% RH and rated voltage. Add 100 K ohm resistor. Measurement

at 24 hours +/- 2 hours after test conclusion.

Low Volt Humidity: 1,000 hours 85°C/85% RH and 1.5 V. Add 100 K ohm resistor.

Measurement at 24 hours +/- 2 hours after test conclusion.

t = 24 hours/cycle. Steps 7a and 7b not required. Unpowered.

Measurement at 24 hours +/- 2 hours after test conclusion.

-55°C/+125°C. Note: Number of cycles required – 300, maximum transfer time – 20 seconds, dwell

time – 15 minutes. Air – Air.

Biased Humidity

MIL–STD–202 Method 103

Moisture Resistance

MIL–STD–202 Method 106

Thermal Shock

MIL–STD–202 Method 107

High Temperature Life

MIL–STD–202 Method 108

/EIA–198

Storage Life

MIL–STD–202 Method 108

150°C, 0 VDC for 1,000 hours.

Vibration

MIL–STD–202 Method 204

5 g's for 20 min., 12 cycles each of 3 orientations. Note: Use 8" X 5" PCB 0.031" thick 7 secure

points on one long side and 2 secure points at corners of opposite sides. Parts mounted within 2"

from any secure point. Test from 10 – 2,000 Hz

Mechanical Shock

MIL–STD–202 Method 213

Figure 1 of Method 213, Condition F.

Resistance to Solvents

MIL–STD–202 Method 215

Add aqueous wash chemical, OKEM Clean or equivalent.

1,000 hours at 125°C (85°C for X5R, Z5U and Y5V) with 2 X rated voltage applied.

Storage & Handling

Ceramic chip capacitors should be stored in normal working environments. While the chips themselves are quite robust in other

environments, solderability will be degraded by exposure to high temperatures, high humidity, corrosive atmospheres, and long term

storage. In addition, packaging materials will be degraded by high temperature– reels may soften or warp and tape peel force may

increase. KEMET recommends that maximum storage temperature not exceed 40ºC and maximum storage humidity not exceed 70%

UHODWLYH�KXPLGLW\��7HPSHUDWXUH�À�XFWXDWLRQV�VKRXOG�EH�PLQLPL]HG�WR�DYRLG�FRQGHQVDWLRQ�RQ�WKH�SDUWV�DQG�DWPRVSKHUHV�VKRXOG�EH�IUHH�RI�

chlorine and sulfur bearing compounds. For optimized solderability chip stock should be used promptly, preferably within 1.5 years of

receipt.

© KEMET Electronics Corporation • P.O. Box 5928 • Greenville, SC 29606 (864) 963-6300 • www.kemet.com

CC101_COMM_SMD • 11/25/2013

65

�Surface Mount Multilayer Ceramic Chip Capacitors (SMD MLCCs)

Capacitor Array, X7R Dielectric, 10 – 200 VDC (Commercial & Automotive Grade)

Construction – Standard Termination

Reference

Item

A

B

Termination

System

Material

Finish

100% Matte Sn

Barrier Layer

Ni

Base Metal

Cu

C

D

Inner Electrode

Ni

E

Dielectric Material

BaTiO3

Note: Image is exaggerated in order to clearly identify all components of construction.

Construction – Flexible Termination

Reference

Item

A

B

C

D

Termination

System

Material

Finish

100% Matte Sn

Barrier Layer

Ni

Epoxy Layer

Ag

Base Metal

Cu

E

Inner Electrode

Ni

F

Dielectric Material

BaTiO3

Note: Image is exaggerated in order to clearly identify all components of construction.

© KEMET Electronics Corporation • P.O. Box 5928 • Greenville, SC 29606 (864) 963-6300 • www.kemet.com

CC101_COMM_SMD • 11/25/2013

66

�Surface Mount Multilayer Ceramic Chip Capacitors (SMD MLCCs)

Commercial Off-the-Shelf (COTS) for Higher Reliability

Applications, C0G Dielectric, 10 – 200 VDC

Overview

KEMET’s COTS program is an extension of KEMET knowledge

of high reliability test regimes and requirements. KEMET regularly

supplies “up-screened” products by working with customer

GUDZLQJV�DQG�LPSRVLQJ�VSHFL¿�HG�GHVLJQ�DQG�WHVW�UHTXLUHPHQWV��

The COTS program offers the same high quality and high reliability

components as up-screened products, but at a lower cost to

the customer. This is accomplished by eliminating the need for

FXVWRPHU�VSHFL¿�F�GUDZLQJV�WR�DFKLHYH�WKH�UHOLDELOLW\�OHYHO�UHTXLUHG�

for customer applications. A series of tests and inspections have

been selected to provide the accelerated conditioning and 100%

screening necessary to eliminate infant mortal failures from the

population.

temperature. Capacitance change is limited to ±30 ppm/ºC from

-55°C to +125°C.

All COTS testing includes voltage conditioning and post-electrical

testing as per MIL–PRF–55681. For enhanced reliability, KEMET

also provides the following test level options and conformance

FHUWL¿�FDWLRQV�

Test Level A

Test Level B

Test Level C

Voltage Conditioning

DWV

IR@25°C

CAP

DF

Voltage Conditioning

DWV

IR@25°C

CAP

DF

Voltage Conditioning

DWV

IR@25°C

CAP

DF

PDA 8%

PDA 8%

PDA 8%

C of C

DPA

DPA

C of C

85/85

KEMET’s C0G dielectric features a 125°C maximum operating

temperature and is considered “stable.” The Electronics

Components, Assemblies & Materials Association (EIA)

characterizes C0G dielectric as a Class I material. Components

RI�WKLV�FODVVL¿�FDWLRQ�DUH�WHPSHUDWXUH�FRPSHQVDWLQJ�DQG�DUH�VXLWHG�

for resonant circuit applications or those where Q and stability

of capacitance characteristics are required. C0G exhibits no

change in capacitance with respect to time and voltage and boasts

a negligible change in capacitance with reference to ambient

C of C

Ordering Information

C

Ceramic

1206

T

Case Size 6SHFL¿�FDWLRQ�

(L" x W")

Series

0402

0603

0805

1206

1210

1812

2220

T = COTS

104

K

5

G

A

C

TU

Capacitance

Code (pF)

Capacitance

Tolerance1

Voltage

Dielectric

Failure Rate/Design

Termination

Finish2

Packaging/Grade

(C-Spec)3

��6LJQL¿�FDQW�

Digits + Number

of Zeros

Use 9 for

1.0 – 9.9 pF

Use 8 for

0.5 – .99 pF

ex. 2.2 pF = 229

ex. 0.5 pF = 508

B = ±0.10 pF

C = ±0.25 pF

D = ±0.5 pF

F = ± 1%

G = ±2%

J = ±5%

K = ±10%

M = ±20%

8 = 10 V

4 = 16 V

3 = 25 V

6 = 35 V

5 = 50 V

1 = 100 V

2 = 200 V

G = C0G

A = Testing per MIL–PRF–

55681 PDA 8%

B= Testing per MIL–PRF–

55681 PDA 8%, DPA per

EIA–469

C = Testing per MIL–

PRF–55681 PDA 8%, DPA

per EIA–469, Humidity per

MIL–STD–202, Method 103,

Condition A

C = 100%

Matte Sn

L = SnPb (5%

minimum)

Blank = Bulk

TU = 7" Reel

Unmarked

TM = 7" Reel

Marked

Additional capacitance tolerance offerings may be available. Contact KEMET for details.

�$GGLWLRQDO�WHUPLQDWLRQ�¿�QLVK�RSWLRQV�PD\�EH�DYDLODEOH��&RQWDFW�.(0(7�IRU�GHWDLOV��

3

Additional reeling or packaging options may be available. Contact KEMET for details.

1

2

One world. One KEMET

© KEMET Electronics Corporation • P.O. Box 5928 • Greenville, SC 29606 (864) 963-6300 • www.kemet.com

CC101_COMM_SMD • 11/25/2013

67

�