NXP Semiconductors

Data Sheet: Technical Data

Document Number: K32L3A

Rev. 1, 09/2019

K32L3A

72 MHz Arm® Cortex®-M0+/M4F Dual Core Microcontroller

with up to 1280 KB Flash and 384 KB SRAM

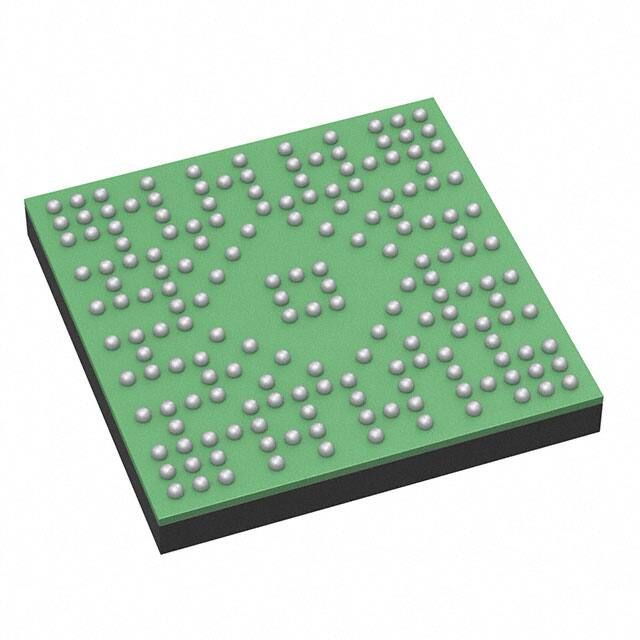

K32L3A60VPJ1AT

The K32L3A family of devices is an ultra-low-power, dual core

solution ideal for applications that require a high performance

Cortex-M4F processor to run the application and an efficient

Cortex-M0+ to run low power operations such as sensor data

collection and perform low level operations that don't need the

full power of the M4 core.

176 VFBGA

9 x 9 x 1 mm Pitch 0.5 mm

Core Processor

• Arm Cortex-M4F core up to 72 MHz (high-speed run up to

72 MHz) for application code

• Arm Cortex-M0+ core up to 72 MHz (high-speed run up to

72 MHz) for low power operations

Memories

• 1.25 MB program flash memory, 1 MB on the M4F domain

and 256 KB on the M0+ domain

• 384 KB SRAM, 256 KB on the M4F domain and 128 KB on

the M0+ domain

• 48 KB ROM with built-in bootloader

• 32 B system register file and 32 B RTC register file

• External bus interface (FlexBUS) for off-chip memory

expansion

Clocks

• Low-Power Frequency-Locked Loop (LPFLL)

• Range 1: 48 MHz

• Range 2: 72 MHz

• Internal Resistance-Capacitance Oscillators (IRCs)

• Fast-Speed IRC (48, 52, 56, 60 MHz)

• Slow-Speed IRC (8 MHz or 2 MHz)

• Low Power Oscillator (LPO - 1 kHz)

• Real Time Clock Oscillator (RTCOSC)

• System Clock Generation

System

• Dual Direct Memory Access (DMA) controllers with

asynchronous capability

• M4F: 16 channels, 64 inputs per channel

• M0+: 8 channels, 32 inputs per channel

Timers

• 2 x 6 ch., 2 x 2 ch. Timer PWM Modules (TPM)

• 2 x 4 ch. Low Power Programmable Interrupt

Timer (LPIT)

• 3 Low Power Timer (LPTMR)

• Real Time Clock (RTC)

• One 56-bit Time stamp

Security and Integrity

• 80-bit unique identification number per chip

• Advanced Flash security and access control

• 16-bit or 32-bit Hardware CRC with

programmable generator polynomial

• Low-power Cryptographic Acceleration Unit

(CAU3) supporting AES128/196/256, DES/

3DES, SHA 256, RSA and ECC PK-256/

Curve25519

• True Random Number Generator

• Up to 4 active anti-tamper detection pins

Analog

• 1 x 12-bit single ended low-power ADC

• 2 x Low power comparator (LPCMP) each

containing a 6-bit DAC and programmable

reference input

• 1 x 12-bit low power digital-to-analog converter

(LPDAC)

• 1 x 1.2V/2.1V dual-range VREF

Peripherals

• 1 x Universal Serial Bus (USB) 2.0 Full Speed

(FS) controller with integrated hardware

transceiver, 5 V regulator and 2 KB USB RAM

NXP reserves the right to change the production detail specifications as may be

required to permit improvements in the design of its products.

�• Two internal Watchdog and one external Watchdog Monitor

• Low-leakage wakeup unit

• JTAG and Serial Wire Debug, version 2.0, programming and

debug interface with multi-drop capability

• Trace Features for M4F

• Cross Trigger Interface

• Embedded Trace Macrocell

• Trace Port Interface Unit

• Trace Features for M0+

• Cross Trigger Interface

• Micro Trace Buffer

• Breakpoint and Watchpoint Unit

• Nested Vectored Interrupt Controller

• Memory Protection Unit

• Extended Resource Domain Controller

• 1 x 32 ch. FlexIO supporting emulation of

UART, I2C, SPI, I2S, Camera IF, LCD RGB,

PWM/Waveform generation

• 4 x low power UART (LPUART)

• 4 x low power I2C (LPI2C) modules supporting

up to 1 Mbps

• 4 x 16-bit low power SPI (LPSPI) supporting

up to 24 Mbps

• 1 x EMVSIM module supporting supporting

ISO-7816 protocol

• 1 x Serial Audio Interface (SAI) with support for

I2S and AC'97

• 1 x Secure Digital Hardware Controller

(uSDHC)

I/O

Power Management

• 104 General-purpose input/output pins (GPIO)

• Bypass mode: 1.71 V to 3.6 V

Packages

• Buck DC-DC converter: 2.1 V to 3.6 V

• 176 VFBGA 9mm x 9mm x 0.86mm, 0.5mm

• Core voltage bypass: 1.14 V to 1.45 V direct supply to core,

pitch, -40 °C to 105 °C

bypassing internal regulator

• Independent VDDIO1 and VDDIO2 supply: 1.71 V to 3.6 V

• Independent VBAT(RTC): 1.71 V to 3.6 V

Related resources

Type

Description

Selector Guide

The NXP Solution Advisor is a web-based tool that features interactive application wizards and a

dynamic product selector.

Reference Manual

The Reference Manual contains a comprehensive description of the structure and function

(operation) of a device.

Data Sheet

The Data Sheet includes electrical characteristics and signal connections.

Chip Errata

The chip mask set Errata provides additional or corrective information for a particular device mask

set.

Package drawing

Package dimensions are provided in package drawings.

2

NXP Semiconductors

K32L3A, Rev. 1, 09/2019

�Table of Contents

1 Ordering information............................................................. 5

2 Overview............................................................................... 5

2.1 System features............................................................. 6

2.1.1

Arm Cortex-M0+ core...................................... 7

2.1.2

Arm Cortex-M4 core........................................ 7

2.1.3

NVIC................................................................ 7

2.1.4

AWIC............................................................... 8

2.1.5

Memory............................................................9

2.1.6

Reset and boot................................................ 10

2.1.7

ROM bootloader.............................................. 12

2.1.8

Clock options................................................... 13

2.1.9

Security............................................................18

2.1.10 Power management........................................ 18

2.1.11 LLWU...............................................................24

2.1.12 Debug controller.............................................. 28

2.1.13 INTMUX........................................................... 28

2.1.14 FlexBus............................................................28

2.1.15 Watch dog....................................................... 29

2.1.16 EWM................................................................ 29

2.1.17 XRDC.............................................................. 30

2.1.18 MU................................................................... 31

2.1.19 SEMA42.......................................................... 31

2.1.20 TRGMUX......................................................... 32

2.2 Peripheral features........................................................ 33

2.2.1

MSMC..............................................................33

2.2.2

CRC................................................................. 33

2.2.3

LPDAC.............................................................34

2.2.4

eDMA and DMAMUX.......................................34

2.2.5

EMV SIM......................................................... 36

2.2.6

FlexIO.............................................................. 37

2.2.7

LPADC.............................................................37

2.2.8

LPCMP............................................................ 38

2.2.9

LPI2C...............................................................39

2.2.10 LPIT................................................................. 40

2.2.11 LPSPI.............................................................. 41

2.2.12 LPTMR............................................................ 42

2.2.13 LPUART.......................................................... 42

2.2.14 RTC................................................................. 43

2.2.15 I2S................................................................... 44

2.2.16 uSDHC............................................................ 44

2.2.17 TPM................................................................. 45

2.2.18 TRNG.............................................................. 46

2.2.19 USB................................................................. 46

2.2.20 VREF............................................................... 47

2.2.21 TSTMR............................................................ 47

2.2.22 CAU3............................................................... 48

2.3 Memory map.................................................................. 48

3 Pinouts.................................................................................. 51

3.1 K32 subfamily pinout..................................................... 51

3.2 Pin properties.................................................................59

K32L3A, Rev. 1, 09/2019

3.3 Module signal description Tables.................................. 69

3.3.1

Core modules.................................................. 69

3.3.2

System modules.............................................. 70

3.3.3

Memories and memory interfaces................... 71

3.3.4

Clock modules................................................. 72

3.3.5

Communication interfaces............................... 72

3.3.6

Analog............................................................. 79

3.3.7

Human-machine interfaces (HMI)....................79

3.3.8

Timer modules................................................. 80

3.3.9

Security modules............................................. 82

3.4 Pinouts diagram............................................................. 82

3.5 Package dimensions......................................................83

4 Electrical characteristics........................................................84

4.1 Terminology and guidelines........................................... 84

4.1.1

Definitions........................................................ 85

4.1.2

Examples......................................................... 85

4.1.3

Typical-value conditions.................................. 86

4.1.4

Relationship between ratings and operating

requirements....................................................86

4.1.5

Guidelines for ratings and operating

requirements....................................................87

4.2 Ratings...........................................................................87

4.2.1

Thermal handling ratings................................. 87

4.2.2

Moisture handling ratings................................ 88

4.2.3

ESD handling ratings....................................... 88

4.2.4

Voltage and current operating ratings............. 88

4.3 General.......................................................................... 89

4.3.1

AC electrical characteristics............................ 89

4.3.2

Nonswitching electrical specifications............. 90

4.3.3

Switching specifications...................................108

4.3.4

Thermal specifications..................................... 111

4.4 Peripheral operating requirements and behaviors......... 112

4.4.1

Core modules.................................................. 112

4.4.2

4.4.3

4.4.4

4.4.5

4.4.6

4.4.7

4.4.8

4.4.9

System modules.............................................. 116

Clock modules................................................. 117

Memories and memory interfaces................... 120

Security and integrity modules........................ 126

Analog............................................................. 126

Timers..............................................................137

Communication interfaces............................... 137

DC-DC Converter Recommended Electrical

Characteristics................................................. 153

5 Design considerations...........................................................154

5.1 Hardware design considerations................................... 154

5.1.1

Printed circuit board recommendations........... 154

5.1.2

Power delivery system.....................................154

5.1.3

Analog design.................................................. 155

5.1.4

Digital design................................................... 156

5.1.5

Crystal oscillator.............................................. 159

5.2 Software considerations................................................ 159

3

NXP Semiconductors

�6 Part identification.....................................................................160

6.1 Part number format..........................................................160

4

NXP Semiconductors

7 Revision History...................................................................... 160

K32L3A, Rev. 1, 09/2019

�Ordering information

1 Ordering information

The following table summarizes the part numbers of the devices covered by this

document.

Table 1. Ordering information

Product

Part Number

K32L3A60VPJ1AT

Memory

Marking

K32L3A60VPJ1AT

Flash

(MB)

1.25

Package

SRAM (KB) Pin Count

384

176

Package

VFBGA

2 Overview

The following figure shows the system diagram of this device

K32L3A, Rev. 1, 09/2019

5

NXP Semiconductors

�Overview

LPCMP1

PORTE

SRAM

128 KB

w/ 6-bit DAC

TRGMUX1

LPSPI3

LPIT1

4CH

LLWU1

LPI2C3

LPTPM3

WDOG1

PCC1

LPUART3

TSTMR1

TRNG

LPTMR2

GPIO

S0

RAMC

AIPS1

S1

S2

AXBS1

M0

Cortex M0+

IOPORT

MPU

NVIC

AWIC1

BP/WP

SysTick

DV/SQ

I/D Cache

(4 KB)

AHB-AP

CM0+ I/D Flash

MDM

M1

S1

S3

ROMC

FlexBus

ROM

48 KB

SRAM

256 KB

M0

MPU

DSP

NVIC

FPB

SysTick

ITM

AWIC0

DWT

SCS

DAP-AP

ETM

CTI

TPIU

RDC

xRDC

Core

Regulator

MU

MSMC

SMC0 SMC1

IO

Regulator

TRGMUX0

FlexIO

32 CH

I2S

LLWU0

VBAT Register

File 32B

RTC

w/ Tamper Pin

System Register

File 32B

DMAMUX0

64 CH

DMA0 16CH

M2

AXBS0

SPM

SEMA42

(72 MHz –HSRun, 48 MHz –Run)

PCC0

48/52/56/60 MHz

CTI

Cortex M4+FPU

I/D Cache

(4 KB)

FIRC

LPFLL

Multi_Core Unit

BUS

Interconnect

SCG

SIRC

2/8 MHz

1 MB

RAMC

Clock

RTC OSC

32 kHz

MTB

CM4F I/D Flash

S0

M3

DMAMUX1

32 CH

256 KB

SWJ-DP

S3

DMA1

8 CH

CAU3

(72 MHz –HSRun, 48 MHz –Run)

SCB

M1

M2

DCDC

USB

Regulator

USB2.0 Device

SDHC

w/ LS/FS PHY

M3

M5

S4

USB SRAM

2 KB

M4

S2

CRC

LPADC

12 Bit

GPIO

LPI2C0~2

LPIT0

4CH

EWM

LPDAC

LPDAC

12-bit

12

Bit

PORTA~D

LPSPI0~2

LPTPM0~2

WDOG0

LPDAC

VREF

12-bit

1.2/2.1V

LPUART0~2

LPTMR0~1

EMVSIM

TSTMR0

AIPS

LPDAC

LPCMP0

w/12-bit

6-bit DAC

Note: When a core needs access the other AXBS domain resources, the corresponding MUx_CCR[CLKE] bit must be set. AXBS keeps active even if another core enters low power mode (and CPO).

Figure 1. System diagram

The crossbar switch connects bus masters and slaves using a crossbar switch structure.

This structure allows up to four bus masters to access different bus slaves

simultaneously for AXBS1 and up to six for AXBS0, while providing arbitration

among the bus masters when they access the same slave.

6

NXP Semiconductors

K32L3A, Rev. 1, 09/2019

�Overview

2.1 System features

The following sections describe the high-level system features.

2.1.1 Arm Cortex-M0+ core

The enhanced Arm Cortex M0+ is the member of the Cortex-M series of processors

targeting microcontroller cores focused on very cost sensitive, low power

applications. It has a single 32-bit AMBA AHB-Lite interface and includes an NVIC

component. It also has hardware debug functionality including support for simple

program trace capability. The processor supports the Arm v6-M instruction set

(Thumb) architecture including all but three 16-bit Thumb opcodes (52 total) plus

seven 32-bit instructions. It is upward compatible with other Cortex-M profile

processors.

This device supports hardware divider (MMDVSQ) when CM0+ core is working.

2.1.2 Arm Cortex-M4 core

The Cortex M4 processor is based on the Armv7 Architecture and Thumb®-2 ISA

and is upward compatible with the Cortex M3, Cortex M1, and Cortex M0

architectures. Cortex M4 improvements include an Armv7 Thumb-2 DSP (ported

from the Armv7-A/R profile architectures) providing 32-bit instructions with SIMD

(single instruction multiple data) DSP style multiply-accumulates and saturating

arithmetic.

2.1.3 NVIC

The Armv7-M exception model and nested-vectored interrupt controller (NVIC)

implement a relocatable vector table supporting many external interrupts, a single

non-maskable interrupt (NMI), and priority levels.

The NVIC replaces shadow registers with equivalent system and simplified

programmability. The NVIC contains the address of the function to execute for a

particular handler. The address is fetched via the instruction port allowing parallel

register stacking and look-up. The first sixteen entries are allocated to Arm internal

sources with the others mapping to MCU-defined interrupts.

K32L3A, Rev. 1, 09/2019

7

NXP Semiconductors

�Overview

2.1.4 AWIC

The primary function of the Asynchronous Wake-up Interrupt Controller (AWIC) is to

detect asynchronous wake-up events in stop modes and signal to clock control logic to

resume system clocking. After clock restart, the NVIC observes the pending interrupt

and performs the normal interrupt or event processing.

The device uses the following internal and external inputs to the AWIC module.

AWIC0 is AWIC in CM4F domain while AWIC1 is AWIC in CM0+ domain.

Table 2. AWIC0 Stop and VLPS wakeup sources

Wake-up source

Description

System resets

All available system resets sources are describted in SMC0

under MSMC chapter

SPM

All available interrupt in SPM, such as low/high voltage

detect interrupt, low voltage detect/warnning interrupt, and

etc.

Pin

PTA, PTB, PTC, PTD, PTE pin interrupts

LPUART0~3

Functional when using clock source which is active in Stop

and VLPS modes

LPI2C0~3

Address match wakeup

LPSPI0~3

Slave mode interrupt

I2S

Functional when using an external bit clock or external

master clock

EMVSIM

Any enabled interrupt can be a source as long as the module

remains clocked.

USB Controller

Wakeup

Secure Digital Hardware Controller (SDHC)

Wakeup

FlexIO

Functional when using clock source which is active in Stop

and VLPS modes

LPTMR0~2

Functional when using clock source which is active in Stop,

VLPS and LLS/VLLS modes

TPM0~3

Functional when using clock source which is active in Stop

and VLPS modes

RTC

Functional in Stop, VLPS, LLS and VLLSx modes

LPIT0/1

Any enabled interrupt can be a source as long as the module

remains clocked.

Tamper detect

Interrupt

NMI

NMI is routed to CM4F or CM0+ automatically, only boot

core has NMI

LPCMP0/1

Interrupt in normal or trigger mode

LPDAC

Any enabled interrupt can be a source as long as the module

remains clocked.

Table continues on the next page...

8

NXP Semiconductors

K32L3A, Rev. 1, 09/2019

�Overview

Table 2. AWIC0 Stop and VLPS wakeup sources (continued)

Wake-up source

Description

LPADC

The LPADC is functional when using internal clock source

LLWU0

Any enabled interrupt can be a source as long as the module

remains clocked.

MUA

Any enabled interrupt can be a source as long as the module

remains clocked.

WDOG0

Watchdog0 Interrupt

Table 3. AWIC1 Stop and VLPS wakeup sources

Wake-up source

Description

System resets

All available system resets sources are describted in SMC1

under MSMC chapter

PortE

PTE pin interrupts

LPUART3

Functional when using clock source which is active in Stop

and VLPS modes

LPI2C03

Address match wakeup

LPSPI3

Any enabled interrupt can be a source as long as the

module remains clocked.

LPTMR2

Functional when using clock source which is active in Stop,

VLPS and LLS/VLLS modes

TPM3

Functional when using clock source which is active in Stop

and VLPS modes

RTC

Functional in Stop,VLPS,LLS and VLLSx modes

LPIT1

Any enabled interrupt can be a source as long as the

module remains clocked.

NMI

NMI is routed to CM4F or CM0+ automatically, only boot

core has NMI

LPCMP1

Interrupt in normal or trigger mode

TRNG

TRNG has no stop wakeup capability

LLWU1

Any enabled interrupt can be a source as long as the

module remains clocked.

MUB

Any enabled interrupt can be a source as long as the

module remains clocked.

WDOG1

Watchdog1 Interrupt

INTMUX0~7

All other wakeup sources availabe in AWIC0 can be

selected through INTMUXn. Please refer to the INTMUXn

description.

2.1.5 Memory

This device has the following features:

K32L3A, Rev. 1, 09/2019

9

NXP Semiconductors

�Overview

• 384 KB of embedded RAM accessible (read/write) at CPU clock speed with 0 wait

states.

• 4 KB of embedded RAM used for flash programming acceleration RAM

• The non-volatile memory is divided into two arrays

• 2 blocks of program flash, providing 1 MB consisting of 4 KB sectors for CM4

• 1 block of program flash, providing 256 KB consisting of 2 KB sectors for

CM0+

The primary program flash memory contains an IFR space that stores default

protection settings and security information.

The protection setting can protect 64 regions of the primary program flash memory

and 16 regions of the secondary program flash memory from unintended erase or

program operations.

The security circuitry prevents unauthorized access to RAM or flash contents from

debug port.

• System register file

This device contains a 32-byte register file that is powered in all power modes.

Also, it retains contents during low power modes and is reset only during a poweron reset.

• VBAT register file

This device includes a 32-byte register file. The register file is powered by the

VBAT domain and is powered in all modes as long as power is applied to the

VBAT supply.

The VBAT register file is only reset during the VBAT Power-on Reset

(PORVBAT) sequence.

2.1.6 Reset and boot

The following table lists all the reset sources supported by this device.

NOTE

In the following table, Y means the specific module, except

for the registers, bits or conditions mentioned in the footnote,

is reset by the corresponding Reset source. N means the

10

NXP Semiconductors

K32L3A, Rev. 1, 09/2019

�Overview

specific module is not reset by the corresponding Reset

source.

Table 4. Reset source

Reset

sources

Descriptions

Modules

SPM

SIM

MSM

C

LLWU

Reset

pin is

negated

RTC1

LPTMR

Others

POR reset

Power-on reset (POR)

Y

Y

Y

Y

Y

N

Y

Y

System reset

Low leakage wakeup (LLWU)

reset

N2

Y3

N

N

Y4

N

N

Y5

External pin reset (RESET_b)

N2

Y3

Y6

Y

Y

N

N

Y

Computer operating properly

(COP) watchdog reset

N2

Y3

Y6

Y

Y

N

N

Y

Stop mode acknowledge error

(SACKERR)

N2

Y3

Y6

Y

Y

N

N

Y

Software reset (SW)

N2

Y3

Y6

Y

Y

N

N

Y

Lockup reset (LOCKUP)

N2

Y3

Y6

Y

Y

N

N

Y

MDM DAP system reset

N2

Y3

Y6

Y

Y

N

N

Y

N

Y3

Y6

Y

Y

N

N

Y

Debug reset

Debug reset

1. The VBAT POR asserts on a VBAT POR reset source. It affects only the modules withinthe VBAT power domain: RTC

and VBAT Register File. These modules are not affected by the other reset types.

2. Except SPM_CORESC[ACKISO], SPM_CORESC[VSEL] and SPM_CORESC[VSEL_OFFSET]

3. The SIM_SDID, SIM_RREPCR1, SIM_RREPCR2, SIM_RREPSR1, SIM_RREPSR2, SIM_FCFG2, SIM_UIDH,

SIM_UIDM, SIM_UIDL, registers are not affected by the reset to exit from VLLS2 or VLLS3 modes.

4. Only if RESET_b is used to wake from VLLS mode.

5. The FTFE, LPCAC and LPLMEM modules cannot be reset when chip is waken up from VLLS2 or VLLS3 modes by

LLWU.

6. Except SMCx_PMCTRL and SMCx_PMSTAT of the MSMC.

The CM0+ core adds support for a programmable Vector Table Offset Register

(VTOR) to relocate the exception vector table after reset. This device supports booting

from:

• internal flash

• ROM

The Flash Option (FOPT) register in the Flash Memory module (FTFE_FOPT) allows

the user to customize the operation of the MCU at boot time. The register contains

read-only bits that are loaded from the NVM's option byte in the IFR spaces. Below is

boot flow chart for this device.

K32L3A, Rev. 1, 09/2019

11

NXP Semiconductors

�Overview

START

Boot Sequence

Core option is

read and stored in

RESET==0

SCG is enabled

FOPT[BOOTCORESEL]

Required clocks

are enabled

Enable selected

boot core

Release device

reset

Flash controller is

initialized

complete flash

initialization

Set up

Stack Pointer

Flash option is read

and stored in

FTFE_FOPT

Release

RESET

Set up

Program Counter

Enable boot

core clock

Set up

Link Register

Is

BOOT_MODE/

BOOT_CLK

==11?

Yes

No

Modify clock

divider

Yes

Is

NMI = 0

?

FOPT

[BOOT_PIN]

==0?

No

No

Yes

10/11 FTFE_FOPT

[BOOT_SRC]

==?

00

Processor boot from

ROM

Processor boots

from Flash

Figure 2. Boot sequence

Blank chips default to boot from ROM and remap the vector table to ROM base

address, otherwise, it remaps to flash address.

If booting from ROM, the device executes in boot loader mode.

2.1.7 ROM bootloader

The Kinetis bootloader is the program residing in the on-chip read-only memory

(ROM) of a Kinetis microcontroller device. There is hardware logic in place at boot

time that either starts execution of an embedded image available on the internal flash

memory, or starts the execution of the Kinetis Bootloader from on-chip ROM.

Features supported by the Kinetis Bootloader in Kinetis ROM:

• Supports USB, LPI2C, LPSPI, and LPUART peripheral interfaces

12

NXP Semiconductors

K32L3A, Rev. 1, 09/2019

�Overview

•

•

•

•

•

•

•

•

•

•

•

•

•

Automatic detection of the active peripheral

Ability to disable any peripheral

LPUART peripheral implements autobaud

Common packet-based protocol for all peripherals

Packet error detection and retransmission

Flash-resident configuration options

Fully supports internal flash security, including ability to mass erase or unlock

security via the backdoor key

Protection of RAM used by the bootloader while it is running

Provides command to read properties of the device, such as flash and RAM size

Multiple options for executing the bootloader either at system start-up or under

application control at runtime

Supports internal flash

Supports encrypted image download

ROM boots from either M4 (Default) or M0+ by configuring to FOPT IFR

(record Index 0x84)

2.1.8 Clock options

This chip provides a wide range of sources to generate the internal clocks. These

sources include internal reference clock (IRC) oscillators, external oscillators, external

clock sources, ceramic resonators, and frequency-locked loop (FLL). These sources

can be configured to provide the required performance and optimize the power

consumption.

The IRC oscillators include the fast internal reference clock (FIRC) oscillator, the

slow internal reference clock (SIRC) oscillator, and the low power oscillator (LPO).

The fast internal resistor capacitor (FIRC) oscillator generates a clock ranging

between 48 MHz and 60 MHz.

The slow internal resistor capacitor (SIRC) oscillator generates clock at either 8 MHz

or 2 MHz. It can serve as the low power, low speed system clock under very low

power run (VLPR) mode or very low power wait (VLPW) mode. It can also be

provided as clock source for other on-chip modules. The SIRC cannot be used in any

VLLS modes.

The LPO generates a 1 kHz clock and default to be off in VLLS0 but can be enabled

by configuring bits of SPM_CORELPCNFG[LPOEN] and

SPM_CORELPCNFG[ALLREFEN].

K32L3A, Rev. 1, 09/2019

13

NXP Semiconductors

�Overview

The frequency-locked loop (FLL) can generate a clock with the frequency of 48 MHz

or 72 MHz without the need of a reference (a reference clock may only be needed to

trim this clock). The FLL can be used as the system clock or clock source for other onchip modules.

The RTC oscillator supports low speed crystals (32.768 kHz) and can also support

external clock on the EXTAL32 pin for use with the RTC.

For more details on the clock operations and configurations, see Reference Manual.

Flash

11

Fast

IRC

48~60MHz

10

01

PREDIV

LPFLL

48~72MHz

CM4F

SRAM

0101

0100

00

SCG_LPFLLTCFG[TRIMDIV]

Slow

IRC

ROM

SCG

SCG_LPFLLTCFG[TRIMSRC]

0011

DIVCORE

8MHz/2MHz

CORE_CLK

CG

0010

CORE_CLK

CG

Other

CG

PCC0

DIVSLOW

LPFLLDIV1

LPFLLDIV2

LPFLLDIV3

SIRC_CLK

SIRCDIV1

SIRCDIV2

FIRC_CLK

SIRCDIV3

FIRCDIV1

FIRCDIV2

FIRCDIV3

SYS_CLK

CG

CG

DIVEXT

LPFLL_CLK

PLAT_CLK (Gated)

PLAT_CLK

CG

SCG_xCCR[SCS]

(x=R, V, H)

DIVBUS

BUS_CLK(Gated)

PCC0_xxx[CGC]

SLOW_CLK(Gated)

BUS_CLK

LPFLL_DIV1_CLK

LPFLL_DIV2_CLK

LPFLL_DIV3_CLK

SIRC_DIV1_CLK

LPFLL_DIVx_CLK

SIRC_DIVx_CLK

FIRC_DIVx_CLK

SIRC_DIV2_CLK

SIRC_DIV3_CLK

Peripherals

FIRC_DIV1_CLK

FIRC_DIV2_CLK

FIRC_DIV3_CLK

PCC0_xxx[PCS]

SCG_CLKOUTCNFG

[CLKOUTSEL]

SYS_CLK (Gated)

SLOW_CLK

0100 0000 0001 0011 0010 0101 Other

*

SCG CLKOUT

SPM

LPO1kHz

CLKOUT/FB_CLKOUT*

LPO_CLK

CM0+

RTC

EXTAL32

RTC OSC

XTAL32

SRAM

RTC_CLKOUT

RTCOSC_CLK

PCC1

SYS_CLK (Gated)

PLAT_CLK (Gated)

PCC1_xxx[CGC]

BUS_CLK(Gated)

SLOW_CLK(Gated)

Peripherals

LPFLL_DIVx_CLK

SIRC_DIVx_CLK

FIRC_DIVx_CLK

* FB_CLKOUT can be from DIVEXT divider only when SCG_CLKOUTCFNG[CLKOUTSEL]=0000 and

PCC_FLEXBUS[CGC]=1.

* One clock divider in PCC0 available for LPADC0 conversion clock.

PCC1_xxx[PCS]

Figure 3. Generic clocking architecture diagram

In order to provide flexibility, many peripherals can select from multiple clock sources

for operation. This enables the peripheral to select a clock that will always be available

during operation in various operational modes.

The following table summarizes the clocks associated with each module.

14

NXP Semiconductors

K32L3A, Rev. 1, 09/2019

�Overview

Table 5. Clock assignments

Module Name

Bus Interface

Clock

PCC Clock Gate

Peripherial

Functional Clock

Clock Domain1

I/O Interface

Clocks

Core Modules

Arm Cortex-M0+

Core

CORE_CLK

—

—

SCG

—

Arm Cortex-M4

Core

CORE_CLK

—

—

SCG

—

CM0+ TRACE

SYS_CLK

Yes

SYS_CLK

SCG

—

CM4F TRACE

SYS_CLK

Yes

SYS_CLK,

PCC0

SIRC_DIV1_CLK,

FIRC_DIV1_CLK,

LPFLL_DIV1_CLK

TRACE_CLK_OU

T

JTAG

NA

—

TCK

—

JTAG_TCLK

SWCK

SCG2

SWD_CLK

SWD

PLAT_CLK

—

Platform Modules

CM0+ Crossbar

PLAT_CLK

—

NA

SCG

—

CM4F Crossbar

PLAT_CLK

—

NA

SCG

—

xRDC

PLAT_CLK

Yes

—

PCC0,PCC1

—

SEMA42

PLAT_CLK

Yes

—

PCC0,PCC1

—

System Modules

MSMC_SMC0

SLOW_CLK

Yes

—

PCC0

—

MSMC_SMC1

SLOW_CLK

Yes

—

PCC1

—

INTMUX

BUS_CLK

—

SCG

—

DMA0

SYS_CLK

Yes

—

PCC0

—

DMA1

SYS_CLK

Yes

—

PCC1

—

DMA MUX0

BUS CLK

Yes

—

PCC0

—

DMA MUX1

BUS CLK

Yes

—

PCC1

—

LPO clock.

PCC02

—

LPO

SCG2

—

—

—

EWM

LLWU0

SLOW_CLK

SLOW_CLK

Yes

Yes

LLWU1

SLOW_CLK

Yes

LPO

SCG2

MU

SLOW_CLK

Yes

—

PCC0,PCC1

SPM

SLOW_CLK

Yes

—

TRGMUX0

SLOW_CLK

Yes

—

SCG

—

TRGMUX1

SLOW_CLK

Yes

—

SCG

—

—

—

WDOG0

SLOW_CLK

Yes

LIRC, or LPO

clock.

PCC02

WDOG1

SLOW_CLK

Yes

LIRC, or LPO

clock.

PCC12

—

SCG

—

Memories

Flash Controller

(FMC)

PLAT_CLK

—

—

Table continues on the next page...

K32L3A, Rev. 1, 09/2019

15

NXP Semiconductors

�Overview

Table 5. Clock assignments (continued)

Module Name

Bus Interface

Clock

PCC Clock Gate

Peripherial

Functional Clock

Clock Domain1

I/O Interface

Clocks

Flash Memory

(FTFE)

SLOW_CLK

—

—

SCG

—

FlexBus

PLAT_CLK

Yes

—

PCC02

FB_CLKOUT/

CLKOUT

CM4F SRAM

PLAT_CLK

—

PLAT_CLK

SCG

—

CM0+ SRAM

PLAT_CLK

—

PLAT_CLK

SCG

—

CAU3

SYS_CLK

Yes

—

PCC1

—

CRC

BUS_CLK

Yes

—

PCC0

—

TRNG

BUS_CLK

Yes

—

PCC1

—

Security and Integrity

Timers

LPIT0

SLOW_CLK

Yes

SIRC_DIV3_CLK, PCC0

FIRC_DIV3_CLK,

LPFLL_DIV3_CLK

—

LPIT1

SLOW_CLK

Yes

SIRC_DIV3_CLK, PCC1

FIRC_DIV3_CLK,

LPFLL_DIV3_CLK

—

RTC

SLOW_CLK

Yes

RTCOSC, LPO

SCG2

RTC_CLKOUT

—

—

LPTMR0/1

SLOW_CLK

—

SIRC_DIV3_CLK,

LPO, RTCOSC

SCG2

LPTMR2

SLOW_CLK

—

SIRC_DIV3_CLK,

LPO, RTCOSC

SCG2

LPTPM0~2

BUS_CLK

Yes

SIRC_DIV2_CLK, PCC02

FIRC_DIV2_CLK,

LPFLL_DIV2_CLK

TPM0~32_CLKIN

LPTPM3

BUS_CLK

Yes

SIRC_DIV2_CLK, PCC12

FIRC_DIV2_CLK,

LPFLL_DIV2_CLK

TPM3_CLKIN

TSTMR

SLOW_CLK

Auto

SIRC_1MHZ_CLK SCG

—

Communication Interfaces

EMVSIM

BUS_CLK

Yes

SIRC_DIV2_CLK, PCC0

FIRC_DIV2_CLK,

LPFLL_DIV2_CLK

, RTCOSC

EMVSIM_CLK

FlexIO

BUS_CLK

Yes

SIRC_DIV2_CLK, PCC0

FIRC_DIV2_CLK,

LPFLL_DIV2_CLK

—

LPI2C0~2

BUS_CLK

Yes

SIRC_DIV2_CLK, PCC0

FIRC_DIV2_CLK,

LPFLL_DIV2_CLK

LPI2C0~2_SCL

LPI2C3

BUS_CLK

Yes

SIRC_DIV2_CLK, PCC1

FIRC_DIV2_CLK,

LPFLL_DIV2_CLK

LPI2C3_SCL

Table continues on the next page...

16

NXP Semiconductors

K32L3A, Rev. 1, 09/2019

�Overview

Table 5. Clock assignments (continued)

Module Name

Bus Interface

Clock

PCC Clock Gate

Peripherial

Functional Clock

Clock Domain1

I/O Interface

Clocks

I2S

BUS_CLK

Yes

SIRC_DIV2_CLK, PCC03

FIRC_DIV2_CLK,

LPFLL_DIV2_CLK

, SAI_MCLK

SAI_TX_BCLK,

SAI_RX_BCLK,

SAI_MCLK

uSDHC

SYS_CLK

Yes

SIRC_DIV1_CLK, PCC0

FIRC_DIV1_CLK,

LPFLL_DIV1_CLK

, SDHC_DCLK

SDHC_DCLK

LPSPI0~2

BUS_CLK

Yes

SIRC_DIV2_CLK, PCC0

FIRC_DIV2_CLK,

LPFLL_DIV2_CLK

LPSPI0~2_SCK

LPSPI3

BUS_CLK

Yes

SIRC_DIV2_CLK, PCC1

FIRC_DIV2_CLK,

LPFLL_DIV2_CLK

LPSPI3_SCK

LPUART0~2

BUS_CLK

Yes

SIRC_DIV2_CLK, PCC0

FIRC_DIV2_CLK,

LPFLL_DIV2_CLK

—

LPUART3

BUS_CLK

Yes

SIRC_DIV2_CLK, PCC1

FIRC_DIV2_CLK,

LPFLL_DIV2_CLK

—

USB

SYS_CLK

Yes

SIRC_DIV1_CLK, PCC02

FIRC_DIV1_CLK,

LPFLL_DIV1_CLK

—

USB SRAM

SIRC_DIV1_CLK, Yes

FIRC_DIV1_CLK,

LPFLL_DIV1_CLK

, SYS_CLK

PCC02

—

—

Human-Machine Interfaces

PORTA~D

SLOW_CLK

Yes

SLOW_CLK, LPO PCC0

—

PORTE

SLOW_CLK

Yes

SLOW_CLK, LPO PCC1

—

RGPIOA~D

PLAT_CLK

Yes

—

PCC0

—

RGPIOE

PLAT_CLK

Yes

—

PCC1

—

Analog

LPADC

BUS_CLK

Yes

SIRC_DIV2_CLK, PCC0

FIRC_DIV2_CLK,

LPFLL_DIV2_CLK

, LPADC Internal

Clock.

—

LPCMP0

SLOW_CLK

—

—

SCG

—

LPCMP1

SLOW_CLK

—

—

SCG

—

LPDAC

BUS_CLK

Yes

—

PCC0

—

VREF

SLOW_CLK

Yes

—

PCC0

—

1. PPC0 controls CM4F domain,and PPC1 controls CM0+ domain.

2. It is bus interface clock domain.

3. SAI_MCLK doesn't blong to PCC clock domain.

K32L3A, Rev. 1, 09/2019

17

NXP Semiconductors

�Overview

2.1.9 Security

Security state can be enabled via programming Flash IFR SEC0 (index 0x80). After

enabling device security, the SWJ (SWD and JTAG) port cannot access the memory

resources of the MCU, and ROM boot loader is also limited to access flash and not

allowed to read out flash information via ROM boot loader commands.

Access interface

Secure state

Unsecure operation

SWJ (SWD and JTAG) port

Cannot access memory source by SWD The debugger can write 1 to the System

interface

Reset Request field and Flash Mass

Erase in Progress field of the MDM-AP

Control register to trigger a mass erase

(Erase All Blocks Unsecure) command

ROM boot loader Interface (LPUART/

LPI2C/LPSPI/USB)

Limit access to the flash, cannot read

out flash content

Send “FlashEraseAllUnsecure"

command or attempt to unlock flash

security using the backdoor key

This device features 80-bit unique identification number, which is programmed in

factory and loaded to SIM register after power-on reset.

2.1.10 Power management

These devices include on-chip LDO regulators and an on-chip DCDC converter to

condition the main power supply voltage and allow for flexibility in power

configurations. Three operating modes are supported: Bypass, LDO only, and DCDC

(buck mode).

The SPM provides Stop (STOP), Very Low Power Stop (VLPS), Low Leakage Stop

(LLS), and Very Low Leakage Stop (VLLS) configurations in Arm’s Deep Sleep

operational mode. In these modes, the MCU core and most of the peripherals are

disabled. Depending on the requirements of the application, different portions of the

analog, logic, and memory can be retained or disabled to conserve power.

The Nested Vectored Interrupt Controller (NVIC), the Asynchronous Wake-up

Interrupt Controller (AWIC), and the Low Leakage Wake-Up Controller (LLWU) are

used to wake up the MCU from low power states. The NVIC is used to wake up the

MCU core from WAIT and VLPW modes. The AWIC is used to wake up the MCU

core from STOP and VLPS modes. The LLWU is used to wake up the MCU core from

LLS and VLLS modes.

18

NXP Semiconductors

K32L3A, Rev. 1, 09/2019

�Overview

For additional information regarding operational modes, power management, the

NVIC, AWIC, or the LLWU, please refer to the Reference Manual.

The following table shows module operations in different low power modes:

Table 7. Module operation in low power modes

Modules

VLPR

VLPW

STOP

VLPS

LLS

VLLS2/3

VLLS0/1

Core modules

NVIC

FF

FF

SR

SR

SR

OFF

OFF

System modules

MSMC

FF

FF

FF

FF

SR/FF1

OFF/FF2

OFF/FF2

LLWUx

FF

FF

FF

FF

FF

FF

FF

Core regulator (1.2

V)

Optional3

Optional3

Optional3

Optional3

Optional3

Optional3

Optional3

AUXREG 1.8 V

Optional3

Optional3

Optional3

Optional3

Optional3

Optional3

Optional3

HVD/LVD

Optional4

Optional4

Optional4

Optional4

Optional4

Optional4

Optional4

POR (Brown-Out)

FF

FF

FF

FF

FF

FF

Optional5

DMA

FF

FF

Async

Async

SR

OFF

OFF

Watchdog

FF

FF

Optional on

with

available

clock source

Optional on SR

with

available

clock source

OFF

OFF

FF

FF

Optional6

Clocks

1 kHz LPO

FF

FF

FF

FF

SCG

8 MHz SIRC 8 MHz SIRC static –

static – SIRC static

SIRC, FIRC, optional

LPFLL

optional

OFF

OFF

Core clock

FF

OFF

OFF

OFF

OFF

OFF

OFF

Plat clock

FF

FF

OFF

OFF

OFF

OFF

OFF

Bus clock

FF

FF

OFF

OFF

OFF

OFF

OFF

Slow clock

FF

FF

OFF

OFF

OFF

OFF

OFF

Memory

Flash

1 MHz No

program

LP

LP

LP

SR

The registers OFF

are retained

SRAM

LP

LP

SR

Optional7

Optional7

Optional7

OFF

LPLMEM (Cache)

FF

FF

SR

SR

Optional

retention

Optional7

OFF

LPCAC (Cache)

FF

FF

SR

SR

Optional

retention

Optional7

OFF

System Register

File

FF

FF

FF

FF

FF

FF

FF

VBAT Register File

Optional8

Optional8

Optional8

Optional8

Optional8

Optional8

Optional8

Communication Interface

Table continues on the next page...

K32L3A, Rev. 1, 09/2019

19

NXP Semiconductors

�Overview

Table 7. Module operation in low power modes (continued)

Modules

VLPR

VLPW

STOP

VLPS

LLS

VLLS2/3

VLLS0/1

USB

static

static

static

static

static

OFF

OFF

USB Reg

Optional

Optional

Optional

Optional

Optional

Optional

Optional

LPUARTx

1 Mbit/s

1 Mbit/s

Async

Async

static

OFF

OFF

LPSPIx

Master 2

Mbit/s

Master 2

Mbit/s

OFF

OFF

Slave 1

Mbit/s

Slave 1

Mbit/s

Static, slave Static, slave static

mode

mode

receive

receive

LPI2Cx

1 Mbit/s

1 Mbit/s

Async

Async

static

OFF

OFF

I2S

FF

FF

Async

Async

static

OFF

OFF

EMVSIM

FF

FF

Static, card

detect

wakeup

Static, card

detect

wakeup

static

OFF

OFF

Timer modules

LPTPMx

FF

FF

Async

Async

static

OFF

OFF

LPIT

FF

FF

Async

Async

static

OFF

OFF

LPTMRx

FF

FF

Async

Async

Async

FF

FF

Optional8

RTC

FF

FF

Async

Async

Async

Optional8

TSTMR

FF

FF

static

static

static

OFF

OFF

Security modules

CAU3

FF

FF

static

static

static

OFF

OFF

CRC

FF

FF

static

static

static

OFF

OFF

Optional8

Digital Tamper

FF

FF

Async

Async

Async

Optional8

TRNG

FF

FF

static

static

static

OFF

OFF

OFF

OFF

Analog

LPADC

FF

FF

LPADC

LPADC

SR

internal clock internal clock

LPCMP0

FF

FF

FF

FF or Low

power Nano

mode

Compare

FF or Low

FF

power Nano

mode

Compare

FF9

LPCMP1

FF

FF

FF

FF or Low

power Nano

mode

Compare

FF or Low

Optional10

power Nano

mode

Compare

Optional10

6-bit DAC

FF

FF

static

static

static

OFF

OFF

12-bit LPDAC

FF

FF

static

static

static

OFF

OFF

VREF

FF

FF

static

static

static

OFF

OFF

HMI

GPIO

FF

FF

Static output, Static output, Static, pins

wake up

wake up

latched

input

input

OFF, pins

latched

OFF, pins

latched

FlexIO

FF

FF

Async

OFF

OFF

20

NXP Semiconductors

Async

SR

K32L3A, Rev. 1, 09/2019

�Overview

1. SR for reset related control and FF for power model related control

2. OFF for reset related control and FF for power model related control

3. It depends on MCU arbitration and SPM LPSEL/BGEN bit.

4. It depends on MCU arbitration and SPM LVDEN/BGEN/ALLREFN bit

5. It depends on MCU arbitration and SPM POREN bit.

6. It depends on MCU arbitration and SPM LPOEN/ALLREFN bit.

7. It depends on the configurations, see the next table for details.

8. Requires the VBAT supply to be properly powered.

9. It depends on SPM_CORELPCNFG[ALLREFEN] =1.

10. It depends on SPM_CORESC[VDDIOOVRIDE] = 1, SPM_CORELPCNFG[ALLREFEN] =1, and VDDIO2.

The following tables list all power mode combinations and corresponding power

behaviors.

Table 8. MCU power mode combinations

CM4F power mode1

CM0+ power mode2

Max CM4F core

clock frequency

Max CM0+ core

clock frequency

MCU power mode3

RUN

RUN

48MHz

48MHz

RUN

RUN

HSRUN

72MHz

72MHz

HSRUN

RUN

VLPR

48MHz

48MHz

RUN

RUN

VLPW

48MHz

OFF

RUN

RUN

VLPS

48MHz

OFF

RUN

RUN

STOP/PSTOP

48MHz

OFF

RUN

RUN

LLS

48MHz

OFF

RUN

RUN

VLLS

48MHz

OFF

RUN

HSRUN

RUN

72MHz

72MHz

HSRUN

HSRUN

HSRUN

72MHz

72MHz

HSRUN

HSRUN

VLPR

72MHz

72MHz

HSRUN

HSRUN

VLPW

72MHz

OFF

HSRUN

HSRUN

VLPS

72MHz

OFF

HSRUN

HSRUN

STOP/PSTOP

72MHz

OFF

HSRUN

HSRUN

LLS

72MHz

OFF

HSRUN

HSRUN

VLLS

72MHz

OFF

HSRUN

VLPR

RUN

48MHz

48MHz

RUN

VLPR

HSRUN

72MHz

72MHz

HSRUN

VLPR

VLPR

8MHz

8MHz

VLP

VLPR

VLPW

8MHz

OFF

VLP

VLPR

VLPS

8MHz

OFF

VLP

VLPR

STOP/PSTOP

48MHz

OFF

RUN

VLPR

LLS

8MHz

OFF

VLP

VLPR

VLLS

8MHz

OFF

VLP

VLPW

RUN

OFF

48MHz

RUN

VLPW

HSRUN

OFF

72MHz

HSRUN

VLPW

VLPR

OFF

8MHz

VLP

Table continues on the next page...

K32L3A, Rev. 1, 09/2019

21

NXP Semiconductors

�Overview

Table 8. MCU power mode combinations (continued)

CM4F power mode1

CM0+ power mode2

Max CM4F core

clock frequency

Max CM0+ core

clock frequency

MCU power mode3

VLPW

VLPW

OFF

OFF

VLP

VLPW

VLPS

OFF

OFF

VLP

VLPW

STOP/PSTOP

OFF

OFF

RUN

VLPW

LLS

OFF

OFF

VLP

VLPW

VLLS

OFF

OFF

VLP

VLPS

RUN

OFF

48MHz

RUN

VLPS

HSRUN

OFF

72MHz

HSRUN

VLPS

VLPR

OFF

8MHz

VLP

VLPS

VLPW

OFF

OFF

VLP

VLPS

VLPS

OFF

OFF

VLP

VLPS

STOP/PSTOP

OFF

OFF

RUN

VLPS

LLS

OFF

OFF

VLP

VLPS

VLLS

OFF

OFF

VLP

STOP/PSTOP

RUN

OFF

48MHz

RUN

STOP/PSTOP

HSRUN

OFF

72MHz

HSRUN

STOP/PSTOP

VLPR

OFF

8MHz

RUN

STOP/PSTOP

VLPW

OFF

OFF

RUN

STOP/PSTOP

VLPS

OFF

OFF

RUN

STOP/PSTOP

STOP/PSTOP

OFF

OFF

RUN

STOP/PSTOP

LLS

OFF

OFF

RUN

STOP/PSTOP

VLLS

OFF

OFF

RUN

LLS

RUN

OFF

48MHz

RUN

LLS

HSRUN

OFF

72MHz

HSRUN

LLS

VLPR

OFF

8MHz

VLP

LLS

VLPW

OFF

OFF

VLP

LLS

VLPS

OFF

OFF

VLP

LLS

STOP/PSTOP

OFF

OFF

RUN

LLS

LLS

OFF

OFF

LLS

LLS

VLLS

OFF

OFF

LLS

VLLS

RUN

OFF

48MHz

RUN

VLLS

HSRUN

OFF

72MHz

HSRUN

VLLS

VLPR

OFF

8MHz

VLP

VLLS

VLPW

OFF

OFF

VLP

VLLS

VLPS

OFF

OFF

VLP

VLLS

STOP/PSTOP

OFF

OFF

RUN

VLLS

LLS

OFF

OFF

LLS

VLLS

VLLS

OFF

OFF

VLLS

22

NXP Semiconductors

K32L3A, Rev. 1, 09/2019

�Overview

1. It is configured by SMC0_PMCTRL register of MSMC.

2. It is configured by SMC1_PMCTRL register of MSMC.

3. It can be read out from SMCx_PMCSTAT register of MSMC. Please note the PMSTAT[7:0] bits in both

SMC0_PMCSTAT and SMC1_PMCSTAT registers refer to MCU power mode so their value are identical. The

STOPSTAT[31:24] bits in SMCx_PMCSTAT register reflect separate CM4F or CM0+ clock status, so can be different.

Table 9. Note

FF

Full functionality. In VLPR and VLPW, the system frequency is limited, but if a

module does not have a limitation in its functionality, it is still listed as FF.

Async

Fully functional with alternate clock source, provided the selected clock source

remains enabled

SR

Module state is retained but not functional.

LP

Module operates in a lower power state.

Off

Module is powered off and in reset state upon wake-up

The following table provides the modules that can wake MCU from low power

modes.

Modules

VLPW

STOP

VLPS

LLS

VLLS3

VLLS1

VLLS0

RTC

Y

Y

Y

Y1

Y1

Y1

Y2

LPTMRx

Y

Y

Y

Y1

Y1

Y1

Y3

LPTPMx

Y

Y

Y

N

N

N

N

LPITx

Y

Y

Y

N

N

N

N

LLWUx

Y

Y

Y

Y

Y

Y

Y

LPSPIx

Y

Y

Y

N

N

N

N

LPI2Cx

Y

Y

Y

N

N

N

N

FlexIO

Y

Y

Y

N

N

N

N

LPUARTx

Y

Y

Y

N

N

N

N

USB

Y

Y

N

N

N

N

N

ADC

Y

Y

Y

N

N

N

N

Y1

Y1

N

LPCMPx

Y

Y

Y

Y1

LVD/HVD

Y

Y

Y

Y

Y

Y

Y

Y4

Y4

Y4

GPIO(except Y

NMI,RESET)

Y

Y

Y4

NMI

Y

Y

Y

Y

Y

Y

Y

RESET

Y

Y

Y

Y

Y

Y

Y

1.

2.

3.

4.

Need to configure this module as wakeup source of LLWU

Need to set EXTAL32 as RTC clock source and configure this module as wakeup source for LLWU

LPTMRs use EXTAL32 or LPO in VLLS0.

Only that pins available to configure to wakeup source of LLWU

K32L3A, Rev. 1, 09/2019

23

NXP Semiconductors

�Overview

Any RESET

VLPW

HSRUN

4

5

12

VLPR

WAIT

1

3

RUN

STOP

6

7

2

VLPS

10

8

9

LLS

VLLS

11

Figure 4. Power mode state transition diagram

2.1.11 LLWU

The LLWU module is used to wake MCU from low leakage power mode (LLS and

VLLSx) and functional only on entry into a low-leakage power mode. After recovery

from LLS, the LLWU is immediately disabled. After recovery from VLLSx, the LLWU

continues to detect wake-up events until the user has acknowledged the wake-up event.

The following is internal peripheral and external pin inputs as wakeup sources for the

Coretex-M4 core (CPU0).

24

NXP Semiconductors

K32L3A, Rev. 1, 09/2019

�Overview

Table 11. Wakeup Sources for LLWU0 inputs

LLWU0 pin

Module source or pin name

LLWU_P0

PTA1

LLWU_P1

PTA2

LLWU_P2

PTA22

LLWU_P3

PTA30

LLWU_P4

PTB1

LLWU_P5

PTB2

LLWU_P6

PTB4

LLWU_P7

PTB6

LLWU_P8

PTB7

LLWU_P9

PTB8

LLWU_P10

PTB16

LLWU_P11

PTB20

LLWU_P12

PTB22

LLWU_P13

PTB25

LLWU_P14

PTB28

LLWU_P15

PTC7

LLWU_P16

PTC9

LLWU_P17

PTC11

LLWU_P18

PTC12

LLWU_P19

PTD8

LLWU_P20

PTD10

LLWU_P21

PTE11

LLWU_P22

PTE31

LLWU_P23

PTE81

LLWU_P24

PTE91

LLWU_P25

PTE101

LLWU_P26

PTE121

LLWU_P27

Reserved2

LLWU_P28

Reserved3

LLWU_P29

USB0 VREGIN

LLWU_P30

USB0_DP4

LLWU_P31

USB0_DM4

LLWU_M0IF

LPTMR0, LPTMR1, LPTMR2 (sharing M0IF)5

LLWU_M1IF

LPCMP06

LLWU_M2IF

LPCMP17

LLWU_M3IF

Reserved8

LLWU_M4IF

Reserved9

LLWU_M5IF

Tamper Detect10

Table continues on the next page...

K32L3A, Rev. 1, 09/2019

25

NXP Semiconductors

�Overview

Table 11. Wakeup Sources for LLWU0 inputs (continued)

LLWU0 pin

Module source or pin name

LLWU_M6IF

RTC Alarm10

LLWU_M7IF

RTC Seconds10

LLWU_M0DR

LPTMR0 Asynchronous DMA

LLWU_M1DR

LPTMR1 Asynchronous DMA

LLWU_M2DR

LPTMR2 Asynchronous DMA

LLWU_M3DR

Reserved11

LLWU_M4DR

LPTMR0 Trigger

LLWU_M5DR

LPTMR1 Trigger

LLWU_M6DR

LPTMR2 Trigger

LLWU_M7DR

Reserved12

1.

2.

3.

4.

5.

Set SPM_CORESC[VDDIOOVRIDE] for all PTE pins to wakeup from VLLS0/1

The corresponding LLWU0_PE[23: 22], LLWU0_PF[27], LLWU0_PDC2[27], and LLWU0_PMC[27] are reserved.

The corresponding LLWU0_PE[25: 24], LLWU0_PF[28], LLWU0_PDC2[28], and LLWU0_PMC[28] are reserved.

Set SPM_CORESC[USBOVRIDE] to wakeup from VLLS0 or VLLS1.

Requires the peripheral and the peripheral interrupt to be enabled. The LLWU's WUME bit enables the internal module

flag as a wakeup input. After wakeup, the flags are cleared based on the peripheral clearing mechanism.

6. Set SPM_CORELPCNFG[ALLREFEN] to wakeup from VLLS0/1.

7. Set SPM_CORESC[VDDIOOVRIDE] and SPM_CORELPCNFG[ALLREFEN] to wakeup from VLLS0/1.

8. The corresponding LLWU0_ME[3] is reserved.

9. The corresponding LLWU0_ME[4] is reserved.

10. Set SPM_CORESC[VDDIOOVRIDE] to wakeup from VLLS0 or VLLS1.

11. The corresponding LLWU0_DE[3] is reserved.

12. The corresponding LLWU0_DE[7] is reserved.

The following is internal peripheral and external pin inputs as wakeup sources for the

Coretex-M0+ core (CPU1).

Table 12. Wakeup Sources for LLWU1 inputs

LLWU1 pin

Module source or pin name

LLWU_P0

PTA1

LLWU_P1

PTA2

LLWU_P2

PTA22

LLWU_P3

PTA30

LLWU_P4

PTB1

LLWU_P5

PTB2

LLWU_P6

PTB4

LLWU_P7

PTB6

LLWU_P8

PTB7

LLWU_P9

PTB8

LLWU_P10

PTB16

LLWU_P11

PTB20

Table continues on the next page...

26

NXP Semiconductors

K32L3A, Rev. 1, 09/2019

�Overview

Table 12. Wakeup Sources for LLWU1 inputs (continued)

LLWU1 pin

Module source or pin name

LLWU_P12

PTB22

LLWU_P13

PTB25

LLWU_P14

PTB28

LLWU_P15

PTC7

LLWU_P16

PTC9

LLWU_P17

PTC11

LLWU_P18

PTC12

LLWU_P19

PTD8

LLWU_P20

PTD10

LLWU_P21

PTE1

LLWU_P22

PTE3

LLWU_P23

PTE8

LLWU_P24

PTE9

LLWU_P25

PTE10

LLWU_P26

PTE12

LLWU_P27

Reserved1

LLWU_P28

Reserved2

LLWU_P29

USB0 VREGIN

LLWU_P30

USB0_DP-1

LLWU_P31

USB0_DM-1

LLWU_M0IF

LPTMR0, LPTMR1, LPTMR2 (sharing M0IF)3

LLWU_M1IF

LPCMP0

LLWU_M2IF

LPCMP1

LLWU_M3IF

RESERVED4

LLWU_M4IF

Reserved5

LLWU_M5IF

Tamper Detect-1

LLWU_M6IF

RTC Alarm-1

LLWU_M7IF

RTC Seconds-1

LLWU_M0DR

LPTMR0 Asynchronous DMA

LLWU_M1DR

LPTMR1 Asynchronous DMA

LLWU_M2DR

LPTMR2 Asynchronous DMA

LLWU_M3DR

Reserved6

LLWU_M4DR

LPTMR0 Trigger

LLWU_M5DR

LPTMR1 Trigger

LLWU_M6DR

LPTMR2 Trigger

LLWU_M7DR

Reserved7

1. The corresponding LLWU1_PE[23:22], LLWU1_PF[27], LLWU1_PDC2[27], and LLWU1_PMC[27] are reserved.

2. The corresponding LLWU1_PE[25:24], LLWU1_PF[28], LLWU1_PDC2[28], and LLWU1_PMC[28] are reserved.

K32L3A, Rev. 1, 09/2019

27

NXP Semiconductors

�Overview

3. Requires the peripheral and the peripheral interrupt to be enabled. The LLWU's WUME bit enables the internal module

flag as a wakeup input. After wakeup, the flags are cleared based on the peripheral clearing mechanism.

4. The corresponding LLWU1_ME[3] is reserved.

5. The corresponding LLWU1_ME[4] is reserved.

6. The corresponding LLWU1_DE[3] is reserved.

7. The corresponding LLWU1_DE[7] is reserved.

2.1.12 Debug controller

This device supports standard Arm 2-pin SWD and JTAG debug port. It provides

register and memory accessibility from the external debugger interface, basic run/halt

control plus 4 breakpoints and 2 watchpoints.

It also supports trace function with the Micro Trace Buffer (MTB), which provides a

simple execution trace capability for the Cortex-M0+ processor.

2.1.13 INTMUX

The Interrupt Multiplexer (INTMUX) routes the interrupt sources to the interrupt

outputs. It provides interrupt status registers to monitor interrupt pending status and

vector numbers and implements the ability to logical AND or OR enabled interrupts on

a given channel.

The INTMUX has the following features:

• Supports 4 multiplex channels

• Each channel receives 32 interrupt sources and has one interrupt output

• Each interrupt source can be enabled or disabled

• Each channel supports logic AND or logic OR of all enabled interrupt sources

2.1.14 FlexBus

The FlexBus multifunction external bus interface controller is a hardware module.

The FlexBus has the following features:

• 6 independent, user-programmable chip-select signals (FB_CS5 – FB_CS0)

• 8-bit, 16-bit, and 32-bit transfers

• Programmable burst and burst-inhibited transfers selectable for each chip-select and

transfer direction

• Programmable address-setup time with reference to the assertion of a chip-select

28

NXP Semiconductors

K32L3A, Rev. 1, 09/2019

�Overview

• Programmable address-hold time with reference to the deassertion of a chip-select

and transfer direction

• Extended address latch enable option to assist with glueless connections to

synchronous and asynchronous memory devices

2.1.15 Watch dog

The Watchdog Timer (WDOG) keeps a watch on the system functioning and resets it

in case of its failure.

The WDOG has the following features:

• Clock source input independent from CPU/bus clock. Choice from LPO, SIRC,

external system clock or bus clock.

• Unlock sequence for allowing updates to write-once WDOG control/configuration

bits.

• All WDOG control/configuration bits are writable once only within 128 bus clock

cycles of being unlocked.

• Programmable time-out period specified in terms of number of WDOG clock

cycles.

• Ability to test WDOG timer and reset with a flag indicating watchdog test.

• Windowed refresh option.

• Robust refresh mechanism.

• Count of WDOG resets as they occur.

• Configurable interrupt on time-out to provide debug breadcrumbs. This is

followed by a reset after 128 bus clock cycles.

2.1.16 EWM

The External Watchdog Monitor (EWM) is a redundant watchdog system which is

used to monitor external circuits, as well as the MCU software flow. This provides a

back-up mechanism to the internal watchdog that resets the MCU's CPU and

peripherals.

The EWM has the following features:

• Independent LPO_CLK clock source

• Programmable time-out period specified in terms of number of EWM LPO_CLK

clock cycles.

• Windowed refresh option

K32L3A, Rev. 1, 09/2019

29

NXP Semiconductors

�Overview

• Provides robust check that program flow is faster than expected.

• Programmable window.

• Refresh outside window leads to assertion of EWM_OUT_b.

• Robust refresh mechanism

• Write values of 0xB4 and 0x2C to EWM Refresh Register within 15 peripheral

bus clock cycles.

• One output port, EWM_OUT_b, when asserted is used to reset or place the external

circuit into safe mode.

• One Input port, EWM_in, allows an external circuit to control the assertion of the

EWM_OUT_b signal.

2.1.17 XRDC

The Extended Resource Domain Controller (XRDC) provides an integrated, scalable

architectural framework for access control, system memory protection and peripheral

isolation.

The XRDC has the following features:

• Assignment of chip resources to processing "domains"

• Processor cores, non-core bus masters, slave memories and slave peripherals

• Each processing domain is assigned a unique domain identifier (domainID,

DID)

• DomainID is a new attribute associated with every system bus transaction

• Used in conjunction with user/privileged, secure/nonsecure attributes

• Access rights to slave targets defined in region descriptor registers for memories

and access control registers for peripherals

• Supports sharing of memory and peripherals with optional inclusion of hardware

semaphores to dynamically determine access rights

• Built upon a 4-level hierarchical access control model

• PrivSecure > PrivNonsecure > UserSecure > UserNonsecure

30

NXP Semiconductors

K32L3A, Rev. 1, 09/2019

�Overview

• Encoded into a 3-bit per-domain access control policy (ACP) used throughout

the XRDC

• Certain processors do not support the PrivNonsecure state. For these cores,

the model simplifies to a 3-state definition: PrivSecure > UserSecure >

UserNonsecure

• Programming model and hardware implementation is distributed across multiple

submodules

• Supports a broad, highly-configurable architecture definition

• Memory region descriptors support a format leveraged from earlier System

Memory Protection Units (SMPU)

2.1.18 MU

The Messaging Unit module enables two processors within the SoC to communicate

and coordinate by passing messages (e.g. data, status and control) through the MU

interface. The MU also provides the ability for one processor to signal the other

processor using interrupts.

The MU has the following features:

• Messaging control by interrupts or by polling

• Symmetrical processor interfaces with each side supporting the following:

• Three general-purpose flags reflected to the other side

• Four general-purpose interrupt requests reflected to the other side

• Four receive registers with maskable interrupt

• Four transmit registers with maskable interrupt

• The Processor B can take the Processor A out of low-power modes by asserting

one of the interrupts to the Processor A and vice versa

2.1.19 SEMA42

The SEMA42 is a memory-mapped module that provides robust hardware support

needed in multi-core systems for implementing semaphores and provides a simple

mechanism to achieve "lock and unlock" operations via a single write access. The

hardware semaphore module provides hardware-enforced gates as well as other useful

system functions related to the gating mechanisms.

K32L3A, Rev. 1, 09/2019

31

NXP Semiconductors

�Overview

The SEMA42 has the following features:

• Supports 16 hardware-enforced gates in a multi-processor configuration, where up

to 15 processors can be supported; cpX is meant to represent core processor X

• Gates appear as an 16-entry byte-size array with read and write accesses.

• Processors lock gates by writing "processor_number+1" to the appropriate

gate and must read back the gate value to verify the lock operation was

successful.

• Once locked, the gate is unlocked by a write of zeroes from the locking

processor.

• The number of implemented gates is specified by a hardware configuration

define.

• Each hardware gate appears as a 16-state, 4-bit state machine.

• 16-state implementation

if gate = 0x0, then state = unlocked

if gate = 0x1, then state = locked by processor (master) 0

if gate = 0x2, then state = locked by processor (master) 1

…

if gate = 0xF, then state = locked by processor (master) 14

• Uses the logical bus master number as a reference attribute plus the

specified data patterns to validate all write operations.

• Once locked, the gate can (and must) be unlocked by a write of zeroes

from the locking processor.

• Secure reset mechanisms are supported to clear the contents of individual

gates, as well as a clear_all capability.

• Memory-mapped IPS slave peripheral platform module

• Interface to the IPS bus for programming-model accesses

2.1.20 TRGMUX

The trigger multiplexer (TRGMUX) module allows software to configure the trigger

inputs for various peripherals.

32

NXP Semiconductors

K32L3A, Rev. 1, 09/2019

�Overview

The TRGMUX module allows software to select the trigger source for peripherals.

Each peripheral has its own dedicated TRGMUX register.

2.2 Peripheral features

The following sections describe the features of each peripherals of the chip.

2.2.1 MSMC

The Multi-System Mode Controller (MSMC) is responsible for sequencing the MCU

into and out of all stop and run power modes.

Specifically, it monitors events to trigger transitions between power modes while

controlling the power, clocks, and memories of the MCU to achieve the power

consumption and functionality of that mode. Additionally, the MSMC will arbitrate

between multiple cores in the MCU to provide each with the most optimal power

mode without negatively impacting the functionality of other cores.

2.2.2 CRC

This device contains one cyclic redundancy check (CRC) module which can generate

16/32-bit CRC code for error detection.

The CRC module provides a programmable polynomial and other parameters required

to implement a 16-bit or 32-bit CRC standard.

The 16/32-bit code is calculated for 32 bits of data at a time.

The CRC module has the following features:

• Hardware CRC generator circuit using a 16-bit or 32-bit programmable shift

register

• Programmable initial seed value and polynomial

• Option to transpose input data or output data (the CRC result) bitwise or bytewise.

This option is required for certain CRC standards. A bytewise transpose operation

is not possible when accessing the CRC data register via 8-bit accesses. In this

case, the user's software must perform the bytewise transpose function.

• Option for inversion of final CRC result

• 32-bit CPU register programming interface

K32L3A, Rev. 1, 09/2019

33

NXP Semiconductors

�Overview

2.2.3 LPDAC

The 12-bit low power digital-to-analog converter (LPDAC) is a low-power, generalpurpose DAC. The output of the DAC can be placed on an external pin or set as one of

the inputs to the analog comparator or ADC.

LPDAC module has the following features:

• On-chip programmable reference generator output. The voltage output range is

from 1⁄4096 Vin to Vin, and the step is 1⁄4096 Vin, where Vin is the input reference

voltage.

• Vin can be selected from two reference sources.

• 16-word depth FIFO supported with configurable watermark.

• Multiple operation modes.

• Buffer mode

• FIFO mode

• Swing back mode

• Software trigger and hardware trigger supported.

• Selectable performance levels: low power mode and high power mode.

• Interrupt and DMA support.

2.2.4 eDMA and DMAMUX

The eDMA controller module enables fast transfers of data, which provides an efficient

way to move blocks of data with minimal processor interaction. The eDMA1 controller

in this device implements eight channels which can be routed from up to 32 DMA

request sources through DMAMUX1 module for CM0+ core. The eDMA0 module

implements 16 channels which can be routed from up to 64 DMA request sources

through DMAMUX0 module for CM4 core. Some of the peripheral request sources

have asynchronous eDMA capability which can be used to wake MCU from Stop

mode. The peripherals which have such capability include FlexIO, LPUART0,

LPUART1, LPUART2, LPUART3, LPSPI0, LPSPI1, LPSPI2, LPSPI3, LPI2C0,

LPI2C1, LPI2C2, LPI2C3, LPCMP0, LPCMP1, TPM0, TPM1, TPM2, TPM3,

34

NXP Semiconductors

K32L3A, Rev. 1, 09/2019

�Overview

LPTMR0, LPTMR1, LPTMR2, LLWU0, LLWU1, I2S, PORTA-PORTE, ADC0, and

LPDAC0. The DMA0 channel 0 to 3 can be periodically triggered by LPIT0 while

DMA1 channel 0 to 3 by LPIT1 via DMA MUX.

eDMA module has the following features:

• All data movement via dual-address transfers: read from source, write to

destination

• Programmable source and destination addresses and transfer size

• Support for enhanced addressing modes

• 16-channel implementation that performs complex data transfers with minimal

intervention from a host processor

• Internal data buffer, used as temporary storage to support 16- and 32-byte

transfers

• Connections to the crossbar switch for bus mastering the data movement

• Transfer control descriptor (TCD) organized to support two-deep, nested transfer

operations

• 32-byte TCD stored in local memory for each channel

• An inner data transfer loop defined by a minor byte transfer count

• An outer data transfer loop defined by a major iteration count

• Channel activation via one of three methods:

• Explicit software initiation

• Initiation via a channel-to-channel linking mechanism for continuous

transfers

• Peripheral-paced hardware requests, one per channel

• Fixed-priority and round-robin channel arbitration

• Channel completion reported via programmable interrupt requests

• One interrupt per channel, which can be asserted at completion of major

iteration count

• Programmable error terminations per channel and logically summed together

to form one error interrupt to the interrupt controller