NXP Semiconductors

Data Sheet: Technical Data

Document Number: MC12XS6D2

Rev. 4.0, 9/2020

10 mOhm and 25 mOhm high-side

switches

MC10XS6200EK; MC10XS6200BEK;

MC10XS6225EK; MC10XS6225BEK;

MC10XS6325EK; MC10XS6325BEK;

MC25XS6300EK; MC25XS6300BEK

The 12XS6 is the latest achievement in automotive lighting drivers. It belongs to

an expanding family, which helps to control and diagnose incandescent lamps

and light-emitting diodes (LEDs) with enhanced precision. It combines flexibility

HIGH-SIDE SWITCH

through daisy chainable SPI 5.0 MHz, extended digital and analog feedback,

safety, and robustness.

Output edge shaping helps to improve electromagnetic performance. To avoid

shutting off the device upon inrush current, while still being able to closely track

the load current, a dynamic overcurrent threshold profile is featured. Current of

each channel can be sensed with a programmable sensing ratio. Whenever

communication with the external microcontroller is lost, the device enters a Fail

operation mode, but remains operational, controllable, and protected.

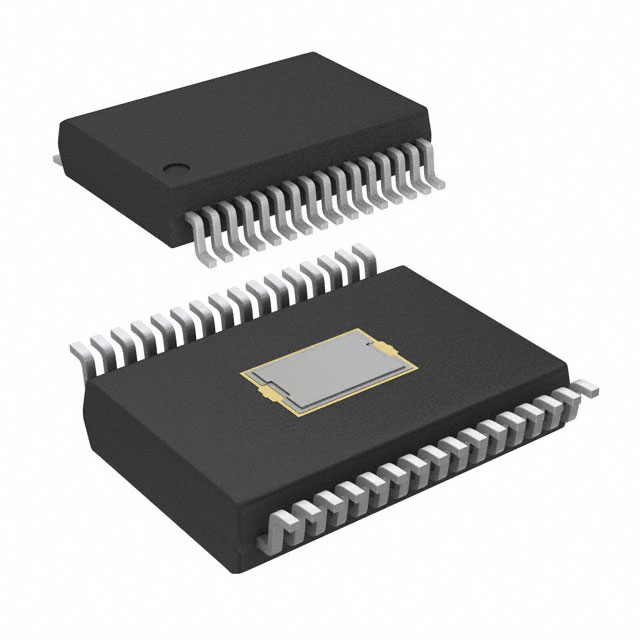

EK SUFFIX (PB-FREE)

BEK SUFFIX (PB-FREE)

98ASA00368D

98ASA00894D

This new generation of high-side switch products family 12XS6 facilitates ECU

32-PIN SOICW-EP

32-PIN SOICW-EP

design due to compatible MCU software and PCB foot prints for each device

variant.

Applications

Features

• Low-voltage automotive lighting

• Dual and triple high-side switches with high transient current capability

• Halogen lamps

• 16-bit 5.0 MHz SPI control of overcurrent profiles, channel control including

• Incandescent bulbs

PWM duty-cycles, output ON and OFF openload detections, thermal

• Light-emitting diodes (LEDs)

shutdown and prewarning, and fault reporting

• HID Xenon ballasts

• Output current monitoring with programmable synchronization signal and

battery voltage feedback

• Limp Home mode

• External smart power switch control

• Operating voltage is 7.0 V to 18 V with sleep current < 5.0 µA, extended mode from 6.0 V to 28 V

• -16 V reverse polarity and ground disconnect protections

• Compatible PCB foot print and SPI software driver among the family

VBAT

VBAT

VBAT

VCC

25XS6300

5.0 V

Regulator

GND

VCC

Main

MCU

GND

SO

CSB

SCLK

SI

RSTB

CLK

A/D1

TRG1

PORT

PORT

PORT

PORT

PORT

A/D2

VBAT

VCC

SI

CP

CSB

OUT1

SCLK

SO

OUT2

RSTB

CLK

OUT3

CSNS

SYNCB

LIMP

IN1

IN2

IN3

IN4

GND OUT6

Figure 1. Triple 25 mΩ simplified application diagram

© 2020 NXP B.V.

VBAT OUT

Smart Power

CSNS GND

IN

�1

Orderable parts

This section describes the part numbers available to be purchased along with their differences. Valid orderable part numbers are provided

on the web. To determine the orderable part numbers for this device, go to http://www.nxp.com and perform a part number search for the

following device numbers.

Table 1. Orderable part variations

Part number

Notes

Temperature

(TA)

OUT1, RDS(on)

Package

MC10XS6200EK

MC10XS6225BEK

MC10XS6325EK

(1)

-40 to 125 °C

OUT4, RDS(on)

OUT6

–

–

10 mΩ

10 mΩ

Yes

25 mΩ

–

10 mΩ

–

Yes

25 mΩ

–

10 mΩ

10 mΩ

Yes

25 mΩ

25 mΩ

25 mΩ

–

Yes

MC10XS6200BEK

MC10XS6225EK

OUT2, RDS(on) OUT3, RDS(on)

SOIC 32-pin

exposed pad

MC10XS6325BEK

MC25XS6300EK

MC25XS6300BEK

Notes

1.

To order parts in tape and reel, add the R2 suffix to the part number.

Table 2. Variation table (EK and BEK versions)

EK version

Symbol

Min.

Typ.

Max.

Min.

Typ.

Max.

Unit

RDS(on)

ON-Resistance, Drain-to-Source for 10 mΩ

power channel

TJ = 150 °C

–

–

16.0

–

–

17.5

mΩ

RDS(on)

ON-Resistance, Drain-to-Source for 25 mΩ

power channel

• TJ = 150 °C

–

–

39.0

–

–

41.0

mΩ

IOCLO

Low overcurrent for 10 mΩ power channel

• High level

16.0

18.0

21.0

14.5

18.0

21.0

A

IOCLO ACM

Low overcurrent for 10 mΩ power channel in

ACM mode

• Low level

3.8

4.5

5.1

3.8

4.5

5.2

A

30

30

150

75

350

160

20

20

150

75

350

160

mA

IOL

Characteristics

BEK version

Output PWM duty cycle range for openload

detection in ON state

• 10 mΩ power channel at TJ = -40 °C

• 25 mΩ power channel at TJ = -40 °C

IOLOFF

Openload current threshold in OFF state

• 10 mΩ power channel

0.7

0.875

1.05

0.7

0.875

1.1

A

RPULLUP

Logic input pull-up resistor for CSB

20

–

100

20

–

130

kΩ

ROUT6 DW

OUT6 pull-down resistor

5

10

20

5

10

30

kΩ

12XS6D2

2

NXP Semiconductors

�Table of Contents

1

2

3

4

5

6

7

8

9

Orderable parts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Internal block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Pin connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.1 Pinout diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.2 Pin definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

General product characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

4.1 Relationship between ratings and operating requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

4.2 Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

4.3 Thermal characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

4.4 Operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

4.5 Supply currents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

General IC functional description and application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

5.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

5.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

5.3 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5.4 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5.5 Modes of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

5.6 SPI interface and configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Functional block requirements and behaviors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

6.1 Self-protected high-side switches description and application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

6.2 Power supply functional block description and application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

6.3 Communication interface and device control functional block description and application information . . . . . . . . . . . . 54

Typical applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

7.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

7.2 EMC and EMI considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

7.3 Robustness considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

7.4 PCB layout recommendations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

7.5 Thermal information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Packaging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

8.1 Marking information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

8.2 Package mechanical dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

12XS6D2

NXP Semiconductors

3

�2

Internal block diagram

VBAT

100 nF

VCC

CP

VCC

Power

Supply

Reverse

Battery

Protection

VBAT_PROTECTED

Vs

UVF

Power-on

Reset

Undervoltage

Detection

OV

Battery

Clamp

CPF

OTW1

OTW2

CS

OTS1

SPI

Thermal

Prewarning

Temperature

Shut-down

SCLK

SI

SPIF

OC1

Fault

Management

OLON1

OLOFF1

Selectable

Slope Control

Selectable Overcurrent

Protection

Selectable OpenLoad

Detection

Selectable

Current Sensing

LIMP

OUT1

IN1

Output Voltage

Monitoring

OUT1 Channel

IN2

PWM Module

OUT2 Channel

OUT2

OUT3 Channel

OUT3

Logic

VCC

Wake OR RST

Clock Failure

Detection

CLK

VCC

5k

CSNS

SYNC\

CSNS

5k

Smart Power

Switch Drive

Reference

PWM Clock

IN3

VCC

A to D Convertion

OUT1

Power channels

Limp Home Control

RST

Charge

Pump

CLKF

SPI Control

SO

VBAT

OUT6

Selectable

Delay

VBAT_PROTECTED

Selectable

Analog

Feedback

VBAT_PROTECTED

Control die

Temperature

Monitoring

Battery

Voltage

Monitoring

GND

Figure 2. Simplified internal block diagram

12XS6D2

4

NXP Semiconductors

�3

Pin connections

3.1

Pinout diagram

Transparent top view of package

CP

1

32

CLK

RSTB

2

31

LIMP

CSB

3

30

IN4

SCLK

4

29

IN3

SI

5

28

IN2

VCC

6

27

IN1

SO

7

26

CSNS SYNCB

OUT6

8

25

CSNS

GND

9

24

GND

OUT2

10

23

OUT1

OUT2

11

22

OUT1

OUT4

12

21

OUT3

OUT4

13

20

OUT3

OUT4

14

19

OUT3

NC

15

18

NC

NC

16

17

NC

VBAT

33

Figure 3. 12XS6 pinout diagram

3.2

Pin definitions

Table 3. 12XS6 pin definitions

Pin number

Pin name

Pin function

Formal name

Definition

1

CP

Internal

supply

Charge Pump

2

RSTB

SPI

Reset

This input pin is used to initialize the device configuration and fault registers, as well as

place the device in a low-current sleep mode. This pin has a passive internal pull-down.

This pin is the connection for an external capacitor for charge pump use only.

3

CSB

SPI

Chip Select

This input pin is connected to a chip select output of a master microcontroller (MCU).

When this digital signal is high, SPI signals are ignored. Asserting this pin low starts the

SPI transaction. The transaction is indicated as completed when this signal returns to

a high level. This pin has a passive internal pull-up to VCC through a diode.

4

SCLK

SPI

Serial Clock

This input pin is connected to the MCU providing the required bit shift clock for SPI

communication. This pin has a passive internal pull-down.

5

SI

SPI

Serial input

This pin is the data input of the SPI communication interface. The data at the input is

sampled on the positive edge of the SCLK. This pin has a passive internal pull-down.

6

VCC

Power

Supply

7

SO

SPI

Serial Output

This output pin is connected to the SPI serial data input pin of the MCU, or to the SI pin

of the next device of a daisy chain of devices. The SPI changes on the negative edge

of SCLK. When CSB is high, this pin is high-impedance.

8

OUT6

Output

External Solid State

This output pin controls an external Smart Power Switch by logic level. This pin has a

passive internal pull-down.

MCU Power Supply This pin is a power supply pin is for internal logic, the SPI I/Os, and the OUT6 driver.

12XS6D2

NXP Semiconductors

5

�Table 3. 12XS6 pin definitions (continued)

Pin number

Pin name

Pin function

Formal name

Definition

9, 24

GND

Ground

Ground

These pins are the ground for the logic and analog circuitries of the device. For ESD

and electrical parameter accuracy purpose, the ground pins must be shorted in the

board.

OUT2

Output

Channel #2

NC

N/A

Not Connected

OUT4

Output

Channel #4

NC

N/A

Not Connected

10XS6225 and 25XS6300: Pins are not connected. It is recommended to connect

these pins to ground.

15, 16, 17, 18

NC

N/A

Not Connected

Pins are not connected. It is recommended to connect these pins to ground.

19, 20, 21

OUT3

Output

Channel #3

Protected high-side power output pins to the load.

OUT1

Output

Channel #1

10XS6225, 10XS6325, and 25XS6300: Protected high-side power output pins to the

load.

NC

N/A

Not Connected

10XS6200: Pins are not connected. It is recommended to connect these pins to ground.

10, 11

12, 13, 14

22, 23

25XS6300: Protected high-side power output pins to the load.

10XS6200, 10XS6225, and 10XS6325: Pins are not connected. It is recommended to

connect these pins to ground.

10XS6200 and 10XS6325: Protected high-side power output pins to the load.

25

CSNS

Feedback

Current Sense

This pin reports an analog value proportional to the designated OUT[1:5] output

current, or the temperature of the exposed pad, or the battery voltage. It is used

externally to generate a ground referenced voltage for the microcontroller (MCU).

Current recopy and analog voltage feedbacks are SPI programmable.

26

CSNS

SYNCB

Feedback

Current Sense

Synchronization

This open drain output pin allows synchronizing the MCU A/D conversion. This pin

requires an external pull-up resistor to VCC.

IN1

Input

Direct Input #1

This input wakes up the device. This input pin is used to directly control corresponding

channel in Fail mode. During Normal mode, the control of the outputs by the control

inputs is SPI programmable.This pin has a passive internal pull-down.

NC

N/A

Not connected

This pin is not connected for 10XS6200

IN2

Input

Direct Input #2

This input wakes up the device. This input pin is used to directly control corresponding

channel in Fail mode. During Normal mode, the control of the outputs by the control

inputs is SPI programmable.This pin has a passive internal pull-down.

NC

N/A

Not connected

This pin is not connected for 10XS6200, 10XS6225, and 10XS6325

IN3

Input

Direct Input #3

This input wakes up the device. This input pin is used to directly control corresponding

channel in Fail mode. During Normal mode, the control of the outputs by the control

inputs is SPI programmable.This pin has a passive internal pull-down.

IN4

Input

Direct Input #4

This input wakes up the device. This input pin is used to directly control corresponding

channel in Fail mode. During Normal mode the control of the outputs by the control

inputs is SPI programmable.This pin has a passive internal pull-down.

NC

N/A

Not connected

This pin is not connected for 10XS6225 and 25XS6300

LIMP

Input

Limp Home

27

28

29

30

31

Device Mode

Feedback

32

CLK

Input/Output

Reference PWM

Clock

33

VBAT

Power

Supply

Battery Power

Supply

The Fail mode can be activated by this digital input. This pin has a passive internal pulldown.

This pin is an input/output pin. It is used to report the device sleep-state information. It

is also used to apply the reference PWM clock which is divided by 28 in Normal

operating mode. This pin has a passive internal pull-down.

This exposed pad connects to the positive power supply and is the source of

operational power for the device.

12XS6D2

6

NXP Semiconductors

�4

General product characteristics

4.1

Relationship between ratings and operating requirements

Fatal Range

Reverse

protection

Probable

permanent

failure

Degraded Operating

Range

Normal

Operating Range

V

40

V

18

32

V

V

7.

0

-1

6

V

Un

5. de

5 rv

V o

lta

ge

The analog portion of device is supplied by the voltage applied to the VBAT exposed pad. Thereby the supply of internal circuitry (logic in

case of a VCC disconnect, charge pump, gate drive,...) is derived from the VBAT pin.

In case of a reverse battery:

• the internal supply rail is protected (max. -16 V)

• the output drivers are switched on, to reduce the power consumption in the drivers when using incandescent bulbs

Degraded Operating

Range

- Reduced performance Full performance - Reduced performance

- Full protection but

- Full protection but

accuracy not

accuracy not

guaranteed

guaranteed

- no PMW feature for

UV to 6.0 V

Potential Failure

Fatal Range

- Reduced performance

- Probable failure in

case of short-circuit

Probable

permanent

failure

-1

6

40

V

V

Operating Range

Fatal Range

Accepted Industry

Standard Practices

Probable

permanent failure

Fatal Range

Probable

permanent failure

Correct operation

Handling Conditions (Power OFF)

Fatal Range

Probable

permanent failure

Not Operating Range

Degraded Operating

Range

Normal Operating

Range

Reduced

performance

Full performance

V

7.

5.

5

0

V

V

5

4.

VC

(2 C

.0 PO

V R

to

4.

0

-0

.6

V

V)

Figure 4. Ratings vs. operating requirements (VBAT pin)

The device’s digital circuitry is powered by the voltage applied to the VCC pin. If VCC is disconnected, the logic part is supplied by the

VBAT pin.

The output driver for SPI signals, CLK pin (wake feedback), and OUT6 are supplied by the VCC pin only. This pin shall be protected

externally in case of a reverse polarity, and in case of a high-voltage disturbance.

Degraded Operating

Range

Fatal Range

Probable

Reduced performance permanent failure

Operating Range

Figure 5. Ratings vs. operating requirements (VCC pin)

12XS6D2

NXP Semiconductors

7

�4.2

Maximum ratings

Table 4. Maximum ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage

to the device.

Symbol

Description (rating)

Min.

Max.

Unit

Notes

Electrical ratings

VBAT

VBAT voltage range

-16

40

V

VCC

VCC logic supply voltage

-0.3

7.0

V

VIN

Digital input voltage

• IN1:IN4 and LIMP

• CLK, SI, SCLK, CSB, and RSTB

-0.3

-0.3

40

20

V

VOUT

Digital output voltage

• SO, CSNS, SYNC, OUT6, CLK

-0.3

20

V

Negative digital input clamp current

–

5.0

mA

Power channel current

• 10 mΩ channel

• 25 mΩ channel

–

–

9

4.5

A

ICL

IOUT

ECL

VESD

Power channel clamp energy capability

• 10 mΩ channel - Initial TJ = 25 °C

• 10 mΩ channel - Initial TJ = 150 °C

• 25 mΩ channel - Initial TJ = 25 °C

• 25 mΩ channel - Initial TJ = 150 °C

ESD voltage

• Human Body Model (HBM) - VBAT, Power Channel, and GND pins

• Human Body Model (HBM) - all other pins

• Charge Device Model (CDM) - corner pins

• Charge Device Model (CDM) - all other pins

(2)

(2)

(3)

(4)

(5)

–

–

–

–

120

60

40

20

-8000

-2000

-750

-500

+8000

+2000

+750

+500

mJ

(6)

V

Notes

2.

Exceeding voltage limits on those pins may cause a malfunction or permanent damage to the device.

3.

Maximum current in negative clamping for IN1:IN4, LIMP, RSTB, CLK, SI, SO, SCLK, and CSB pins.

4.

Continuous high-side output current rating so long as maximum junction temperature is not exceeded. Calculation of maximum output current

using package thermal resistance is required.

5.

Active clamp energy using single-pulse method (L = 2.0 mH, RL = 0 Ω, VBAT = 14 V). See Output clamps.

6.

ESD testing is performed in accordance with the Human Body Model (HBM) (CZAP = 100 pF, RZAP = 1500 Ω), and the Charge Device Model.

12XS6D2

8

NXP Semiconductors

�4.3

Thermal characteristics

Table 5. Thermal ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage

to the device.

Symbol

Description (rating)

Min.

Max.

Unit

Notes

Operating temperature

• Ambient

• Junction

-40

-40

+125

+150

°C

TSTG

Storage temperature

-55

+150

°C

TPPRT

Peak Package Reflow Temperature During Reflow

–

260

°C

(7) (8)

Thermal ratings

TA

TJ

Thermal resistance and package dissipation ratings

RΘJB

Junction-to-Board

–

8.0

°C/W

(9)

RΘJA

Junction-to-Ambient, Natural Convection, Four-Layer Board (2s2p)

–

22

°C/W

(10) (11)

RΘJC

Junction-to-Case (Case top surface)

–

22

°C/W

(12)

Notes

7.

Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause

malfunction or permanent damage to the device.

8.

NXP’s Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and

Moisture Sensitivity Levels (MSL), go to www.nxp.com, search by part number (remove prefixes/suffixes), enter the core ID to view all orderable

parts, and review parametrics.

9.

Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the

board near the package.

10.

Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient

temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

11.

Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

12.

Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

4.4

Operating conditions

This section describes the operating conditions of the device. Conditions apply to all the following data, unless otherwise noted.

Table 6. Operating conditions

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage

to the device.

Symbol

Ratings

Min.

Max.

Unit

7.0

18

V

–

–

28

40

V

Reverse battery

-16

–

V

Functional operating supply voltage - Device is fully functional. All features are

operating.

4.5

5.5

V

Functional operating supply voltage - Device is fully functional. All features are

operating.

VBAT

VCC

Overvoltage range

• Jump Start

• Load dump

Notes

12XS6D2

NXP Semiconductors

9

�4.5

Supply currents

This section describes the current consumption characteristics of the device.

Table 7. Supply currents

Characteristics noted under conditions 4.5 V ≤ VCC ≤ 5.5 V, - 40 °C ≤ TA ≤ 125 °C, GND = 0 V, unless otherwise noted. Typical values

noted reflect the approximate parameter means at TA = 25 °C under nominal conditions, unless otherwise noted.

Symbol

Ratings

Min.

Typ.

Max.

Unit

Notes

Sleep mode measured at VPWR = 12 V

• TA = 25 °C

• TA = 125 °C

–

–

1.2

10

5.0

30

µA

(13) (14)

Operating mode measured at VPWR = 18 V

–

7.0

8.0

mA

(14)

Sleep mode measured at VCC = 5.5 V

–

0.05

5.0

µA

Operating mode measured at VPWR = 5.5 V (SPI frequency 5.0 MHz)

–

2.8

4.0

mA

VBAT current consumptions

IQVBAT

IVBAT

VCC current consumptions

IQVCC

IVCC

Notes

13.

With the Outputs power channels grounded.

14.

With the Outputs power channels opened.

12XS6D2

10

NXP Semiconductors

�5

General IC functional description and application

information

5.1

Introduction

The 12XS6 is the latest SMARTMOS achievement in automotive drivers for all types of centralized automotive lighting applications. It is

an evolution of the successful Gen3 by providing improved features of a complete family of devices using NXP's latest and unique

technologies for the controller and the power stages.

It consists of a scalable family of devices compatible in terms of software driver and package footprint. It allows diagnosing the lightemitting diodes (LEDs) with an enhanced current sense precision with synchronization pin. It combines flexibility through daisy chainable

SPI 5.0 MHz, extended digital and analog feedbacks, safety, and robustness. It integrates an enhanced PWM module with 8-bit duty cycle

capability and PWM frequency prescaler per power channel.

5.2

Features

The main attributes of 12XS6 are:

• Dual, Triple, Quad or Penta high-side switches with overload, overtemperature, and undervoltage protection

• Control output for one external smart power switch

• 16-Bit SPI communication interface with daisy chain capability

• Dedicated control inputs for use in Fail mode

• Analog feedback pin with SPI programmable multiplexer and sync signal

• Channel diagnosis by SPI communication

• Advanced current sense mode for LED usage

• Synchronous PWM module with external clock, prescaler, and multiphase feature

• Excellent EMC behavior

• Power net and reverse polarity protection

• Ultra low-power mode

• Scalable and flexible family concept

• Board layout compatible SOIC54 and SOIC32 package with exposed pad

12XS6D2

NXP Semiconductors

11

�5.3

Block diagram

The choice of multi-die technology in SOIC exposed pad package including low cost vertical trench FET power die associated with Smart

Power control die lead to an optimized solution.

12XS6 - Functional Block Diagram

Power Supply

MCU Interface and Device Control

SPI Interface

Parallel Control Inputs

MCU

Interface

Self-protected

High-side

Switches

OUT[x]

PWM Controller

Supply

MCU Interface and Output Control

Self-protected High-side Switches

Figure 6. Functional block diagram

5.3.1

Self-protected high-side switches

OUT1:OUT4 (depending on the device used) are the output pins of the power switches. The power channels are protected against various

kinds of short-circuits and have active clamp circuitry that may be activated when switching off inductive loads. Many protective and

diagnostic functions are available.

5.3.2

Power supply

The device operates with supply voltages from 5.5 to 40 V (VBAT), but is full spec. compliant only between 7.0 and 18 V. The VBAT pin

supplies power to the internal regulator, analog, and logic circuit blocks. The VCC pin (5.0 V typ.) supplies the output register of the serial

peripheral interface (SPI). Consequently, the SPI registers cannot be read without presence of VCC. The employed IC architecture

guarantees a low quiescent current in Sleep mode.

5.3.3

MCU interface and device control

In Normal mode, the power output channels are controlled by the embedded PWM module, which is configured by the SPI register

settings. VCC must be in the authorized range for bidirectional SPI communication. Failure diagnostics and configuration are also

performed through the SPI port. The reported failure types are: open load, short-circuit to battery, severe short-circuit to ground,

overcurrent, overtemperature, clock-fail, and under and overvoltage.

The device allows driving loads at different frequencies up to 400 Hz.

5.4

Functional description

The device has four fundamental operating modes: Sleep, Normal, Fail, and Power off. It possesses multiple high-side switches (power

channels) each of which can be controlled independently:

• In Normal mode by SPI interface. A second supply voltage (VCC) is required for bidirectional SPI communication

• In Fail mode by the corresponding the direct inputs IN1:IN4. OUT6 is off in this mode

12XS6D2

12

NXP Semiconductors

�5.5

Modes of operation

The operating modes are based on the signals:

• wake = (IN1_ON) OR (IN2_ON) OR (IN3_ON) OR (IN4_ON) OR (RSTB). More details in Logic I/O plausibility check section

• fail = (SPI_fail) OR (LIMP). More details in Loss of communication interface section

The following chapters provide information for OUT1:OUT4. Depending on the device part number, do not consider Non Connected

outputs.

Sleep

wake = [0]

wake = [0]

wake = [1]

(VBAT < VBATPOR) and

(VCC < VCCPOR)

(VBAT < VBATPOR) and

(VCC < VCCPOR)

Fail

(VBAT > VBATPOR) or

(VCC > VCCPOR)

Power

off

(VBAT < VBATPOR) and

(VCC < VCCPOR)

fail = [0] and valid watchdog toggle

Normal

fail = [1]

Figure 7. General IC operating modes

5.5.1

Power off mode

The Power Off mode is applied when VBAT and VCC are below the power on reset threshold (VBAT POR, VCC POR). In power off, no

functionality is available but the device is protected by the clamping circuits. Refer to Supply voltages disconnection section.

5.5.2

Sleep mode

The Sleep mode is used to provide ultra low current consumption. During Sleep mode:

• the component is inactive and all outputs are disabled

• the outputs are protected by the clamping circuits

• the pull-up/pull-down resistors are present

The Sleep mode is the default mode of the device after applying the supply voltages (VBAT or VCC) prior to any wake-up condition (wake

= [0]). The wake-up from Sleep mode is provided by the wake signal.

12XS6D2

NXP Semiconductors

13

�5.5.3

Normal mode

The Normal mode is the regular operating mode of the device. The device is in Normal mode, when the device is in the wake state

(wake = [1]) and no fail condition (fail = [0]) is detected.

During Normal mode:

• the power outputs are under control of the SPI

• the power outputs are controlled by the programmable PWM module

• the power outputs are protected by the overload protection circuit

• the control of the power outputs by SPI programming

• the digital diagnostic feature transfers status of the smart switch via the SPI

• the analog feedback output (CSNS and CSNS SYNC) can be controlled by the SPI

The channel control (CHx) can be summarized:

• CH1:4 controlled by ONx or iINx (if it is programmed by the SPI)

• CH6 controlled by ONx

• Rising CHx by definition means starting overcurrent window for OUT1:4

5.5.4

Fail mode

The device enters the Fail mode, when:

• the LIMP input pin is high (logic [1])

• or the SPI failure is detected

During Fail mode (wake = [1] and fail = [1]):

• the OUT1:OUT4 outputs are directly controlled by the corresponding control inputs (IN1:IN4)

• the OUT6 is turned off

• the PWM module is not available

• while no SPI control is feasible, the SPI diagnosis is functional (depending on the fail mode condition):

• the SO shall report the content of SO register defined by SOA0 to 3 bits

• the outputs are fully protected in case of an overload, overtemperature, and undervoltage

• no analog feedback is available

• the max. output overcurrent profile is activated (OCLO and window times)

• in case of an overload condition or undervoltage, the autorestart feature controls the OUT1:OUT4 outputs

• in case of an overtemperature condition, OCHI1 detection, or severe short-circuit detection, the corresponding output is

latched OFF until a new wake-up event.

The channel control (CHx) can be summarized:

• CH1: 4 controlled by iINx, while the overcurrent windows are controlled by IN_ONx

• CH6 is off

5.5.5

Mode transitions

After a wake-up:

• a power on reset is applied and all SPI SI and SO registers are cleared (logic[0])

• the faults are blanked during tBLANKING

The device enters in Normal mode after start-up if following sequence is provided:

• VBAT and VCC power supplies must be above their undervoltage thresholds (Sleep mode)

• generate wake-up event (wake =1) setting RSTB from 0 to 1

The device initialization is completed after 50 µsec (typ). During this time, the device is robust in case of VBAT interrupts higher than

150 nsec.

The transition from “Normal mode” to “Fail mode” is executed immediately when a fail condition is detected.

During the transition, the SPI SI settings are cleared and the SPI SO registers are not cleared.

When the Fail mode condition was a:

• LIMP input, WD toggle timeout, WD toggle sequence, or the SPI modulo 16 error, the SPI diagnosis is available during Fail

mode

• SI/SO stuck to static level, the SPI diagnosis is not available during Fail mode

12XS6D2

14

NXP Semiconductors

�The transition from “Fail mode” to “Normal mode” is enabled, when:

• the fail condition is removed and

• two SPI commands are sent within a valid watchdog cycle (first WD=[0] and then WD=[1])

During this transition:

• all SPI SI and SO registers are cleared (logic[0])

• the DSF (device status flag) in the registers #1:#7 and the RCF (Register Clearer flag) in the device status register #1 are set

(logic[1])

To delatch the RCF diagnosis, a read command of the quick status register #1 must be performed.

5.6

SPI interface and configurations

5.6.1

Introduction

The SPI is used to:

• control the device in case of Normal mode

• provide diagnostics in case of Normal and Fail mode

The SPI is a 16 Bit full-duplex synchronous data transfer interface with daisy chain capability.

The interface consists of four I/O lines with 5.0 V CMOS logic levels and termination resistors:

• The SCLK pin clocks the internal shift registers of the device

• The SI pin accepts data into the input shift register on the rising edge of the SCLK signal

• The SO pin changes its state on the rising edge of SCLK and reads out on the falling edge

• The CSB enables the SPI interface

• with the leading edge of CSB the registers are loaded

• while CSB is logic [0] SI/SO data are shifted

• with the trailing edge of the CSB signal, SPI data is latched into the internal registers

• when CSB is logic [1], the signals at the SCLK and SI pins are ignored and SO is high-impedance

When the RSTB input is:

• low (logic [0]), the SPI and the fault registers are reset. The Wake state then depends on the status of the input pins

(IN_ON1:IN_ON4)

• high (logic[1]), the device is in Wake status and the SPI is enabled

The functionality of the SPI is checked by a plausibility check. In case of the SPI failure the device enters the Fail mode.

5.6.2

SPI input register and bit descriptions

The first nibble of the 16-bit data word (D15:D12) serves as address bits.

Register

name

SI address

#

D15

8

D14

SI data

D13

4 Bit address

D12

D11

WD

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

11 Bit address

11 bits (D10:D1) are used as data bits.

The D11 bit is the WD toggle bit. This bit has to be toggled with each write command.

When the toggling of the bit is not executed within the WD timeout, the SPI fail is detected.

All register values are logic [0] after a reset. The predefined value is off/inactive unless otherwise noted.

12XS6D2

NXP Semiconductors

15

�SI address

SI data

Register

#

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Initialization 1

0

0

0

0

0

WD

WD SEL

SYNC

EN1

SYNC

EN0

MUX2

MUX1

MUX0

SOA

MODE

SOA3

SOA2

SOA1

SOA0

initialization 2

1

0

0

0

1

WD

OCHI

THERM

AL

X

OCHI

OD4

OCHI

OD3

OCHI

OD2

OCHI

OD1

PWM

sync

OTW

SEL

CH1 control

2

0

0

1

0

WD

PH11

PH01

ON1

PWM71

PWM61

PWM51

PWM41

PWM31

PWM21

PWM11

PWM01

CH2 control

3

0

0

1

1

WD

PH12

PH02

ON2

PWM72

PWM62

PWM52

PWM42

PWM32

PWM22

PWM12

PWM02

CH3 control

4

0

1

0

0

WD

PH13

PH03

ON3

PWM73

PWM63

PWM53

PWM43

PWM33

PWM23

PWM13

PWM03

CH4 control

5

0

1

0

1

WD

PH14

PH04

ON4

PWM74

PWM64

PWM54

PWM44

PWM34

PWM24

PWM14

PWM04

CH6 control

7

0

1

1

1

WD

PH16

PH06

ON6

PWM76

PWM66

PWM56

PWM46

PWM36

PWM26

PWM16

PWM06

output control

8

1

0

0

0

WD

X

PSF4

PSF3

PSF2

PSF1

ON6

X

ON4

ON3

ON2

ON1

9-1

1

0

0

1

WD

0

X

X

X

X

GPWM

EN6

X

GPWM

EN4

GPWM

EN3

GPWM

EN2

GPWM

EN1

9-2

1

0

0

1

WD

1

X

X

10-1

1

0

1

0

WD

0

X

OCLO4

OCLO3

OCLO2

OCLO1

X

ACM

EN4

ACM

EN3

ACM

EN2

ACM

EN1

10-2

1

0

1

0

WD

1

X

NO

OCHI4

NO

OCHI3

NO

OCHI2

NO

OCHI1

X

SHORT

OCHI4

SHORT

OCHI3

SHORT

OCHI2

SHORT

OCHI1

11

1

0

1

1

WD

0

X

X

INEN14

INEN04

INEN13

INEN03

INEN12

INEN02

INEN11

INEN01

12-1

1

1

0

0

WD

0

X

X

PRS14

PRS04

PRS13

PRS03

PRS12

PRS02

PRS11

PRS01

12-2

1

1

0

0

WD

1

X

X

X

X

X

X

X

X

PRS16

PRS06

OLON

DGL3

OLON

DGL2

OLON

DGL1

X

OLOFF

EN4

OLOFF

EN3

OLOFF

EN2

OLOFF

EN1

Global PWM

control

overcurrent

control

input enable

OCHI

TRANSI NO HID1 NO HID0

ENT

GPWM7 GPWM6 GPWM5 GPWM4 GPWM3 GPWM2 GPWM1 GPWM0

prescaler settings

OL control

13-1

1

1

0

1

WD

0

X

OLON

DGL4

OLLED control

13-2

1

1

0

1

WD

1

res

res

res

res

OLLED

TRIG

X

OLLED

EN4

OLLED

EN3

OLLED

EN2

OLLED

EN1

increment /

decrement

14

1

1

1

0

WD

INCR

SGN

X

X

INCR14

INCR04

INCR13

INCR03

INCR12

INCR02

INCR11

INCR01

testmode

15

1

1

1

1

X

X

X

X

X

X

X

X

X

X

X

X

12XS6D2

16

NXP Semiconductors

�WD #0~#14 = watchdog toggle bit

SOA0 ~ SOA3

MUX2

MUX1

MUX0

#0

= address of next SO data word

#0

0

0

0

off

CSNS

OUT1 current

SOA MODE

#0

= single read address of next SO data word

0

0

1

MUX0 ~ MUX2

#0

= CSNS multiplexer setting

0

1

0

OUT2 current

SYNC EN0~ SYNC EN1

#0

= SYNC delay setting

0

1

1

OUT3 current

WD SEL

#0

= watchdog timeout select

1

0

0

OUT4 current

OTW SEL

#1

= over temperature warning threshold selection

1

0

1

unused

PWM SYNC

#1

= reset clock module

1

1

0

VBAT monitor

OCHI ODx

#1

= OCHI window on load demand

1

1

1

control die temp.monitor

NO HIDx

#1

= HID outputs selection

SYNC

SYNC

OCHI THERMAL

#1

= OCHI1 level depending on control die temperature

EN1

EN0

OCHI TRANSIENT

#1

= OCHIx levels adjusted during OFF-to-ON transition

0

0

sync off

PWM0x ~ PWM7x

#2~#7

= PWM value (8Bit)

0

1

valid

PH0x ~ PH1x

#2~#7

= phase control

1

0

trig0

ONx

#2~#8

= channel on/off incl. OCHI control

1

1

trig1/2

PSFx

#8

#0

Sync status

= pulse skipping feature for power output channels

GPWM ENx

#9-1

= global PWM enable

PH 1x

PH 0x

GPWM1 ~ GPWM7

#9-2

= global PWM value (8Bit)

#2~#7

0

0

Phase

0°

ACM ENx

#10-1

= advanced current sense mode enable

0

1

90°

180°

OCLOx

#10-1

= OCLO level control

1

0

SHORT OCHIx

#10-2

= use short OCHI window time

1

1

270°

NO OCHIx

#10-2

= start with OCLO threshold

INEN1x

INEN0x

GPWM

#11

ONx

PWMx

OUTx

x

x

OFF

x

OFF

x

0

0

0

ON

individual

ON

individual

0

1

1

0

1

1

= input enable control

PRS0x ~ PRS1x

#12

= pre scaler setting

0

x

1

#13-1

= OL load in off state enable

OLON DGLx

#13-1

= OL ON deglitch time

OLLED ENx

#13-2

= OL LED mode enable

OLLED TRIG

#13-2

= trigger for OLLED detection in 100% d.c.

INCR SGN

#14

= PWM increment / decrement sign

INCR0x ~ INCR1x

#14

= PWM increment / decrement setting

#12

#1

NO

HID1

NO

HID0

HID Selection

0

0

0

1

1

0

available for channels 3 and 4 only

1

1

unavailable for all channels

INx=1

OUTx

#11

OLOFF ENx

INx=0

ENx

INEN0x ~ INEN1x

PRS 1x

1

ON

global

ON

global

0

OFF

individual

ON

individual

1

OFF

global

ON

global

0

OFF

individual

ON

individual

1

OFF

global

ON

global

0

ON

individual

ON

global

1

ON

global

ON

individual

PRS 0x PRS divider

0

0

available for all channels

0

1

/2

50Hz .... 200Hz

available for channel 3 only

1

x

/1

100Hz .... 400Hz

#14

#14

PWMx

INCR SGN

/4

25Hz .... 100Hz

increment/decrement

0

decrement

1

increment

INCR 1x INCR 0x increment/decrement

0

0

0

1

no increment/decrement

1

0

8 LSB

1

1

16 LSB

4 LSB

12XS6D2

NXP Semiconductors

17

�5.6.3

SPI output register and bit descriptions

The first nibble of the 16 Bit data word (D12:D15) serves as address bits. All register values are logic [0] after a reset, except DSF and

RCF bits. The predefined value is off/inactive unless otherwise noted.

SO address

SO data

Register

#

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

not used

0

0

0

0

0

X

X

X

X

X

X

X

X

X

X

X

X

quick status

1

0

0

0

1

FM

DSF

OVLF

OLF

CPF

RCF

CLKF

X

QSF4

QSF3

QSF2

QSF1

CH1 status

2

0

0

1

0

FM

DSF

OVLF

OLF

res

OTS1

OTW1

OC21

OC11

OC01

OLON1

OLOFF1

CH2 status

3

0

0

1

1

FM

DSF

OVLF

OLF

res

OTS2

OTW2

OC22

OC12

OC02

OLON2

OLOFF2

CH3 status

4

0

1

0

0

FM

DSF

OVLF

OLF

res

OTS3

OTW3

OC23

OC13

OC03

OLON3

OLOFF3

CH4 status

5

0

1

0

1

FM

DSF

OVLF

OLF

res

OTS4

OTW4

OC24

OC14

OC04

OLON4

OLOFF4

device status

7

0

1

1

1

FM

DSF

OVLF

OLF

res

res

res

TMF

OVF

UVF

SPIF

iLIMP

I/O status

8

1

0

0

0

FM

res

TOGGL

E

iIN4

iIN3

iIN2

iIN1

X

OUT4

OUT3

OUT2

OUT1

device ID

9

1

0

0

1

FM

res

res

res

DEVID

7

DEVID

6

DEVID

5

DEVID

4

DEVID

3

DEVID

2

DEVID

1

DEVID

0

not used

10-14

X

X

X

X

X

X

X

X

X

X

X

X

testmode

15

1

X

X

X

X

X

X

X

X

X

X

X

X

QSFx

CLKF

RCF

CPF

OLF

OVLF

DSF

FM

OLOFFx

OLONx

OTWx

OTSx

iLIMP

SPIF

UVF

OVF

TMF

OUTx

iINx

TOGGLE

DEVID0 ~ DEVID2

DEVID3 ~ DEVID4

DEVID5 ~ DEVID7

#1

#1

#1

#1

#1~#7

#1~#7

#1~#7

#1~#8

#2~#6

#2~#6

#2~#6

#2~#6

#7

#7

#7

#7

#7

#8

#8

#8

#9

#9

#9

address from 1010 to 1110

1

1

1

= quick status (OC or OTW or OTS or OLON or OLOFF)

= PWM clock fail flag

= registers clear flag

= charge pump flag

= open load flag (wired or of all OL signals)

= over load flag (wired or of all OC and OTS signals)

= device status flag (RCF or UVF or OVF or CPF or CLKF or TMF)

= fail mode flag

= open load in off state status bit

= open load in on state status bit

= over temperature warning bit

= over temperature shutdown bit

= limp input pin status

= SPI fail flag

= under voltage flag

= over voltage flag

= testmode activation flag

= status of VBAT/2 comparator (reported in real time)

= status of iINx signal (reported in real time)

= status of INx_ON signals (IN1_ON or IN2_ON or IN3_ON or IN4_ON)

= device type

= device family

= design status (incremented number)

#2~#6

#9

OC2x OC1x OC0x over current status

0

0

0

no overcurrent

0

0

1

OCHI1

0

1

0

OCHI2

0

1

1

OCHI3

1

0

0

OCLO

1

0

1

OCHIOD

1

1

0

SSC

1

1

1

not used

DEVID2 DEVID1 DEVID0 device type

0

0

0

Penta3/2

0

0

1

Penta0/5

0

1

0

Quad2/2

0

1

1

Quad0/4

1

0

0

Triple1/2

1

0

1

Triple0/3

1

1

0

res

1

1

1

res

12XS6D2

18

NXP Semiconductors

�5.6.4

Timing diagrams

RSTB

VIH

10% VCC

VIL

tWRST

tCS

tENBL

CSB

90% VCC

VIH

10% VCC

VIL

tRSI

tWSCLKh

tLEAD

tLAG

VIH

90% VCC

SCLK

10% VCC

tSI(SU)

VIL

tWSCLKl

tFSI

tSI(H)

SI

VIH

90% VCC

10% VCC

Don’t Care

Must be Valid

Don’t Care

VIL

tSOEN

SO

Don’t Care

Must be Valid

tSODIS

Tri-stated

Tri-stated

VIH

VIL

Figure 8. Timing requirements during SPI communication

tFSI

tRSI

VOH

90% VCC

50%

SCLK

10% VCC

VOL

VOH

10% VCC

SO

VOL

tRSO

Low to High

tVALID

tFSO

SO

High To Low

VOH

90% VCC

10% VC

VOL

Figure 9. Timing diagram for serial output (SO) data communication

12XS6D2

NXP Semiconductors

19

�5.6.5

Electrical Characterization

Table 8. Electrical characteristics

Characteristics noted under conditions 4.5 V ≤ VCC ≤ 5.5 V, - 40 °C ≤ TA ≤ 125 °C, GND = 0 V, unless otherwise noted. Typical values

noted reflect the approximate parameter means at TA = 25 °C under nominal conditions, unless otherwise noted.

Symbol

Characteristic

Min.

Typ.

Max.

Unit

Notes

SPI signals CSB, SI, SO, SCLK, SO

fSPI

SPI clock frequency

0.5

–

5.0

MHz

VIH

Logic input high state Level (SI, SCLK, CSB, RSTB)

3.5

–

–

V

Logic input high state level for wake-up (RSTB)

3.75

–

–

V

–

–

0.85

V

VIH(WAKE)

VIL

Logic input low state level (SI, SCLK, CSB, RSTB)

VOH

Logic output high state level (SO)

VCC - 0.4

–

–

V

VOL

Logic output low state level (SO)

–

–

0.4

V

Logic input leakage current in Inactive state (SI = SCLK = RSTB = [0]

and CSB = [1])

-0.5

–

+0.5

µA

Logic output tri-state leakage current (SO from 0 V to VCC)

-10

–

+1.0

µA

Logic input pull-up/pull-down resistor

25

–

100

kΩ

Logic pull-up resistor for CSB

25

–

130

kΩ

Logic input capacitance

–

–

20

pF

7.5

10

12.5

µs

SO rising and falling edges with 80 pF

–

–

20

ns

tWCLKh

Required High state duration of SCLK (required setup time)

80

–

–

ns

tWCLKl

Required Low state duration of SCLK (required setup time)

80

–

–

ns

tCS

Required duration from the rising to the falling edge of CSB (required

setup time)

1.0

–

–

µs

tRST

Required low state duration for reset RSTB

1.0

–

–

µs

tLEAD

Falling edge of CSB to rising edge of SCLK (required setup time)

320

–

–

ns

tLAG

Falling edge of SCLK to rising edge of CSB (required setup lag time)

100

–

–

ns

tSI(SU)

SI to falling edge of SCLK (required setup time)

20

–

–

ns

tSI(H)

Falling edge of SCLK to SI (required hold time of the SI signal)

20

–

–

ns

tRSI

SI, CSB, SCLK, max. rise time allowing operation at maximum fSPI

–

20

50

ns

tFSI

SI, CSB, SCLK, max. fall time allowing operation at maximum fSPI

–

20

50

ns

tSO(EN)

Time from falling edge of CSB to reach low-impedance on SO (access

time)

–

–

60

ns

tSO(DIS)

Time from rising edge of CSB to reach Tri-state on SO

–

–

60

ns

IIN

IOUT

RPULL

RPULL-CSB

CIN

tRST_DGL

tSO

RSTB deglitch Time

(15)

Notes

15.

Parameter is derived from simulations.

12XS6D2

20

NXP Semiconductors

�6

Functional block requirements and behaviors

6.1

Self-protected high-side switches description and application

information

6.1.1

Features

Up to four power outputs are foreseen to drive automotive light applications. The outputs are optimized for driving automotive bulbs, but

also HID ballasts, LEDs, and other primarily resistive loads.

The smart switches are controlled by use of high sophisticated gate drivers. The gate drivers provide:

• output pulse shaping

• output protections

• active clamps

• output diagnostics

6.1.2

Output pulse shaping

The outputs are controlled with a closed loop active pulse shaping to provide the best compromise between:

• low switching losses

• low EMC emission performance

• minimum propagation delay time

Depending on the programming of the prescaler setting register #12-1, #12-2, the switching speeds of the outputs are adjusted to the

output frequency range of each channel.

The edge shaping shall be designed according the following table:

Divider

factor

PWM freq. (Hz)

PWM period (ms)

D.C. range (hex)

D.C. range (LSB)

min.

max.

min.

max.

min.

max.

min.

max

Min. on/off

duty cycle

time (μs)

4

25

100

10

40

03

FB

4

252

156

2

50

200

5

20

07

F7

8

248

156

1

100

400

2.5

10

07

F7

8

248

78

The edge shaping provides full symmetry for rising and falling transition:

• the slopes for the rising and falling edge are matched to provide the best EMC emission performance

• the shaping of the upper edges and the lower edges are matched to provide the best EMC emission performance

• the propagation delay time for the rising edge and the falling edge is matched to provide true duty cycle control of the output

duty cycle error, < 1 LSB at max. frequency

• a digital regulation loop is used to minimize the duty cycle error of the output signal

12XS6D2

NXP Semiconductors

21

�Figure 10. Typical power output switching (slow and fast slew rate)

6.1.2.1

SPI control and configuration

For optimized control of the outputs, a synchronous clock module is integrated. The PWM frequency and output timing during Normal

mode are generated from the clock input (CLK) by the integrated PWM module. In case of clock fail (very low frequency, very high

frequency), the output duty cycle is 100%.

Each output (OUT1:OUT6) can be controlled by an individual channel control register:

Register

CHx control

SI address

#

2-7

D15

D14

SI data

D13

channel address

D12

D11

D10

D9

D8

WD

PH1x

PH0x

Onx

D7

D6

D5

D4

D3

D2

D1

D0

PWM7 PWM6 PWM5 PWM4 PWM3 PWM2 PWM1 PWM0

x

x

x

x

x

x

x

x

where:

• PH0x:PH1x: phase assignment of the output channel x

• ONx: on/off control including overcurrent window control of the output channel x

• PWM0x:PWM7x: 8-bit PWM value individually for each output channel x

The ONx bits are duplicated in the output control register #8 to control the outputs with either the CHx control register or the output control

register.

The PRS1x:PRS0x prescaler settings can be set in the prescaler settings register #12-1 and #12-2.

The following changes of the duty cycle are performed asynchronous (with pos. edge of CSB signal):

• turn on with 100% duty cycle (CHx = ON)

• change of duty cycle value to 100%

• turn off (CHx = OFF)

• phase setting (PH0x:PH1x)

• prescaler setting (PRS1x:PRS0x)

A change in phase setting or prescaler setting during CHx = ON may cause an unwanted long ON-time. Therefore it is recommended to

turn off the output(s) before execution of this change.

The following changes of the duty cycle are performed synchronous (with the next PWM cycle):

• turn on with less than 100% duty cycle (OUTx = ONx)

• change of duty cycle value to less than 100%

A change of the duty cycle value can be achieved by a change of the:

• PWM0x:PWM7x bits in individual channel control register #2:#7

• GPWM EN1: GPWM EN6 bits (change between individual PWM and global PWM settings) in global PWM control register #9-1

• incremental/decremental register #14

The synchronization of the switching phases between different devices is provided by the PWM SYNC bit in the initialization 2 register #1.

12XS6D2

22

NXP Semiconductors

�On the SPI write into initialization 2 register (#1):

• initialization when the bit D1 (PWM SYNC) is logic[1], all counters of the PWM module are reset with the positive edge of the

CSB, i.e. the phase synchronization is performed immediately within one SPI frame. It could help to synchronize different

12XS6 devices in the board

• when the bit D1 is logic[0], no action is executed

The switching frequency can be adjusted for the corresponding channel as described in the following table:

CLK freq. (kHz)

min.

25.6

Prescaler setting

max.

102.4

PWM freq. (Hz)

PRS1x

PRS0x

Divider

factor

0

0

4

25

100

slow

0

1

2

50

200

slow

1

X

1

100

400

fast

min.

max.

PWM resolution)

Slew rate

(bit)

(steps)

8

256

No PWM feature is provided in case of:

• Fail mode

• clock input signal failure

6.1.2.2

Global PWM control

In addition to the individual PWM register, each channel can be assigned independently to a global PWM register.

The setting is controlled by the GPWM EN bits inside the global PWM control register #9-1. When no control by direct input pin is enabled

and the GPWM EN bit is:

• low (logic[0]), the output is assigned to individual PWM (default status)

• high (logic[1]), the output is assigned to global PWM

The PWM value of the global PWM channel is controlled by the global PWM control register #9-2.

Table 9. Global PWM register

ONx

INEN1x

INEN0x

GPWM ENx

0

x

x

0

0

0

1

INx = 0

INx = 1

CHx

PWMx

CHx

PWMx

x

OFF

x

OFF

x

0

ON

individual

ON

individual

1

ON

global

ON

global

1

0

OFF

individual

ON

individual

1

0

1

OFF

global

ON

global

1

1

0

ON

individual

ON

global

1

ON

global

ON

individual

When a channel is assigned to global PWM, the switching phase the prescaler and the pulse skipping are according the corresponding

output channel setting.

6.1.2.3

Incremental PWM control

To reduce the control overhead during soft start/stop of bulbs (e.g. theatre dimming), an incremental PWM control feature is implemented.

With the incremental PWM control feature the PWM values of all internal channels OUT1:OUT4 can be incremented or decremented with

one SPI frame.

The incremental PWM feature is not available for:

• the global PWM channel

• the external channel OUT6

The control is according the increment/decrement register #14:

• INCR SGN: sign of incremental dimming (valid for all channels)

• INCR 1x, INCR 0x increment/decrement

12XS6D2

NXP Semiconductors

23

�INCR SG N increm ent/decre me nt

0

de creme nt

incre ment

1

INCR 1x INCR 0x incre ment/decreme nt

0

0

n o i ncrement/d ecre me nt

0

1

1

0

8

1

1

16

4

This feature limits the duty cycle to the rails (00 resp. FF) to avoid any overflow.

6.1.2.4

Pulse skipping

Due to the output pulse shaping feature and the resulting switching delay time of the smart switches, duty cycles close to 0% resp. 100%

can not be generated by the device. Therefore the pulse skipping feature (PSF) is integrated to interpolate this output duty cycle range in

Normal mode.

The pulse skipping provides a fixed duty cycle pattern with eight states to interpolate the duty cycle values between F7 (Hex) and FF (Hex).

The range between 00 (Hex) and 07 (Hex) is not considered to be provided.

The pulse skipping feature:

• is available individually for the power output channels (OUT1:OUT4)

• is not available for the external channel (OUT6)

The feature is enabled with the PSF bits in the output control register #8.

When the corresponding PSF bit is:

• low (logic[0]), the pulse skipping feature is disabled on this channel (default status)

• high (logic[1]), the pulse skipping feature is enabled on this channel

hex

FF

FE

FD

FC

FB

FA

F9

F8

F7

F6

F5

F4

.

.

.

.

03

02

01

00

PWM duty cycle

dec

[%]

256

100,00%

255

99,61%

254

99,22%

253

98,83%

252

98,44%

251

98,05%

250

97,66%

249

97,27%

96,88%

248

96,48%

247

96,09%

246

245

95,70%

.

.

.

.

.

.

.

.

4

1,56%

3

1,17%

2

0,78%

1

0,39%

S0

FF

F7

F7

F7

F7

F7

F7

F7

pulse skipping frame

S1 S2 S3 S4 S5 S6

FF FF FF FF FF FF

FF FF FF FF FF FF

FF FF FF F7 FF FF

FF F7 FF F7 FF FF

FF F7 FF F7 FF F7

F7 F7 FF F7 FF F7

F7 F7 FF F7 F7 F7

F7 F7 F7 F7 F7 F7

S7

FF

FF

FF

FF

FF

FF

FF

FF

12XS6D2

24

NXP Semiconductors

�6.1.2.5

Input control

Up to four dedicated control inputs (IN1:IN4) are foreseen to:

• wake-up the device

• fully control the corresponding output in case of Fail mode

• control the corresponding output in case of Normal mode

The control during Normal mode is according the INEN0x and INEN1x bits in the input enable register #11. See Table 9.

An input deglitcher is provided at each control input to avoid high frequency control of the outputs. The internal signal is called iINx.

The channel control (CHx) can be summarized:

• Normal mode:

• CH1: 4 controlled by ONx or INx (if it is programmed by the SPI)

• CH6 controlled by ONx

• Rising CHx by definition means starting overcurrent window for OUT1:4

• Fail mode:

• CH1: 4 controlled by iINx, while the over current windows are controlled by IN_ONx

• CH6 are off

The input thresholds are logic level compatible, so the input structure of the pins are able to withstand battery voltage level (max.40 V)

without damage. External current limit resistors (i.e. 1.0 k:10 k) can be used to handle reverse current conditions.

The inputs have an integrated pull-down resistor.

6.1.2.6

Electrical characterization

Table 10. Electrical characteristics

Characteristics noted under conditions 7.0 V ≤ VBAT ≤ 18 V, - 40 °C ≤ TA ≤ 125 °C, GND = 0 V, unless otherwise noted. Typical values

noted reflect the approximate parameter means at TA = 25 °C under nominal conditions, unless otherwise noted.

Symbol

Characteristic

Min.

Typ.

Max.

RDS(on)

ON-Resistance, Drain-to-Source for 10 mΩ power channel

• TJ = 25 °CV

• TJ = 150 °C

• TJ = 25 °C, VBAT = -12 V

• TJ = 150 °C, VBAT = -12 V

–

–

–

–

9.0

–

–

–

–

17.5

18

28

RDS(on)

ON-Resistance, Drain-to-Source for 25 mΩ power channel

• TJ = 25 °C

• TJ = 150 °C

• TJ = 25 °C, VBAT = -12 V

• TJ = 150 °C, VBAT = -12 V

–

–

–

–

22

–

–

–

–

41

43

57

Sleep mode output leakage current (output shorted to GND) per

channel

• TJ = 25 °C, VBAT = 12 V

• TJ = 125 °C, VBAT = 12 V

• TJ = 25 °C, VBAT = 35 V

• TJ = 125 °C, VBAT = 35 V

–

–

–

–

–

–

–

–

0.5

5.0

5.0

25

Operational output leakage current in OFF-State per channel

• TJ = 25 °C, VBAT = 18 V

• TJ = 125 °C, VBAT = 18 V

–

–

–

–

10

20

Output PWM duty cycle range (measured at VOUT = VBAT/2)

• Low frequency range (25 to 100 Hz)

• Medium frequency range (50 to 200 Hz)

• High frequency range (100 to 400 Hz)

4.0

8.0

8.0

–

–

–

252

248

248

Unit

Notes

Power outputs OUT1:OUT4

ILEAK SLEEP

IOUT

OFF

δPWM

mΩ

mΩ

µA

µA

LSB

12XS6D2

NXP Semiconductors

25

�Table 10. Electrical characteristics (continued)

Characteristics noted under conditions 7.0 V ≤ VBAT ≤ 18 V, - 40 °C ≤ TA ≤ 125 °C, GND = 0 V, unless otherwise noted. Typical values

noted reflect the approximate parameter means at TA = 25 °C under nominal conditions, unless otherwise noted.

Symbol

Min.

Typ.

Max.

Unit

Notes

Rising and falling edges slew-rate at VBAT = 14 V (measured from

VOUT = 2.5 V to VBAT - 2.5 V)

• Low frequency range

• Medium frequency range

• High frequency range

0.3

0.3

0.65

0.55

0.55

1.15

0.8

0.8

1.65

V/µs

(16)

ΔSR

Rising and falling edges slew rate matching at VBAT = 14 V (SRr/SRf)

0.8

1.0

1.1

tDLY

Turn-on and Turn-off delay times at VBAT = 14 V

• Low frequency range

• Medium frequency range

• High frequency range

20

20

10

60

60

30

100

100

50

Turn-on and Turn-off delay times matching at VBAT = 14 V

• Low frequency range

• Medium frequency range

• High frequency range

-20

-20

-10

0.0

0.0

0.0

20

20

10

Shutdown delay time in case of fault

0.5

2.5

4.5

µs

25.6

–

102.4

kHz

SR

ΔtDLY

tOUTPUT SD

Characteristic

(16)

µs

(16)

µs

(16)

Reference PWM clock

fCLK

Clock input frequency range

Notes

16.

With nominal resistive load: 2.5 Ω and 5.0 Ω respectively for 10 mΩ and 25 mΩ channel.

6.1.3

Output protections

The power outputs are protected against fault conditions in Normal and Fail mode in case of:

• overload conditions

• harness short-circuit

• overcurrent protection against ultra-low resistive short-circuit conditions thanks to smart overcurrent profile and severe shortcircuit protection

• overtemperature protection including overtemperature warning

• under and overvoltage protections

• charge pump monitoring

• reverse battery protection

In case a fault condition is detected, the corresponding output is commanded off immediately after the deglitch time tFAULT SD.

The turn off in case of a fault shutdown (OCHI1, OCHI2, OCHI3, OCLO, OTS, UV, CPF, OLOFF) is provided by the FTO feature (fast turn

off).

The FTO:

• does not use edge shaping

• is provided with high slew rate to minimize the output turn-off time tOUTPUT SD, in regards to the detected fault

• uses a latch which keeps the FTO active during an undervoltage condition (0 < VBAT < VBAT UVF)

12XS6D2

26

NXP Semiconductors

�Figure 11. Power output switching in nominal operation and in case of fault

Normal mode

In case of a fault condition during Normal mode:

• the status is reported in the quick status register #1 and the corresponding channel status register #2:#5.

To restart the output:

• the channel must be restarted by writing the corresponding ON bit in the channel control register #2:#5 or output control

register #8

12XS6D2

NXP Semiconductors

27

�OLOFF

(Ioutx > I oloff thres) or (t > t oloff)

OUTx = 1

(OLOFF ENx = 1)

(rewrite CHx=1) & (tochi1+tochi2< t tochi1+tochi2+tochi3)] or

[(set CHx=1) & (NO OCHIx=1)]

[(t > tochi1+tochi2+tochi3) & (fault x=0)] or

[(NO OCHIx=1) & (fault x=0)]

Definitions of key logic signals

(fault x):= (UV) or (OCHI1x) or (OCHI2x) or (OCHI3x) or (OCLOx) or (OTx) or (SSCx)

(set CHx=1):= [(ONx=0) then (ONx=1)] or [(iINx=0) then (iINx=1)]

(rewrite CHx=1):= (rewrite ONx=1) after (fault x=1)

SSCx:= severe short circuit detection

tochi2 is depending on NO_HID settings and output current during OCHI2 state

Figure 12. Output control diagram in normal mode

12XS6D2

28

NXP Semiconductors

�Fail mode

In case of an overcurrent (OCHI2, OCHI3, OCLO) or undervoltage, the restart is controlled by the autorestart feature

I threshold

I OCHI2

I OCHI3

driver turned off in case of

fault_fail x ( = OC or UV)

event during autorestart

driver turned on again with

OCHI2 after fault_fail x

I OCLO

In case of successful autorestart

(no fault_fail x event)

OCLO remains active

tOCHI2

time

t AUT ORESTART

Figure 13. Autorestart in fail mode