QorIQ Communications Platforms

QorIQ P1010 and P1014

Communications Processors

QorIQ P1010 and P1014 Block Diagram

Target Markets and Applications

• Wireless LAN access points

(802.11ac/802.11n)

QorIQ P1010 and P1014 Processor Block Diagram

Power Architecture®

e500-v2 Core

• SOHO/SMB routers

32 KB

D Cache

• Controller for Ethernet switches

• Network attached storage

• Video surveillance

• Factory automation and industrial control

256 KB

Frontside

Cache

32 KB

I Cache

Security Fuse

Processor

Security Monitor

16/32-bit DDR3/3L

Memory Controller

(16-bit only for the P1014)

Coherent System Bus

2x FlexCAN

USB 2.0 w/PHY

IFC, TDM

Security

4.4

SD/MMC

DMA

1 GE

1 GE

2x DUART

1 GE

(P1010

only)

SATA

SATA

PCIe

PCIe

2x I2C

SPI, GPIO

6-Lane 2.5 GHz SerDes

(P1010 only)

Core Complex (CPU and L2 Cache)

Basic Peripherals and Interconnect

Accelerators and Memory Control

Networking Elements

Overview

Secure Boot

The QorIQ P1010 and P1014 processors are

The secure boot feature ensures that the

members of the value-perfomance tier, offering

processors only run authenticated code.

extensive integration and extreme power

intelligence for a wide variety of applications

in cost-sensitive networking, network

attached storage, digital video surveillance

and industrial segments. Based on 45 nm

technology for low-power implementation,

the P1010 and P1014 processors provide a

single-core, low-power solution for the 533

to 1000 MHz performance range, along with

a trusted security platform and a rich set of

interfaces.

Through a set of fuses that OEMs can

program once but can never be read, secure

boot prevents unauthorized parties from

reverse engineering code to steal intellectual

property, from loading illegitimate code to

change system functionality or from extracting

sensitive user information that may be stored

in the system.

�Security Engine

Dual FlexCAN controllers

The QorIQ security engine (SEC) is optimized

Two FlexCAN (revision 2.0B) controllers provide

to handle all the algorithms associated with

a standard interface for implementing industrial

IPSec, IEEE Std. 802.11i™ standard, and iSCSI.

protocols. Each FlexCAN controller has the

The security engine also supports booting to a

following features:

known good state, untamperable boot code,

key storage, I/O protection, and secure debug.

The SEC is a modular and scalable security

core optimized to process all the algorithms

associated with IPsec, IKE, SSL/TLS,

iSCSI, SRTP, IEEE Std. 802.11i™, IEEE Std.

802.16™ (WiMAX), and IEEE Std. 802.1AE

(MACSec). The SEC is designed to perform

multi-algorithmic operations (for example,

3DES-HMAC-SHA-1) in a single pass of the

data. The security coprocessor in the QorIQ

P1010 processor is capable of performing

single-pass security cryptographic processing

for SSL 3.0, SSL 3.1/TLS 1.0, IPSec, SRTP,

and IEEE Std. 802.11i.

• High-speed interfaces (not all available

simultaneously)

Six SerDes to 3.125 GHz multiplexed

across controllers

Two PCI Express controllers

Two SGMII interfaces

• Programmable bit rates up to 1 Mb/s

Two SATA interfaces

• Standard data and remote frames

• Up to eight bytes data length

• One USB controller (USB 2.0) with

integrated PHY, host, OTG and device

support

• Up to 64 message buffers (MB), each

• Serial peripheral interface

• Extended data and remote frames

• Trusted boot platform, integrated security

engine (SEC 4.0)

configurable as Rx or Tx

• Individual Rx mask registers per message

Crypto algorithm support includes

3DES, AES, RSA/ECC, MD5/

SHA, ARC4, Snow 3G and FIPS

deterministic RNG

buffers

• Rx FIFO with storage capacity of six frames

and internal pointer handling

• Rx FIFO ID filtering

Single pass encryption/message

authentication for common security

protocols (IPsec, SSL, SRTP, WiMAX)

• Time stamp based on 16-bit free running

timer

XOR acceleration

Technical Specifications

SEC Features

• XOR engine for parity checking in RAID

storage applications

• Single e500 core, built on Power

Architecture® technology

• RNG (random number generator)

• 32 general-purpose I/O signals

533 MHz to 800 MHz core clock

frequency

• PKHA (public key hardware accelerator)

accelerator)

• Integrated flash controller with enhanced

capabilities to support large pages

32 KB L1 instruction cache and 32 KB

L1 data cache

Cryptographic Execution Units:

• MDHA (message digest hardware

• Two I2C controllers, two DUARTs, timers

Double-precision floating-point support

multi-command descriptor chains

• AESA (AES accelerator)

• Four-channel DMA controller

36-bit physical addressing

• Four crypto-channels, each supporting

• DESA (DES accelerator)

• 16/32-bit DDR3/DDR3L SDRAM memory

controller with ECC support

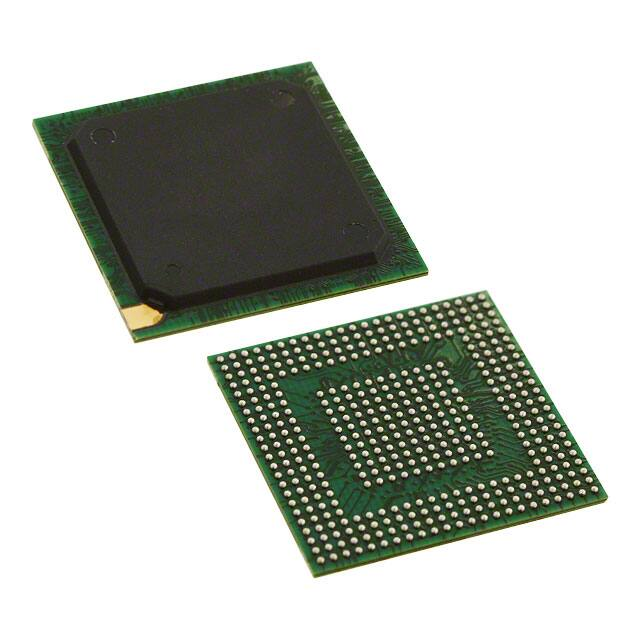

• Package: 425-pin TEPBGA1, 0.8 mm pitch,

19 mm x 19 mm

• 256 KB L2 cache with ECC, also

configurable as SRAM and stashing

memory

Software and Tools Support

• Enea®: Real-time operating system support

• Three 10/100/1000 Mb/s enhanced threespeed Ethernet controllers (eTSECs)

• Green Hills®: Complete portfolio of

software and hardware development tools,

TCP/IP acceleration and classification

capabilities

• AFHA (ARC four hardware accelerator)

• STHA (SNOW 3G f8 and f9 hardware

trace tools and real-time operating systems

• Mentor Graphics®: Commercial grade Linux®

IEEE® 1588 support

accelerators)

solution

Lossless flow control

• CRCA (cyclic redundancy check

• P1010 reference design board (RDB)

RGMII, SGMII

accelerator)

• KFHA (Kasumi hardware accelerator)

QorIQ P1010 and P1014 Comparison

QorIQ Device

Top Core Frequency

L2 Size

DDR 3 Support

GE Ports

SATA

PCI Express®

Security

CAN

P1010

1000 MHz

256 KB

16/32-bit @ 800 MHz

3

2

2

Trusted

2

P1014

800 MHz

256 KB

16-bit @ 800 MHz

2

2

2

No

No

For more information about QorIQ products, visit freescale.com/QorIQ

Freescale, the Freescale logo, PowerQUICC and QorIQ are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off.

All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks

and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2010, 2013 Freescale Semiconductor, Inc.

Document Number: QP1010FS REV 1

�