3.3 VOLT TIME SLOT INTERCHANGE

DIGITAL SWITCH

16,384 X 16,384

IDT72V71660

FEATURES:

DESCRIPTION:

•

•

•

The IDT72V71660 has a non-blocking switch capacity of 2,048 x 2,048

channels at 2.048Mb/s, 4,096 x 4,096 channels at 4.096Mb/s, and 8,192 x

8,192 channels at 8.192Mb/s and 16,384 x 16,384 channels at 16.384Mb/s.

With 64 inputs and 64 outputs, programmable per stream control, and a variety

of operating modes the IDT72V71660 is designed for the TDM time slot

interchange function in either voice or data applications.

Some of the main features of the IDT72V71660 are LOW power 3.3 Volt

operation, automatic ST-BUS® /GCI sensing, memory block programming,

simple microprocessor interface, one cycle direct internal memory accesses,

JTAG Test Access Port (TAP) and per stream programmable input offset delay,

variable or constant throughput modes, output enable and processor mode.

The IDT72V71660 is capable of switching up to 16,384 x 16,384 channels

without blocking. Designed to switch 64 Kbit/s PCM or N x 64 Kbit/s data, the

device maintains frame integrity in data applications and minimizes throughput

delay for voice applications on a per-channel basis.

•

•

•

•

•

•

•

•

•

•

•

•

16K x 16K non-blocking switching at 16.384Mb/s

64 serial input and output streams

Accepts data streams at 2.048Mb/s, 4.096Mb/s, 8.192Mb/s or

16.384Mb/s

Per-channel Variable Delay Mode for low-latency applications

Per-channel Constant Delay Mode for frame integrity applications

Automatic identification of ST-BUS® and GCI bus interfaces

Automatic frame offset delay measurement

Per-stream frame delay offset programming

Per-channel high-impedance output control

Direct microprocessor access to all internal memories

Memory block programming for quick setup

IEEE-1149.1 (JTAG) Test Port

3.3V Power Supply

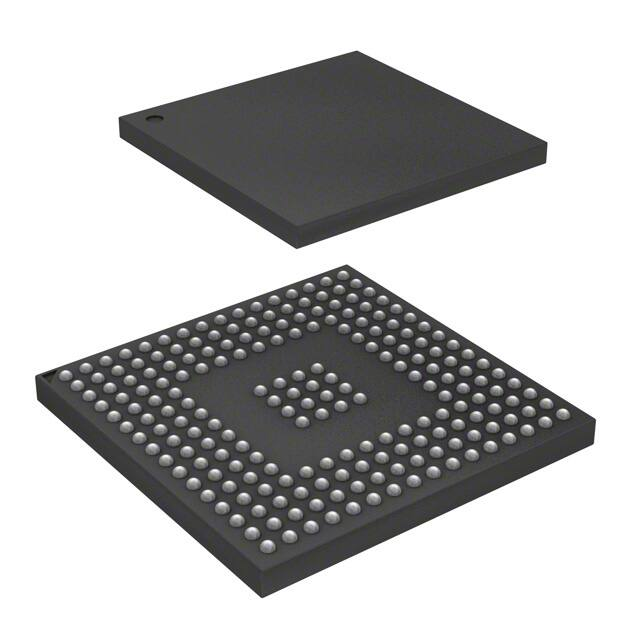

Available in 208-pin (17mm x 17mm) Plastic Ball Grid Array

(PBGA) and 208-pin (28mm x 28mm) Plastic Quad Flatpack

(PQFP) packages

Operating Temperature Range -40°°C to +85°°C

FUNCTIONAL BLOCK DIAGRAM

VCC

GND

ODE

R ESET

TX0

RX0

Data Memory

TX1

MUX

RX1

Receive

Serial Data

Streams

Transmit

Serial Data

Streams

Connection

Memory

Internal

Registers

TX3

1

TX32/OEI0

TX33/OEI1

TX63/OEI31

RX63

Microprocessor Interface

Timing Unit

CLK

FP FE/HCLK WFPS

DS

CS

R/W

A0-A15

D TA

JTAG Port

D0-D15

TMS TDI TCK TDO TR ST

5905 drw01

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc. The ST-BUS® is a trademark of Mitel Corp.

JUNE 2004

1

© 2004

Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice.

DSC-5905/10

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

PIN CONFIGURATIONS

A1 BALL PAD CORNER

A

CLK

R ESET

ODE

RX1

RX4

TX0

TX4

TX7

TX12

TX15

RX11

RX15

RX20

TX16

TX18

TX19

FP

FE/HCLK

RX0

RX2

RX5

TX1

TX5

TX8

TX11

TX14

RX10

RX14

RX19

RX23

TX17

TX20

B

C

WFP

S

TMS

TDI

RX3

RX6

TX2

TX6

TX9

TX10

TX13

RX9

RX13

RX18

RX22

TX22

TX21

TDO

TCK

TR ST

DS

RX7

TX3

VCC

VCC

VCC

VCC

RX8

RX12

RX17

RX21

TX24

TX23

CS

R/W

A0

A

1

RX16

TX27

TX26

TX25

A2

A3

A4

A5

TX31

TX30

TX29

TX28

A6

A7

A8

VCC

GND

GND

GND

GND

VCC

RX26

RX25

RX24

A9

A10

A11

VCC

GND

GND

GND

GND

VCC

RX29

RX28

RX27

A14

A13

A12

VCC

GND

GND

GND

GND

VCC

RX30

RX31

RX32

D15

D TA

A15

VCC

GND

GND

GND

GND

VCC

RX33

RX34

RX35

D12

D13

D14

NC(1)

RX36

RX37

RX38

RX39

D8

D9

D10

D11

TX32/

OEI0

TX33/

OEI1

TX34/

OEI2

TX35/

OEI3

D5

D6

D7

RX56

TX60/

OEI28

TX56/

OEI24

VCC

VCC

VCC

VCC

RX51

RX47

TX36/

OEI4

TX37/

OEI5

TX38/

OEI6

TX39/

OEI7

D3

D4

RX60

RX57

TX61/

OEI29

TX57/

OEI25

TX53/

OEI21

TX50/

OEI18

TX49/

OEI17

RX54

RX50

RX46

RX43

TX40/

OEI8

TX41/

OEI9

TX42/

OEI10

D2

RX63

RX61

RX58

TX62/

OEI30

TX58/

OEI26

TX54/

OEI22

TX51/

OEI19

TX48/

OEI16

RX53

RX49

RX45

RX42

RX40

TX46/

OEI14

TX43/

OEI11

D1

D0

RX62

RX59

TX63/

OEI31

TX59/

OEI27

TX55/

OEI23

TX52/

OEI20

RX55

RX52

RX48

RX44

RX41

TX47/

OEI15

TX45/

OEI13

TX44/

OEI12

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

D

E

F

G

H

J

K

L

M

N

P

R

T

16

5905 drw02

NOTE:

1. NC = No Connect

PBGA: 1mm pitch, 17mm x 17mm (BB208-1, order code: BB)

TOP VIEW

2

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

PIN CONFIGURATIONS (CONTINUED)

TX19

TX18

TX17

TX16

RX23

RX22

RX21

RX20

RX19

RX18

RX17

RX16

RX15

RX14

RX13

RX12

RX11

RX10

RX9

RX8

TX15

TX14

TX13

TX12

GND

VCC

TX11

TX10

TX9

TX8

GND

VCC

TX7

TX6

TX5

TX4

GND

VCC

TX3

TX2

TX1

TX0

RX7

RX6

RX5

RX4

RX3

RX2

RX1

RX0

ODE

R ESET

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

GND

CLK

FP

FE/HCLK

WFPS

TMS

TDI

TDO

TCK

TR ST

DS

CS

R/W

VCC

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

NC(1)

D TA

D15

D14

D13

D12

VCC

GND

D11

D10

D9

D8

VCC

GND

D7

D6

D5

D4

VCC

GND

D3

D2

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

·

PIN 1

TX44/OEI12

TX45/OEI13

TX46/OEI14

TX47/OEI15

RX40

RX41

RX42

RX43

RX44

RX45

RX46

RX47

RX48

RX49

RX50

RX51

RX52

RX53

RX54

RX55

TX48/OEI16

TX49/OEI17

TX50/OEI18

TX51/OEI19

GND

VCC

TX52/OEI20

TX53/OEI21

TX54/OEI22

TX55/OEI23

GND

VCC

TX56/OEI24

TX57/OEI25

TX58/OEI26

TX59/OEI27

GND

VCC

TX60/OEI28

TX61/OEI29

TX62/OEI30

TX63/OEI31

RX56

RX57

RX58

RX59

RX60

RX61

RX62

RX63

D0

D1

NOTE:

1. NC = No Connect

PQFP: 0.50mm pitch, 28mm x 28mm (DR208-1, order code: DR)

TOP VIEW

3

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

VCC

GND

TX20

TX21

TX22

TX23

VCC

GND

TX24

TX25

TX26

TX27

VCC

GND

TX28

TX29

TX30

TX31

RX24

RX25

RX26

RX27

RX28

RX29

RX30

RX31

RX32

RX33

RX34

RX35

RX36

RX37

RX38

RX39

TX32/OEI0

TX33/OEI1

TX34/OEI2

TX35/OEI3

GND

VCC

TX36/OEI4

TX37/OEI5

TX38/OEI6

TX39/OEI7

GND

VCC

TX40/OEI8

TX41/OEI9

TX42/OEI10

TX43/OEI11

GND

VCC

5905 drw03

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

PIN DESCRIPTION

SYMBOL

NAME

I/O DESCRIPTION

A0-15

Address 0 to 15

I

These address lines access all internal memories.

CLK

Clock

I

Serial clock for shifting data in/out on the serial data streams. Depending upon the value programmed, this

input accepts a 4.096, 8.192 or 16.384 MHz clock. See the Control Register bits on Table 5 for the values.

CS

D0-15

Chip Select

Data Bus 0-15

DS

Data Strobe

I

This active LOW input works in conjunction with CS to enable the read and write operations and enables the

data bus lines (D0-D15).

DTA

Data Transfer

Acknowledgment

O

Indicates that a data bus transfer is complete. When the bus cycle ends, this pin drives HIGH and then goes

high-impedance, allowing for faster bus cycles with a weaker pull-up resistor. A pull-up resistor is required

to hold a HIGH level when the pin is in high-impedance.

FE/HCLK Frame Evaluation/

HCLK Clock

I

When the WFPS pin is LOW, this pin is the frame measurement input. When the WFPS pin is HIGH, the

HCLK (4.096 MHZ clock) is required for frame alignment in the wide frame pulse mode (WFPS). (1)

FP

Frame Pulse

I

GND

ODE

Ground

Output Drive Enable

I

RESET

Device Reset

I

R/W

RX0-63

I

I

TCK

TDI

Read/Write

Data Stream

Input 0 to 63

Test Clock

Test Serial Data In

I

I

TDO

Test Serial Data Out

O

TMS

Test Mode Select

I

TRST

Test Reset

I

When the WFPS pin is LOW, this input accepts and automatically identifies frame synchronization signals

formatted according to ST-BUS® and GCI specifications. When pin WFPS is HIGH, this pin accepts a

negative frame pulse, which conforms to the WFPS format.

Ground Rail.

This is the output enable control for the TX serial outputs. When the ODE input is LOW and the Output Stand

By bit of the Control Register is LOW, all TX outputs are in a high-impedance state. If this input is HIGH, the TX

output drivers are enabled. However, each channel may still be put into a high-impedance state by using the

per-channel control bit in the Connection Memory.

This input puts the IDT72V71660 into a reset state that clears the device internal counters, registers and

brings TX0-63 and D0-D15 into a high-impedance state. The RESET pin must be held LOW for a

minimum of 20ns to properly reset the device.

This input controls the direction of the data bus lines (D0-D15) during a microprocessor access.

Serial data input stream. These streams may have a data rate of 2.048Mb/s, 4.096Mb/s, 8.192Mb/s, or

16.384Mb/s, depending upon the value programmed in the Control Register.

Provides the clock to the JTAG test logic.

JTAG serial test instructions and data are shifted in on this pin. This pin is pulled HIGH by an internal pull-up

when not driven.

JTAG serial data is output on this pin on the falling edge of TCK. This pin is held in high-impedance state

when JTAG scan is not enabled.

JTAG signal that controls the state transitions of the Test Access Port controller. This pin is pulled HIGH by an

internal pull-up when not driven.

Asynchronously initializes the JTAG Test Access Port controller by putting it in the Test-Logic-Reset state. This

pin is pulled by an internal pull-up when not driven. This pin should be pulsed LOW on power-up, or held LOW,

to ensure that the IDT72V71660 is in the normal functional mode.

Serial data output stream. These streams may have a data rate of 2.048Mb/s, 4.096Mb/s, 8.192Mb/s,

or 16.384Mb/s, depending upon the value programmed in the Control Register.

When all 64 output streams are selected via Control Register, these pins are the output streams TX32 to TX63

and may operate at a data rate of 2.048Mb/s, 4.096Mb/s, 8.192Mb/s, or 16.384Mb/s. When output enable

function is selected, these pins reflect the active or high-impedance status for the

corresponding output stream OEI0-31.

+3.3 Volt Power Supply.

When 1, enables the wide frame pulse (WFPS) Frame Alignment interface. When 0, the device operates in

ST-BUS® /GCI mode.(2)

TX0-31

TX Output 0 to 31

(Three-state Outputs)

TX32-63/ TX Output 32 to 63/

OEI0-31 Output Enable

Indication 0 to 31

(Three-state Outputs)

V CC

V CC

WFPS

Wide Frame Pulse Select

I This active LOW input is used by a microprocessor to activate the microprocessor port of IDT72V71660.

I/O These pins are the data bits of the microprocessor port.

O

O

I

NOTES:

1. For compatibility with the IDT72V73273/63 device, this pin should be logic High.

2. For compatibility with the IDT72V73273/63 device, this pin should be logic Low.

4

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

DESCRIPTION (CONTINUED)

setup the device. The IDT72V71660 provides two different interface timing

modes, ST-BUS® or GCI. The IDT72V71660 automatically detects the presence of an input frame pulse and identifies it as either ST-BUS® or GCI.

In ST-BUS®, when running at 16.384 MHz, data is clocked out on the falling

edge and is clocked in on the subsequent rising-edge. At all other data rates,

there are two clock cycles per bit and every second falling edge of the master

clock marks a bit boundary and the data is clocked in on the rising edge of CLK,

three quarters of the way into the bit cell. See Figure 14 for timing.

In GCI format, when running at 16.384 MHz, data is clocked out on the rising

edge and is clocked in on the subsequent falling edge. At all other data rates,

there are two clock cycles per bit and every second rising edge of the master

clock marks the bit boundary and data is clocked in on the falling edge of CLK

at three quarters of the way into the bit cell. See Figure 15 for timing.

The 64 serial input streams (RX) of the IDT72V71660 can run up to

16.384Mb/s allowing 256 channels per 125μs frame. The data rates on the

output streams (TX) are identical to those on the input streams (RX).

With two main operating modes, Processor Mode and Connection Mode, the

IDT72V71660 can easily switch data from incoming serial streams (Data

Memory) or from the controlling microprocessor via Connection Memory. As

control and status information is critical in data transmission, the Processor Mode

is especially useful when there are multiple devices sharing the input and output

streams.

With data coming from multiple sources and through different paths, data

entering the device is often delayed. To handle this problem, the IDT72V71660

has a Frame Evaluation feature to allow individual streams to be offset from the

frame pulse in half clock-cycle intervals up to +7.5 clock cycles.

The IDT72V71660 also provides a JTAG Test Access Port, memory block

programming, a simple microprocessor interface and automatic ST-BUS® /GCI

sensing to shorten setup time, aid in debugging and ease use of the device

without sacrificing capabilities.

INPUT FRAME OFFSET SELECTION

Input frame offset selection allows the channel alignment of individual input

streams to be offset with respect to the output stream channel alignment . Although

all input data comes in at the same speed, delays can be caused by variable

path serial backplanes and variable path lengths which may be implemented

in large centralized and distributed switching systems. Because data is often

delayed, this feature is useful in compensating for the skew between input

streams.

Each input stream can have its own delay offset value by programming the

frame input offset registers (FOR, Table 8). The maximum allowable skew is +7.5

master clock (CLK) periods forward with a resolution of ½ clock period, see

Table 9. The output frame cannot be adjusted.

FUNCTIONAL DESCRIPTION

DATA AND CONNECTION MEMORY

All data that comes in through the RX inputs go through a serial-to-parallel

conversion before being stored into internal Data Memory. The 8 KHz frame

pulse (FP) is used to mark the 125μs frame boundaries and to sequentially

address the input channels in Data Memory.

Data output on the TX streams may come from either the serial input streams

(Data Memory) or from the microprocessor (Connection Memory). In the case

that RX input data is to be output, the addresses in Connection Memory are used

to specify a stream and channel of the input. The Connection Memory is setup

in such a way that each location corresponds to an output channel for each

particular stream. In that way, more than one channel can output the same data.

In Processor Mode, the microprocessor writes data to the Connection Memory

locations corresponding to the stream and channel that is to be output. The lower

half (8 least significant bits) of the Connection Memory is output every frame until

the microprocessor changes the data or mode of the channel. By using this

Processor Mode capability, the microprocessor can access input and output

time-slots on a per-channel basis.

The two most significant bits of the Connection Memory are used to control

the per-channel mode of the out put streams. Specifically, the MOD1-0 bits are

used to select Processor Mode, Constant or Variable delay Mode, and the highimpedance state of output drivers. If the MOD1-0 bits are set to 1-1 accordingly,

only that particular output channel (8 bits) will be in the high-impedance state.

If however, the ODE input pin is LOW and the Output Standby Bit in the Control

Register is LOW, all of the outputs will be in a high-impedance state even if a

particular channel in Connection Memory has enabled the output for that

channel. In other words, the ODE pin and Output Stand By control bit are master

output enables for the device (See Table 3).

SERIAL INPUT FRAME ALIGNMENT EVALUATION

The IDT72V71660 provides the Frame Evaluation input to determine

different data input delays with respect to the frame pulse FP. A measurement

cycle is started by setting the Start Frame Evaluation bit of the Control Register

LOW for at least one frame. When the Start Frame Evaluation bit in the Control

Register is changed from LOW to HIGH, the evaluation starts. Two frames later,

the Complete Frame Evaluation bit of the Frame Alignment Register changes

from LOW to HIGH to signal that a valid offset measurement is ready to be read

from bits 0 to 11 of the Frame Alignment Register. The Start Frame Evaluation

bit must be set to zero before a new measurement cycle is started.

In ST-BUS ® mode, the falling edge of the frame measurement signal (Frame

Evaluation) is evaluated against the falling edge of the ST-BUS ® frame pulse.

In GCI mode, the rising edge of Frame Evaluation is evaluated against the rising

edge of the GCI frame pulse. See Table 7 and Figure 1 for the description of

the Frame Alignment Register.

MEMORY BLOCK PROGRAMMING

The IDT72V71660 provides users with the capability of initializing the entire

Connection Memory block in two frames. To set bits 14 and 15 of every

Connection Memory location, first program the desired pattern in the Block

Programming Data Bits (BPD 1-0), located in bits 7 and 8 of the Control Register.

The block programming mode is enabled by setting the Memory Block

Program bit of the Control Register HIGH. When the Block Programming Enable

bit of the Control Register is set to HIGH, the Block Programming Data will be

loaded into the bits 14 and 15 of every Connection Memory location. The other

Connection Memory bits (bit 0 to bit 13) are loaded with zeros. When the memory

block programming is complete, the device resets the Block Programming

Enable , BPD 1-0 and MBP bits to zero.

SERIAL DATA INTERFACE TIMING

When a 16.384Mb/s serial data rate is required, the master clock frequency

will be running at 16.384 MHz resulting in a single-bit per clock. For all other

cases, 2.048Mb/s, 4.096Mb/s, and 8.192Mb/s, the master clock frequency will

be twice the data rate on the serial streams, resulting in two clocks per bit. Use

Table 5 to determine clock speed and the DR1-0 bits in the Control Register to

5

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

DELAY THROUGH THE IDT72V71660

The data in the Control Register consists of the Memory Block Programming

bit, the Block Programming Data bits, the Begin Block Programming Enable, the

Output Stand By, Start Frame Evaluation, Output Enable Indication and Data

Rate Select bits. As explained in the Memory Block Programming section, the

Block Programming Enable begins the programming if the MBP bit is enabled.

This allows the entire Connection Memory block to be programmed with the

Block Programming Data bits. If the ODE pin is LOW, the Output Stand By bit

enables (if HIGH) or disables (if LOW) all TX output drivers. If the ODE pin is

HIGH, the Output Stand By bit is ignored and all TX output drivers are enabled.

The switching of information from the input serial streams to the output serial

streams results in a throughput delay. The device can be programmed to

perform time-slot interchange functions with different throughput delay capabilities on a per-channel basis. For voice applications, variable throughput delay

is best as it ensure minimum delay between input and output data. In wideband

data applications, constant throughput delay is best as the frame integrity of the

information is maintained through the switch.

The delay through the device varies according to the type of throughput delay

selected in the Switching Mode Selection bits of the Connection Memory.

SOFTWARE RESET

The Software Reset serves the same function as the hardware reset. As

with the hard reset, the Software Reset must also be set HIGH for 20ns before

bringing the Software Reset LOW again for normal operation. Once the Software

Reset is LOW, internal registers and other memories may be read or written.

During Software Reset, the microprocessor port is still able to read from all

internal memories. The only write operation allowed during a Software Reset

is to the Software Reset bit in the Control Register to complete the Software Reset.

VARIABLE DELAY MODE (MOD1-0 = 0-0)

In this mode, the delay is dependent only on the combination of source and

destination channels and is independent of input and output streams. The

minimum delay achievable in the IDT72V71660 is three time-slots. If the input

channel data is switched to the same output channel (channel n, frame p), it will

be output in the following frame (channel n, frame p+1). The same is true if the

input channel n is switched to output channel n+1 or n+2. If the input channel

n is switched to output channel n+3, n+4,..., the new output data will appear in

the same frame. Table 2 shows the possible delays for the IDT72V71660 in

Variable Delay mode.

CONNECTION MEMORY CONTROL

If the ODE pin and the Output Stand By bit are LOW, all output channels will

be in three-state. See Table 3 for detail.

If MOD1-0 of the Connection Memory is 1-0 accordingly, the output channel

will be in Processor Mode. In this case the lower eight bits of the Connection

Memory are output each frame until the MOD1-0 bits are changed. If MOD10 of the Connection Memory are 0-1 accordingly, the channel will be in Constant

Delay Mode and bits 13-0 are used to address a location in Data Memory. If

MOD1-0 of the Connection Memory are 0-0, the channel will be in Variable

Delay Mode and bits 13-0 are used to address a location in Data Memory. If

MOD 1-0 of the Connection Memory are 1-1, the channel will be in high

Impedance mode and that channel will be in three-state.

CONSTANT DELAY MODE (MOD1-0 = 0-1)

In this mode, frame integrity is maintained in all switching configurations by

making use of a multiple data memory buffer. Input channel data is written into

the data memory buffers during frame n will be read out during frame n+2. In

the IDT72V71660, the minimum throughput delay achievable in Constant Delay

mode will be one frame plus one channel. See Table 1.

MICROPROCESSOR INTERFACE

OUTPUT ENABLE INDICATION

The IDT72V71660 has the capability to indicate the state of the outputs (active

or three-state) by enabling the Output Enable Indication in the Control Register.

In the Output Enable Indication mode however, only half of the output streams

are available. If this same capability is desired with all 64 streams, this can be

accomplished by using two IDT72V71660 devices. In one device, the All Output

Enable bit is set to a one while in the other the All Output Enable is set to zero.

In this way, one device acts as the switch and the other as a three-state control

device, see Figure 5. It is important to note if the TSI device is programmed for

All Output Enables and the Output Enable Indication is also set, the device will

be in the All Output Enables mode not Output Enable Indication. To use all 64

streams, set Output Enable Indication in the Control Register to zero.

The IDT72V71660’s microprocessor interface looks like a standard RAM

interface to improve integration into a system. With a 16-bit address bus and a

16-bit data bus, reads and writes are mapped directly into Data and Connection

Memories and require only one clock cycle to access. By allowing the internal

memories to be randomly accessed in one cycle, the controlling microprocessor

has more time to manage other peripheral devices and can more easily and

quickly gather information and setup the switch paths. Table 4 shows the

mapping of the addresses into internal memory blocks.

MEMORY MAPPING

The address bus on the microprocessor interface selects the internal registers

and memories of the IDT72V71660.

The two most significant bits of the address select between the registers, Data

Memory, and Connection Memory. If A15 and A14 are HIGH, A13-A0 are used

to address the Data Memory. If A15 is HIGH and A14 is LOW, A13-A0 are used

to address Connection Memory. If A15 is LOW and A14 is HIGH A13-A0 are

used to select the Control Register, Frame Alignment Register, and Frame Offset

Registers. See Table 4 for mappings.

As explained in the Serial Data Interface Timing and Switching Configurations

sections, after system power-up, the Control Register should be programmed

immediately to establish the desired switching configuration.

INITIALIZATION OF THE IDT72V71660

After power up, the state of the Connection Memory is unknown. As such,

the outputs should be put in high-impedance by holding the ODE pin LOW. While

the ODE is LOW, the microprocessor can initialize the device by using the Block

Programming feature and program the active paths via the microprocessor bus.

Once the device is configured, the ODE pin (or Output Stand By bit depending

on initialization) can be switched to enable the TSI switch.

6

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

TABLE 1 — CONSTANT THROUGHPUT

DELAY VALUE

TABLE 2 — VARIABLE THROUGHPUT

DELAY VALUE

Delay for Variable Throughput Delay Mode

(m – output channel number; n – input channel number)

Input Rate

Delay for Constant Throughput Delay Mode

(m – output channel number)

(n – input channel number)

Input Rate

2.048Mb/s

32 + (32 – n) +m time-slots

2.048Mb/s

4.096Mb/s

64 + (64 – n) +m time-slots

4.096Mb/s

64 – (n-m) time-slots

(m-n) time-slots

8.192Mb/s

128 + (128 – n) +m time-slots

8.192Mb/s

128 – (n-m) time-slots

(m-n) time-slots

16.384Mb/s

256 + (256 – n) +m time-slots

16.384Mb/s

256 – (n-m) time-slots

(m-n) time-slots

m ≤ n+2

m > n+2

32 – (n-m) time-slots

(m-n) time-slots

TABLE 3 — OUTPUT HIGH-IMPEDANCE CONTROL

Bits MOD1-0 Values in

Connection Memory

ODE pin

OSB bit in Control

Register

Output Status

1 and 1

Don’t Care

Don’t Care

Per-channel

high-Impedance

Any, other than 1 and 1

0

0

high-Impedance

Any, other than 1 and 1

0

1

Enable

Any, other than 1 and 1

1

0

Enable

Any, other than 1 and 1

1

1

Enable

TABLE 4 — INTERNAL REGISTER AND ADDRESS MEMORY MAPPING

A15

A14 A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

R/W

Location

R

Data Memory

R/W

Connection Memory

R/W

Control Register

1

1

STA5

STA4

STA3

STA2

STA1

STA0

CH7

CH6

CH5

CH4

CH3

CH2 CH1 CH0

1

0

STA5

STA4

STA3

STA2

STA1

STA0

CH7

CH6

CH5

CH4

CH3

CH2 CH1 CH0

0

1

0

0

0

0

0

x

x

x

x

x

x

x

x

x

0

1

0

0

0

0

1

x

x

x

x

x

x

x

x

x

R

Frame Align Register

0

1

1

0

0

0

0

x

x

x

x

x

x

x

x

x

R/W

Frame Offset Register 0

0

1

1

0

0

0

1

x

x

x

x

x

x

x

x

x

R/W

Frame Offset Register 1

0

1

1

0

0

1

0

x

x

x

x

x

x

x

x

x

R/W

Frame Offset Register 2

0

1

1

0

0

1

1

x

x

x

x

x

x

x

x

x

R/W

Frame Offset Register 3

0

1

1

0

1

0

0

x

x

x

x

x

x

x

x

x

R/W

Frame Offset Register 4

0

1

1

0

1

0

1

x

x

x

x

x

x

x

x

x

R/W

Frame Offset Register 5

0

1

1

0

1

1

0

x

x

x

x

x

x

x

x

x

R/W

Frame Offset Register 6

0

1

1

0

1

1

1

x

x

x

x

x

x

x

x

x

R/W

Frame Offset Register 7

0

1

1

1

0

0

0

x

x

x

x

x

x

x

x

x

R/W

Frame Offset Register 8

0

1

1

1

0

0

1

x

x

x

x

x

x

x

x

x

R/W

Frame Offset Register 9

0

1

1

1

0

1

0

x

x

x

x

x

x

x

x

x

R/W

Frame Offset Register 10

0

1

1

1

0

1

1

x

x

x

x

x

x

x

x

x

R/W

Frame Offset Register 11

0

1

1

1

1

0

0

x

x

x

x

x

x

x

x

x

R/W

Frame Offset Register 12

0

1

1

1

1

0

1

x

x

x

x

x

x

x

x

x

R/W

Frame Offset Register 13

0

1

1

1

1

1

0

x

x

x

x

x

x

x

x

x

R/W

Frame Offset Register 14

0

1

1

1

1

1

1

x

x

x

x

x

x

x

x

x

R/W

Frame Offset Register 15

NOTE: Unused STA and CH bits should be set to zero.

7

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

TABLE 5 — CONTROL REGISTER (CR) BITS

Reset Value:

0000H.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

SRS

OEI

OEPOL

AOE

0

0

MBP

BPD1

BPD0

BPE

OSB

SFE

0

0

DR1

DR0

BIT

NAME

DESCRIPTION

15

SRS

(Software Reset)

A one will reset the device and have the same effect as the RESET pin. Must be zero for normal operation.

14

OEI

(Output Enable Indication)

When 1, the TX32-63/OEI0-31 pins will be OEI0-31 and reflect the active or high-impedance state of their corresponding output data

streams. When 0, this feature is disabled and these pins are used as output data streams TX32-63.

13

OEPOL

(Output Enable Polarity)

When 1, a one on an Output Enable Indication pin denotes an active state on the output data stream; zero on an Output Enable Indication

pin denotes high-impedance state. When 0, a one on an Output Enable Indication pin denotes high-impedance and a zero denotes

an active state.

12

AOE

(All Output Enables)

When 1, TX0-63 will behave as OEI0-63 accordingly. These outputs will reflect the active or high-impedance state of the

corresponding output data streams (TX0-63) in another IDT72V71660 if programmed identically. When 0, the TSI operates in the normal

switch mode.

Unused

Must be zero for normal operation.

MBP

(Memory Block Program)

When 1, the Connection Memory block programming feature is ready for the programming of Connection Memory HIGH bits,

bit 14 and bit 15. When 0, this feature is disabled.

8-7

BPD1-0

(Block Programming

Data)

These bits carry the value to be loaded into the Connection Memory block whenever the memory block programming feature

is activated. After the Memory Block Program bit in the Control Register is set to 1 and the Block Programming Enable is set to 1,

the contents of the bits Block Programming Data1-0 are loaded into bit 15 and 14 of the Connection Memory. Bit 13 to bit 0 of the

Connection Memory are set to 0.

6

BPE

(Begin Block

Programming Enable)

A zero to one transition of this bit enables the memory block programming function. Once the Block Programming Enable

bit is set HIGH, the device requires two frames to complete the block programming. After the programming function has finished,

the Block Programming Enable, Memory Block Program and Block Programming Data1-0 bits will be reset to zero by the device

to indicate the operation is complete.

5

OSB

(Output Stand By)

When ODE = 0 and Output Stand By = 0, the output drivers of the transmit serial streams are in high-impedance mode. When

either ODE = 1 or Output Stand By =1 the output serial streams drivers function normally.

4

SFE

(Start Frame Evaluation)

A zero to one transition in this bit starts the Frame Evaluation procedure. When the Complete Frame Evaluation bit in the Frame Alignment

Register changes from zero to one, the evaluation procedure stops. To start another Frame Evaluation cycle, set this bit to zero for

at least one frame.

3-2

Unused

Must be zero for normal operation.

1-0

DR1-0

(Data Rate Select)

11-10

9

DR1

0

0

1

1

DR0

0

1

0

1

8

Data Rate

2.048Mb/s

4.096Mb/s

8.192Mb/s

16.384Mb/s

Master Clock

4.096 MHz

8.192 MHz

16.384 MHz

16.384 MHz

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

TABLE 6 — CONNECTION MEMORY BITS

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

MOD1

MOD0

SAB5

SAB4

SAB3

SAB2

SAB1

SAB0

CAB7

CAB6

CAB5

CAB4

CAB3

CAB2

CAB1

CAB0

Bit

Name

15, 14 MOD1-0

(Switching Mode Selection)

Description

MOD1 MOD0

0

0

0

1

1

0

1

1

MODE

Variable Delay mode

Constant Delay mode

Processor mode

Output high-impedance

13-8

SAB5-0

(Source Stream Address Bits)

The binary value is the number of the data stream for the source of the connection.

7-0

CAB7-0

The binary value is the number of the channel for the source of the connection.

(Source Channel Address Bits)

NOTE:

1. Unused Source Stream Address Bits and Source Channel Address Bits bits should be set to zero.

9

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

TABLE 7 — FRAME ALIGNMENT REGISTER (FAR) BITS

Reset Value:

0000H.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

0

0

CFE

FD11

FD10

FD9

FD8

FD7

FD6

FD5

FD4

FD3

FD2

FD1

FD0

Bit

Name

Description

15-13

Unused

Must be zero for normal operation

12

CFE (Complete

Frame Evaluation)

When Complete Frame Evaluation = 1, the Frame Evaluation is completed and bits FD11 to FD0 bits contains a valid frame alignment offset.

This bit is reset to zero, when Start Frame Evaluation bit in the Control Register is changed from 1 to 0.

11

FD11

The falling edge of Frame Evaluation (or rising edge for GCI mode) is sampled during the CLK-HIGH phase (FD11 = 1) or during the CLK(Frame Delay Bit 11) LOW phase (FD11 = 0). This bit allows the measurement resolution to ½ CLK cycle. This bit is reset to zero when the Start Frame Evaluation

bit of the Control Register changes from 1 to 0.

10-0

FD10-0

(Frame Delay Bits)

The binary value expressed in these bits refers to the measured input offset value. These bits are reset to zero when the Start Frame Evaluation

bit of the Control Register changes from 1 to 0. (FD10 – MSB, FD0 – LSB)

ST-BUS®

Frame

CLK

0

Offset

Value

1

2

3

4

5

6

7

8

9

1

0

1

1

1

2

1

3

1

4

1

5

1

2

1

3

1

4

1

5

FE

Input

(FD[10:0] = 06H)

(FD11 = 0, sample at CLK LOW

phase)

GCI

Frame

CLK

Offset

Value

0

1

2

3

4

5

6

7

8

9

1

0

1

1

FE

Input

(FD[10:0] = 09H)

(FD11 = 1, sample at CLK HIGH

phase)

5905

drw04

Figure 1. Example for Frame Alignment Measurement

10

1

6

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

TABLE 8 — FRAME INPUT OFFSET REGISTER (FOR) BITS

Reset Value:0000H for all FOR registers.

Register

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

FOR0 Register

OF32

OF31

OF30

DLE3

OF22

OF21

OF20

DLE2

OF12

OF11

OF10

DLE1

OF02

OF01

OF00

DLE0

FOR1 Register

OF72

OF71

OF70

DLE7

OF62

OF61

OF60

DLE6

OF52

OF51

OF50

DLE5

OF42

OF41

OF40

DLE4

FOR2 Register

OF112 OF111 OF110 DLE11 OF102 OF101 OF100 DLE10

OF92

OF91

OF90

DLE9

OF82

OF81

OF80

DLE8

FOR3 Register

OF152 OF151 OF150 DLE15 OF142 OF141 OF140 DLE14 OF132 OF131 OF130

DLE13 OF122 OF121 OF120 DLE12

FOR4 Register

OF192 OF191 OF190 DLE19 OF182 OF181 OF180 DLE18 OF172 OF171 OF170

DLE17 OD162 OD161 OF160 DLE16

FOR5 Register

OF232 OF231 OF230 DLE23 OF222 OF221 OF220 DLE22 OF212 OF211 OF210

DLE21 OF202 OF201 OF200 DLE20

FOR6 Register

OF272 OF271 OF270 DLE27 OF262 OF261 OF260 DLE26 OF252 OF251 OF250

DLE25 OF242 OF241 OF240 DLE24

FOR7 Register

OF312 OF311 OF310 DLE31 OF302 OF301 OF300 DLE30 OF292 OF291 OF290

DLE29 OF282 OF281 OF280 DLE28

FOR8 Register

OF352 OF351 OF350 DLE35 OF342 OF341 OF340 DLE34 OF332 OF331 OF330

DLE33 OF322 OF321 OF320 DLE32

FOR9 Register

OF392 OF391 OF390 DLE39 OF382 OF381 OF380 DLE38 OF372 OF371 OF370

DLE37 OF362 OF361 OF360 DLE36

FOR10 Register

OF432 OF431 OF430 DLE43 OF422 OF421 OF420 DLE42 OF412 OF411 OF410

DLE41 OF402 OF401 OF400 DLE40

FOR11 Register

OF472 OF471 OF470 DLE47 OF462 OF461 OF460 DLE46 OF452 OF451 OF450

DLE45 OF442 OF441 OF440 DLE44

FOR12 Register

OF512 OF511 OF510 DLE51 OF502 OF501 OF500 DLE50 OF492 OF491 OF490

DLE49 OF482 OF481 OF480 DLE48

FOR13 Register

OF552 OF551 OF550 DLE55 OF542 OF541 OF540 DLE54 OF532 OF531 OF530

DLE53 OF522 OF521 OF520 DLE52

FOR14 Register

OF592 OF591 OF590 DLE59 OF582 OF581 OF580 DLE58 OF572 OF571 OF570

DLE57 OF562 OF561 OF560 DLE56

FOR15 Register

OF632 OF631 OF630 DLE63 OF622 OF621 OF620 DLE62 OF612 OF611 OF610

DLE61 OF602 OF601 OF600 DLE60

Name(1)

Description

OFn2, OFn1, OFn0

(Offset Bits 2, 1 & 0)

These three bits define how long the serial interface receiver takes to recognize and store bit 0 from the RX input pin: i.e., to start a new frame.

The input frame offset can be selected to +7.5 clock periods from the point where the external frame pulse input signal is applied to the FP

input of the device. See Figure 2.

DLEn

ST-BUS® and

GCI mode:

DLEn = 0, offset is on the clock boundary

DLEn = 1, offset is a half clock cycle off of the clock boundary.

NOTE:

1. n denotes an input stream number from 0 to 63.

11

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

TABLE 9 — OFFSET BITS (OFn2, OFn1, OFn0, DLEn) & FRAME DELAY BITS

(FD11, FD2-0)

Input Stream

Measurement Result from

Corresponding

Frame Delay Bits

Offset Bits

Offset

FD11

FD2

FD1

FD0

OFn2

OFn1

OFn0

DLEn

No clock period shift (Default)

1

0

0

0

0

0

0

0

+ 0.5 clock period shift

0

0

0

0

0

0

0

1

+ 1.0 clock period shift

1

0

0

1

0

0

1

0

+ 1.5 clock period shift

0

0

0

1

0

0

1

1

+ 2.0 clock period shift

1

0

1

0

0

1

0

0

+ 2.5 clock period shift

0

0

1

0

0

1

0

1

+ 3.0 clock period shift

1

0

1

1

0

1

1

0

+ 3.5 clock period shift

0

0

1

1

0

1

1

1

+ 4.0 clock period shift

1

1

0

0

1

0

0

0

+ 4.5 clock period shift

0

1

0

0

1

0

0

1

+5.0 clock period shift

1

1

0

1

1

0

1

0

+5.5 clock period shift

0

1

0

1

1

0

1

1

+6.0 clock period shift

1

1

1

0

1

1

0

0

+6.5 clock period shift

0

1

1

0

1

1

0

1

+7.0 clock period shift

1

1

1

1

1

1

1

0

+7.5 clock period shift

0

1

1

1

1

1

1

1

FP (ST-BUS®)

CLK

RX Stream

(16.384 Mb/s)

Bit 7

RX Stream

(16.384 Mb/s)

RX Stream

(16.384 Mb/s)

Bit 6

Bit 5

Bit 4

offset = 0, DLE = 0

Bit 7

Bit 6

Bit 5

offset = 1, DLE = 0

Bit 7

Bit 6

offset = 0, DLE = 1

Bit 4

Bit 5

FP (GCI)

CLK

RX Stream

(16.384 Mb/s)

Bit 0

RX Stream

(16.384 Mb/s)

RX Stream

(16.384 Mb/s)

Bit 0

Bit 1

Bit 2

Bit 0

Bit 1

offset = 0, DLE = 0

offset = 1, DLE = 0

Bit 2

offset = 0, DLE = 1

Bit 2

Bit 1

5905 drw05

Figure 2. Examples for Input Offset Delay Timing in 16.384Mb/s mode

12

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

FP (ST-BUS®)

CLK

RX Stream

Bit 7

offset = 0, DLE = 0

RX Stream

offset = 1, DLE = 0

Bit 7

offset = 0, DLE = 1

Bit 7

RX Stream

offset = 1, DLE = 1

Bit 7

RX Stream

denotes the 3/4 point of the bit cell

FP (GCI)

CLK

RX Stream

Bit 0

offset = 0, DLE = 0

RX Stream

RX Stream

RX Stream

offset = 1, DLE = 0

Bit 0

offset = 0, DLE = 1

Bit 0

offset = 1, DLE = 1

Bit 0

denotes the 3/4 point of the bit cell

5905 drw06

Figure 2. Examples for Input Offset Delay Timing in 8.192Mb/s, 4.096Mb/s and 2.048Mb/s mode (Continued)

13

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

JTAG SUPPORT

The IDT72V71660 JTAG interface conforms to the Boundary-Scan standard

IEEE-1149.1. This standard specifies a design-for-testability technique called

Boundary-Scan test (BST). The operation of the boundary-scan circuitry is

controlled by an external Test Access Port (TAP) Controller.

TEST ACCESS PORT (TAP)

The Test Access Port (TAP) provides access to the test functions of the

IDT72V71660. It consists of three input pins and one output pin.

•Test Clock Input (TCK)

TCK provides the clock for the test logic. The TCK does not interfere with any

on-chip clock and thus remains independent. The TCK permits shifting of test

data into or out of the Boundary-Scan register cells concurrently with the

operation of the device and without interfering with the on-chip logic.

•Test Mode Select Input (TMS)

The logic signals received at the TMS input are interpreted by the Test Access

Port Controller to control the test operations. The TMS signals are sampled at

the rising edge of the TCK pulse. This pin is internally pulled to VCC when it is

not driven from an external source.

•Test Data Input (TDI)

Serial input data applied to this port is fed either into the instruction register

or into a test data register, depending on the sequence previously applied to

the TMS input. Both registers are described in a subsequent section. The

received input data is sampled at the rising edge of TCK pulses. This pin is

internally pulled to VCC when it is not driven from an external source.

•Test Data Output (TDO)

Depending on the sequence previously applied to the TMS input, the contents

of either the instruction register or data register are serially shifted out through

the TDO pin on the falling edge of each TCK pulse. When no data is shifted

through the boundary scan cells, the TDO driver is set to a high-impedance state.

•Test Reset (TRST)

Reset the JTAG scan structure. This pin is internally pulled to VCC when it

is not driven from an external source.

INSTRUCTION REGISTER

In accordance with the IEEE-1149.1 standard, the IDT72V71660 uses public

instructions. The IDT72V71660 JTAG interface contains a four-bit instruction

register. Instructions are serially loaded into the instruction register from the TDI

when the Test Access Port Controller is in its shift-IR state. Subsequently, the

instructions are decoded to achieve two basic functions: to select the test data

register that may operate while the instruction is current, and to define the serial

test data register path, which is used to shift data between TDI and TDO during

data register scanning. See Table 12 below for Instruction decoding.

TEST DATA REGISTER

As specified in IEEE-1149.1, the IDT72V71660 JTAG Interface contains two

test data registers:

•The Boundary-Scan register

The Boundary-Scan register consists of a series of Boundary-Scan cells

arranged to form a scan path around the boundary of the IDT72V71660 core

logic.

•The Bypass Register

The Bypass register is a single stage shift register that provides a one-bit path

from TDI to TDO. The IDT72V71660 boundary scan register bits are shown

in Table 14. Bit 0 is the first bit clocked out. All three-state enable bits are active

HIGH.

ID CODE REGISTER

As specified in IEEE-1149.1, this instruction loads the IDR with the Revision

Number, Device ID, and ID Register Indicator Bit. See Table 10.

TABLE 10 — IDENTIFICATION REGISTER DEFINITIONS

INSTRUCTION FIELD

Revision Number (31:28)

VALUE

0x0

DESCRIPTION

Reserved for version number

IDT Device ID (27:12)

0x434

Defines IDT part number

IDT JEDEC ID (11:1)

0x33

Allows unique identification of device vendor as IDT

ID Register Indicator Bit (Bit 0)

1

Indicates the presence of an ID register

TABLE 11 — SCAN REGISTER SIZES

REGISTER NAME

BIT SIZE

Instruction (IR)

4

Bypass (BYR)

1

Identification (IDR)

Boundary Scan (BSR)

32

Note(1)

NOTE:

1. The Boundary Scan Descriptive Language (BSDL) file for this device is available on

the IDT website (www.idt.com), or by contacting your local IDT sales representative.

14

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

TABLE 12 — SYSTEM INTERFACE PARAMETERS

INSTRUCTION

CODE

EXTEST

0000

Forces contents of the boundary scan cells onto the device outputs(1). Places the boundary scan register (BSR) between TDI and TDO.

BYPASS

1111

Places the bypass register (BYR) between TDI and TDO.

IDCODE

0010

Loads the ID register (IDR) with the vendor ID code and places the register between TDI and TDO.

HIGH-Z

0100

Places the bypass register (BYR) between TDI and TDO. Forces all device output drivers to a High-Z state.

CLAMP

0011

Places the bypass register (BYR) between \TDI and TDO. Forces contents of the boundary scan cells onto the device outputs.

SAMPLE/PRELOAD

0001

Places the boundary scan register (BSR) between TDI and TDO. SAMPLE allows data from device inputs(2) and outputs(1) to

be captured in the boundary scan cells and shifted serially through TDO. PRELOAD allows data to be input serially into the boundary

scan cells via the TDI.

RESERVED

DESCRIPTION

All other codes Several combinations are reserved. Do not use other codes than those identified above.

NOTES:

1. Device outputs = All device outputs except TDO.

2. Device inputs = All device inputs except TDI, TMS and TRST.

TABLE 13 — JTAG AC ELECTRICAL CHARACTERISTICS (1,2,3,4)

SYMBOL

MIN.

MAX.

UNITS

tJCYC

JTAG Clock Input Period

PARAMETER

100

⎯

ns

tJCH

JTAG Clock HIGH

40

⎯

ns

tJCL

JTAG Clock LOW

40

⎯

ns

tJR

JTAG Clock Rise Time

⎯

3(1)

ns

tJF

JTAG Clock Fall Time

⎯

3(1)

ns

tJRST

JTAG Reset

50

⎯

ns

tJRSR

JTAG Reset Recovery

50

⎯

ns

tJCD

JTAG Data Output

⎯

25

ns

tJDC

JTAG Data Output Hold

0

⎯

ns

tJS

JTAG Setup

15

⎯

ns

tJH

JTAG Hold

15

⎯

ns

NOTES:

1. Guaranteed by design.

2. 30pF loading on external output signals.

3. Refer to AC Electrical Test Conditions stated earlier in this document.

4. JTAG operations occur at one speed (10MHz). The base device may run at any speed specified in this datasheet.

tJCYC

tJR

tJF

tJCL

tJCH

TCK

Device Inputs(1)

TDI/TMS

tJH

tJS

tJDC

Device Outputs(2)

TDO

tJCD

tJRSR

5905 drw07

TRST

tJRST

NOTES:

1. Device inputs = All device inputs except TDI, TMS and TRST.

2. Device outputs = All device outputs except TDO.

Figure 3. JTAG TIming Specifications

15

x

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

TABLE 14 — BOUNDARY SCAN REGISTER BITS

Device Pin

ODE

RESET

CLK

FP

FE/HCLK

WFPS

DS

CS

R/W

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

DTA

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

RX63

RX62

RX61

RX60

RX59

RX58

RX57

RX56

Boundary Scan Bit 0 to bit 265

Input

Output

Three-State

Scan Cell

Scan Cell

Control

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

Device Pin

TX63/OEI31

TX62/OEI30

TX61/OEI29

TX60/OEI28

TX59/OEI27

TX58/OEI26

TX57/OEI25

TX56/OEI24

TX55/OEi23

TX54/OEi22

TX53/OEI21

TX52/OEI20

TX51/OEI19

TX50/OEI18

TX49/OE17

TX48/OEI16

RX55

RX54

RX53

RX52

RX51

RX50

RX49

RX48

RX47

RX46

RX45

RX44

RX43

RX42

RX41

RX40

TX47/OEI15

TX46/OEI14

TX45/OEI13

TX44/OEI12

TX43/OEI11

TX42/OEI10

TX41/OEI9

TX40/OEI8

TX39/OEI7

TX38/OEI6

TX37/OEI5

TX36/OEI4

TX35/OEI3

TX34/OEI2

TX33/OEI1

TX32/OEI0

16

Boundary Scan Bit 0 to bit 265

Input

Output

Three-State

Scan Cell

Scan Cell

Control

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

TABLE 14 — BOUNDARY SCAN REGISTER BITS (CONTINUED)

Device Pin

RX39

RX38

RX37

RX36

RX35

RX34

RX33

RX32

RX31

RX30

RX29

RX28

RX27

RX26

RX25

RX24

TX31

TX30

TX29

TX28

TX27

TX26

TX25

TX24

TX23

TX22

TX21

TX20

TX19

TX18

TX17

TX16

RX23

RX22

RX21

RX20

RX19

RX18

RX17

RX16

RX15

RX14

RX13

RX12

RX11

RX10

RX9

RX8

Boundary Scan Bit 0 to bit 265

Input

Output

Three-State

Scan Cell

Scan Cell

Control

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

220

221

222

223

224

225

Device Pin

TX15

TX14

TX13

TX12

TX11

TX10

TX9

TX8

TX7

TX6

TX5

TX4

TX3

TX2

TX1

TX0

RX7

RX6

RX5

RX4

RX3

RX2

RX1

RX0

17

Boundary Scan Bit 0 to bit 265

Input

Output

Three-State

Scan Cell

Scan Cell

Control

226

228

230

232

234

236

238

240

242

244

246

248

250

252

254

256

258

259

260

261

262

263

264

265

227

229

231

233

235

237

239

241

243

245

247

249

251

253

255

257

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

APPLICATIONS

CREATING LARGE SWITCH MATRICES

To create a switch matrix with twice the capacity of a given TSI device, four

devices must be used. In the example below, four IDT72V71660, 16K x 16K

channel capacity devices are used to create a 32K x 32K channel switch matrix.

As can be seen, Device #1 and Device #2 will receive the same incoming

RX0-63 data and thus have the same contents in Data Memory. On the output

side, however Device #1 is used to switch data out on to TX0-63 where as

RX0-63

RX64-127

Device #2 is used to switch out on TX 64-127. Likewise Device #3 and

Device #4 are used in the same way as Device #1 and Device #2 but

switch RX 64-127 to TX0-63 and TX 64-127, respectively. With this configuration all possible combinations of input and output streams are possible. In short,

Device #1 is used to switch RX0-63 to TX0-63, Device #2 to switch RX0-63

to TX64-127, Device #3 to switch RX 64-127 to TX0-63, and Device #4 to switch

RX64-127 to TX64-127.

Device 1

IDT72V71660

TX0-63

Device 2

IDT72V71660

TX64-127

Device 3

IDT72V71660

Device 4

IDT72V71660

5905 drw08

Figure 4. Creating Larger Switch Matrices

18

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

Using OEI

RX0-31

AOE=0

OEI =1

RX0-31

TX0-31

RX32-63

OEI0-31

AOE=0

OEI =0

RX0-31

TX0-31

RX32-63

RX32-63

TX0-31

TX32-63

TX32-63

AOE=0

OEI =1

RX0-31

TX0-31

OEI0-31

RX32-63

AOE=0

OEI =0

RX0-31

TX0-31

RX32-63

AOE=0

Using AOE

OEI32-63

OEI0-31

TX32-63

OEI =0

RX0

RX0

TX0

TX0

RX63

RX63

TX63

TX63

AOE=1

RX0

RX0

RX63

RX63

OEI =0

TX0

TX63

OEI0

OEI63

5905 drw09

Figure 5. Using All Output Enable (AOE)

19

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

RECOMMENDED OPERATING

CONDITIONS(1)

ABSOLUTE MAXIMUM RATINGS(1)

Symbol

VCC

Parameter

Min.

Max.

Unit

Supply Voltage

-0.5

+4.0

V

Vi

Voltage on Digital Inputs

GND -0.3

VCC +0.3

V

IO

Current at Digital Outputs

-50

50

mA

TS

Storage Temperature

-55

+125

°C

PD

Package Power Dissapation

⎯

2

W

Symbol

NOTE:

1. Exceeding these values may cause permanent damage. Functional operation under

these conditions is not implied.

Parameter

Min.

Typ.

Max.

Unit

VCC

Positive Supply

3.0

3.3

3.6

V

VIH

Input HIGH Voltage

2.0

⎯

VCC

V

VIL

Input LOW Voltage

-0.3

⎯

0.8

V

TOP

Operating Temperature

Industrial

-40

25

+85

°C

NOTE:

1. Voltages are with respect to Ground unless otherwise stated.

DC ELECTRICAL CHARACTERISTICS

Symbol

ICC

(2)

Parameter

Supply Current

@ 2.048Mb/s

@ 4.096Mb/s

@ 8.192Mb/s

@ 16.384Mb/s

Min.

Typ.

Max.

Units

-

-

80

90

130

140

mA

mA

mA

mA

-

-

60

μA

IIL(3,4)

Input Leakage (input pins)

IOZ(3,4)

high-impedance Leakage

-

-

60

μA

VOH(5)

Output HIGH Voltage

2.4

-

-

V

VOL(6)

Output LOW Voltage

-

-

0.4

V

NOTES:

1. Voltages are with respect to ground (GND) unless otherwise stated.

2. Outputs unloaded.

3. 0 ≤ V ≤ VCC.

4. Maximum leakage on pins (output or I/O pins in high-impedance state) is over an applied voltage (V).

5. IOH = 10 mA.

6. IOL = 10 mA.

20

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

AC ELECTRICAL CHARACTERISTICS - TIMING PARAMETER

MEASUREMENT VOLTAGE LEVELS

Symbol

Rating

Level

Unit

1.5

V

V TT

TTL Threshold

VHM

TTL Rise/Fall Threshold Voltage HIGH

2.0

V

VLM

TTL Rise/Fall Threshold Voltage LOW

0.8

V

1

ns

Input Pulse Levels

tr,tf

C

V

Input Rise/Fall Times

L (1)

Cin(2)

Input Timing Reference Levels

V

Output Reference Levels

V

Output Load

Input Capacitance

150

pF

8

pF

NOTES:

1. JTAG CL is 30pF

2. For 208 PQFP.

3.3v

VDD

330Ω

50Ω

D.U.T.

Z0 = 50Ω

I/O

510Ω

5905 drw10

30pF*

5905 Drw11

Figure 6. AC Termination

ΔtSOD

(Typical, ns)

6

5

4

Not

Yet

3

2

1

20 30 50

Cha

rac

teri

80 100

Capacitance (pF)

Figure 7. AC Test Load

zed

200

5905 drw12

Figure 8. Lumped Capacitive Load, Typical Derating

21

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

AC ELECTRICAL CHARACTERISTICS - FRAME PULSE AND CLOCK

Symbol

Parameter

tFPW

Frame Pulse Width (ST-BUS®, GCI)

Bit rate = 2.048Mb/s

Bit rate = 4.096Mb/s

Bit rate = 8.192Mb/s or 16.384Mb/s

Min.

Typ.

Max.

Units

26

26

26

⎯

⎯

⎯

295

145

65

ns

ns

ns

tFPS

Frame Pulse Setup time before CLK falling (ST-BUS® or GCI)

5

⎯

⎯

ns

tFPH

Frame Pulse Hold Time from CLK falling (ST-BUS® or GCI)

10

⎯

⎯

ns

tCP

CLK Period

Bit rate = 2.048Mb/s

Bit rate = 4.096Mb/s

Bit rate = 8.192Mb/s or 16.384Mb/s

190

110

55

244

122

61

300

150

70

ns

ns

ns

CLK Pulse Width HIGH

Bit rate = 2.048Mb/s

Bit rate = 4.096Mb/s

Bit rate = 8.192Mb/s or 16.384Mb/s

85

50

20

122

61

30

150

75

40

ns

ns

ns

CLK Pulse Width LOW

Bit rate = 2.048Mb/s

Bit rate = 4.096Mb/s

Bit rate = 8.192Mb/s or 16.384Mb/s

85

50

20

122

61

30

150

75

40

ns

ns

ns

tCH

tCL

tHFPW

Wide Frame Pulse Width

HCLK = 4.096Mb/s

244

ns

tHFPS

Frame Pulse Setup Time before HCLK @ 4.096 MHz falling

50

⎯

150

ns

tHFPH

Frame Pulse Hold Time from HCLK @ 4.096 MHz falling

50

⎯

150

ns

tHCP

HCLK Period

@ 4.096 MHz

190

244

300

ns

HCLK Pulse Width HIGH

@ 4.096Mb/s

110

122

150

ns

tHCL

HCLK Pulse Width LOW

@ 4.096Mb/s

110

122

150

ns

tHr, tHf

HCLK Rise/Fall Time

⎯

⎯

10

ns

tDIF

Delay between falling edge of HCLK and falling edge of CLK

-10

⎯

10

ns

tHCH

22

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

tODE(1)

RESET

tZR

tRZ

tRZ

tRS

TX

tODELZ

ODE

5905 drw13

NOTE:

1. To guarentee TX outputs remain in high-impedance.

Figure 9. RESET and ODE Timing

C 32i

(ST-BUS® mode)

C32i

(GCI mode)

tSOD

tCHZ

TX

VALID DATA

ODE

tCLZ

TX

tSIH

tODEA

tODEL

tODEHZ

Z

VALID DATA

5905 drw14

TX

VALID DATA

5905 drw15

Figure 10. Serial Output and External Control

Figure 11. Output Driver Enable (ODE)

23

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

AC ELECTRICAL CHARACTERISTICS - MICROPROCESSOR INTERFACE TIMING

Symbol

Parameter

tCSS

CS Setup from DS falling

Min.

Typ.

Max.

Units

0

⎯

⎯

ns

tRWS

tADS

R/W Setup from DS falling

3

⎯

⎯

ns

Address Setup from DS falling

2

⎯

⎯

ns

tCSH

tRWH

CS Hold after DS rising

0

⎯

⎯

ns

R/W Hold after DS Rising

3

⎯

⎯

ns

tADH

tDDR

Address Hold after DS Rising

2

⎯

⎯

ns

Data Setup from DTA LOW on Read

1

⎯

⎯

ns

tDHR

Data Hold on Read

10

tDSW

Data Setup on Write (Register Write)

10

15

25

ns

⎯

⎯

ns

tSWD

Valid Data Delay on Write (Connection Memory Write)

⎯

tDHW

Data Hold on Write

5

⎯

0

ns

⎯

⎯

tAKD

Acknowledgment Delay:

Reading/Writing Registers

Reading/Writing Memory

ns

32

345

200

120

ns

ns

ns

ns

ns

@ 2.048Mb/s

@ 4.096Mb/s

@ 8.192Mb/s or 16.384Mb/s

⎯

⎯

20

Data Strobe Setup Time

6

⎯

⎯

ns

Data Strobe Pulse Width High

28

—

—

ns

tAKH

Acknowledgment Hold Time

tDSS

tDSPW

24

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

CLK GCI

CLK ST-BUS®

tDSPW

tDSS

DS

tCSH

tCSS

CS

tRWH

tRWS

R/W

tADH

tADS

VALID ADDRESS

A0-A11

tDHR

D0-D15

READ

VALID READ DATA

tSWD

tDSW

D0-D15

WRITE

tDHW

VALID WRITE DATA

tDDR

tAKD

D TA

tAKH

5905 drw16

NOTE:

1. For quick microprocessor access tDSS must be met. In this case tAKD = tAKD (max) - CLK (period) tDSS.

Figure 12. Motorola Non-Multiplexed Bus Timing

25

�tFPS

tOEI

tOEI

tCLZ

tSOD

tFPW

tFPH

Bit 7

tCP

Bit 6

tCH

Bit 5

tCL

tr

Bit 4

tf

Bit 3

Bit 2

Figure 13. Output Enable Indicator Timing (8.192Mb/s ST-BUS® )

NOTES:

1. When Output Enable Polarity = 1, Output Enable Indication is HIGH when TX is active and LOW when TX is in three-state.

2. When Output Enable Polarity = 0, Output Enable Indication is LOW when TX is active and HIGH when TX is in three-state.

OEI(2)

OEI(1)

TX

CLK

FP

Bit 1

Bit 0

tOEI

tOEI

tCHZ

5905 drw17

IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

26

�IDT72V71660 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 16,384 x 16,384

INDUSTRIAL TEMPERATURE RANGE

AC ELECTRICAL CHARACTERISTICS ⎯ SERIAL STREAM (ST-BUS® and GCI)

Symbol

Parameter

tSIS

RX Setup Time

Min.

Typ.

Max.

Units

4

⎯

⎯

ns

tSIH

tSOD

RX Hold Time

8

⎯

⎯

ns

Clock to Valid Data

8

⎯

20

ns

tCHZ

Clock to High-Z

⎯

⎯

9

ns

tCLZ

Clock to Low-Z

3

⎯

⎯

ns

tODE

Output Driver Enable to Reset HIGH

5

⎯

⎯

ns

tODEHZ

Output Driver Enable (ODE) Delay

⎯

⎯

9

ns

tODELZ

Output Driver Enable (ODE) to Low-Z

5

⎯

⎯

ns

tOEI

Output Enable Indicator

8

⎯

20

ns

tRZ

Active to High-Z on Master Reset

⎯

⎯

12

ns

tZR

High-Z to Active on Master Reset

⎯

⎯

12

ns

tRS

Reset pulse width

20

⎯

⎯

ns

tODEA

Output Drive Enable to Active

6

⎯

16

ns

27

�RX 8 Mb/s

TX 8 Mb/s

HCLK4.096 MHz

CLK

FP

Bit 1

Bit 1

Bit 0

Bit 0

tDIF

tHFPS

tHFPW

tSIS

tSOD

tHFPH

Bit 7

Bit 7

tSIH

Bit 6

Bit 6

tCP

Figure 14. WFPS Timing

Bit 5

Bit 5

tr

tCH

Bit 4

Bit 4

tf

tCL

Bit 3

Bit 3

Bit 2

Bit 2

tHCL

tHr

Bit 1

Bit 1

tHCP

tHCH

Bit 0

Bit 0

5905 drw18

tHf

IDT72V71660 3.3V TIME SLOT INTERCHANGE