DATASHEET

15 Output PCIe G2/QPI Differential Buffer with

2:1 Input Mux

9EX21501A

Description

Features/Benefits:

The ICS9EX21501 provides 15 output clocks for PCIe Gen2

(100MHz) or QPI (133MHz) applications. A differential CPU clock

from a CK410B+ main clock generator, such as the ICS932S421,

drives the ICS9EX21501. In fanout mode, the ICS9EX21501

provides outputs up to 400MHz. A 2:1 input mux allows selection

between local and remote clock sources.

•

Recommended Application:

•

•

•

15 Output PCIe G2/QPI Differential Buffer with 2:1 input mux

•

Key Specifications:

•

•

•

•

DIF output cycle-to-cycle jitter < 50ps

DIF output-to-output skew < 150 ps

PCIe Gen2 compliant phase jitter

QPI 6.4Gb/s 12UI compliant phase jitter

Output clock frequencies up to 400 MHz/supports wide

range of applications

4 Selectable SMBus addresses/multiple devices can share

SMBus segment

SMBus address independent of PLL operating mode/

maximum flexibility

Dedicated CKPWRGD/PD# and VDDA pins/Easy board

design

8 Dedicated OE# and 2 Group OE# pins/Support for

hardware clock management

Output Features:

•

•

•

•

•

15 - 0.7V current-mode differential HCSL output pairs

Supports zero delay buffer mode and fanout mode

Selectable PLL bandwidth

80-150 MHz in PLL Mode

33-400 MHz operation in Bypass mode

Functional Block Diagram

OE13_14#

OE(5:12)#,

OE_01234#

10

CLKA_IN

CLKA_IN#

PLL

(SS Compatible)

15

DIF(14:0)

CLKB_IN

CLKB_IN#

HIBW_BYPM_LOBW#

100M_133M#

CKPWRGD/PD#

SMB_A0

SMB_A1

SEL_A_B#

SMBDAT

SMBCLK

Logic

IREF

IDT® 15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

1578—07/18/11

1

�9EX21501

15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

VDD

OE7#

DIF_7

DIF_7#

100M_133M#

SMBCLK

SMBDAT

SMB_A1

SMB_A0

SEL_A_B#

CKPWRGD/PD#

DIF_8

DIF_8#

OE8#

VDD

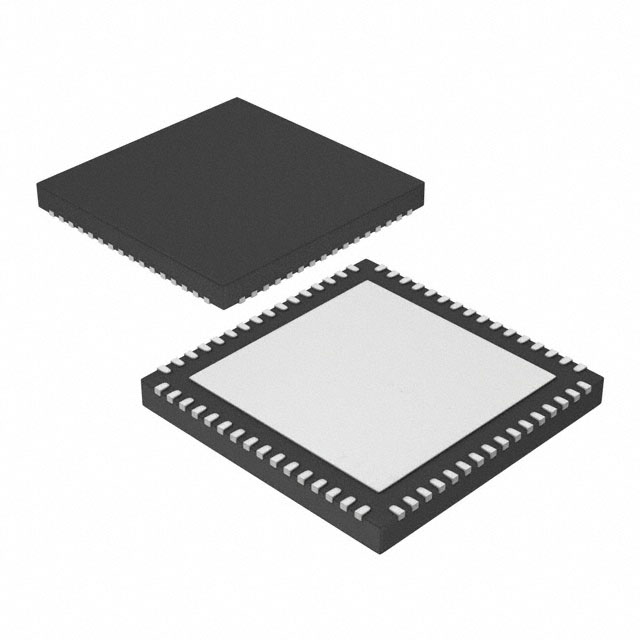

PIn Configuration

HIBW_BYPM_LOBW#

Datasheet

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

OE9#

DIF_9

DIF_9#

OE10#

DIF_10

DIF_10#

OE11#

DIF_11

DIF_11#

GND

VDD

DIF_12

DIF_12#

OE12#

DIF_13

DIF_13#

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

9EX21501

DIF_6#

DIF_6

OE6#

DIF_5#

DIF_5

OE5#

DIF_4#

DIF_4

DIF_3#

DIF_3

GND

VDD

DIF_2#

DIF_2

DIF_1#

DIF_1

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

DIF_0#

DIF_0

OE_01234#

VDD

CLKB_IN#

CLKB_IN

GND

CLKA_IN#

CLKA_IN

VDDA

GNDA

IREF

DIF_14#

DIF_14

OE13_14#

VDD

64-pin MLF

Power Groups

Frequency/Functionality Table

Byte 0,

bit 2

(100_133M#

Latch)

Byte 0,

bit 1

FSB

Byte 0,

bit 0

FSA

Input

MHz

1

0

1

0

0

0

1

1

1

0

1

0

0

0

0

1

0

0

1

1

0

100.00

133.33

166.67

200.00

266.67

333.33

400.00

1

1

1

DIF_x

MHz

100.00

133.33

166.67

200.00

266.67

333.33

400.00

Reserved

Notes

1

1

2

2

2

2

2

Pin Number

VDD

GND

23

22

29

26

11,17,37,49, 64

10, 38

Description

Main PLL, Analog

Input buffers

DIF clocks

Power Down Functionality

INPUTS

CKPWRGD/PD#

1

0

Input

Running

X

OUTPUTS

DIF_x

Running

Hi-Z

PLL State

ON

OFF

SMBus Address Selection (pins 57, 58)

SMB_A1

SMB_A0

Address

0

0

D4

0

1

D6

1

0

D8

1

1

DA

Notes:100M_133M#

1. Latch selects between 100 and 133 MHz.

This is equivalent to FSC in CK410B+/CK509B FS table.

2. Writing Byte 2 bits (2:0) can select other frequencies.

These frequencies are not characterized in PLL Mode

HIBW_BYPM_LOBW# Selection (Pin 54)

State

Voltage

Mode

Low

=200MHz

33

40

mA

1

IDD3.3VDDAOP

TA - TIND, All outputs active >=200MHz

33

40

mA

1

VDD Powerdown Current,

Industrial Temp

IDD3.3VDDPDZ

TA = TIND, All differential pairs Hi-Z

15

20

mA

1

VDDA Powerdown Current,

Industrial Temp

IDD3.3VDDAPDZ

TA = TIND, All differential pairs Hi-Z

16

20

mA

1

VDD Operating Current,

Commerical Temp

VDDA Operating Current,

Commercial Temp

VDD Operating Current,

Industrial Temp

VDDA Operating Current,

Industrial Temp

SYMBOL

CONDITIONS

IDD3.3VDDOP

MIN

UNITS NOTES

1

Guaranteed by design and characterization, not 100% tested in production.

IDT® 15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

7

1578—01/18/11

�9EX21501

15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

Datasheet

Electrical Characteristics - Skew and Differential Jitter Parameters

TA = TCOM or TIND; Supply Voltage VDD/VDDA = 3.3 V +/-5%, See Test Loads for Loading Conditions

PARAMETER

SYMBOL

CLK_IN, DIF[x:0], 100M

t SPO_PLL100M

CLK_IN, DIF[x:0], 133M

t SPO_PLL133M

CLK_IN, DIF[x:0]

t PD_BYP

CLK_IN, DIF[x:0]

tDSPO_PLL

CLK_IN, DIF[x:0]

t DSPO_BYP

CLK_IN, DIF[x:0]

t DTE

CLK_IN, DIF[x:0]

t DSSTE

DIF{x:0]

t SKEW_ALL

PLL Jitter Peaking

PLL Jitter Peaking

PLL Bandwidth

PLL Bandwidth

Duty Cycle

jpeak-hibw

jpeak-lobw

pllHIBW

pllLOBW

t DC

Duty Cycle Distortion

t DCD

Jitter, Cycle to cycle

t jcyc-cyc

CONDITIONS

Input-to-Output Skew in PLL mode

nominal value @ 25°C, 3.3V

Input-to-Output Skew in PLL mode

nominal value @ 25°C, 3.3V

Input-to-Output Skew in Bypass mode

nominal value @ 25°C, 3.3V

Input-to-Output Skew Varation in PLL

mode across voltage and temperature

Input-to-Output Skew Varation in

Bypass mode across voltage and

temperature

Random Differential Tracking error

beween two 9EX2 devices in Hi BW

Mode

Random Differential Spread Spectrum

Tracking error beween two 9EX2

devices in Hi BW Mode

Output-to-Output Skew

across all outputs

(Common to Bypass and PLL mode)

High Bandwidth

Low Bandwidth

High Bandwidth

Low Bandwidth

Measured differentially, PLL Mode

Measured differentially, Bypass Mode

@100MHz

PLL mode

Additive Jitter in Bypass Mode

MIN

TYP

MAX

UNITS NOTES

925

1019

1125

ps

1,2,4,5,8

1100

1120

1200

ps

1,2,4,5,8

4

4.6

5.2

ns

1,2,3,5,8

|258|

|350|

ps

1,2,3,5,6

,8

|771|

|900|

ps

1,2,3,5,6

,8

2

10

20

75

ps

1,2,3,5,8

,13

75

150

ps

1,2,8

0

0

2

0.7

45

2.3

2.5

2.5

0.87

49.6

3

3

4

1.4

55

dB

dB

MHz

MHz

%

7,8

7,8

8,9

8,9

1

-2

0.2

2

%

1,10

27

20

50

50

ps

ps

1

1

ps 1,2,3,5,8

(rms)

,12

Notes for preceding table:

Measured into fixed 2 pF load cap. Input to output skew is measured at the first output edge following the corresponding input.

1

2

Measured from differential cross-point to differential cross-point.

3

All Bypass Mode Input-to-Output specs refer to the timing between an input edge and the specific output edge created by it.

4

This parameter is deterministic for a given device

5

Measured with scope averaging on to find mean value.

6.

Long-term variation from nominal of input-to-output skew over temperature and voltage for a single device.

7

Measured as maximum pass band gain. At frequencies within the loop BW, highest point of magnification is called PLL jitter peaking.

8.

Guaranteed by design and characterization, not 100% tested in production.

9

Measured at 3 db down or half power point.

10

Duty cycle distortion is the difference in duty cycle between the output and the input clock when the device is operated in bypass mod

11

Measured from differential waveform

12.

This parameter is measured at the outputs of two separate ICS9EX21501 devices driven by a single CK410B+. The

ICS9EX21501's must be set to high bandwidth. Differential phase jitter is the accumulation of the phase jitter not shared by the outputs

(eg. not including the affects of spread spectrum). Target ranges of consideration are agents with BW of 1-22Mhz and 11-33Mhz.

13

Differential spread spectrum tracking error is the difference in spread spectrum tracking between two ICS9EX21501 devices This

parameter is measured at the outputs of two separate ICS9EX21501 devices driven by a single CK410B+ in Spread Spectrum mode.

The ICS9EX21501's must be set to high bandwidth. The spread spectrum characteristics are: maximum of 0.5%, 30-33KHz

modulation frequency, triangle profile.

IDT® 15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

1578—01/18/11

8

�9EX21501

15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

Datasheet

HCSL Differential Output Test Load

Zo= differential impedance

Rs

2pF

Rs

Rp

HCSL Output

2pF

Rp

Differential Output Termination Table

DIF Zo (Ω) Iref (Ω)

100

85

475

412

Rs (Ω)

Rp (Ω)

CL (pF)

33

27

50

43.2

2

2

Test Load

IDT® 15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

1578—01/18/11

9

�9EX21501

15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

Datasheet

General SMBus serial interface information for the 9EX21501

How to Write:

How to Read:

Controller (host) sends a start bit.

Controller (host) sends the write address D4 (H)

ICS clock will acknowledge

Controller (host) sends the beginning byte location = N

ICS clock will acknowledge

Controller (host) sends the data byte count = X

ICS clock will acknowledge

Controller (host) starts sending Byte N through

Byte N + X -1

• ICS clock will acknowledge each byte one at a time

• Controller (host) sends a Stop bit

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Index Block Write Operation

Controlle r (Host)

starT bit

T

Slave Address D4(H )

W Rite

WR

Controller (host) will send start bit.

Controller (host) sends the write address D4 (H)

ICS clock will acknowledge

Controller (host) sends the begining byte

location = N

ICS clock will acknowledge

Controller (host) will send a separate start bit.

Controller (host) sends the read address D5 (H)

ICS clock will acknowledge

ICS clock will send the data byte count = X

ICS clock sends Byte N + X -1

ICS clock sends Byte 0 through byte X (if X(H)

was written to byte 8).

Controller (host) will need to acknowledge each byte

Controller (host) will send a not acknowledge bit

Controller (host) will send a stop bit

Index Block Read Operation

Controlle r (Host)

T

starT bit

Slave Address D4(H )

WR

W Rite

ICS (Sla ve /Re ce ive r)

ICS (Sla ve /Re ce ive r)

ACK

ACK

Beginning Byte = N

Beginning Byte = N

ACK

ACK

Data Byte Count = X

RT

Repeat starT

Slave Address D5(H )

RD

ReaD

ACK

Beginning Byte N

ACK

X Byte

ACK

Data Byte Count = X

ACK

Beginning Byte N

Byte N + X - 1

ACK

X Byte

ACK

P

stoP bit

Byte N + X - 1

Note: SMBus address is selectable among 4 addresses.

See tabel on page 2.

N

P

IDT® 15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

Not acknowledge

stoP bit

1578—01/18/11

10

�9EX21501

15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

Datasheet

9EX21501 SMBus Addressing

SMB_A(2:0) = 000

SMB Adr: D0

(DB1200G/GS)

(DB1900G/GS)

SMB_A(2:0) = 001

SMB Adr: D2

(DB1200G/GS)

(DB1900G/GS)

SMB_A(1:0) = 00

SMB Adr: D4

OR

SMB_A(2:0) = 010

SMB Adr: D4

(DB1200G/GS)

(DB1900G/GS)

OR

SMB_A(2:0) = 011

SMB Adr: D6

(DB1200G/GS)

`

(DB1900G/GS)

OR

SMB_A(2:0) = 100

SMB Adr: D8

(DB1200G/GS)

(DB1900G/GS)

OR

SMB_A(2:0) = 101

SMB Adr: DA

(DB1200G/GS)

(DB1900G/GS)

9EX21501

SMB_A(1:0) = 01

SMB Adr: D6

9EX21501

SMB_A(1:0) = 10

SMB Adr: D8

9EX21501

SMB_A(1:0) = 11

SMB Adr: DA

9EX21501

SMB_A(2:0) = 110

SMB Adr: DC

(DB1200G/GS)

(DB1900G/GS)

SMB Adr: D2

OR

(CK410B+/CK509B)

OR

SMB Adr: DC

9DB403/803

(DB400E/800E)

SMB_A(2:0) = 111

SMB Adr: DE

(DB1200G/GS)

(DB1900G/GS)

IDT® 15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

1578—01/18/11

11

�9EX21501

15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

Datasheet

SMBusTable: Output, and PLL BW Control Register

Pin #

Name

Control Function

Byte 0

Type

PLL_BW# adjust

RW

BYPASS# test mode / PLL

RW

Bit 7

54

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

DIF_14

-

100M_133M#

FSB

FSA

RESERVED

Output Control

RESERVED

Frequency Select Bit C

Frequency Select Bit B

Frequency Select bit A

RW

RW

RW

RW

0

1

00 = Low BW (1MHz)

10 = Bypass

11 = High BW (3MHz)

Hi-Z

Enable

133MHz

100MHz

See Frequency Select

Table

Default

Latch

Latch

1

1

0

Latch

0

1

SMBusTable: Output Control Register

Pin #

Name

Byte 1

Bit 7

DIF_6

Bit 6

DIF_5

Bit 5

DIF_4

Bit 4

DIF_3

Bit 3

DIF_2

Bit 2

DIF_1

Bit 1

DIF_0

Bit 0

Control Function

RESERVED

Output Control

Output Control

Output Control

Output Control

Output Control

Output Control

Output Control

Type

0

1

RW

RW

RW

RW

RW

RW

RW

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Enable

Enable

Enable

Enable

Enable

Enable

Enable

SMBusTable: Output Control Register

Byte 2

Pin #

Name

DIF_13

Bit 7

Bit 6

DIF_12

Bit 5

DIF_11

Bit 4

DIF_10

Bit 3

DIF_9

Bit 2

Control Function

Output Control

RESERVED

Output Control

Output Control

Output Control

Output Control

Type

RW

0

Hi-Z

1

Enable

RW

RW

RW

RW

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Enable

Enable

Enable

Enable

Default

1

1

1

1

1

1

Default

1

1

1

1

1

1

1

1

Bit 1

DIF_8

Output Control

RW

Hi-Z

Enable

1

Bit 0

DIF_7

Output Control

RW

Hi-Z

Enable

1

Type

R

R

R

R

0

Pin Low

Pin Low

Pin Low

Pin Low

1

Pin Hi

Pin Hi

Pin Hi

Pin Hi

R

R

R

Pin Low

Pin Low

Pin Low

Pin Hi

Pin Hi

Pin Hi

Default

X

X

X

X

1

X

X

X

SMBusTable: Output Enable Readback Register

Pin #

Name

Control Function

Byte 3

OE10# Input

Pin Readback

4

Bit 7

1

OE9# Input

Pin Readback

Bit 6

63

OE8# Input

Pin Readback

Bit 5

50

OE7# Input

Pin Readback

Bit 4

RESERVED

Bit 3

46

OE6# Input

Pin Readback

Bit 2

43

OE5# Input

Pin Readback

Bit 1

30

OE_01234# Input

Pin Readback

Bit 0

IDT® 15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

1578—01/18/11

12

�9EX21501

15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

Datasheet

SMBusTable: Output Enable Readback Register

Byte 4

Pin #

Name

Control Function

RESERVED

Bit 7

RESERVED

Bit 6

100M_133M# Input

Pin Readback

Bit 5

SEL_A_B# Input

Pin Readback

Bit 4

OE13_14# Input

Pin Readback

18

Bit 3

RESERVED

Bit 2

14

OE12# Input

Pin Readback

Bit 1

7

OE11# Input

Pin Readback

Bit 0

Type

0

1

R

R

R

133M

Input B

Pin Low

100M

Input A

Pin Hi

R

R

Pin Low

Pin Low

Pin Hi

Pin Hi

Default

0

0

X

X

X

1

X

X

Note: For an output to be enabled, BOTH the Output Enable Bit and the OE# pin must be enabled.

This means that the Output Enable Bit must be '1' and the corresponding OE# pin must be '0'.

SMBusTable: Vendor & Revision ID Register

Byte 5

Pin #

Name

Control Function

RID3

Bit 7

RID2

Bit 6

REVISION ID

RID1

Bit 5

RID0

Bit 4

VID3

Bit 3

VID2

Bit 2

VENDOR ID

VID1

Bit 1

VID0

Bit 0

Type

R

R

R

R

R

R

R

R

0

-

1

-

Default

0

0

0

1

0

0

0

1

SMBusTable: DEVICE ID

Byte 6

Pin #

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Type

R

R

R

R

R

R

R

R

0

1

Default

0

0

0

1

1

0

0

0

Name

Control Function

Device ID 7 (MSB)

Device ID 6

Device ID 5

Device ID 4

Device ID 3

Device ID 2

Device ID 1

Device ID 0

SMBusTable: Byte Count Register

Byte 7

Pin #

Name

BC7

Bit 7

BC6

Bit 6

BC5

Bit 5

BC4

Bit 4

BC3

Bit 3

BC2

Bit 2

BC1

Bit 1

BC0

Bit 0

Control Function

Writing to this register

configures how many

bytes will be read back.

IDT® 15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

Type

RW

RW

RW

RW

RW

RW

RW

RW

Device ID is 18 hex

0

-

1

-

Default

0

0

0

0

0

1

1

1

1578—01/18/11

13

�9EX21501

15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

Datasheet

THERMALLY ENHANCED, VERY THIN, FINE PITCH

QUAD FLAT / NO LEAD PLASTIC PACKAGE

DIMENSIONS

N

ND

NE

DIMENSIONS (mm)

SYMBOL

A

A1

A3

b

e

D x E BASIC

D2 MIN. / MAX.

E2 MIN. / MAX.

L MIN. / MAX.

64

16

16

MIN.

MAX.

0.8

1.0

0

0.05

0.25 Reference

0.18

0.3

0.50 BASIC

9.00 x 9.00

7.00

7.25

7.00

7.25

0.30

0.50

Ordering Information

Part / Order Number

9EX21501AKLF

9EX21501AKLFT

9EX21501AKILF

9EX21501AKILFT

Shipping Packaging

Trays

Tape and Reel

Trays

Tape and Reel

Package

64-pin MLF

64-pin MLF

64-pin MLF

64-pin MLF

Temperature

0 to +70° C

0 to +70° C

-40 to +85°C

-40 to +85°C

"LF” suffix to the part number are the Pb-free configuration and are RoHS compliant.

"A" is the revision designator (will not correlate with datasheet revision).

Due to package size constraints actual top side marking may differ from the full orderable part number.

IDT® 15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

1578—01/18/11

14

�9EX21501

15 Output PCIe G2/QPI Differential Buffer with 2:1 Input Mux

Datasheet

Revision History

Rev.

0.1

0.2

0.3

0.4

0.5

Who Issue Date Description

RDW 4/6/2009 Initial Release

1. Lowered IDD

2. Updated block diagram to correct typo's

3. Corrected Pin descriptions

4. Corrected Frequency/functionality table references to Byte 2, should be

RDW 4/7/2008

Byte 0

5. Updated Power Groups Table

6. Corrected typo in SMBus Address Selection Table.

7. Corrected references to 9EX1501 to be 9EX21501

1. Added more detailed Idd numbers to DS

RDW 11/24/2009

2. Added industrial temp Idd numbers and ordering information

1.Corrected Pin Description for Pin 52. There was descrepancy between

the Frequency/Functionality Table and the Pin Description. The Pin

RDW 2/4/2010 Description was not correct. Instead of the pin description defining

functionality, it now refers to the Frequency Functionality Table for the

definition.

1. Reformatted Electrical Tables to latest template

2. Updated electrical tables with characterized data

RDW 1/18/2011

3. Added Test loads diagram and table

4. Move to Final

Page #

-

Various

4

Various

Innovate with IDT and accelerate your future networks. Contact:

www.IDT.com

For Sales

For Tech Support

800-345-7015

408-284-8200

Fax: 408-284-2775

408-284-6578

pcclockhelp@idt.com

Corporate Headquarters

Asia Pacific and Japan

Europe

Integrated Device Technology, Inc.

6024 Silver Creek Valley Road

San Jose, CA 95138

United States

800 345 7015

+408 284 8200 (outside U.S.)

IDT Singapore Pte. Ltd.

1 Kallang Sector #07-01/06

KolamAyer Industrial Park

Singapore 349276

Phone: 65-6-744-3356

Fax: 65-6-744-1764

IDT Europe Limited

321 Kingston Road

Leatherhead, Surrey

KT22 7TU England

Phone: 44-1372-363339

Fax: 44-1372-378851

© 2011 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT, ICS, and the IDT logo are trademarks

of Integrated Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks

are or may be trademarks or registered trademarks used to identify products or services of their respective owners.

Printed in USA

15

�IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES (“RENESAS”) PROVIDES TECHNICAL

SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING

REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND

OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED,

INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible

for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3)

ensuring your application meets applicable standards, and any other safety, security, or other requirements. These

resources are subject to change without notice. Renesas grants you permission to use these resources only for

development of an application that uses Renesas products. Other reproduction or use of these resources is strictly

prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property.

Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims,

damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject

to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources

expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

Corporate Headquarters

Contact Information

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

www.renesas.com

For further information on a product, technology, the most

up-to-date version of a document, or your nearest sales

office, please visit:

www.renesas.com/contact/

Trademarks

Renesas and the Renesas logo are trademarks of Renesas

Electronics Corporation. All trademarks and registered

trademarks are the property of their respective owners.

© 2020 Renesas Electronics Corporation. All rights reserved.

�