DATASHEET

9VRS4818B

FUSION II CLOCK GENERATOR

General Description

Features/Benefits

The 9VRS4818B is a 1.5V Core main clock synthesizer

chip for AMD Fusion platform. An SMBus interface allows

full control of the device.

Recommended Application

•

•

•

•

Very Low Power Clock Generator for AMD Fusion II

Platforms

Key Specifications

•

•

•

•

Input/Output Features

• Low power differential outputs with integrated series

resistors for Zo=50ohm systems

• 12 - Differential PCIe Gen2 SRC pairs w/dedicated

•

•

•

•

•

•

•

CLKREQ# pins

3 - Differential PCIe Gen2 SATA_DISPLAY pairs

w/microspread capability

2 - 48MHz USB clocks (180 degrees out of phase for EMI

reduction)

2 - 14.318MHz REF clock outputs

1 - 25MHz LAN clock output that can run from VDD

suspend rail

1 - CkPwrGd/WOL_STOP#

1 - VDD_SUSPEND pin

1- RESET_IN# pin

•

•

1.5V Core for minimal Power consumption

Spread Spectrum for EMI reduction

Outputs may be disabled via SMBus

External crystal load capacitors for maximum frequency

accuracy

SRC/SATA_DISP output cycle-to-cycle jitter < 125ps

14.318MHz output cycle-to-cycle jitter < 200ps

48MHz output cycle-to-cycle jitter < 130ps

SRC/SATA_DISP output phase jitter < 3.1ps rms (PCIe

Gen2)

+/- 100ppm frequency accuracy on all clocks, (assuming

REF is trimmed to 0 ppm)

31.5KHz spread modulation frequency; passes USB3.0

compliance test

VDD25_SUSP3.3

GND25M

25MHz

SMBDAT

SMBCLK

^CLKREQ9#

^CLKREQ8#

^CLKREQ7#

GNDREF

REF0

REF1

VDDREF_3.3

^CLKREQ6#

^CLKREQ5#

^CLKREQ4#

^RESET_IN#

VDD48_3.3

48MHz_0

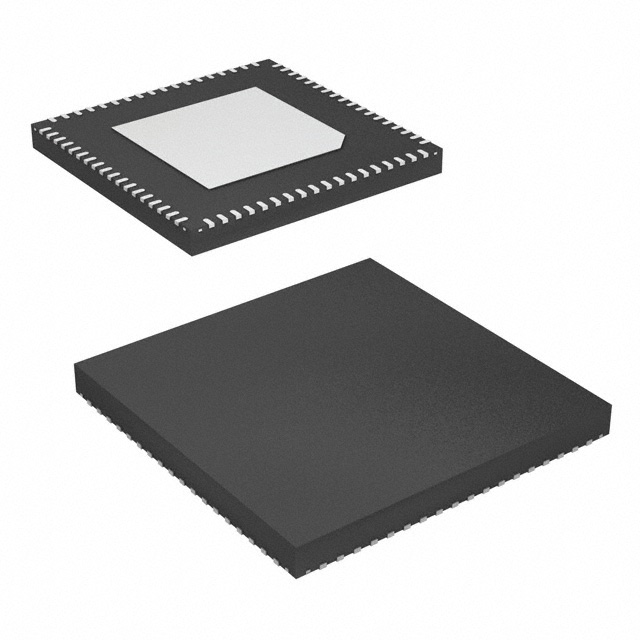

Pin Configuration

72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55

48MHz_1

GND48

^CLKREQ3#

^CLKREQ2#

^CLKREQ1#

^CLKREQ0#

SRC0T_LPRS

SRC0C_LPRS

SRC1T_LPRS

SRC1C_LPRS

GNDSRC

VDDSRC_LIO

SRC2T_LPRS

SRC2C_LPRS

SRC3T_LPRS

SRC3C_LPRS

VDDSRC_1.5

GNDSRC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

9VRS4818

X1_25

X2_25

^CKPwrGd/WOL_STOP#

^CLKREQ10#

^CLKREQ11#

VDDSATADISP_1.5

GNDSATADISP

SATA_DISP0C_LPRS

SATA_DISP0T_LPRS

SATA_DISP1C_LPRS

SATA_DISP1T_LPRS

GNDSATADISP

VDDSATADISP_LIO

SATA_DISP2C_LPRS

SATA_DISP2T_LPRS

GNDSR C

SRC11C_LPRS

SRC11T_LPRS

SRC10C_LPRS

SRC10T_LPRS

GNDSRC

VDDSRC_1.5

SRC9C_LPRS

SRC9T_LPRS

SRC8C_LPRS

SRC8T_LPRS

VDDSRC_LIO

GNDSRC

SRC7C_LPRS

SRC7T_LPRS

SRC6C_LPRS

SRC6T_LPRS

SRC5C_LPRS

SRC5T_LPRS

SRC4T_LPRS

SRC4C_LPRS

19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36

^ Indicates that pin has 100Kohm internal pullup resistor.

IDT® FUSION II CLOCK GENERATOR

1

9VRS4818B

REV A 062512

�9VRS4818B

FUSION II CLOCK GENERATOR

Pin Descriptions

PIN #

PIN NAME

PIN TYPE

1

2

48MHz_1

GND48

OUT

GND

3

^CLKREQ3#

IN

4

^CLKREQ2#

IN

5

^CLKREQ1#

IN

6

^CLKREQ0#

IN

7

SRC0T_LPRS

OUT

8

SRC0C_LPRS

OUT

9

SRC1T_LPRS

OUT

10

SRC1C_LPRS

OUT

11

12

GNDSRC

VDDSRC_LIO

GND

PWR

13

SRC2T_LPRS

OUT

14

SRC2C_LPRS

OUT

15

SRC3T_LPRS

OUT

16

SRC3C_LPRS

OUT

17

18

VDDSRC_1.5

GNDSRC

PWR

GND

19

SRC4T_LPRS

OUT

20

SRC4C_LPRS

OUT

21

SRC5T_LPRS

OUT

22

SRC5C_LPRS

OUT

23

SRC6T_LPRS

OUT

24

SRC6C_LPRS

OUT

25

SRC7T_LPRS

OUT

26

SRC7C_LPRS

OUT

27

28

GNDSRC

VDDSRC_LIO

GND

PWR

29

SRC8T_LPRS

OUT

30

SRC8C_LPRS

OUT

31

SRC9T_LPRS

OUT

32

SRC9C_LPRS

OUT

33

34

VDDSRC_1.5

GNDSRC

PWR

GND

35

SRC10T_LPRS

OUT

36

SRC10C_LPRS

OUT

IDT® FUSION II CLOCK GENERATOR

DESCRIPTION

48MHz clock output. (180 degrees out of phase with 48MHz_0)

Ground pin for the 48MHz outputs

Output enable for SRC/PCI Express output pair '3'

0 = enabled, 1 = Low/Low. This pin has a 120K internal pull up resistor.

Output enable for SRC/PCI Express output pair '2'

0 = enabled, 1 = Low/Low. This pin has a 120K internal pull up resistor.

Output enable for SRC/PCI Express output pair '1'

0 = enabled, 1 = Low/Low. This pin has a 120K internal pull up resistor.

Output enable for SRC/PCI Express output pair '0'

0 = enabled, 1 = Low/Low. This pin has a 120K internal pull up resistor.

True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor

needed)

Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series

resistor needed)

True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor

needed)

Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series

resistor needed)

Ground pin for the SRC outputs

Supply for SRC outputs, 1.05V to 1.5V nominal

True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor

needed)

Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series

resistor needed)

True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor

needed)

Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series

resistor needed)

Supply for SRC core and outputs, 1.5V nominal

Ground pin for the SRC outputs

True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor

needed)

Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series

resistor needed)

True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor

needed)

Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series

resistor needed)

True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor

needed)

Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series

resistor needed)

True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor

needed)

Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series

resistor needed)

Ground pin for the SRC outputs

Supply for SRC outputs, 1.05V to 1.5V nominal

True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor

needed)

Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series

resistor needed)

True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor

needed)

Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series

resistor needed)

Supply for SRC core and outputs, 1.5V nominal

Ground pin for the SRC outputs

True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor

needed)

Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series

resistor needed)

2

9VRS4818B

REV A 062512

�9VRS4818B

FUSION II CLOCK GENERATOR

Pin Descriptions (cont.)

PIN #

PIN TYPE

37

SRC11T_LPRS

OUT

38

SRC11C_LPRS

OUT

39

GNDSRC

GN D

40

SATA_DISP2T_LPRS

OUT

41

SATA_DISP2C_LPRS

OUT

42

43

VDDSATADISP_LIO

GNDSATADISP

PWR

GN D

44

SATA_DISP1T_LPRS

OUT

45

SATA_DISP1C_LPRS

OUT

46

SATA_DISP0T_LPRS

OUT

47

SATA_DISP0C_LPRS

OUT

48

49

GNDSATADISP

VDDSATADISP_1.5

GN D

PWR

50

^CLKREQ11#

IN

51

^CLKREQ10#

IN

52

^CKPw rGd/WOL_STOP#

IN

53

54

X2_25

X1_25

OUT

IN

55

VDD25_SUSP3.3

PWR

56

57

58

59

GND25M

25MHz

SMBDAT

SMBCLK

GN D

OUT

I/O

IN

60

^CLKREQ9#

IN

61

^CLKREQ8#

IN

62

^CLKREQ7#

IN

63

64

65

66

GNDREF

REF0

REF1

VDDREF_3.3

GN D

OUT

OUT

PWR

67

^CLKREQ6#

IN

68

^CLKREQ5#

IN

69

^CLKREQ4#

IN

70

^RESET_IN#

OD

I/O

71

72

VDD48_3.3

48MHz_0

PWR

OUT

IDT® FUSION II CLOCK GENERATOR

DESCRIPTION

True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor

needed)

Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series

resistor needed)

Ground pin for the SRC outputs

True clock of low power differential SATA_DISPlay clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm

series resistor needed)

Complement clock of low power differential SATA_DISPlay clock pair. (no 50 ohm shunt resistor to GND and no 33

ohm series resistor needed)

Supply for SATA_DISPlay outputs, 1.05V to 1.5V nominal

Ground pin for the SATA_DISPlay outputs

True clock of low power differential SATA_DISPlay clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm

series resistor needed)

Complement clock of low power differential SATA_DISPlay clock pair. (no 50 ohm shunt resistor to GND and no 33

ohm series resistor needed)

True clock of low power differential SATA_DISPlay clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm

series resistor needed)

Complement clock of low power differential SATA_DISPlay clock pair. (no 50 ohm shunt resistor to GND and no 33

ohm series resistor needed)

Ground pin for the SATA_DISPlay outputs

Supply for SATA_DISPlay core and outputs, 1.5V nominal

Output enable for SR C/PCI Express output pair '11'

0 = enabled, 1 = Low/Low. This pin has a 120K internal pull up resistor.

Output enable for SR C/PCI Express output pair '10'

0 = enabled, 1 = Low/Low. This pin has a 120K internal pull up resistor.

This devices powers up the clock chip and latched strap pins when asserted high. When asserted low, the clock is

powered down except for the 25M output, if VDD25_SUSP3.3 is maintained.

0 = Power Dow n, 1 = normal operation.

Crystal output, nominally 25MHz

Crystal input, nominally 25MHz

Power pin for the 25M output and XTAL oscillator. This pin allows the 25MHz output when the rest of the power is

collapsed and VttPwrGd/WOL_STOP# is low.

Ground pin for the 25MHz output and XTAL oscillator circuit

25MHz clock output.

Data pin for SMBus circuitry, 5V tolerant.

Clock pin of SMBus circuitry, 5V tolerant.

Output enable for SR C/PCI Express output pair '9'

0 = enabled, 1 = Low/Low. This pin has a 120K internal pull up resistor.

Output enable for SR C/PCI Express output pair '8'

0 = enabled, 1 = Low/Low. This pin has a 120K internal pull up resistor.

Output enable for SR C/PCI Express output pair '7'

0 = enabled, 1 = Low/Low. This pin has a 120K internal pull up resistor.

Ground pin for the REF outputs.

14.318 MHz reference clock, 3.3V

14.318 MHz reference clock, 3.3V

Ref, XTAL power supply, nominal 3.3V

Output enable for SR C/PCI Express output pair '6'

0 = enabled, 1 = Low/Low. This pin has a 120K internal pull up resistor.

Output enable for SR C/PCI Express output pair '5'

0 = enabled, 1 = Low/Low. This pin has a 120K internal pull up resistor.

Output enable for SR C/PCI Express output pair '4'

0 = enabled, 1 = Low/Low. This pin has a 120K internal pull up resistor.

As an input it resets the device to the power up default state. As an output, it is driven low when the internal watchdog

hardware timer expires. It is cleared when the internal watchdog hardware timer is reset or disabled. The input is falling

edge triggered.

0 = Restore Settings, 1 = normal operation.

Power pin for the 48MHz and SIO outputs and core. 3.3V

48MHz clock output.

3

9VRS4818B

REV A 062512

�9VRS4818B

FUSION II CLOCK GENERATOR

Block Diagram

25MHz

REF(1:0)

14.318MHz PLL

SATA_DISP(2:0)

SATA_DISP PLL

SRC(11:0)

Gen2 SRC PLL

SS capable

X1

X2

25M

XTAL OSC

48M(1:0)

USB48 PLL

CKPwrGD/WOL_STOP#

LOGIC

DIFFERENTIAL

CLKREQ(11:0)#

SINGLE-ENDED

SMBCLK

SMBDAT

Power Groups

VDD3.3

Pin Number

VDD1.5

VDD_LIO

17, 33

12, 28,

49

42

Description

GND

11, 18, 27,

34, 39

Power for SRC PLL and Outputs

66

50

63

Power for SATA_DISP PLL and

Outputs

Power for HTT output

Power for REF PLL and Outputs

55

56

Power for XTAL osc.and 25M outputs

71

2

Power for 48MHz PLL and outputs.

47

IDT® FUSION II CLOCK GENERATOR

43, 48

4

9VRS4818B

REV A 062512

�9VRS4818B

FUSION II CLOCK GENERATOR

SATA_DISP Frequency Selection Table

Line

SATA_DISP

FS4

Byte 3, Bit 4

SATA_DISP

FS3

Byte 3, Bit 3

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

IDT® FUSION II CLOCK GENERATOR

SATA_DISP SATA_DISP SATA_DISP SATA_DISP

FS2

FS1

FS0

Speed

Byte 3, Bit2 Byte 3, Bit1 Byte 3, Bit0

(MHz)

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

5

Spread

%

91.25

91.25

92.50

92.50

93.75

93.75

95.00

95.00

96.25

96.25

97.50

97.50

98.75

98.75

100.00

100.00

100.00

100.00

101.25

101.25

102.50

102.50

103.75

103.75

105.00

105.00

106.25

106.25

107.50

107.50

108.75

108.75

9VRS4818B

N/A

REV A 062512

�9VRS4818B

FUSION II CLOCK GENERATOR

Line

SS Type

Byte 4, Bit 4

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

IDT® FUSION II CLOCK GENERATOR

SRC Spread Selection Table

SS

SRC

SRC FS1 SRC FS0

Range

SS_EN

Byte 4,

Byte 4,

Byte 4,

Byte 4,

Bit1

Bit0

Bit 3

Bit2

0

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

1

0

0

0

1

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

0

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

1

0

0

0

1

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

6

SRC

Speed

(MHz)

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

Spread

%

SS OFF

0%

-0.49

-0.45

-0.40

-0.35

SS OFF

0%

-0.3

-0.25

-0.25

-0.25

SS OFF

0%

+/-0.25

+/-0.225

+/-0.20

+/-0.175

SS OFF

0%

+/-0.15

+/-0.125

+/-0.125

+/-0.125

9VRS4818B

REV A 062512

�9VRS4818B

FUSION II CLOCK GENERATOR

Absolute Maximum Ratings

Stresses above the ratings listed below can cause permanent damage to the 9VRS4818B. These ratings, which are

standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any

other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute

maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over

the recommended operating temperature range.

PARAMETER

I/O Supply Voltage

1.5V Core Supply

Voltage

3.3V Core Supply

Voltage

Storage Temperature

SYMBOL

VDDxxx_LIO

CONDITIONS

-

VDDxxx_1.5

-

1.5

GND+1.9V

V

1

VDDxxx_3.3

-

3.3

GND+3.8V

V

1

Ts

-

-65

150

°C

1

Ambient Operating Temp

Tambient

-

0

70

°C

1

Case Temperature

Input ESD protection

Tcase

ESD prot

Human Body Model

115

2000

°C

V

1

1

1

MIN

TYP

1.05

MAX

UNITS

GND+1.9V

V

Notes

1

Guaranteed by design and characterization, not 100% tested in production.

Electrical Characteristics–USB - 48MHz

PARAMETER

SYMBOL

Long Accuracy

ppm

Clock period

Clock Low Time

Clock High Time

Output High Voltage

Output Low Voltage

TPERIOD

TLOW

THIGH

VOH

V OL

Rise Time

tr_USB

Fall Time

Output High Voltage

Output Low Voltage

Output High Voltage

Output Low Voltage

Skew(out of phase)

Jitter, Cycle to cycle

tf_USB

V OHUSB1

VOLUSB1

V OHUSB2

VOLUSB2

tSKEW

tjCYC-CYC

Jitter, Short Term

tjSHORT-TERM

Jitter, Long Term

tjLONG-TERM

Duty Cycle

dCYCUSB

CONDITIONS*

see Tperiod min-max

values

USB output nominal

Measure from < 0.6V

Measure from > 2.0V

IOH = -1 mA

IOL = 1 mA

VOL = 20% of Voh,

VOH = 80%of Voh

VOL = 20% of Voh,

VOH = 80%of Voh

IOH = -1 mA

IOL = 1 mA

IOH = -0.2 mA

IOL = 0.2 mA

VT = 1.5 V

VT = 1.5 V

VT = 1.5 V, integrated from

10MHz to 250Mhz

VT = 1.5 V, integrated from

0.1MHz to 10Mhz

VT = 1.5 V

MIN

TYP

MAX

-100

0

100

ppm

1

20.831

9.375

9.375

2.4

0

20.833

10.400

10.750

2.8

20.836

11.458

11.458

3.3

0.4

ns

ns

ns

V

V

1,3

1

1

1

1

0.5

1.9

3

ns

0.5

2.4

2

3

0.4

2.2

0.4

250

130

ns

V

V

V

V

ps

ps

1

1

1

1

1,4

1,2

-100

100

ps

1,2

-30

30

ps

1,2,3

55

%

1

1.8

2

240

115

45

50

UNITS NOTES

1

1

*TA = 0 - 70°C; Supply Voltage VDD = 3.3 V +/-5%

1

Guaranteed by design and characterization, not 100% tested in production.

2

IDT recommended and/or chipset vendor layout guidelines must be followed to meet this specification

3

All Long Term Accuracy and Clock Period specifications are guaranteed assuming that 25MHz output is at 25MHz

4

USB outputs are 180 degrees out of phase.

5

The Ncycle jitter (N periods after trigger) must not exceed +/- 130 ps for any N-cuycle inside a winder starting at trigger and finsihing 100ns after

trigger. (N=1..4)

IDT® FUSION II CLOCK GENERATOR

7

9VRS4818B

REV A 062512

�9VRS4818B

FUSION II CLOCK GENERATOR

Electrical Characteristics–Input/Supply/Common Output Parameters

PARAMETER

I/O Supply Voltage

1.5V Core Supply

Voltage

3.3V Core Supply

Voltage

Input High Voltage

Input Low Voltage

Input High Current

SYMBOL

VDDxxx_LIO

CONDITIONS*

-

MIN

0.9975

TYP

1.05

MAX

1.1025

UNITS

V

Notes

1

VDDxxx_1.5

-

1.425

1.5

1.575

V

1

VDDxxx_3.3

-

3.135

3.3

3.465

V

1

VDD + 0.3

0.8

5

V

V

uA

1, 3

1, 3

1

uA

1

uA

1

10

mA

1

1

mA

1

1

mA

1

2

mA

1

1

mA

1

V IH

VIL

IIH

IIL1

Input Low Current

IIL2

3.3V Inputs

2

3.3V inputs

VSS - 0.3

VIN = VDD

-5

VIN = 0 V; Inputs with no

-5

pull-up resistors

VIN = 0 V; Inputs with pull-200

up resistors

IDD_3.3SUSP

Suspend Current

WOL_STOP (25M)

Enabled in Power Down

IDD_1.5SUSP

IDD_I/OSUSP

IDD_3.3PD

Power Down Current

WOL_STOP (25M)

Disabled in Power down

IDD_1.5PD

IDD_I/OPD

IDD_3.3

IDD_1.5

IDD_I/O

Fi

Lpin

CIN

COUT

CINX

Operating Current

Input Frequency

Pin Inductance

Input Capacitance

Clk Stabilization

TSTAB

Modulation Frequency

Tdrive_PD

Tfall_PD

Trise_PD

SMBus Voltage

Low-level Output Voltage

Current sinking at

VOL = 0.4 V

SMBCLK/SMBDAT

Clock/Data Rise Time

SMBCLK/SMBDAT

Clock/Data Fall Time

all outputs driven

VDD = 3.3 V +/-5%

Logic Inputs

Output pin capacitance

X1 & X2 pins

From VDD Power-Up to 1st

clock

Triangular Modulation

SATA_DISP output enable

after

PD de-assertion

PD fall time of

PD rise time of

VDDSMB

VOLSMB

TRSMB

TFSMB

mA

1

30

30

70

7

5

6

5

mA

mA

mA

MHz

nH

pF

pF

pF

1

1

1

2

1

1

1

1

1.8

ms

1

32

kHz

1

300

us

1

5

5

5.5

0.4

ns

ns

V

V

1

1

1

1

mA

1

1000

ns

1

300

ns

1

25.00

31

31.500

2.7

@ IPULLUP

4

IPULLUPSMB

0.1

6

(Max VIL - 0.15) to

(Min VIH + 0.15)

(Min VIH + 0.15) to

(Max VIL - 0.15)

*TA = 0 - 70°C; All Supply Voltages at nominal+/-5%

1

Guaranteed by design and characterization, not 100% tested in production.

2

Input frequency should be measured at the 25M output pin and tuned to ideal 25MHz to meet ppm frequency accuracy on PLL outputs.

3

CLKREQ# Inputs are 3.3V tolerant

IDT® FUSION II CLOCK GENERATOR

8

9VRS4818B

REV A 062512

�9VRS4818B

FUSION II CLOCK GENERATOR

AC Electrical Characteristics–Low-Power DIF Outputs: SATA_DISP and SRC

PARAMETER

SRC/SATA Frequency

Long Term Accuracy

Rising Edge Slew Rate

Falling Edge Slew Rate

Slew Rate Variation

Maximum Output

Voltage

SYMBOL

f SRC_SATA

ppm

tSLR

tFLR

tSLVAR

CONDITIONS

Spread Specturm Off

Spread Specturm Off

Differential Measurement

Differential Measurement

Single-ended Measurement

VHIGH

Includes overshoot

Minimum Output Voltage

VLOW

Includes undershoot

-300

Differential Voltage

Swing

VSWING

Differential Measurement

Crossing Point Voltage

VXABS

Single-ended Measurement

Crossing Point Variation

VXABSVAR

Single-ended Measurement

Duty Cycle

Jitter - Cycle to Cycle

SRC[11:0] Skew Even

Outputs

SRC[11:0] Skew Odd

Outputs

SRC[11:0] Even to Odd

Skew

Jitter - SSC Residual

t dCYC

tjCYC-CYC

Differential Measurement

Differential Measurement

t SRCSKEW_E

Jitter, Phase

SSC

MIN

-100

0.6

0.6

TYP

100

0

3.5

3.5

10

MAX

925

1150

+100

4

4

20

UNITS NOTES

MHz

1,6

ppm

1,6

V/ns

1,2

V/ns

1,2

%

1

mV

1

-50

mV

1

300

1950

mV

1

300

445

550

mV

1,3,4

28

140

mV

1,3,5

50

55

53

125

%

ps

1

1

Differential Measurement

46

200

ps

1,8

tSRCSKEW_O

Differential Measurement

60

200

ps

1,8

tSRCSKEW

Differential Measurement

1.925

ns

1,8

tSSC_RES

Differential Measurement

PCIe Gen 1 specs

(1.5 - 22 MHz)

PCIe Gen 2 (8-16 MHz, 516 MHz)

Lo-band content

(10kHz to 1.5MHz)

PCIe Gen 2 (8-16 MHz, 516 MHz)

Hi-band content

(1.5MHz to Nyquist)

Default Spread when

enabled

Spread Option 1

Spread Option 2

Spread Option 3

10

75

ps

1

38

86

ps

1, 7

1.5

3

ps rms

1, 7

2.4

3.1

ps rms

1, 7

-0.49

%

1, 9

-0.48

-0.47

-0.46

%

%

%

1, 9

1, 9

1, 9

tjphase

tjphaseSRC

47

*TA = 0 - 70°C; All Supply Voltages at nominal+/-5%

1

Guaranteed by design and characterization, not 100% tested in production.

2

Slew rate measured through Vswing centered around differential zero

3

Vxabs is defined as the voltage where CLK = CLK#

4

Only applies to the differential rising edge (CLK rising and CLK# falling)

Defined as the total variation of all crossing voltages of CLK rising and CLK# falling. Matching applies to rising edge rate of CLK and falling edge of

CLK#. It is measured using a +/-75mV window centered on the average cross point where CLK meets CLK#.

5

6

All Long Term Accuracy and Clock Period specifications are guaranteed assuming that 25MHz output is at 25MHz

7

Applicable to all SRC outputs. See http://www.pcisig.com for complete specs. Guaranteed by design/characterization, not tested in production.

8

SRC outputs are divided into two banks, odd and even. The odd bank skew window is 200 ps. The even bank skew window is 200ps. The

skew between the even and odd banks is intentionally set at 1.925 ns.

9

Only applies to SRC outputs. SATA_DISP outputs do not spread.

IDT® FUSION II CLOCK GENERATOR

9

9VRS4818B

REV A 062512

�9VRS4818B

FUSION II CLOCK GENERATOR

Electrical Characteristics–REF-14.318MHz

PARAMETER

SYMBOL

Long Accuracy

ppm

Long Term Jitter

tjLT

CONDITIONS

see Tperiod min-max

values

@ 10us

Clock period

TPERIOD

14.318MHz output nominal

Clock Low Time

Clock High Time

Output High Voltage

Output Low Voltage

TLOW

THIGH

VOH

VOL

Rise Time

tR

Fall Time

tF

Skew

Duty Cycle

Jitter, Cycle to Cycle

tSKEW

dt1

tjCYC-CYC

Jitter, Peak to Peak

tjPK-PK

Measure from V T = 50%

Measure from V T = 50%

IOH = -1 mA

IOL = 1 mA

V OL = 20% of VOH,

V OH = 80%of VOH

V OL = 20% of VOH,

V OH = 80%of VOH

Measure from V T = 50%

VT = VOH/2

Measure from V T = 50%

Measure from VT = 50%

(0.9V)

t jpk-pk =[|tjcyc-cyc max| + |tjcyccyc min|]/2

MIN

TYP

MAX

UNITS

Notes

-50

0

50

ppm

1,2

200

500

ps

1,2,3

69.8413

ns

2

33

34

2.8

3.3

0.4

ns

ns

V

V

2

2

1

1

1.2

1.5

ns

1

1.2

1.5

ns

1

71

50

125

250

55

200

ps

%

ps

1

1

1,3

100

200

ps

1,3

2

2

2.4

0

45

*TA = 0 - 70°C; Supply Voltage VDD = 3.3 V +/-5%

1

Guaranteed by design and characterization, not 100% tested in production.

2

All Long Term Accuracy and Clock Period specifications are guaranteed assuming that 25MHz output is at 25MHz

3

IDT recommended and/or chipset vendor layout guidelines must be followed to meet this specification

Electrical Characteristics–25MHz

PARAMETER

SYMBOL

Long Accuracy

ppm

Long Term Jitter

tjLT

Clock period

TPERIOD

Clock Low Time

Clock High Time

Output High Voltage

Output Low Voltage

TLOW

THIGH

VOH

VOL

Rise Time

tR

Fall Time

tF

Duty Cycle

Jitter, Cycle to Cycle

dt1

t jCYC-CYC

Jitter, Peak to Peak

tjPK-PK

CONDITIONS

see Tperiod min-max

values

@ 10us

25MHz XTAL output

nominal

Measure from V T = 50%

Measure from V T = 50%

IOH = -1 mA

IOL = 1 mA

V OL = 10% of VOH,

V OH = 90%of VOH

V OL = 10% of VOH,

V OH = 90%of VOH

VT = 50%

Measure from V T = 50%

Measure from VT = 50%

tjpk-pk =[|tjcyc-cyc max| + |tjcyccyc min|]/2

MIN

TYP

MAX

UNITS

Notes

-50

0

50

ppm

1,2

200

250

ps

1,2,3

40.0000

ns

2

16.6

17.2

2.8

3.3

0.4

ns

ns

V

V

2

2

1

1

2.4

3

ns

1

2.4

3

ns

1

48

180

55

200

%

ps

1

1,3

160

200

ps

1,3

2

2

2.4

0

45

*TA = 0 - 70°C; Supply Voltage VDD = 3.3 V +/-5%

1

Guaranteed by design and characterization, not 100% tested in production.

2

All Long Term Accuracy and Clock Period specifications are guaranteed assuming that 25MHz output is at 25MHz

3

IDT recommended and/or chipset vendor layout guidelines must be followed to meet this specification

IDT® FUSION II CLOCK GENERATOR

10

9VRS4818B

REV A 062512

�9VRS4818B

FUSION II CLOCK GENERATOR

General SMBus Serial Interface Information for 9VRS4818B

How to Write

How to Read

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Controller (host) sends a start bit

Controller (host) sends the write address

IDT clock will acknowledge

Controller (host) sends the beginning byte location = N

IDT clock will acknowledge

Controller (host) sends the byte count = X

IDT clock will acknowledge

Controller (host) starts sending Byte N through Byte

N+X-1

IDT clock will acknowledge each byte one at a time

Controller (host) sends a Stop bit

Index Block Write Operation

Controller (Host)

T

Index Block Read Operation

IDT (Slave/Receiver)

Controller (Host)

starT bit

T

Slave Address

WR

•

•

•

Controller (host) will send a start bit

Controller (host) sends the write address

IDT clock will acknowledge

Controller (host) sends the beginning byte location = N

IDT clock will acknowledge

Controller (host) will send a separate start bit

Controller (host) sends the read address

IDT clock will acknowledge

IDT clock will send the data byte count = X

IDT clock sends Byte N+X-1

IDT clock sends Byte 0 through Byte X (if X(H) was

written to Byte 8)

Controller (host) will need to acknowledge each byte

Controller (host) will send a not acknowledge bit

Controller (host) will send a stop bit

IDT (Slave/Receiver)

starT bit

Slave Address

WRite

ACK

WR

WRite

ACK

Beginning Byte = N

ACK

Beginning Byte = N

ACK

Data Byte Count = X

ACK

RT

Slave Address

Beginning Byte N

ACK

O

O

RD

ReaD

ACK

X Byte

O

Repeat starT

O

Data Byte Count=X

O

O

ACK

ACK

ACK

Beginning Byte N

Byte N + X - 1

stoP bit

O

X Byte

P

O

O

O

O

O

Read Address

Write Address

D3(H)

D2(H)

IDT® FUSION II CLOCK GENERATOR

Byte N + X - 1

N

Not acknowledge

P

stoP bit

11

9VRS4818B

REV A 062512

�9VRS4818B

FUSION II CLOCK GENERATOR

Byte

0

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

SMBus Table: Output Enable Control Register

Name

Description

25M_OE

Output Enable

REF1_OE

Output Enable

REF0_OE

Output Enable

SATA_DISP2_OE

Output Enable

SATA_DISP1_OE

Output Enable

SATA_DISP0_OE

Output Enable

48MH z_1_OE

Output Enable

48MH z_0_OE

Output Enable

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

Low

Low

Low

Low/Low

Low/Low

Low/Low

Low

Low

1

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

Default

1

1

1

1

1

1

1

1

Byte

1

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

SMBus Table:CKLREQ and Output Control Register

Name

Control Function

CLKR EQ7

CLKREQ 7controls SRC7

CLKR EQ6

CLKREQ6 controls SRC6

CLKR EQ5

CLKREQ5 controls SRC5

CLKR EQ4

CLKREQ4 controls SRC4

SRC11_OE

Output Enable

SRC10_OE

Output Enable

SRC9_OE

Output Enable

SRC8_OE

Output Enable

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

D oes not control

D oes not control

D oes not control

D oes not control

Low/Low

Low/Low

Low/Low

Low/Low

1

Controls

Controls

Controls

Controls

Enabled

Enabled

Enabled

Enabled

Default

0

0

0

0

1

1

1

1

Byte

2

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

SMBus Table: Output Enable Control Register

Name

Control Function

SRC7_OE

Output Enable

SRC6_OE

Output Enable

SRC5_OE

Output Enable

SRC4_OE

Output Enable

SRC3_OE

Output Enable

SRC2_OE

Output Enable

SRC1_OE

Output Enable

SRC0_OE

Output Enable

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

Low/Low

Low/Low

Low/Low

Low/Low

Low/Low

Low/Low

Low/Low

Low/Low

1

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

Default

1

1

1

1

1

1

1

1

Byte

3

Bit 7

Bit 6

SMBus Table: SATA_DISP/HTT Frequency and Output

Name

Control Function

CLKR EQ3

CLKREQ3 controls SRC3

CLKR EQ2

CLKREQ2 controls SRC2

1

Controls

Controls

25M does RUNS when

VDD_SUSP is present and

WOL_STOP# = 0

Default

0

0

Enable Control Register

Type

0

RW

D oes not control

RW

D oes not control

25M does not run when

RW

VDD_SUSP is present and

WOL_STOP# = 0

Bit 5

WOL_EN

Enables 25M output in Suspend

State

Bit 4

SATA_DISP_FS4

SATA_DISP Freq. Select MSB

RW

Bit 3

Bit 2

Bit 1

Bit 0

SATA_DISP_FS3

SATA_DISP_FS2

SATA_DISP_FS1

SATA_DISP Freq. Select

SATA_DISP Freq. Select

SATA_DISP Freq. Select

RW

RW

RW

SATA_DISP_FS0

SATA_DISP Freq. Select LSB

RW

Byte

4

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

SMBus Table: SRC Frequency Control Register

Name

Control Function

CLKR EQ1

CLKREQ1 controls SRC1

CLKR EQ0

CLKREQ0 controls SRC0

SRC SS TYPE

SRC _SS_RNG

SRC_SS_EN

SRC_SS_SEL1

SRC_SS_SEL0

IDT® FUSION II CLOCK GENERATOR

Dow n or Center Spread

Normal or Low Range

SRC Spread Enable

SRC Spread Amount

SRC Spread Amount

Type

RW

RW

Reserved

RW

RW

RW

RW

RW

1

0

See SATA_DISP Frequency Select Table

1

1

1

1

0

D oes not control

D oes not control

1

Controls

Controls

Down

Center

Normal

Low R ange (