L9347

Intelligent quad (2x5A/2x2.5A) low-side switch

Features

■

Quad low-side switch

■

2 x 5A designed as conventional switch

■

2 x 2.5A designed as switched currentregulator

■

Low ON resistance 2 x 0.2, 2 x 0.35 (typ.)

■

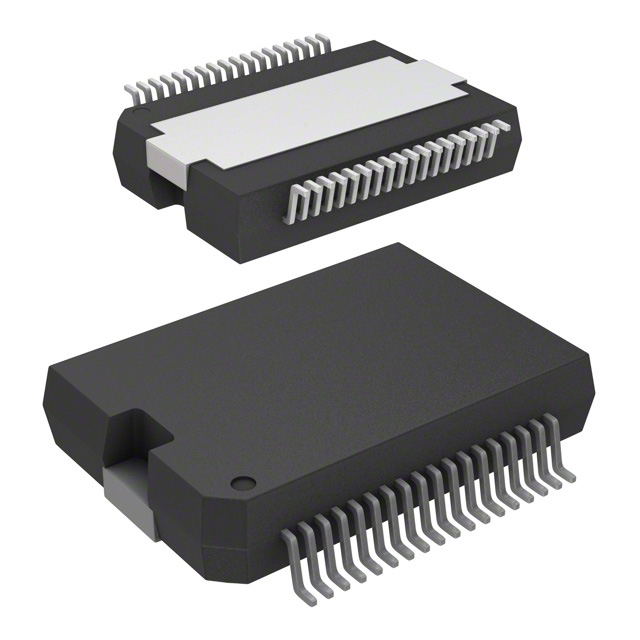

Power SO-36 package with integrated

cooling area

■

Integrated free wheeling and clamping Z

diodes

■

Output slope control

■

Short circuit protection

■

Selective overtemperature shutdown

■

Open load detection

■

Ground and supply loss detection

■

External clock control

■

Recirculation control

■

Regulator drift detection

■

Regulator error control

■

Regulator resolution 5mA

■

Status monitoring

■

Status push-pull stages

■

Electrostatic discharge (ESD) protection

Table 1.

PowerSO-36

Bare Die

Description

The L9347 is an integrated quad low-side power

switch to drive inductive loads like valves used in

ABS systems. Two of the four channels are

current regulators with current range from 250mA

to 2.25A and an accuracy of 10%.

All channels are protected against fail functions.

They are monitored by a status output.

Device summary

Part number

Package

Packing

L9347LF

PowerSO-36

Tray

L9347LF-TR

PowerSO-36

Tape and reel

L9347DIE1

Bare die

Bare die

September 2013

Rev 3

1/29

www.st.com

1

�Contents

L9347

Contents

1

Block diagram and pin connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2

Electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

4

3.1

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.2

Input circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.3

Output stages (not regulated) Channel 1 and 2 . . . . . . . . . . . . . . . . . . . . 13

3.4

Current regulator stages Channel 3 and 4 . . . . . . . . . . . . . . . . . . . . . . . . 13

3.5

Protective circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.6

Error detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.7

Drift detection (regulated channels only) . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.8

Other test modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.9

Diagnostic table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Timing diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.1

Non regulated channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.2

Regulated channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5

Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

6

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2/29

�L9347

List of tables

List of tables

Table 1.

Table 2.

Table 3.

Table 4.

Table 5.

Table 6.

Table 7.

Table 8.

Table 9.

Table 10.

Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Electrical characteristcs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Thermal data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Operating range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Detected errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Special test mode functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Diagnostic table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3/29

�List of figures

L9347

List of figures

Figure 1.

Figure 2.

Figure 3.

Figure 4.

Figure 5.

Figure 6.

Figure 7.

Figure 8.

Figure 9.

Figure 10.

Figure 11.

Figure 12.

Figure 13.

Figure 14.

Figure 15.

Figure 16.

Figure 17.

Figure 18.

4/29

Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Pin connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Input PWM to output current range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Current accuracy according to the input and clock frequency ratio . . . . . . . . . . . . . . . . . . 14

Output slope, resistive load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Overload switch OFF delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Normal condition, resistive load, pulsed input signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Current overload . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Under current condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Open load condition in the case of pulsed input signal. . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Pulsed open load conditions (regulated and non-regulated channels) . . . . . . . . . . . . . . . . 23

Normal condition, inductive load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Current overload . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Recirculation error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Current regulation error (e.g. as a result of voltage reduction) . . . . . . . . . . . . . . . . . . . . . . 25

Over temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Test mode 4 (VEN low). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

PowerSO-36 mechanical data and package dimensions . . . . . . . . . . . . . . . . . . . . . . . . . 27

�L9347

1

Block diagram and pin connections

Block diagram and pin connections

Figure 1.

Block diagram

VS

VCC

VDD

Internal Supply

EN

Overtemperature

Channel 4

Overtemperature

Channel 1

CLK

Open Load

Overload

IN1

Q1

LOGIC

ST1

IPD

GND-det.

Open Load

D4

IN4

LOGIC

&

DA

Overload

Q4

ST4

IPD

GND-det.

Overtemperature

Channel 3

Overtemperature

Channel 2

Open Load

Overload

IN2

Q2

LOGIC

ST2

IPD

GND-det.

Open Load

D3

IN3

LOGIC

&

DA

Overload

Q3

ST3

IPD

GND-det.

drift-det.

TEST

99AT0059

GND

5/29

�Block diagram and pin connections

Figure 2.

L9347

Pin connections

GND

PGND3

PGND3

Q3

Q3

D3

D3

Q1

Q1

Q2

Q2

D4

D4

Q4

Q4

PGND4

PGND4

N.C.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

CLK

ST3

IN1

IN3

ST1

PGND1

PGND1

VS

PGND2

PGND2

TEST

EN

ST2

IN4

IN2

ST4

VDD

VCC

99AT0060

Table 2.

6/29

Pin description

N°

Pin

Function

1

GND

2, 3

PGND 3

Power Ground Channel 3

4, 5

Q3

Power Output Channel 3

6, 7

D3

Free-Wheeling Diode Channel 3

8, 9

Q1

Power Output Channel 1

10, 11

Q2

Power Output Channel 2

12, 13

D4

Free-Wheeling Diode Channel 4

14, 15

Q4

Power Output Channel 4

16, 17

PGND 4

Power Ground Channel 4

18

NC

19

VCC

5V Supply

20

VDD

5V Supply

21

ST 4

Status Output Channel 4

22

IN 2

Control Input Channel 2

23

IN 4

Control Input Channel 4

24

ST 2

Status Output Channel 2

25

EN

26

TEST

27, 28

PGND 2

29

VS

Logic Ground

Not Connected

Enable Input for all four Channels

Enable Input for Drift detection

Power Ground Channel 2

Supply Voltage

�L9347

Block diagram and pin connections

Table 2.

Pin description (continued)

N°

Pin

Function

30, 31

PGND 1

Power Ground Channel 1

32

ST 1

Status Output Channel 1

33

IN 3

Control Input Channel 3

34

IN 1

Control Input Channel 1

35

ST 3

Status Output Channel 3

36

CLK

Clock Input

7/29

�Electrical specifications

L9347

2

Electrical specifications

Table 3.

Electrical characteristcs:

(Vs = 4.8 to 18V; Tj = -40 to 150°C unless otherwise specified)

Symbol

Parameter

Test condition

Min.

Typ.

Max.

Unit

Power supply

ISON

Supply current

VS 18V

(outputs ON)

5

mA

ISOFF

Quiescent current

VS 18V

(outputs OFF)

5

mA

Icc

Supply current VCC (analog supply)

VCC =5V

5

mA

Idd

Supply current VDD (digital supply)

VDD =5V fCLK=0Hz

5

uA

Idd

Supply current VDD (digital supply)

VDD =5V fCLK=250kHz

5

mA

0.36

x VQ

1

V

3.5

V

100

kHz

45

%

General diagnostic functions

Open load voltage

VS 6.5V

(outputs OFF)

0.3

VthGND

Signal-GND-loss threshold

VCC= 5V

0.1

VthPGL

Power-GND-loss threshold

VCC= 5V

1.5

fCLK,min

Clock frequency error

VQU

fCLK= 250 kHz

DCCLKe_high Clock duty cycle error detection high

fCLK= 250 kHz

55

VCC = VDD = 5V

2

Supply detection

2.5

10

DCCLKe_low Clock duty cycle error detection low

VSloss

0.33

33,3

66,6

%

4.5

V

140

mA

9

A

90

%

Additional diagnostic functions channel 1 and channel 2 (non regulated channels)

IQU1,2

Open-load current channel 1, 2

VS 6.5V

50

IQO1,2

Over-load current channel 1, 2

VS 6.5V

5

7.5

Additional diagnostic functions channel 3 and channel 4 (regulated channels)

DCOUT

Output duty cycle range

filtered with 10ms

10

IQO3,4

Overload current

channel 3,4

VS 6.5V

2.5

5

8

A

Vrerr

Recirculation error shutdown

threshold (open D3/D4)

Iout > 50mA

45

50

60

V

PWMdOUT

Output PWM ratio during drift

comparison

VIN3 = VIN4 = PWMIN

VTEST = H

+14.3

%

-14.3

Digital inputs (IN1 to IN4, ENA, CLK, TEST). The valid PWM-Ratio for IN3/IN4 is 10% to 90%

8/29

VIL

Input low voltage

-0.3

1

V

VIH

Input high voltage

2

6

V

VIHy

Input voltage hysteresis (1)

20

500

mV

�L9347

Table 3.

Electrical specifications

Electrical characteristcs: (continued)

(Vs = 4.8 to 18V; Tj = -40 to 150°C unless otherwise specified)

Symbol

II

Parameter

Input pull down current

Test condition

Min.

Typ.

Max.

Unit

VIN = 5V, VS 6.5V

8

20

40

A

IST 40A

0

0.4

V

IST -40A

2.5

3.45

V

IST -120A

2

3.45

V

Digital outputs (ST1 to ST4)

VSTL

Status output voltage in low state (2)

VSTH

Status output voltage in high state (2)

RDIAGL

ROUT + RDSON in low state

0.3

0.64

1.5

k

RDIAGH

ROUT + RDSON in high state

1.5

3.2

7.0

k

0.2

0.5

0.5

W

W

W

0.35

0.75

0.75

Power outputs (Q1 to Q4)

RDSON1,2

RDSON3,4

Static drain-source ON-resistance

Q1 and Q2

(non-reg. channels)

Static drain-source ON-resistance

Q3 and Q4

(reg. channels)

IQ = 1A; VS 9.5V

Tj = 25°C

Tj = 125°C(3)

Tj = 150°C(4)

IQ = 1A; VS 9.5V

Tj = 25°C

Tj = 125°C (3)

Tj = 150°C (4)

VF_250mA

Forward voltage of free wheeling path

ID3/4 = -250mA

D3, D4 @250mA

0.5

1.5

V

VF_2.25A

Forward voltage of free wheeling path

ID3/4 = -2.25A

D3, D4 @2.25A

2.0

4.5

V

Rsens

Sense resistor = (VF_2.25AVF_250mA)/2A

1

VZ

Z-diode clamping voltage

IQ 100mA

45

60

V

IPD

Output pull down current

VEN = H, VIN = L

10

150

A

IQlk

Output leakage current

VEN = L; VQ = 20V

5

A

tON

Output ON delay time

IQ = 1A

0

5

20

s

tOFF

Output OFF delay time channel

IQ = 1A

0

10

30

s

Output OFF delay time regulator

(5)

tr

Output rise time

IQ = 1A

tf

Output fall time

IQ = 1A

Timing

tOFFREG

tsf

tlf

tSCP

s

528

0.5

1.5

8

s

0.5

1.5

8

s

fCLK = 250kHz DC =

50%(5)

4

8

s

Long error detection filter time

fCLK = 250kHz DC =

50%(5)

16

32

s

Short circuit switch-OFF delay time

(5)

4

30

s

Short error detection filter time

9/29

�Electrical specifications

Table 3.

L9347

Electrical characteristcs: (continued)

(Vs = 4.8 to 18V; Tj = -40 to 150°C unless otherwise specified)

Symbol

Parameter

tD

Status delay time

tRE

Regulation error status delay time

Test condition

Min.

(5)

Typ.

896

Max.

Unit

1024

us

(5)

10

ms

528

s

(reg. channels only)

(5)

tDreg

Output off status delay time

(reg. channels only

Reg. current accuracy (reg. channels only)

IQ3/Q4

Minimum current

DC = 10%

200

250

300

mA

IQ3/Q4

Maximum current

DC = 90%

2

2.25

2.5

A

Max. regulation deviation @

DC 10% - 90%

250mA < IQ3/Q4 < 400mA

400mA IQ3/Q4 800mA

800mA < IQ3/Q4 < 2.25A

±10

±6

±10

%

%

%

IREG

IQ3/Q4

Min. quant. step

5

mA

250

kHz

2

kHz

Frequencies

CLK frequency

crystal-controlled

Input PWM frequency

(reg. channels only)

1. This parameter will not be tested but assured by design

2. Short circuit between two digital outputs (one in high the other in low state) will lead to the defined result "LOW"

3. Measured chip, bond wires not included

4. Measured on Power SO-36 devices

5. Digital filtered with external clock, only functional test

Table 4.

Symbol

EQ

.

Absolute maximum ratings

The absolute maximum ratings are the limiting values for this device. Damage may occur if

this device is subjected to conditions which are beyond these values

Parameter

Test conditions

Min

Switch off energy for inductive loads

Typ

Max

Unit

50

mJ

Voltages

VS

Supply voltage

-0.3

40

V

VCC, VDD

Supply voltage

-0.3

6

V

40

V

60

V

-1.5

6

V

VQ

Output voltage static

VQ

Output voltage during clamping

t < 1ms

Input voltage IN1 to IN4, EN

II < |10|mA

VIN, VEN

VCLK

Input Voltage CLK

-1.5

6

V

VST

Output voltage status

-0.3

6

V

VD

Recirculation circuits D3, D4

40

V

max. reverse breakdown voltage of free

wheeling diodes D3, D4

55

V

VDRmax

10/29

�L9347

Table 4.

Electrical specifications

Absolute maximum ratings (continued)

The absolute maximum ratings are the limiting values for this device. Damage may occur if

this device is subjected to conditions which are beyond these values

Symbol

Parameter

Test conditions

Min

Typ

Max

Unit

Currents

IQ1/2

Output current for Q1 and Q2

>5

internal

limited

A

IQ3/4

Output current for Q3 and Q4

>3

internal

limited

A

IQ1/2,

IPGND1/2

Output current at reversal supply for Q1

and Q2

-4

A

IQ3/4,

IPGND3/4

Output current at reversal supply for Q3

and Q4

-2

A

Output current status pin

-5

IST

5

mA

ESD Protection

ESD

Electrostatical Discharging

MIL883C

2

kV

ESD

Output Pins (Qx, Dx)

vs. Common GND

(PGND1-4 + GND)

4

kV

Test conditions

Min

Table 5.

Thermal data

Symbol

Parameter

Typ

Max

Unit

150

°C

175

190

°C

Tj

Junction temperature

Tj

Tjc

Junction temperature during clamping

(life time)

t

Tstg

Storage temperature

Tstg

-55

150

°C

Overtemperature shutdown threshold

(1)

175

200

°C

Overtemperature shutdown hysteresis

(1)

Thermal resistance junction to case

RthJC

Tth

Thy

RthJC

t

-40

= 30min

= 15min

10

°C

2

K/W

1. This parameter will not be tested but assured by design.

Table 6.

Operating range

Symbol

Parameter

Test conditions

Min.

Typ.

Max.

Unit

VS

Supply voltage

4.8

18

V

VCC, VDD

Supply voltage

4.5

5.5

V

Supply voltage transient time

-1

1

V/s

-0.3

40

V

60

V

6

V

dVS/dt

VQ

Output voltage static

VQ

Output voltage induced by inductive

switching

VST

Output voltage status

Voltage will be

limited by internal

Z-diode clamping

-0.3

11/29

�Electrical specifications

Table 6.

Symbol

L9347

Operating range (continued)

Parameter

Test conditions

Min.

Typ.

Max.

Unit

IST

Output current status

-1

1

mA

Tj

Junction temperature

-40

150

°C

Tjc

Junction temperature during clamping

175

190

°C

12/29

= 30min

= 15min

�L9347

Functional Description

3

Functional Description

3.1

Overview

The L9347 is designed to drive inductive loads (relays, electromagnetic valves) in low side

configuration. Integrated active Zener-clamp (for channel1 and 2) or free wheeling diodes

(for channel 3 and 4) allow the recirculation of the inductive loads. All four channels are

monitored with a status output. All wiring to the loads and supply pins of the device are

controlled. The device is self-protected against short circuit at the outputs and

overtemperature. For each channel one independent push-pull status output is used for a

parallel diagnostic function.

Channel 3 and 4 work as current regulator. A PWM signal on the input defines the target

output current. The output current is controlled through the output PWM of the power stage.

The regulator limits of 10% or 90% are detected and monitored with the status signal. The

current is measured during recirculation phase of the load.

A test mode compares the differences between the two regulators. This “drift” test compares

the output PWM of the regulators. By this feature a drift of the load during lifetime can be

detected.

3.2

Input circuits

The INput, CLK, TEST and ENable inputs, are active high, consist of Schmidt triggers with

hysteresis. All inputs are connected to pull-down current sources.

3.3

Output stages (not regulated) Channel 1 and 2

The two power outputs (5A) consist of DMOS power transistors with open drain output. The

output stages are protected against short circuit. Via integrated Zener clamp diodes the

overvoltage of the inductive loads due to recirculation are clamped to typ. 52V for fast shut

off of the valves. Parallel to the DMOS transistors there are internal pull-down current

sources. They are provided to assure an open load condition in the OFF state. With EN=low

this current source is switched off, but the open load comparator is still active.

3.4

Current regulator stages Channel 3 and 4

The current-regulator channels are designed to drive inductive loads. The target value of the

current is given by the duty cycle (DC) of the 2kHz PWM input signal. The following figure

shows the relation between the input PWM and the output current and the specified

accuracy.

13/29

�Functional Description

Figure 3.

L9347

Input PWM to output current range

Cu

rre

nt

p

re

cis

io

n

OUTPUT Current [mA]

2250

+-10%

800

+- 6%

400

±10%

250

INPUT PWM[%]

10

90

The ON period of the input signal is measured with a 1MHz clock, synchronized with the

external 250kHz clock. For requested precision of the output current the ratio between the

frequencies of the input signal and the external 250kHz clock has to be fixed according to

the graph shown in Figure 3.

Current accuracy according to the input and clock frequency ratio

current accuracy

Figure 4.

5.6%

112.5

Regulator

125

132

fCLK / fIN

0%

switched off

-10%

The theoretical error is zero for fCLK / fIN = 125.

If the period of the input signal is longer than 132 times the period of the clock the regulator

is switched off. For a clock frequency lower than 100kHz the clock control will also disable

the regulator. For high precision applications the clock frequency and the input frequency

have to be correlated.

14/29

�L9347

Functional Description

The output current is measured during the recirculation of the load. The current sense

resistor is in series to the free wheeling diode. If this recirculation path is interrupted the

regulator stops immediately and the status output remains low for the rest of the input cycle.

The output period is 64 times the clock period. With a clock frequency of 250kHz the output

PWM frequency is 3.9kHz. The output PWM is synchronized with the first negative edge of

the input signal. After that the output and the input are asynchronous. The first period is

used to measure the current. This means the first turn-on of the power is 256s after the first

negative edge of the input signal.

As regulator a digital PI-regulator with the Transfer function for:

KI:

and KP: 0.96

0.126

--------------z–1

for a sampling time of 256s is realised.

To speed up the current settling time the regulator output is locked to 90% output PWM untill

the target current value is reached. This happens alsowhen the target current value

changes and the output PWM reaches 90% during the regulation. The status output gets

low if the target current value is not reached within the regulation error delay time of

tRE=10ms. The output PWM is than out of the regulation range from 10% to 90%.

3.5

Protective circuits

The outputs are protected against current overload, overtemperature, and power-GND-loss.

The external clock is monitored by a clock watchdog. This clock watchdog detects a minimal

frequency fCLK,min and wrong clock duty cycles. The allowed clock duty cycle range is 45% to

55%. The current-regulator stages are protected against recirculation errors, when D3 or D4

is not connected. All these error conditions shut off the power stage and invert the status

output information.

3.6

Error detection

The status outputs indicate the switching state under normal conditions (status LOW = OFF;

status HIGH = ON). If an error occurs, the logic level of the status output is inverted, as listed

in the diagnostic table below. All external errors, for example open load, are filtered

internally. The following table shows the detected errors, the filter times and the detection

mode (on/off).

15/29

�Functional Description

Table 7.

L9347

Detected errors

ON State

EN &IN =

HIGH

Short circuit of the load

OFF State

EN &IN =

LOW

X

Open load

(under voltage detection)

X

Filter

time

Reset done by

tsf

EN & IN = “LOW”

for TD or TDreg

tlf

timer TD

Open load

(under current detection)

X

tsf

timer TD

Over temperature

X

tsf

EN & IN = “LOW”

for TD or TDreg

Power-GND-loss

X

X

tlf

in on: EN & IN = “LOW”

for TD or TDreg

in off: timer TD

Signal-GND-loss

X

X

tlf

timer TD

Supply-VS-loss

X

X

tlf

timer TD

Clock control

X

X

no

in on: EN & IN = “LOW”

for TD or TDreg

in off: timer TD

no

in on: EN & IN = “LOW”

for TD or TDreg

in off: timer TD

Output voltage clamp active

X

(regulated

channels)

EN&IN=low means that at least one between enable and input is low. For the inputs IN = low

means also no input PWM. For the regulator input period longer than TDreg and for the

standard channel input period longer thanTD.

A detected error is stored in an error register. The reset of this register is made with a timer

TD. With this approach all errors are present at the status output at least for the time TD.

All protection functions like short circuit of the output, overtemperature, clock failure or

power-GND-loss in ON condition are stored into an internal “fail” register. The output is then

shut off. The register must be reset with a low signal at the input. A “low signal” means that

the input is low for a time longer than TD or TDReg for the reulated channel, otherwise it is

interpreted as a PWM input signal and the register is left in set mode.

Signal-GND-loss and VS-loss are detected in the active on mode, but they do not set the fail

register. This type of error is only delayed with the standard timer tlf function.

Open load is detected for all four channels in on and off state.

Open load in off condition detects the voltage on the output pin. If this voltage is below 0.33

* VS the error register is set and delayed with TD. A sink current stage pull the output down

to ground, with EN high. With EN low the output is floating in case of openload and the

detection is not assured. In the ON state the load current is monitored by the non-regulated

channels. If it drops below the specified threshold value IQU an open load is detected and

the error register is set and delayed with TD. A regulated channel detects the open load in

the on state with the current regulator error detection. If the output PWM reaches 90% for a

time longer than tRE than an error occurs. This could happen when no load is connected, the

16/29

�L9347

Functional Description

resistivity of the load is too high or the supply voltage too low. The same error is shown if the

regulator is not able to reduce the current in the load in the time tRE, so the output PWM falls

below 10%.

A clock failure (clock loss) is detected when the frequency becomes lower than fCLK,min. All

status outputs are set on error and all power outputs are shut off. The status signals remain

in their state until the clock signal is present again. A clock failure during power on of VCC is

detected only on the regulated channels. The status outputs of the channel 1 and 2 are low

in this case.

3.7

Drift detection (regulated channels only)

The drift detection is used to compare the two regulated channels during regulation. This

“Drift” test compares the output PWM of the regulators. The resistivity of the load influences

the output PWM. The approximated formula for the output current below shows the

dependency of the load resistor to the output PWM. In this formula the energy reduction

during the recirculation is not taken into account. The real output PWM is higher. The

testmode is enabled with IN,EN and TEST high. With an identical 2kHz PWM-Signal

connected to the IN-inputs the output PWM must be in a range of +-14.3%. If the difference

between the two on-times is more than ±14.3% of the expected value an error is detected

and monitored by the status outputs, in the same way as described above, but a drift error

will not be registered and also not delayed with TD as other errors

VBAT

IOUT = ---------------------------- PWM

RL + RON

Drift Definition:

Drift = PWM(1+E) - PWM (1-E) = 2PWM E

Drift * 4 < PWM (1+E)

with E >14.3% a drift is detected

E.. not correlated Error of the channels

%PWM ... Corresponding ideal output PWM to a given input PWM

A 7bit output-PWM-register is used for the comparison. The register with the lower value is

subtracted from the higher one. This result is multiplied by four and compared with the

higher value.

3.8

Other test modes

The test pin is also used to test the regulated channels in the production. With a special

sequence on this pin the power stages of the regulated channels can be controlled direct

from the input. No status feedback of the regulated channels is given. The status output is

clocked by the regulator logic. The output sequence is a indication of a proper logic

functionality. The functionality of this special test mode is shown in Table 8.

17/29

�Functional Description

Table 8.

L9347

Special test mode functionality

EN

In

Test

Out

Status

Note

1

X

X

X

X

disable test mode

1

1

1

on

1

Drift mode

0

X

off

test pattern

test condition one

0

X

off

test pattern

test condition two

0

X

off

test pattern

test condition three

0

0

off

test pattern

test condition four

0

1

on

test pattern

test condition four

For more details about the test conditions see timing diagrams in Section 4.

3.9

Diagnostic table

The status follows the input signal in normal operating conditions.

If any error is detected the status is inverted.

Table 9.

Diagnostic table

Operating Condition

18/29

Test

Enable

Control

Power

Input non- Output/Curr

reg./reg. IN ent reg. Q

Status

Input

Input

TEST

ENA

Output

Normal function

L

L

L

L

L

L

H

H

L

H/PWM

L

H/PWM

OFF

OFF

OFF

ON

L

L

L

H

Open load or short to ground

L

L

L

L

L

L

H

H

L

H/PWM

L

H/PWM

OFF

OFF

OFF

ON

X

X

H

L

Overload or short to supply

Latched overload

Reset latch

Reset latch

L

L

L

L

H

H

H –> L

H

H/PWM

H/PWM

X

H/PWM –> L

OFF

OFF

OFF

OFF

L

L

L

L

Overtemperature

Latched overtemperature

Reset latch

Reset latch

L

L

L

L

H

H

H –> L

H

H/PWM

H/PWM

X

H/PWM –> L

OFF

OFF

OFF

OFF

L

L

L

L

Recirculation error (reg.chn.)

Latched error

Reset latch

Reset latch

L

L

L

L

H

H

H –> L

H

PWM

PWM

X

PWM –> L

OFF

OFF

OFF

OFF

L

L

L

L

ST

�L9347

Functional Description

Table 9.

Diagnostic table (continued)

Operating Condition

Clock failure (clock loss) (1)

Drift (2)

Failure

No failure

Test

Enable

Input

Input

TEST

ENA

L

L

L

L

L

L

H

H

L

H/PWM

L

H/PWM

OFF

OFF

OFF

OFF

H

H

H

L

H

H

H

H

L

L

H

H

L

H/PWM

H/PWM

H/PWM

OFF

OFF

ON

ON

X

X

L

H

Control

Power

Input non- Output/Curr

reg./reg. IN ent reg. Q

Status

Output

ST

1. During power on sequence only detected on channel 3 and 4 (see description).

2. This input combination is also used for an internal chip-test and must not be used.

19/29

�Timing diagrams

L9347

4

Timing diagrams

4.1

Non regulated channels

Figure 5.

Output slope, resistive load

VI

VIH

VIL

t

VQ

tON

tOFF

tf

tr

VS

85% V S

15% V S

t

99AT0061

Figure 6.

Overload switch OFF delay

IQ

IQO

IQU

t

tD

tSCP

VST

tsf

t

00RS0001

20/29

�L9347

Timing diagrams

Figure 7.

Normal condition, resistive load, pulsed input signal

VIN

VQ

IQ

IQU

tD

tD

VST

99AT0063

Figure 8.

Current overload

tD

Reset Fail

register

VIN

VQ

Set Fail

register

IQO

IQ

tD

VST

99AT0064

21/29

�Timing diagrams

L9347

Figure 9 and Figure 10 show diagnostic status output at different OPEN load current

conditions followed by normal operation.

Figure 9.

Under current condition

tD

VIN

VQ

IQ

IQU

tD

VST

99AT0065

Figure 10. Open load condition in the case of pulsed input signal

tD

VIN

VQ

IQU

IQ

tD

VST

99AT0066

22/29

�L9347

Timing diagrams

Figure 11. Pulsed open load conditions (regulated and non-regulated channels)

VIN

VQ

0.33 x VS

IQ

tD

tlf

tlf

VST

99AT0067

4.2

Regulated channels (timing diagrams of diagnostic with

2kHz PWM input signal)

Figure 12. Normal condition, inductive load

tDREG

500μs

VIN

VQ

Target Current

IQ

256μs

256μs

VST

99AT0068

23/29

�Timing diagrams

L9347

Figure 13. Current overload

tDREG

500μs

Reset Fail

register

VIN

VQ

Set fail

registor

IQO

IQ

tsf

VST

99AT0069

Figure 14. Recirculation error

500μs

tDREG

VIN

VQ

IQ

Set Fail

register

target current

VST

99AT0070

24/29

Reset Fail

register

�L9347

Timing diagrams

Figure 15. Current regulation error (e.g. as a result of voltage reduction)

500μs

VIN

VQ

IQ

PWM ratio = 90%

target current

tRE

VST

99AT0071

Figure 16. Over temperature

Over temperature

Condition

500ms

tDREG

Reset Fail

register

VIN

VQ

IQ

Set Fail

register

target current

VST

99AT0072

25/29

�Timing diagrams

L9347

Figure 17. Test mode 4

VTEST

VIN3/4

VQ3/4

99AT0073

26/29

VEN low

�L9347

5

Package information

Package information

In order to meet environmental requirements, ST offers these devices in ECOPACK®

packages. These packages have a lead-free second level interconnect. The category of

second level interconnect is marked on the package and on the inner box label, in

compliance with JEDEC standard JESD97. The maximum ratings related to soldering

conditions are also marked on the inner box label. ECOPACK is an ST trademark.

ECOPACK specifications are available at: www.st.com.

Figure 18. PowerSO-36 mechanical data and package dimensions

DIM.

mm

MIN.

TYP.

A

a1

inch

MAX.

MIN.

TYP.

3.60

0.10

0.30

a2

MAX.

0.1417

0.0039

0.0118

3.30

0.1299

a3

0

0.10

b

0.22

0.38

0.0087

0.0150

0.0039

0.32

0.0091

0.0126

16.00 0.6220

0.6299

c

0.23

D

15.80

D1

9.40

9.80

0.3701

E

13.90

14.5

0.5472

0.5709

E1

10.90

11.10 0.4291

0.4370

E2

E3

e

6.20

0.1142

0.2283

0.65

e3

0

H

15.50

h

0.4350

0.10

0.0039

15.90 0.6102

1.10

0.8

0.2441

0.0256

11.05

G

L

0.3858

2.90

5.80

OUTLINE AND

MECHANICAL DATA

1.10

0.6260

0.0433

0.0315

N

10˚ (max)

s

8˚ (max)

0.0433

PowerSO-36

Note: “D and E1” do not include mold flash or protusions.

- Mold flash or protusions shall not exceed 0.15mm (0.006”)

- Critical dimensions are "a3", "E" and "G".

0096119 C

27/29

�Revision history

6

L9347

Revision history

Table 10.

28/29

Document revision history

Date

Revision

Changes

06-July-2002

1

Initial release.

02-May-2007

2

Package change, text modifications, corporate layout changes.

25-Sep-2013

3

Updated disclaimer.

�L9347

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE

SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B)

AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS

OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT

PURCHASER’S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS

EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR “AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL” INDUSTRY

DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE

DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

29/29

�