Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

ASNT5114-KMC

DC-32Gbps Linearized High Sensitivity D-Type Flip-Flop

High speed broadband D-Type Flip-Flop for data retiming with full rate clock

Sensitive input data buffer with increased CM range that is ideal for sampling applications

Input data single-ended common mode controls

Exhibits low jitter and limited temperature variation over industrial temperature range

4ps set-up/hold time capability

88% clock phase margin for retiming of data input eye

Fully differential CML input interfaces

Fully differential CML output interface with 400mV single-ended swing

Single +3.3V or -3.3V power supply

Power consumption: 530mW

Fabricated in SiGe for high performance, yield, and reliability

Custom CQFP 24-pin package

Rev. 1.4.2

1

Nov 2020

�Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

DESCRIPTION

vee

dcinp

206

vcc

vcc

79

413

50

DFF

core

dp

dn

206

dcinn

413

vee

qp

qn

79

50

vcc

50

vcc

50

vcc

cp

cn

vcc

Fig. 1. Functional Block Diagram

The temperature stable ASNT5114-KMC SiGe IC provides broadband data retiming functionality and is

intended for use in high-speed measurement / test equipment. The IC shown in Fig. 1 can sample a highspeed data signal dp/dn with a full-rate external clock cp/cn to create a full-rate retimed NRZ data output

qp/qn.

The data input buffer is designed to have increased input signal sensitivity and is able to operate over a

wider range of input common mode (CM) voltages. The actual common mode voltage levels on data

inputs dp/dn can be adjusted by applying voltages between vee and vcc to the corresponding control

inputs dcinp/dcinn. The part’s I/O’s support the CML logic interface with on chip equivalent 50Ohm

termination and may be used differentially, AC/DC coupled, single-ended, or in any combination (see

also POWER SUPPLY CONFIGURATION). In case of AC-coupled input data signals, the internal

common mode voltage levels at the inputs of the input buffer are defined by on-chip resistive dividers.

It should be noted that the control inputs dcinp/dcinn should be always connected to voltage sources to

ensure correct 50Ohm terminations for the data inputs.

POWER SUPPLY CONFIGURATION

The part can operate with either a negative supply (vcc = 0.0V = ground and vee = −3.3V), or a positive

supply (vcc = +3.3V and vee = 0.0V = ground). In case of a positive supply, all I/Os need AC termination

when connected to any devices with 50Ohm termination to ground. Different PCB layouts will be needed

for each different power supply combination.

All the characteristics detailed below assume vcc = 0.0V and vee = -3.3V.

Rev. 1.4.2

2

Nov 2020

�Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

ABSOLUTE MAXIMUM RATINGS

Caution: Exceeding the absolute maximum ratings shown in Table 1 may cause damage to this product

and/or lead to reduced reliability. Functional performance is specified over the recommended operating

conditions for power supply and temperature only. AC and DC device characteristics at or beyond the

absolute maximum ratings are not assumed or implied. All min and max voltage limits are referenced to

ground (assumed vcc).

Table 1. Absolute Maximum Ratings

Parameter

Supply Voltage (vee)

Power Consumption

Input Data Voltage Swing (SE)

Input Clk Voltage Swing (SE)

Case Temperature

Storage Temperature

Operational Humidity

Storage Humidity

Min

-40

10

10

Max

-3.6

0.58

1.7

1.7

+90

+100

98

98

Units

V

W

V

V

ºC

ºC

%

%

TERMINAL FUNCTIONS

TERMINAL

Name No.

Type

dp

dn

cp

cn

qp

qn

dcinp

dcinn

Name

vcc

vee

Rev. 1.4.2

DESCRIPTION

High-Speed I/Os

21

CML Differential data inputs with internal SE 50Ohm termination to

Input vcc

23

3

CML Differential clock inputs with internal SE 50Ohm termination

Input to vcc

5

11

CML Differential data outputs with internal SE 50Ohm termination

Output to vcc. Require external SE 50Ohm termination to vcc

9

DC Controls

15

Input Input data DC common mode voltage level controls. Should be

always connected to voltage sources!

17

Supply and Termination Voltages

Description

Pin Number

Positive power supply

2, 4, 6, 8, 10, 12, 14, 16, 18, 20, 22, 24

(+3.3V or 0V)

Negative power supply

1, 7, 13, 19

(0V or -3.3V)

3

Nov 2020

�Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

ELECTRICAL CHARACTERISTICS

PARAMETER

vcc

vee

Ivcc

Power consumption

Junction temperature

Data rate

Swing

CM Voltage Level

Frequency

Swing

CM Voltage Level

Duty Cycle

Clock phase margin

Data rate

Logic “1” level

Logic “0” level

Jitter

Max level

Min level

MIN

TYP

MAX

UNIT

COMMENTS

General Parameters

0.0

V

External ground

-3.1

-3.3

-3.5

V

±6%

160

175

mA

530

580

mW

-25

50

125

°C

HS Input Data (dp/dn)

DC

32

40

Gbps

0.01

1.6

V

Differential or SE, p-p

vcc-1.6+sw/2

vcc-sw/2

V

Must match for both inputs

HS Input Clock (cp/cn)

DC

32

40

GHz

0.05

1.3

V

Differential or SE, p-p

vcc-0.7+sw/2 vcc+0.6-sw/2

V

Must match for both inputs

40

50

60

%

86

88

90

%

For reliable data latching

HS Output Data (qp/qn)

DC

32

40

Gbps

vcc-0.05 vcc-0.03 vcc-0.01

V

vcc-0.46 vcc-0.44 vcc-0.42

V

With external 50Ohm DC termination

0.15

ps

Peak-to-peak at 32Gbps

DC Input Controls (dcinp/dcinn)

vcc + 1.0

V

vcc - 1.0

V

PACKAGE INFORMATION

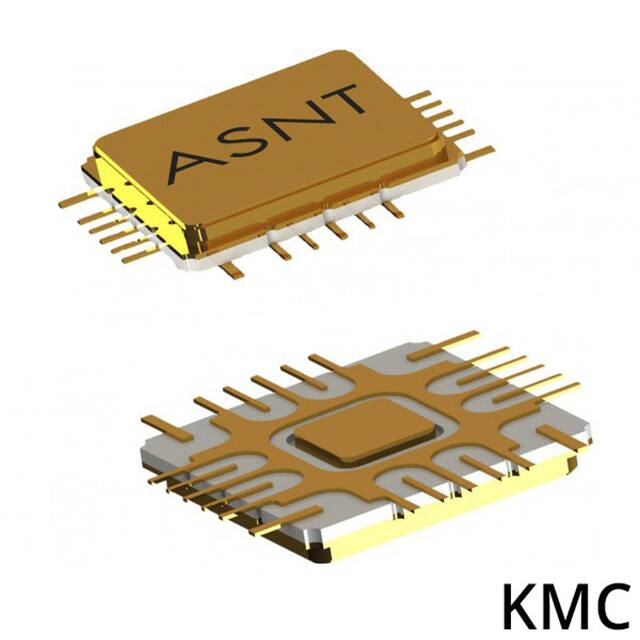

The chip die is housed in a custom 24-pin CQFP package shown in Fig. 2. The package provides a center

heat slug located on its back side to be used for heat dissipation. ADSANTEC recommends for this

section to be soldered to the vcc plain, which is ground for a negative supply, or power for a positive

supply.

The part’s identification label is ASNT5114-KMC. The first 8 characters of the name before the

underscore identify the bare die including general circuit family, fabrication technology, specific circuit

type, and part version while the 3 characters after the underscore represent the package’s manufacturer,

type, and pin out count.

This device complies with the Restriction of Hazardous Substances (RoHS) per 2011/65/EU for all ten

substances.

Rev. 1.4.2

4

Nov 2020

�Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

Fig. 2. CQFP 24-Pin Package Drawing (All Dimensions in mm)

Rev. 1.4.2

5

Nov 2020

�Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

REVISION HISTORY

Revision

1.4.2

1.3.2

1.2.2

1.2.1

1.1.1

1.0.1

Rev. 1.4.2

Date

11-2020

05-2020

07-2019

01-2014

06-2013

02-2013

Changes

Corrected Pin Diagram

Updated Package Information

Updated Letterhead

Corrected title

Removed data duty cycle specification

First release

6

Nov 2020

�