APT38F80B2

APT38F80L

800V, 41A, 0.24Ω Max, trr ≤300ns

N-Channel FREDFET

Power MOS 8™ is a high speed, high voltage N-channel switch-mode power MOSFET.

This 'FREDFET' version has a drain-source (body) diode that has been optimized for

high reliability in ZVS phase shifted bridge and other circuits through reduced trr, soft

recovery, and high recovery dv/dt capability. Low gate charge, high gain, and a greatly

reduced ratio of Crss/Ciss result in excellent noise immunity and low switching loss. The

intrinsic gate resistance and capacitance of the poly-silicon gate structure help control

di/dt during switching, resulting in low EMI and reliable paralleling, even when switching

at very high frequency.

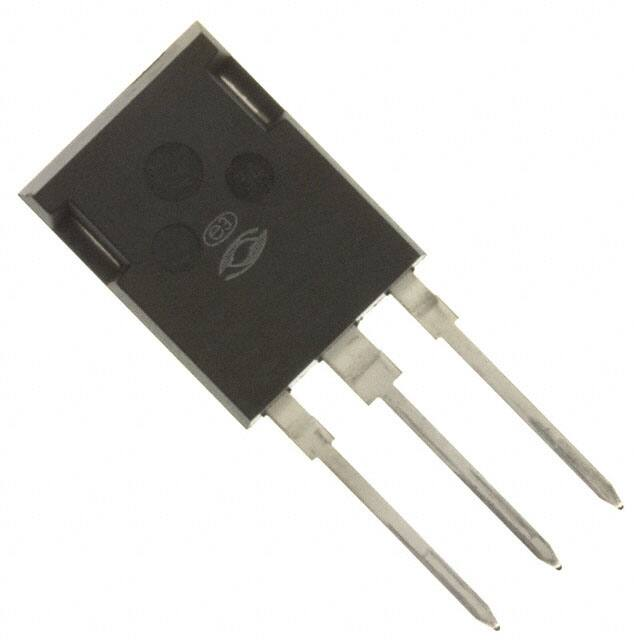

T-Max®

TO-264

APT38F80B2

APT38F80L

D

Single die FREDFET

G

S

TYPICAL APPLICATIONS

FEATURES

• Fast switching with low EMI

• ZVS phase shifted and other full bridge

• Low trr for high reliability

• Half bridge

• Ultra low Crss for improved noise immunity

• PFC and other boost converter

• Low gate charge

• Buck converter

• Avalanche energy rated

• Single and two switch forward

• RoHS compliant

• Flyback

Absolute Maximum Ratings

Symbol

ID

Parameter

Unit

Ratings

Continuous Drain Current @ TC = 25°C

41

Continuous Drain Current @ TC = 100°C

26

A

IDM

Pulsed Drain Current

VGS

Gate-Source Voltage

±30

V

EAS

Single Pulse Avalanche Energy 2

1710

mJ

IAR

Avalanche Current, Repetitive or Non-Repetitive

20

A

1

150

Thermal and Mechanical Characteristics

Min

Characteristic

Typ

Max

Unit

W

PD

Total Power Dissipation @ TC = 25°C

1040

RθJC

Junction to Case Thermal Resistance

0.12

RθCS

Case to Sink Thermal Resistance, Flat, Greased Surface

Operating and Storage Junction Temperature Range

150

°C

Soldering Temperature for 10 Seconds (1.6mm from case)

WT

Package Weight

300

0.22

oz

6.2

g

10

in·lbf

1.1

N·m

Mounting Torque ( TO-264 Package), 4-40 or M3 screw

MicrosemiWebsite-http://www.microsemi.com

04-2009

TL

Torque

-55

Rev C

TJ,TSTG

°C/W

0.11

050-8107

Symbol

�Static Characteristics

TJ = 25°C unless otherwise specified

Symbol

Parameter

VBR(DSS)

Drain-Source Breakdown Voltage

ΔVBR(DSS)/ΔTJ

Breakdown Voltage Temperature Coefficient

RDS(on)

Drain-Source On Resistance

VGS(th)

Gate-Source Threshold Voltage

ΔVGS(th)/ΔTJ

Min

800

VGS = 10V, ID = 20A

3

Zero Gate Voltage Drain Current

IGSS

Gate-Source Leakage Current

Dynamic Characteristics

VDS = 800V

TJ = 25°C

VGS = 0V

TJ = 125°C

Forward Transconductance

Ciss

Input Capacitance

Crss

Reverse Transfer Capacitance

Coss

Output Capacitance

Typ

Max

0.87

0.19

4

-10

0.24

5

250

1000

±100

VGS = ±30V

Unit

V

V/°C

Ω

V

mV/°C

µA

nA

TJ = 25°C unless otherwise specified

Parameter

gfs

2.5

VGS = VDS, ID = 2.5mA

Threshold Voltage Temperature Coefficient

IDSS

Symbol

Test Conditions

VGS = 0V, ID = 250µA

Reference to 25°C, ID = 250µA

APT38F80B2_L

Min

Test Conditions

VDS = 50V, ID = 20A

4

Effective Output Capacitance, Charge Related

Co(er)

5

Effective Output Capacitance, Energy Related

Max

38

8070

140

805

VGS = 0V, VDS = 25V

f = 1MHz

Co(cr)

Typ

Unit

S

pF

380

VGS = 0V, VDS = 0V to 533V

Qg

Total Gate Charge

Qgs

Gate-Source Charge

Qgd

Gate-Drain Charge

td(on)

Turn-On Delay Time

tr

td(off)

tf

Current Rise Time

Turn-Off Delay Time

190

260

44

135

46

65

200

60

VGS = 0 to 10V, ID = 20A,

VDS = 400V

Resistive Switching

VDD = 533V, ID = 20A

RG = 2.2Ω 6 , VGG = 15V

Current Fall Time

nC

ns

Source-Drain Diode Characteristics

Symbol

IS

ISM

VSD

Parameter

Continuous Source Current

(Body Diode)

Pulsed Source Current

(Body Diode) 1

Diode Forward Voltage

trr

Reverse Recovery Time

Qrr

Reverse Recovery Charge

Irrm

Reverse Recovery Current

dv/dt

Peak Recovery dv/dt

Test Conditions

Min

Typ

D

MOSFET symbol

showing the

integral reverse p-n

junction diode

(body diode)

A

150

S

TJ = 25°C

TJ = 125°C

TJ = 25°C

VDD = 100V

TJ = 125°C

diSD/dt = 100A/µs

TJ = 25°C

Unit

41

G

ISD = 20A, TJ = 25°C, VGS = 0V

ISD = 20A 3

Max

TJ = 125°C

ISD ≤ 20A, di/dt ≤1000A/µs, VDD = 533V,

TJ = 125°C

250

485

2

6.7

13

22

1.1

300

600

V

ns

µC

A

20

V/ns

1 Repetitive Rating: Pulse width and case temperature limited by maximum junction temperature.

2 Starting at TJ = 25°C, L = 8.55mH, RG = 25Ω, IAS = 20A.

050-8107

Rev C

04-2009

3 Pulse test: Pulse Width < 380µs, duty cycle < 2%.

4 Co(cr) is defined as a fixed capacitance with the same stored charge as COSS with VDS = 67% of V(BR)DSS.

5 Co(er) is defined as a fixed capacitance with the same stored energy as COSS with VDS = 67% of V(BR)DSS. To calculate Co(er) for any value of

VDS less than V(BR)DSS, use this equation: Co(er) = -2.17E-7/VDS^2 + 2.63E-8/VDS + 3.74E-11.

6 RG is external gate resistance, not including internal gate resistance or gate driver impedance. (MIC4452)

Microsemi reserves the right to change, without notice, the specifications and information contained herein.

�APT38F80B2_L

50

100

V

GS

= 10V

T = 125°C

J

90

TJ = -55°C

70

TJ = 25°C

60

50

40

30

TJ = 125°C

20

30

20

5V

10

4.5V

4V

0

0

5

10

15

20

25

30

VDS(ON), DRAIN-TO-SOURCE VOLTAGE (V)

0

5

10

15

20

25

30

VDS, DRAIN-TO-SOURCE VOLTAGE (V)

Figure 2, Output Characteristics

150

NORMALIZED TO

VDS> ID(ON) x RDS(ON) MAX.

250µSEC. PULSE TEST

@

很抱歉,暂时无法提供与“APT38F80B2”相匹配的价格&库存,您可以联系我们找货

免费人工找货- 国内价格 香港价格

- 1+151.186581+19.40660

- 100+122.68445100+15.74801