dsPIC30F3014/4013

Data Sheet

High-Performance,

16-bit Digital Signal Controllers

2010 Microchip Technology Inc.

DS70138G

�Note the following details of the code protection feature on Microchip devices:

•

Microchip products meet the specification contained in their particular Microchip Data Sheet.

•

Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

•

There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

•

Microchip is willing to work with the customer who is concerned about the integrity of their code.

•

Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device

applications and the like is provided only for your convenience

and may be superseded by updates. It is your responsibility to

ensure that your application meets with your specifications.

MICROCHIP MAKES NO REPRESENTATIONS OR

WARRANTIES OF ANY KIND WHETHER EXPRESS OR

IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION,

INCLUDING BUT NOT LIMITED TO ITS CONDITION,

QUALITY, PERFORMANCE, MERCHANTABILITY OR

FITNESS FOR PURPOSE. Microchip disclaims all liability

arising from this information and its use. Use of Microchip

devices in life support and/or safety applications is entirely at

the buyer’s risk, and the buyer agrees to defend, indemnify and

hold harmless Microchip from any and all damages, claims,

suits, or expenses resulting from such use. No licenses are

conveyed, implicitly or otherwise, under any Microchip

intellectual property rights.

Trademarks

The Microchip name and logo, the Microchip logo, dsPIC,

KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART,

PIC32 logo, rfPIC and UNI/O are registered trademarks of

Microchip Technology Incorporated in the U.S.A. and other

countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor,

MXDEV, MXLAB, SEEVAL and The Embedded Control

Solutions Company are registered trademarks of Microchip

Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard,

dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN,

ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial

Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified

logo, MPLIB, MPLINK, mTouch, Omniscient Code

Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit,

PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance,

TSHARC, UniWinDriver, WiperLock and ZENA are

trademarks of Microchip Technology Incorporated in the

U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2010, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-60932-666-1

Microchip received ISO/TS-16949:2002 certification for its worldwide

headquarters, design and wafer fabrication facilities in Chandler and

Tempe, Arizona; Gresham, Oregon and design centers in California

and India. The Company’s quality system processes and procedures

are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchip’s quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

DS70138G-page 2

2010 Microchip Technology Inc.

�dsPIC30F3014/4013

High-Performance, 16-Bit Digital Signal Controllers

Note:

This data sheet summarizes features of

this group of dsPIC30F devices and is not

intended to be a complete reference

source. For more information on the CPU,

peripherals, register descriptions and

general device functionality, refer to the

“dsPIC30F Family Reference Manual”

(DS70046). For more information on the

device instruction set and programming,

refer to the “16-bit MCU and DSC Programmer’s

Reference

Manual”

(DS70157).

High-Performance Modified RISC CPU:

•

•

•

•

•

•

•

•

•

•

Modified Harvard Architecture

C Compiler Optimized Instruction Set Architecture

Flexible Addressing modes

83 Base Instructions

24-Bit Wide Instructions, 16-Bit Wide Data Path

Up to 48 Kbytes On-Chip Flash Program Space

2 Kbytes of On-Chip Data RAM

1 Kbyte of Nonvolatile Data EEPROM

16 x 16-Bit Working Register Array

Up to 30 MIPS Operation:

- DC to 40 MHz External Clock Input

- 4 MHz-10 MHz Oscillator Input with

PLL Active (4x, 8x, 16x)

• Up to 33 Interrupt Sources:

- 8 user-selectable priority levels

- 3 external interrupt sources

- 4 processor traps

DSP Features:

• Dual Data Fetch

• Modulo and Bit-Reversed modes

• Two 40-Bit Wide Accumulators with Optional

saturation Logic

• 17-Bit x 17-Bit Single-Cycle Hardware

Fractional/Integer Multiplier

• All DSP Instructions are Single Cycle

- Multiply-Accumulate (MAC) Operation

• Single-Cycle ±16 Shift

2010 Microchip Technology Inc.

Peripheral Features:

• High-Current Sink/Source I/O Pins: 25 mA/25 mA

• Up to Five 16-Bit Timers/Counters; Optionally Pair

Up

16-Bit Timers into 32-Bit Timer modules

• Up to Four 16-Bit Capture Input Functions

• Up to Four 16-Bit Compare/PWM Output Functions

• Data Converter Interface (DCI) Supports Common

Audio Codec Protocols, Including I2S and AC’97

• 3-Wire SPI module (supports 4 Frame modes)

• I2C™ module Supports Multi-Master/Slave mode

and 7-Bit/10-Bit Addressing

• Up to Two Addressable UART modules with FIFO

Buffers

• CAN bus module Compliant with CAN 2.0B

Standard

Analog Features:

• 12-Bit Analog-to-Digital Converter (ADC) with:

- 200 ksps conversion rate

- Up to 13 input channels

- Conversion available during Sleep and Idle

• Programmable Low-Voltage Detection (PLVD)

• Programmable Brown-out Reset

Special Microcontroller Features:

• Enhanced Flash Program Memory:

- 10,000 erase/write cycle (min.) for

industrial temperature range, 100K (typical)

• Data EEPROM Memory:

- 100,000 erase/write cycle (min.) for

industrial temperature range, 1M (typical)

• Self-Reprogrammable under Software Control

• Power-on Reset (POR), Power-up Timer (PWRT)

and Oscillator Start-up Timer (OST)

• Flexible Watchdog Timer (WDT) with On-Chip

Low-Power RC Oscillator for Reliable Operation

• Fail-Safe Clock Monitor Operation:

- Detects clock failure and switches to on-chip

low-power RC oscillator

• Programmable Code Protection

• In-Circuit Serial Programming™ (ICSP™)

• Selectable Power Management modes:

- Sleep, Idle and Alternate Clock modes

DS70138G-page 3

�dsPIC30F3014/4013

CMOS Technology:

•

•

•

•

Low-Power, High-Speed Flash Technology

Wide Operating Voltage Range (2.5V to 5.5V)

Industrial and Extended Temperature Ranges

Low-Power Consumption

dsPIC30F3014/4013 Controller Family

Program Memory

48K

8K

16K

2048

2048

1024

3

1024

2

5

4

CAN

dsPIC30F4013 40/44

24K

I2C™

dsPIC30F3014 40/44

SPI

Output

SRAM EEPROM Timer Input

Codec A/D 12-Bit

Comp/

Bytes

Bytes

16-Bit

Cap

Interface 200 Ksps

Bytes Instructions

Std PWM

Pins

UART

Device

2

—

13 ch

2

1

1

0

4

AC’97, I2S

13 ch

2

1

1

1

Pin Diagrams

MCLR

AN0/VREF+/CN2/RB0

AN1/VREF-/CN3/RB1

AN2/SS1/LVDIN/CN4/RB2

AN3/CN5/RB3

AN4/CN6/RB4

AN5/CN7/RB5

PGC/EMUC/AN6/OCFA/RB6

PGD/EMUD/AN7/RB7

AN8/RB8

VDD

Vss

OSC1/CLKI

OSC2/CLKO/RC15

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

INT0/RA11

IC2/INT2/RD9

RD3

Vss

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

MCLR

AN0/VREF+/CN2/RB0

AN1/VREF-/CN3/RB1

AN2/SS1/LVDIN/CN4/RB2

AN3/CN5/RB3

AN4/IC7/CN6/RB4

AN5/IC8/CN7/RB5

PGC/EMUC/AN6/OCFA/RB6

PGD/EMUD/AN7/RB7

AN8/RB8

VDD

VSS

OSC1/CLKI

OSC2/CLKO/RC15

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

INT0/RA11

IC2/INT2/RD9

OC4/RD3

VSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

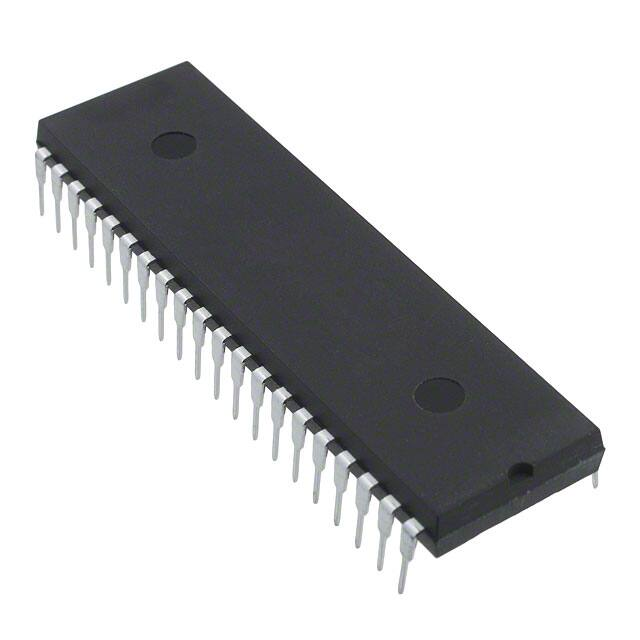

dsPIC30F3014

40-Pin PDIP

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

AVDD

AVss

AN9/RB9

AN10/RB10

AN11/RB11

AN12/RB12

EMUC2/OC1/RD0

EMUD2/OC2/RD1

VDD

Vss

RF0

RF1

U2RX/CN17/RF4

U2TX/CN18/RF5

U1RX/SDI1/SDA/RF2

EMUD3/U1TX/SDO1/SCL/RF3

EMUC3/SCK1/RF6

IC1/INT1/RD8

RD2

VDD

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

AVDD

AVSS

AN9/CSCK/RB9

AN10/CSDI/RB10

AN11/CSDO/RB11

AN12/COFS/RB12

EMUC2/OC1/RD0

EMUD2/OC2/RD1

VDD

VSS

C1RX/RF0

C1TX/RF1

U2RX/CN17/RF4

U2TX/CN18/RF5

U1RX/SDI1/SDA/RF2

EMUD3/U1TX/SDO1/SCL/RF3

EMUC3/SCK1/RF6

IC1/INT1/RD8

OC3/RD2

VDD

DS70138G-page 4

dsPIC30F4013

40-Pin PDIP

2010 Microchip Technology Inc.

�dsPIC30F3014/4013

Pin Diagrams (Continued)

44

43

42

41

40

39

38

37

36

35

34

EMUD3/U1TX/SDO1/SCL/RF3

EMUC3/SCK1/RF6

IC1/NT1/RD8

RD2

VDD

VSS

RD3

IC2/INT2/RD9

INT0/RA11

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

NC

44-Pin TQFP

dsPIC30F3014

33

32

31

30

29

28

27

26

25

24

23

12

13

14

15

16

17

18

19

20

21

22

1

2

3

4

5

6

7

8

9

10

11

NC

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

OSC2/CLKO/RC15

OSC1/CLKI

VSS

VDD

AN8/RB8

PGD/EMUD/AN7/RB7

PGC/EMUC/AN6/OCFA/RB6

AN5/CN7/RB5

AN4/CN6/RB4

NC

NC

AN10/RB10

AN9/RB9

AVSS

AVDD

MCLR

AN0/VREF+/CN2/RB0

AN1/VREF-/CN3/RB1

AN2/SS1/LVDIN/CN4/RB2

AN3/CN5/RB3

U1RX/SDI1/SDA/RF2

U2TX/CN18/RF5

U2RX/CN17/RF4

RF1

RF0

VSS

VDD

EMUD2/OC2/RD1

EMUC2/OC1/RD0

AN12/RB12

AN11/RB11

2010 Microchip Technology Inc.

DS70138G-page 5

�dsPIC30F3014/4013

Pin Diagrams (Continued)

44

43

42

41

40

39

38

37

36

35

34

EMUD3/U1TX/SDO1/SCL/RF3

EMUC3/SCK1/RF6

IC1/INT1/RD8

RD2

VDD

VSS

RD3

IC2/INT2/RD9

INT0/RA11

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

44-Pin QFN(1)

1

2

3

4

5

6

7

8

9

10

11

dsPIC30F3014

33

32

31

30

29

28

27

26

25

24

23

OSC2/CLKO/RC15

OSC1/CLKI

VSS

VSS

VDD

VDD

AN8/RB8

PGD/EMUD/AN7/RB7

PGC/EMUC/AN6/OCFA/RB6

AN5/CN7/RB5

AN4/CN6/RB4

AN11/RB11

NC

AN10/RB10

AN9/RB9

AVSS

AVDD

MCLR

AN0/VREF+/CN2/RB0

AN1/VREF-/CN3/RB1

AN2/SS1/LVDIN/CN4/RB2

AN3/CN5/RB3

12

13

14

15

16

17

18

19

20

21

22

U1RX/SDI1/SDA/RF2

U2TX/CN18/RF5

U2RX/CN17/RF4

RF1

RF0

VSS

VDD

VDD

EMUD2/OC2/RD1

EMUC2/OC1/RD0

AN12/RB12

Note

1:

The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to VSS externally.

DS70138G-page 6

2010 Microchip Technology Inc.

�dsPIC30F3014/4013

Pin Diagrams (Continued)

44

43

42

41

40

39

38

37

36

35

34

EMUD3/U1TX/SDO1/SCL/RF3

EMUC3/SCK1/RF6

IC1/INT1/RD8

OC3/RD2

VDD

VSS

OC4/RD3

IC2/INT2/RD9

INT0/RA11

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

NC

44-Pin TQFP

dsPIC30F4013

33

32

31

30

29

28

27

26

25

24

23

12

13

14

15

16

17

18

19

20

21

22

1

2

3

4

5

6

7

8

9

10

11

NC

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

OSC2/CLKO/RC15

OSC1/CLKI

VSS

VDD

AN8/RB8

PGD/EMUD/AN7/RB7

PGC/EMUC/AN6/OCFA/RB6

AN5/IC8/CN7/RB5

AN4/IC7/CN6/RB4

NC

NC

AN10/CSDI/RB10

AN9/CSCK/RB9

AVSS

AVDD

MCLR

AN0/VREF+/CN2/RB0

AN1/VREF-/CN3/RB1

AN2/SS1/LVDIN/CN4/RB2

AN3/CN5/RB3

U1RX/SDI1/SDA/RF2

U2TX/CN18/RF5

U2RX/CN17/RF4

C1TX/RF1

C1RX/RF0

VSS

VDD

EMUD2/OC2/RD1

EMUC2/OC1/RD0

AN12/COFS/RB12

AN11/CSDO/RB11

2010 Microchip Technology Inc.

DS70138G-page 7

�dsPIC30F3014/4013

Pin Diagrams (Continued)

44

43

42

41

40

39

38

37

36

35

34

EMUD3/U1TX/SDO1/SCL/RF3

EMUC3/SCK1/RF6

IC1/NT1/RD8

OC3/RD2

VDD

VSS

OC4/RD3

IC2/INT2/RD9

INT0/RA11

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

44-Pin QFN(1)

1

2

3

4

5

6

7

8

9

10

11

dsPIC30F4013

33

32

31

30

29

28

27

26

25

24

23

OSC2/CLKO/RC15

OSC1/CLKI

VSS

VSS

VDD

VDD

AN8/RB8

PGD/EMUD/AN7/RB7

PGC/EMUC/AN6/OCFA/RB6

AN5/IC8/CN7/RB5

AN4/IC7/CN6/RB4

AN11/CSDO/RB11

NC

AN10/CSDI/RB10

AN9/CSCK/RB9

AVSS

AVDD

MCLR

AN0/VREF+/CN2/RB0

AN1/VREF-/CN3/RB1

AN2/SS1/LVDIN/CN4/RB2

AN3/CN5/RB3

12

13

14

15

16

17

18

19

20

21

22

U1RX/SDI1/SDA/RF2

U2TX/CN18/RF5

U2RX/CN17/RF4

C1TX/RF1

C1RX/RF0

VSS

VDD

VDD

EMUD2/OC2/RD1

EMUC2/OC1/RD0

AN12/COFS/RB12

Note

1:

The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to VSS externally.

DS70138G-page 8

2010 Microchip Technology Inc.

�dsPIC30F3014/4013

Table of Contents

1.0 Device Overview ........................................................................................................................................................................ 11

2.0 CPU Architecture Overview........................................................................................................................................................ 15

3.0 Memory Organization ................................................................................................................................................................. 25

4.0 Address Generator Units............................................................................................................................................................ 37

5.0 Flash Program Memory.............................................................................................................................................................. 43

6.0 Data EEPROM Memory ............................................................................................................................................................. 49

7.0 I/O Ports ..................................................................................................................................................................................... 53

8.0 Interrupts .................................................................................................................................................................................... 59

9.0 Timer1 Module ........................................................................................................................................................................... 67

10.0 Timer2/3 Module ........................................................................................................................................................................ 71

11.0 Timer4/5 Module ....................................................................................................................................................................... 77

12.0 Input Capture Module................................................................................................................................................................. 81

13.0 Output Compare Module ............................................................................................................................................................ 85

14.0 I2C™ Module ............................................................................................................................................................................. 91

15.0 SPI Module................................................................................................................................................................................. 99

16.0 Universal Asynchronous Receiver Transmitter (UART) Module .............................................................................................. 103

17.0 CAN Module ............................................................................................................................................................................. 111

18.0 Data Converter Interface (DCI) Module.................................................................................................................................... 121

19.0 12-bit Analog-to-Digital Converter (ADC) Module .................................................................................................................... 131

20.0 System Integration ................................................................................................................................................................... 141

21.0 Instruction Set Summary .......................................................................................................................................................... 159

22.0 Development Support............................................................................................................................................................... 167

23.0 Electrical Characteristics .......................................................................................................................................................... 171

24.0 Packaging Information.............................................................................................................................................................. 211

Index ................................................................................................................................................................................................. 219

The Microchip Web Site ..................................................................................................................................................................... 225

Customer Change Notification Service .............................................................................................................................................. 225

Customer Support .............................................................................................................................................................................. 225

Reader Response .............................................................................................................................................................................. 226

Product Identification System ............................................................................................................................................................ 227

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at docerrors@microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150. We

welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of

silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are

using.

Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

2010 Microchip Technology Inc.

DS70138G-page 9

�dsPIC30F3014/4013

NOTES:

DS70138G-page 10

2010 Microchip Technology Inc.

�dsPIC30F3014/4013

1.0

DEVICE OVERVIEW

Note:

This document contains specific information for the

dsPIC30F3014/4013 Digital Signal Controller (DSC)

devices. The dsPIC30F3014/4013 devices contain

extensive Digital Signal Processor (DSP) functionality

within a high-performance, 16-bit microcontroller

(MCU) architecture. Figure 1-1 and Figure 1-2 show

device block diagrams for dsPIC30F3014 and

dsPIC30F4013, respectively.

This data sheet summarizes features of

this group of dsPIC30F devices and is not

intended to be a complete reference

source. For more information on the CPU,

peripherals, register descriptions and

general device functionality, refer to the

“dsPIC30F Family Reference Manual”

(DS70046). For more information on the

device instruction set and programming,

refer to the “16-bit MCU and DSC Programmer’s

Reference

Manual”

(DS70157).

FIGURE 1-1:

dsPIC30F3014 BLOCK DIAGRAM

Y Data Bus

X Data Bus

16

16

Interrupt

Controller

PSV & Table

Data Access

24 Control Block 8

Data Latch

Y Data

RAM

(1 Kbyte)

Address

Latch

16

24

Program Memory

(24 Kbytes)

INT0/RA11

PORTA

16

X RAGU

X WAGU

Y AGU

PCU PCH PCL

Program Counter

Loop

Stack

Control

Control

Logic

Logic

Data Latch

X Data

RAM

(1 Kbyte)

Address

Latch

16

16

24

Address Latch

16

16

AN0/VREF+/CN2/RB0

AN1/VREF-/CN3/RB1

AN2/SS1/LVDIN/CN4/RB2

AN3/CN5/RB3

AN4/CN6/RB4

AN5/CN7/RB5

PGC/EMUC/AN6/OCFA/RB6

PGD/EMUD/AN7/RB7

AN8/RB8

AN9/RB9

AN10/RB10

AN11/RB11

AN12/RB12

16

Data EEPROM

(1 Kbyte)

Effective Address

16

Data Latch

ROM Latch

16

24

PORTB

IR

16

16

Decode

Instruction

Decode and

Control

Control Signals

to Various Blocks

OSC1/CLKI

PORTC

DSP

Engine

VDD, VSS

AVDD, AVSS

Watchdog

Timer

Low-Voltage

Detect

12-Bit ADC

2010 Microchip Technology Inc.

Divide

Unit

Oscillator

Start-up Timer

EMUC2/OC1/RD0

EMUD2/OC2/RD1

RD2

RD3

IC1/INT1/RD8

IC2/INT2/RD9

ALU

POR/BOR

Reset

MCLR

EMUC1/SOSCO/T1CK/U1ARX/

CN0/RC14

OSC2/CLKO/RC15

16 16

Power-up

Timer

Timing

Generation

EMUD1/SOSCI/T2CK/U1ATX/

CN1/RC13

16 x 16

W Reg Array

16

16

PORTD

Input

Capture

Module

Output

Compare

Module

I2C™

Timers

SPI1

UART1,

UART2

RF0

RF1

U1RX/SDI1/SDA/RF2

EMUD3/U1TX/SDO1/SCL/RF3

U2RX/CN17/RF4

U2TX/CN18/RF5

EMUC3/SCK1/RF6

PORTF

DS70138G-page 11

�dsPIC30F3014/4013

FIGURE 1-2:

dsPIC30F4013 BLOCK DIAGRAM

Y Data Bus

X Data Bus

16

16

Interrupt

Controller

PSV & Table

Data Access

24 Control Block

8

Data Latch

Y Data

RAM

(1 Kbyte)

Address

Latch

16

24

Program Memory

(48 Kbytes)

INT0/RA11

PORTA

16

X RAGU

X WAGU

Y AGU

PCU PCH PCL

Program Counter

Loop

Stack

Control

Control

Logic

Logic

Data Latch

X Data

RAM

(1 Kbyte)

Address

Latch

16

16

24

Address Latch

16

16

AN0/VREF+/CN2/RB0

AN1/VREF-/CN3/RB1

AN2/SS1/LVDIN/CN4/RB2

AN3/CN5/RB3

AN4/IC7/CN6/RB4

AN5/IC8/CN7/RB5

PGC/EMUC/AN6/OCFA/RB6

PGD/EMUD/AN7/RB7

AN8/RB8

AN9/CSCK/RB9

AN10/CSDI/RB10

AN11/CSDO/RB11

AN12/COFS/RB12

16

Data EEPROM

(1 Kbyte)

Effective Address

16

Data Latch

ROM Latch

16

24

PORTB

IR

16

16

Decode

Instruction

Decode &

Control

PORTC

Power-up

Timer

DSP

Engine

EMUC2/OC1/RD0

EMUD2/OC2/RD1

OC3/RD2

OC4/RD3

ALU

POR/BOR

Reset

MCLR

VDD, VSS

AVDD, AVSS

DS70138G-page 12

Divide

Unit

Oscillator

Start-up Timer

Timing

Generation

CAN1

EMUC1/SOSCO/T1CK/U1ARX/

CN0/RC14

OSC2/CLKO/RC15

16 16

Control Signals

to Various Blocks

OSC1/CLKI

EMUD1/SOSCI/T2CK/U1ATX/

CN1/RC13

16 x 16

W Reg Array

Watchdog

Timer

Low-Voltage

Detect

IC1/INT1/RD8

IC2/INT2/RD9

16

16

PORTD

12-Bit ADC

Input

Capture

Module

Output

Compare

Module

I2C™

Timers

DCI

SPI1

UART1,

UART2

C1RX/RF0

C1TX/RF1

U1RX/SDI1/SDA/RF2

EMUD3/U1TX/SDO1/SCL/RF3

U2RX/CN17/RF4

U2TX/CN18/RF5

EMUC3/SCK1/RF6

PORTF

2010 Microchip Technology Inc.

�dsPIC30F3014/4013

Table 1-1 provides a brief description of device I/O pinouts and the functions that may be multiplexed to a port

pin. Multiple functions may exist on one port pin. When

multiplexing occurs, the peripheral module’s functional

requirements may force an override of the data

direction of the port pin.

TABLE 1-1:

PINOUT I/O DESCRIPTIONS

Pin

Type

Buffer

Type

AN0-AN12

I

Analog

Analog input channels. AN6 and AN7 are also used for device programming

data and clock inputs, respectively.

AVDD

P

P

Positive supply for analog module. This pin must be connected at all times.

AVSS

P

P

Ground reference for analog module. This pin must be connected at all times.

CLKI

I

CLKO

O

CN0-CN7,

CN17-CN18

I

ST

Input change notification inputs. Can be software programmed for internal

weak pull-ups on all inputs.

COFS

CSCK

CSDI

CSDO

I/O

I/O

I

O

ST

ST

ST

—

Data Converter Interface Frame Synchronization pin.

Data Converter Interface Serial Clock input/output pin.

Data Converter Interface Serial data input pin.

Data Converter Interface Serial data output pin.

C1RX

C1TX

I

O

ST

—

CAN1 bus receive pin.

CAN1 bus transmit pin.

EMUD

EMUC

EMUD1

EMUC1

EMUD2

EMUC2

EMUD3

EMUC3

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

ST

ST

ST

ST

ST

ST

ST

ST

ICD Primary Communication Channel data input/output pin.

ICD Primary Communication Channel clock input/output pin.

ICD Secondary Communication Channel data input/output pin.

ICD Secondary Communication Channel clock input/output pin.

ICD Tertiary Communication Channel data input/output pin.

ICD Tertiary Communication Channel clock input/output pin.

ICD Quaternary Communication Channel data input/output pin.

ICD Quaternary Communication Channel clock input/output pin.

IC1, IC2, IC7,

IC8

I

ST

Capture inputs 1,2, 7 and 8.

INT0

INT1

INT2

I

I

I

ST

ST

ST

External interrupt 0.

External interrupt 1.

External interrupt 2.

LVDIN

I

Analog

MCLR

I/P

ST

Master Clear (Reset) input or programming voltage input. This pin is an

active-low Reset to the device.

OCFA

OC1-OC4

I

O

ST

—

Compare Fault A input (for Compare channels 1, 2, 3 and 4).

Compare outputs 1 through 4.

OSC1

I

OSC2

I/O

PGD

PGC

I/O

I

Pin Name

Description

ST/CMOS External clock source input. Always associated with OSC1 pin function.

Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator

mode. Optionally functions as CLKO in RC and EC modes.

—

Always associated with OSC2 pin function.

Low-Voltage Detect Reference Voltage Input pin.

ST/CMOS Oscillator crystal input. ST buffer when configured in RC mode; CMOS

otherwise.

—

Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator

mode. Optionally functions as CLKO in RC and EC modes.

ST

ST

In-Circuit Serial Programming data input/output pin.

In-Circuit Serial Programming clock input pin.

Legend: CMOS = CMOS compatible input or output

ST

= Schmitt Trigger input with CMOS levels

I

= Input

2010 Microchip Technology Inc.

Analog = Analog input

O

= Output

P

= Power

DS70138G-page 13

�dsPIC30F3014/4013

TABLE 1-1:

PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin

Type

Buffer

Type

RA11

I/O

ST

PORTA is a bidirectional I/O port.

RB0-RB12

I/O

ST

PORTB is a bidirectional I/O port.

RC13-RC15

I/O

ST

PORTC is a bidirectional I/O port.

RD0-RD3,

RD8, RD9

I/O

ST

PORTD is a bidirectional I/O port.

Pin Name

Description

RF0-RF5

I/O

ST

PORTF is a bidirectional I/O port.

SCK1

SDI1

SDO1

SS1

I/O

I

O

I

ST

ST

—

ST

Synchronous serial clock input/output for SPI1.

SPI1 data in.

SPI1 data out.

SPI1 slave synchronization.

SCL

SDA

I/O

I/O

ST

ST

Synchronous serial clock input/output for I2C™.

Synchronous serial data input/output for I2C.

SOSCO

SOSCI

O

I

T1CK

T2CK

I

I

ST

ST

Timer1 external clock input.

Timer2 external clock input.

U1RX

U1TX

U1ARX

U1ATX

I

O

I

O

ST

—

ST

—

UART1 receive.

UART1 transmit.

UART1 alternate receive.

UART1 alternate transmit.

VDD

P

—

Positive supply for logic and I/O pins.

VSS

P

—

VREF+

I

Analog

Analog voltage reference (high) input.

VREF-

I

Analog

Analog voltage reference (low) input.

—

32 kHz low-power oscillator crystal output.

ST/CMOS 32 kHz low-power oscillator crystal input. ST buffer when configured in RC

mode; CMOS otherwise.

Ground reference for logic and I/O pins.

Legend: CMOS = CMOS compatible input or output

ST

= Schmitt Trigger input with CMOS levels

I

= Input

DS70138G-page 14

Analog = Analog input

O

= Output

P

= Power

2010 Microchip Technology Inc.

�dsPIC30F3014/4013

2.0

Note:

2.1

CPU ARCHITECTURE

OVERVIEW

This data sheet summarizes features of

this group of dsPIC30F devices and is not

intended to be a complete reference

source. For more information on the CPU,

peripherals, register descriptions and

general device functionality, refer to the

“dsPIC30F Family Reference Manual”

(DS70046). For more information on the

device instruction set and programming,

refer to the “16-bit MCU and DSC Programmer’s

Reference

Manual”

(DS70157).

Core Overview

This section contains a brief overview of the CPU

architecture of the dsPIC30F.

The core has a 24-bit instruction word. The Program

Counter (PC) is 23 bits wide with the Least Significant

bit (LSb) always clear (refer to Section 3.1 “Program

Address Space”), and the Most Significant bit (MSb)

is ignored during normal program execution, except for

certain specialized instructions. Thus, the PC can

address up to 4M instruction words of user program

space. An instruction prefetch mechanism is used to

help maintain throughput. Program loop constructs,

free from loop count management overhead, are

supported using the DO and REPEAT instructions, both

of which are interruptible at any point.

The working register array consists of 16-bit x 16-bit

registers, each of which can act as data, address or offset registers. One working register (W15) operates as

a Software Stack Pointer for interrupts and calls.

The data space is 64 Kbytes (32K words) and is split

into two blocks, referred to as X and Y data memory.

Each block has its own independent Address Generation Unit (AGU). Most instructions operate solely

through the X memory, AGU, which provides the

appearance of a single, unified data space. The

Multiply-Accumulate (MAC) class of dual source DSP

instructions operate through both the X and Y AGUs,

splitting the data address space into two parts (see

Section 3.2 “Data Address Space”). The X and Y

data space boundary is device-specific and cannot be

altered by the user. Each data word consists of 2 bytes,

and most instructions can address data either as words

or bytes.

2010 Microchip Technology Inc.

There are two methods of accessing data stored in

program memory:

• The upper 32 Kbytes of data space memory can

be mapped into the lower half (user space) of program space at any 16K program word boundary,

defined by the 8-bit Program Space Visibility Page

(PSVPAG) register. This lets any instruction

access program space as if it were data space,

with a limitation that the access requires an additional cycle. Moreover, only the lower 16 bits of

each instruction word can be accessed using this

method.

• Linear indirect access of 32K word pages within

program space is also possible using any working

register, via table read and write instructions.

Table read and write instructions can be used to

access all 24 bits of an instruction word.

Overhead-free circular buffers (Modulo Addressing)

are supported in both X and Y address spaces. This is

primarily intended to remove the loop overhead for

DSP algorithms.

The X AGU also supports Bit-Reversed Addressing on

destination effective addresses to greatly simplify input

or output data reordering for radix-2 FFT algorithms.

Refer to Section 4.0 “Address Generator Units” for

details on Modulo and Bit-Reversed Addressing.

The core supports Inherent (no operand), Relative,

Literal, Memory Direct, Register Direct, Register

Indirect, Register Offset and Literal Offset Addressing

modes. Instructions are associated with predefined

addressing modes, depending upon their functional

requirements.

For most instructions, the core is capable of executing

a data (or program data) memory read, a working register (data) read, a data memory write and a program

(instruction) memory read per instruction cycle. As a

result, 3-operand instructions are supported, allowing

C = A+B operations to be executed in a single cycle.

A DSP engine has been included to significantly

enhance the core arithmetic capability and throughput. It

features a high-speed, 17-bit x 17-bit multiplier, a 40-bit

ALU, two 40-bit saturating accumulators and a 40-bit

bidirectional barrel shifter. Data in the accumulator, or

any working register, can be shifted up to 15 bits right, or

16 bits left in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been

designed for optimal real-time performance. The MAC

class of instructions can concurrently fetch two data

operands from memory while multiplying two W

registers. To enable this concurrent fetching of data

operands, the data space has been split for these

instructions and linear is for all others. This has been

achieved in a transparent and flexible manner by

dedicating certain working registers to each address

space for the MAC class of instructions.

DS70138G-page 15

�dsPIC30F3014/4013

The core does not support a multi-stage instruction

pipeline. However, a single-stage instruction prefetch

mechanism is used, which accesses and partially

decodes instructions a cycle ahead of execution, in

order to maximize available execution time. Most

instructions execute in a single cycle with certain

exceptions.

The core features a vectored exception processing

structure for traps and interrupts, with 62 independent

vectors. The exceptions consist of up to 8 traps (of

which 4 are reserved) and 54 interrupts. Each interrupt

is prioritized based on a user-assigned priority between

1 and 7 (1 being the lowest priority and 7 being the

highest), in conjunction with a predetermined ‘natural

order’. Traps have fixed priorities ranging from 8 to 15.

2.2

Programmer’s Model

The programmer’s model is shown in Figure 2-1 and

consists of 16 x 16-bit working registers (W0 through

W15), 2 x 40-bit accumulators (AccA and AccB),

STATUS register (SR), Data Table Page register

(TBLPAG), Program Space Visibility Page register

(PSVPAG), DO and REPEAT registers (DOSTART,

DOEND, DCOUNT and RCOUNT) and Program Counter (PC). The working registers can act as data,

address or offset registers. All registers are memory

mapped. W0 acts as the W register for file register

addressing.

Some of these registers have a shadow register associated with each of them, as shown in Figure 2-1. The

shadow register is used as a temporary holding register

and can transfer its contents to or from its host register

upon the occurrence of an event. None of the shadow

registers are accessible directly. The following rules

apply for transfer of registers into and out of shadows.

• PUSH.S and POP.S

W0, W1, W2, W3, SR (DC, N, OV, Z and C bits

only) are transferred.

• DO instruction

DOSTART, DOEND, DCOUNT shadows are

pushed on loop start and popped on loop end.

2.2.1

SOFTWARE STACK POINTER/

FRAME POINTER

The dsPIC® DSC devices contain a software stack.

W15 is the dedicated Software Stack Pointer (SP) and

is automatically modified by exception processing and

subroutine calls and returns. However, W15 can be referenced by any instruction in the same manner as all

other W registers. This simplifies the reading, writing

and manipulation of the Stack Pointer (e.g., creating

Stack Frames).

Note:

In order to protect against misaligned

stack accesses, W15 is always clear.

W15 is initialized to 0x0800 during a Reset. The user

may reprogram the SP during initialization to any

location within data space.

W14 has been dedicated as a Stack Frame Pointer, as

defined by the LNK and ULNK instructions. However,

W14 can be referenced by any instruction in the same

manner as all other W registers.

2.2.2

STATUS REGISTER

The dsPIC DSC core has a 16-bit STATUS register

(SR), the Least Significant Byte (LSB) of which is

referred to as the SR Low byte (SRL) and the Most

Significant Byte (MSB) as the SR High byte (SRH). See

Figure 2-1 for SR layout.

SRL contains all the MCU ALU operation status flags

(including the Z bit), as well as the CPU Interrupt Priority Level Status bits, IPL and the Repeat Active

Status bit, RA. During exception processing, SRL is

concatenated with the MSB of the PC to form a

complete word value which is then stacked.

The upper byte of the STATUS register contains the

DSP adder/subtracter Status bits, the DO Loop Active

bit (DA) and the Digit Carry (DC) Status bit.

2.2.3

PROGRAM COUNTER

The program counter is 23 bits wide; bit 0 is always

clear. Therefore, the PC can address up to 4M

instruction words.

When a byte operation is performed on a working

register, only the Least Significant Byte of the target

register is affected. However, a benefit of memory

mapped working registers is that both the Least and

Most Significant Bytes can be manipulated through

byte-wide data memory space accesses.

DS70138G-page 16

2010 Microchip Technology Inc.

�dsPIC30F3014/4013

FIGURE 2-1:

PROGRAMMER’S MODEL

D15

D0

W0/WREG

PUSH.S Shadow

W1

DO Shadow

W2

W3

Legend

W4

DSP Operand

Registers

W5

W6

W7

Working Registers

W8

W9

DSP Address

Registers

W10

W11

W12/DSP Offset

W13/DSP Write-Back

W14/Frame Pointer

W15/Stack Pointer

SPLIM

AD39

Stack Pointer Limit Register

AD15

AD31

AD0

AccA

DSP

Accumulators

AccB

PC22

PC0

Program Counter

0

0

7

TABPAG

TBLPAG

7

Data Table Page Address

0

PSVPAG

Program Space Visibility Page Address

15

0

RCOUNT

REPEAT Loop Counter

15

0

DCOUNT

DO Loop Counter

22

0

DOSTART

DO Loop Start Address

DOEND

DO Loop End Address

22

15

0

Core Configuration Register

CORCON

OA

OB

SA

SB OAB SAB DA

SRH

2010 Microchip Technology Inc.

DC IPL2 IPL1 IPL0 RA

N

OV

Z

C

STATUS Register

SRL

DS70138G-page 17

�dsPIC30F3014/4013

2.3

Divide Support

The dsPIC DSC devices feature a 16/16-bit signed

fractional divide operation, as well as 32/16-bit and 16/

16-bit signed and unsigned integer divide operations, in

the form of single instruction iterative divides. The

following instructions and data sizes are supported:

1.

2.

3.

4.

5.

DIVF – 16/16 signed fractional divide

DIV.sd – 32/16 signed divide

DIV.ud – 32/16 unsigned divide

DIV.s – 16/16 signed divide

DIV.u – 16/16 unsigned divide

The divide instructions must be executed within a

REPEAT loop. Any other form of execution (e.g., a

series of discrete divide instructions) will not function

correctly because the instruction flow depends on

RCOUNT. The divide instruction does not automatically

set up the RCOUNT value and it must, therefore, be

explicitly and correctly specified in the REPEAT instruction, as shown in Table 2-1 (REPEAT will execute the

target instruction {operand value+1} times). The

REPEAT loop count must be setup for 18 iterations of

the DIV/DIVF instruction. Thus, a complete divide

operation requires 19 cycles.

The 16/16 divides are similar to the 32/16 (same number

of iterations), but the dividend is either zero-extended or

sign-extended during the first iteration.

TABLE 2-1:

Note:

The divide flow is interruptible. However,

the user needs to save the context as

appropriate.

DIVIDE INSTRUCTIONS

Instruction

Function

DIVF

Signed fractional divide: Wm/Wn W0; Rem W1

DIV.sd

Signed divide: (Wm+1:Wm)/Wn W0; Rem W1

DIV.s

Signed divide: Wm/Wn W0; Rem W1

DIV.ud

Unsigned divide: (Wm+1:Wm)/Wn W0; Rem W1

DIV.u

Unsigned divide: Wm/Wn W0; Rem W1

DS70138G-page 18

2010 Microchip Technology Inc.

�dsPIC30F3014/4013

2.4

DSP Engine

The DSP engine consists of a high-speed, 17-bit x

17-bit multiplier, a barrel shifter and a 40-bit adder/

subtracter (with two target accumulators, round and

saturation logic).

The DSP engine also has the capability to perform

inherent

accumulator-to-accumulator

operations,

which require no additional data. These instructions are

ADD, SUB and NEG.

The dsPIC30F is a single-cycle instruction flow architecture, therefore, concurrent operation of the DSP

engine with MCU instruction flow is not possible.

However, some MCU ALU and DSP engine resources

may be used concurrently by the same instruction (e.g.,

ED, EDAC). (See Table 2-2 for DSP instructions.)

The DSP engine has various options selected through

various bits in the CPU Core Configuration register

(CORCON), as listed below:

1.

2.

3.

4.

5.

6.

Fractional or integer DSP multiply (IF).

Signed or unsigned DSP multiply (US).

Conventional or convergent rounding (RND).

Automatic saturation on/off for AccA (SATA).

Automatic saturation on/off for AccB (SATB).

Automatic saturation on/off for writes to data

memory (SATDW).

Accumulator Saturation mode selection

(ACCSAT).

7.

Note:

For CORCON layout, see Table 3-3.

A block diagram of the DSP engine is shown in

Figure 2-2.

TABLE 2-2:

Instruction

CLR

Algebraic

Operation

ACC WB?

A=0

Yes

2

A = (x – y)

No

EDAC

A = A + (x – y)2

No

MAC

A = A + (x * y)

Yes

MAC

A = A + x2

No

No change in A

Yes

A=x*y

No

ED

MOVSAC

MPY

MPY.N

MSC

2010 Microchip Technology Inc.

DSP INSTRUCTION

SUMMARY

A=–x*y

No

A=A–x*y

Yes

DS70138G-page 19

�dsPIC30F3014/4013

FIGURE 2-2:

DSP ENGINE BLOCK DIAGRAM

40

S

a

40 Round t 16

u

Logic r

a

t

e

40-Bit Accumulator A

40-Bit Accumulator B

Carry/Borrow Out

Carry/Borrow In

Saturate

Adder

Negate

40

40

40

16

X Data Bus

Barrel

Shifter

40

Y Data Bus

Sign-Extend

32

16

Zero Backfill

32

33

17-Bit

Multiplier/Scaler

16

16

To/From W Array

DS70138G-page 20

2010 Microchip Technology Inc.

�dsPIC30F3014/4013

2.4.1

MULTIPLIER

The 17-bit x 17-bit multiplier is capable of signed or

unsigned operation and can multiplex its output using a

scaler to support either 1.31 fractional (Q31) or 32-bit

integer results. Unsigned operands are zero-extended

into the 17th bit of the multiplier input value. Signed

operands are sign-extended into the 17th bit of the

multiplier input value. The output of the 17-bit x 17-bit

multiplier/scaler is a 33-bit value, which is signextended to 40 bits. Integer data is inherently

represented as a signed two’s complement value,

where the MSB is defined as a sign bit. Generally

speaking, the range of an N-bit two’s complement integer is -2N-1 to 2N-1 – 1. For a 16-bit integer, the data

range is -32768 (0x8000) to 32767 (0x7FFF) including

‘0’. For a 32-bit integer, the data range is 2,147,483,648 (0x8000 0000) to 2,147,483,645

(0x7FFF FFFF).

When the multiplier is configured for fractional multiplication, the data is represented as a two’s complement

fraction, where the MSB is defined as a sign bit and the

radix point is implied to lie just after the sign bit (QX format). The range of an N-bit two’s complement fraction

with this implied radix point is -1.0 to (1 – 21-N). For a

16-bit fraction, the Q15 data range is -1.0 (0x8000) to

0.999969482 (0x7FFF) including ‘0’ and has a precision of 3.01518x10-5. In Fractional mode, the 16x16

multiply operation generates a 1.31 product, which has

a precision of 4.65661 x 10-10.

The same multiplier is used to support the MCU multiply instructions, which includes integer 16-bit signed,

unsigned and mixed sign multiplies.

The MUL instruction can be directed to use byte or

word-sized operands. Byte operands direct a 16-bit

result, and word operands direct a 32-bit result to the

specified register(s) in the W array.

2.4.2

2.4.2.1

The adder/subtracter is a 40-bit adder with an optional

zero input into one side and either true or complement

data into the other input. In the case of addition, the

carry/borrow input is active-high and the other input is

true data (not complemented), whereas in the case of

subtraction, the carry/borrow input is active-low and the

other input is complemented. The adder/subtracter

generates overflow Status bits, SA/SB and OA/OB,

which are latched and reflected in the STATUS register:

• Overflow from bit 39: this is a catastrophic

overflow in which the sign of the accumulator is

destroyed.

• Overflow into guard bits 32 through 39: this is a

recoverable overflow. This bit is set whenever all

the guard bits are not identical to each other.

The adder has an additional saturation block which

controls accumulator data saturation if selected. It uses

the result of the adder, the overflow Status bits

described above, and the SATA/B (CORCON)

and ACCSAT (CORCON) mode control bits to

determine when and to what value to saturate.

Six STATUS register bits have been provided to

support saturation and overflow. They are:

1.

2.

3.

4.

DATA ACCUMULATORS AND

ADDER/SUBTRACTER

The data accumulator consists of a 40-bit adder/

subtracter with automatic sign extension logic. It can

select one of two accumulators (A or B) as its preaccumulation

source

and

post-accumulation

destination. For the ADD and LAC instructions, the data

to be accumulated or loaded can be optionally scaled

via the barrel shifter prior to accumulation.

2010 Microchip Technology Inc.

Adder/Subtracter, Overflow and

Saturation

5.

6.

OA:

AccA overflowed into guard bits

OB:

AccB overflowed into guard bits

SA:

AccA saturated (bit 31 overflow and saturation)

or

AccA overflowed into guard bits and saturated

(bit 39 overflow and saturation)

SB:

AccB saturated (bit 31 overflow and saturation)

or

AccB overflowed into guard bits and saturated

(bit 39 overflow and saturation)

OAB:

Logical OR of OA and OB

SAB:

Logical OR of SA and SB

The OA and OB bits are modified each time data

passes through the adder/subtracter. When set, they

indicate that the most recent operation has overflowed

into the accumulator guard bits (bits 32 through 39).

The OA and OB bits can also optionally generate an

arithmetic warning trap when set and the corresponding overflow trap flag enable bit (OVATE, OVBTE) in

the INTCON1 register (refer to Section 8.0 “Interrupts”) is set. This allows the user to take immediate

action, for example, to correct system gain.

DS70138G-page 21

�dsPIC30F3014/4013

The SA and SB bits are modified each time data

passes through the adder/subtracter but can only be

cleared by the user. When set, they indicate that the

accumulator has overflowed its maximum range (bit 31

for 32-bit saturation or bit 39 for 40-bit saturation) and

will be saturated if saturation is enabled. When

saturation is not enabled, SA and SB default to bit 39

overflow and, thus, indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1

register is set, SA and SB bits generate an arithmetic

warning trap when saturation is disabled.

The overflow and saturation Status bits can optionally

be viewed in the STATUS register (SR) as the logical

OR of OA and OB (in bit OAB) and the logical OR of SA

and SB (in bit SAB). This allows programmers to check

one bit in the STATUS register to determine if either

accumulator has overflowed, or one bit to determine if

either accumulator has saturated. This would be useful

for complex number arithmetic which typically uses

both the accumulators.

The device supports three saturation and overflow

modes:

1.

2.

3.

Bit 39 Overflow and Saturation:

When bit 39 overflow and saturation occurs, the

saturation logic loads the maximally positive 9.31

(0x7FFFFFFFFF), or maximally negative 9.31

value (0x8000000000) into the target accumulator. The SA or SB bit is set and remains set until

cleared by the user. This is referred to as ‘super

saturation’ and provides protection against erroneous data or unexpected algorithm problems

(e.g., gain calculations).

Bit 31 Overflow and Saturation:

When bit 31 overflow and saturation occurs, the

saturation logic then loads the maximally positive 1.31 value (0x007FFFFFFF), or maximally

negative 1.31 value (0x0080000000) into the

target accumulator. The SA or SB bit is set and

remains set until cleared by the user. When this

Saturation mode is in effect, the guard bits are

not used, so the OA, OB or OAB bits are never

set.

Bit 39 Catastrophic Overflow:

The bit 39 overflow Status bit from the adder is

used to set the SA or SB bit which remain set

until cleared by the user. No saturation operation

is performed and the accumulator is allowed to

overflow (destroying its sign). If the COVTE bit in

the INTCON1 register is set, a catastrophic

overflow can initiate a trap exception.

DS70138G-page 22

2.4.2.2

Accumulator ‘Write-Back’

The MAC class of instructions (with the exception of

MPY, MPY.N, ED and EDAC) can optionally write a

rounded version of the high word (bits 31 through 16)

of the accumulator that is not targeted by the instruction

into data space memory. The write is performed across

the X bus into combined X and Y address space. The

following addressing modes are supported:

1.

2.

W13, Register Direct:

The rounded contents of the non-target

accumulator are written into W13 as a

1.15 fraction.

[W13]+=2, Register Indirect with Post-Increment:

The rounded contents of the non-target accumulator are written into the address pointed to by

W13 as a 1.15 fraction. W13 is then

incremented by 2 (for a word write).

2.4.2.3

Round Logic

The round logic is a combinational block which performs

a conventional (biased) or convergent (unbiased) round

function during an accumulator write (store). The Round

mode is determined by the state of the RND bit in the

CORCON register. It generates a 16-bit, 1.15 data value,

which is passed to the data space write saturation logic.

If rounding is not indicated by the instruction, a truncated

1.15 data value is stored and the least significant word

(lsw) is simply discarded.

Conventional rounding takes bit 15 of the accumulator,

zero-extends it and adds it to the ACCxH word (bits 16

through 31 of the accumulator). If the ACCxL word

(bits 0 through 15 of the accumulator) is between

0x8000 and 0xFFFF (0x8000 included), ACCxH is

incremented. If ACCxL is between 0x0000 and 0x7FFF,

ACCxH is left unchanged. A consequence of this algorithm is that over a succession of random rounding

operations, the value tends to be biased slightly

positive.

Convergent (or unbiased) rounding operates in the

same manner as conventional rounding, except when

ACCxL equals 0x8000. If this is the case, the Least Significant bit (LSb) (bit 16 of the accumulator) of ACCxH

is examined. If it is ‘1’, ACCxH is incremented. If it is ‘0’,

ACCxH is not modified. Assuming that bit 16 is

effectively random in nature, this scheme removes any

rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC) or rounded (SAC.R) version of the contents

of the target accumulator to data memory via the X bus

(subject to data saturation, see Section 2.4.2.4 “Data

Space Write Saturation”). Note that for the MAC class

of instructions, the accumulator write-back operation

functions in the same manner, addressing combined

MCU (X and Y) data space though the X bus. For this

class of instructions, the data is always subject to

rounding.

2010 Microchip Technology Inc.

�dsPIC30F3014/4013

2.4.2.4

Data Space Write Saturation

2.4.3

BARREL SHIFTER

In addition to adder/subtracter saturation, writes to data

space may also be saturated but without affecting the

contents of the source accumulator. The data space

write saturation logic block accepts a 16-bit,

1.15 fractional value from the round logic block as its

input, together with overflow status from the original

source (accumulator) and the 16-bit round adder.

These are combined and used to select the appropriate

1.15 fractional value as output to write to data space

memory.

The barrel shifter is capable of performing up to 16-bit

arithmetic or logic right shifts, or up to 16-bit left shifts

in a single cycle. The source can be either of the two

DSP accumulators, or the X bus (to support multi-bit

shifts of register or memory data).

If the SATDW bit in the CORCON register is set, data

(after rounding or truncation) is tested for overflow and

adjusted accordingly. For input data greater than

0x007FFF, data written to memory is forced to the

maximum positive 1.15 value, 0x7FFF. For input data

less than 0xFF8000, data written to memory is forced

to the maximum negative 1.15 value, 0x8000. The

Most Significant bit (MSb) of the source (bit 39) is used

to determine the sign of the operand being tested.

The barrel shifter is 40 bits wide, thereby obtaining a

40-bit result for DSP shift operations and a 16-bit result

for MCU shift operations. Data from the X bus is

presented to the barrel shifter between bit positions 16

to 31 for right shifts, and bit positions 0 to 16 for left

shifts.

The shifter requires a signed binary value to determine

both the magnitude (number of bits) and direction of the

shift operation. A positive value shifts the operand right.

A negative value shifts the operand left. A value of ‘0’

does not modify the operand.

If the SATDW bit in the CORCON register is not set, the

input data is always passed through unmodified under

all conditions.

2010 Microchip Technology Inc.

DS70138G-page 23

�dsPIC30F3014/4013

NOTES:

DS70138G-page 24

2010 Microchip Technology Inc.

�dsPIC30F3014/4013

Note:

MEMORY ORGANIZATION

This data sheet summarizes features of

this group of dsPIC30F devices and is not

intended to be a complete reference

source. For more information on the CPU,

peripherals, register descriptions and

general device functionality, refer to the

“dsPIC30F Family Reference Manual”

(DS70046). For more information on the

device instruction set and programming,

refer to the “16-bit MCU and DSC Programmer’s

Reference

Manual”

(DS70157).

User program space access is restricted to the lower

4M instruction word address range (0x000000 to

0x7FFFFE) for all accesses other than TBLRD/TBLWT,

which use TBLPAG to determine user or configuration space access. In Table 3-1, bit 23 allows access to

the Device ID, the User ID and the Configuration bits;

otherwise, bit 23 is always clear.

FIGURE 3-2:

dsPIC30F4013 PROGRAM

SPACE MEMORY MAP

Reset – GOTO Instruction

Reset – Target Address

000000

000002

000004

Interrupt Vector Table

Program Address Space

Reset – GOTO Instruction

Reset – Target Address

Interrupt Vector Table

Reserved

00007E

000080

User Memory

Space

000084

Alternate Vector Table

0000FE

000100

User Flash

Program Memory

(8K instructions)

Reserved

(Read ‘0’s)

Data EEPROM

(1 Kbyte)

003FFE

004000

000084

0000FE

000100

User Flash

Program Memory

(16K instructions)

Data EEPROM

(1 Kbyte)

000000

000002

000004

00007E

000080

Alternate Vector Table

Reserved

(Read ‘0’s)

dsPIC30F3014 PROGRAM

SPACE MEMORY MAP

Vector Tables

FIGURE 3-1:

Reserved

User Memory

Space

The program address space is 4M instruction words. It

is addressable by a 24-bit value from either the 23-bit

PC, table instruction Effective Address (EA) or data

space EA, when program space is mapped into data

space as defined by Table 3-1. Note that the program

space address is incremented by two between successive program words in order to provide compatibility

with data space addressing.

007FFE

008000

7FFBFE

7FFC00

7FFFFE

800000

Reserved

8005BE

8005C0

Configuration Memory

Space

3.1

Vector Tables

3.0

UNITID (32 instr.)

8005FE

800600

Reserved

Device Configuration

Registers

7FFBFE

7FFC00

F7FFFE

F80000

F8000E

F80010

Reserved

7FFFFE

800000

Reserved

DEVID (2)

FEFFFE

FF0000

FF0002

Configuration Memory

Space

8005BE

8005C0

UNITID (32 instr.)

8005FE

800600

Reserved

Device Configuration

Registers

F7FFFE

F80000

F8000E

F80010

Reserved

DEVID (2)

2010 Microchip Technology Inc.

FEFFFE

FF0000

FF0002

DS70138G-page 25

�dsPIC30F3014/4013

TABLE 3-1:

PROGRAM SPACE ADDRESS CONSTRUCTION

Program Space Address

Access

Space

Access Type

Instruction Access

User

TBLRD/TBLWT

User

(TBLPAG = 0)

TBLPAG

Data EA

TBLRD/TBLWT

Configuration

(TBLPAG = 1)

TBLPAG

Data EA

Program Space Visibility

User

FIGURE 3-3:

PC

0

0

PSVPAG

0

Data EA

DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

23 bits

Using

Program

Counter

Program Counter

0

Select

Using

Program

Space

Visibility

0

1

0

EA

PSVPAG Reg

8 bits

15 bits

EA

Using

Table

Instruction

1/0 TBLPAG Reg

User/

Configuration

Space

Select

Note:

DS70138G-page 26

8 bits

16 bits

24-bit EA

Byte

Select

Program space visibility cannot be used to access bits of a word in program memory.

2010 Microchip Technology Inc.

�dsPIC30F3014/4013

3.1.1

DATA ACCESS FROM PROGRAM

MEMORY USING TABLE

INSTRUCTIONS

A set of table instructions are provided to move byte or

word-sized data to and from program space. (See

Figure 3-4 and Figure 3-5.)

1.

This architecture fetches 24-bit wide program memory.

Consequently, instructions are always aligned.

However, as the architecture is modified Harvard, data

can also be present in program space.

There are two methods by which program space can

be accessed: via special table instructions, or through

the remapping of a 16K word program space page into

the upper half of data space (see Section 3.1.2 “Data

Access from Program Memory Using Program

Space Visibility”). The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lsw

of any address within program space, without going

through data space. The TBLRDH and TBLWTH instructions are the only method whereby the upper 8 bits of a

program space word can be accessed as data.

2.

3.

The PC is incremented by two for each successive

24-bit program word. This allows program memory

addresses to directly map to data space addresses.

Program memory can thus be regarded as two 16-bit

word-wide address spaces, residing side by side, each

with the same address range. TBLRDL and TBLWTL

access the space which contains the least significant

data word, and TBLRDH and TBLWTH access the space

which contains the MS Data Byte.

4.

TBLRDL: Table Read Low

Word: Read the lsw of the program address;

P maps to D.

Byte: Read one of the LSBs of the program

address;

P maps to the destination byte when byte

select = 0;

P maps to the destination byte when byte

select = 1.

TBLWTL: Table Write Low (refer to Section 5.0

“Flash Program Memory” for details on Flash

programming)

TBLRDH: Table Read High

Word: Read the most significant word (msw) of

the program address; P maps to D;

D will always be = 0.

Byte: Read one of the MSBs of the program

address;

P maps to the destination byte when

byte select = 0;

The destination byte will always be = 0 when

byte select = 1.

TBLWTH: Table Write High (refer to Section 5.0

“Flash Program Memory” for details on Flash

Programming)

Figure 3-3 shows how the EA is created for table operations and data space accesses (PSV = 1). Here,

P refers to a program space word, whereas

D refers to a data space word.

FIGURE 3-4:

PROGRAM DATA TABLE ACCESS (LEAST SIGNIFICANT WORD)

PC Address

0x000000

0x000002

0x000004

0x000006

Program Memory

‘Phantom’ Byte

(read as ‘0’)

2010 Microchip Technology Inc.

23

16

8

0

00000000

00000000

00000000

00000000

TBLRDL.W

TBLRDL.B (Wn = 0)

TBLRDL.B (Wn = 1)

DS70138G-page 27

�dsPIC30F3014/4013

FIGURE 3-5:

PROGRAM DATA TABLE ACCESS (MSB)

TBLRDH.W

PC Address

0x000000

0x000002

0x000004

0x000006

23

16

8

0

00000000

00000000

00000000

00000000

TBLRDH.B (Wn = 0)

Program Memory

‘Phantom’ Byte

(read as ‘0’)

3.1.2

TBLRDH.B (Wn = 1)

DATA ACCESS FROM PROGRAM

MEMORY USING PROGRAM SPACE

VISIBILITY

The upper 32 Kbytes of data space may optionally be

mapped into any 16K word program space page. This

provides transparent access of stored constant data

from X data space without the need to use special

instructions (i.e., TBLRDL/H, TBLWTL/H instructions).

Program space access through the data space occurs

if the MSb of the data space, EA, is set and program

space visibility is enabled by setting the PSV bit in the

Core Control register (CORCON). The functions of

CORCON are discussed in Section 2.4 “DSP

Engine”.

Data accesses to this area add an additional cycle to

the instruction being executed, since two program

memory fetches are required.

Note that the upper half of addressable data space is

always part of the X data space. Therefore, when a

DSP operation uses program space mapping to access

this memory region, Y data space should typically contain state (variable) data for DSP operations, whereas

X data space should typically contain coefficient

(constant) data.

Although each data space address, 0x8000 and higher,

maps directly into a corresponding program memory

address (see Figure 3-6), only the lower 16 bits of the

24-bit program word are used to contain the data. The

upper 8 bits should be programmed to force an illegal

instruction to maintain machine robustness. Refer to

the “16-bit MCU and DSC Programmer’s Reference

Manual” (DS70157) for details on instruction encoding.

DS70138G-page 28

Note that by incrementing the PC by 2 for each

program memory word, the 15 LSbs of data space

addresses directly map to the 15 LSbs in the corresponding program space addresses. The remaining

bits are provided by the Program Space Visibility Page

register, PSVPAG, as shown in Figure 3-6.

Note:

PSV access is temporarily disabled during

table reads/writes.

For instructions that use PSV which are executed

outside a REPEAT loop:

• The following instructions require one instruction

cycle in addition to the specified execution time:

- MAC class of instructions with data operand

prefetch

- MOV instructions

- MOV.D instructions

• All other instructions require two instruction cycles

in addition to the specified execution time of the

instruction.

For instructions that use PSV which are executed

inside a REPEAT loop:

• The following instances require two instruction

cycles in addition to the specified execution time

of the instruction:

- Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an

interrupt

- Execution upon re-entering the loop after an

interrupt is serviced

• Any other iteration of the REPEAT loop allows the

instruction accessing data, using PSV, to execute

in a single cycle.

2010 Microchip Technology Inc.

�dsPIC30F3014/4013

FIGURE 3-6:

DATA SPACE WINDOW INTO PROGRAM SPACE OPERATION

Data Space

Program Space

0x0000

0x000100

PSVPAG(1)

0x00

8

15

EA = 0

Data 16

Space

15

EA

EA = 1

0x8000

15

Address

Concatenation 23

23

15

0

0x000200

Upper Half of Data

Space is Mapped

into Program Space

0x007FFF

0xFFFF

BSET

MOV

MOV

MOV

CORCON,#2

#0x00, W0

W0, PSVPAG

0x8200, W0

; PSV bit set

; Set PSVPAG register

; Access program memory location

; using a data space access

Data Read

Note:

PSVPAG is an 8-bit register, containing bits of the program space address (i.e., it defines

the page in program space to which the upper half of data space is being mapped).

The memory map shown here is for a dsPIC30F4013 device.

2010 Microchip Technology Inc.

DS70138G-page 29

�dsPIC30F3014/4013

3.2

Data Address Space

The core has two data spaces. The data spaces can be

considered either separate (for some DSP instructions),

or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address

Generation Units (AGUs) and separate data paths.

3.2.1

DATA SPACE MEMORY MAP

The data space memory is split into two blocks, X and

Y data space. A key element of this architecture is that

Y space is a subset of X space, and is fully contained

within X space. In order to provide an apparent Linear

Addressing space, X and Y spaces have contiguous

addresses.

FIGURE 3-7:

When executing any instruction other than one of

the MAC class of instructions, the X block consists of the

64-Kbyte data address space (including all Y addresses).

When executing one of the MAC class of instructions, the

X block consists of the 64-Kbyte data address space

excluding the Y address block (for data reads only). In

other words, all other instructions regard the entire data