dsPIC33FJ06GS101/X02 and

dsPIC33FJ16GSX02/X04

16-Bit Digital Signal Controllers (up to 16-Kbyte Flash and up to

2-Kbyte SRAM) with High-Speed PWM, ADC and Comparators

Operating Conditions

Advanced Analog Features (Continued)

• 3.0V to 3.6V, -40ºC to +150ºC, DC to 20 MIPS

• 3.0V to 3.6V, -40ºC to +125ºC, DC to 40 MIPS

• 3.0V to 3.6V, -40ºC to +85ºC, DC to 50 MIPS

• Up to Four High-Speed Comparators with Direct

Connection to the PWM module:

- Programmable references with 1024 voltage points

Core: 16-Bit dsPIC33F CPU

Timers/Output Compare/Input Capture

•

•

•

•

•

• Three General Purpose Timers:

- Three 16-bit and one 32-bit timer/counter

• Two Output Compare (OC) modules

• Two Input Capture (IC) modules

• Peripheral Pin Select (PPS) to allow Function Remap

Code-Efficient (C and Assembly) Architecture

Two 40-Bit Wide Accumulators

Single-Cycle (MAC/MPY) with Dual Data Fetch

Single-Cycle Mixed-Sign MUL plus Hardware Divide

32-Bit Multiply Support

Clock Management

•

•

•

•

•

±2.0% Internal Oscillator

Programmable PLLs and Oscillator Clock Sources

Fail-Safe Clock Monitor (FSCM)

Independent Watchdog Timer (WDT)

Fast Wake-up and Start-up

Power Management

• Low-Power Management modes (Sleep, Idle, Doze)

• Integrated Power-on Reset and Brown-out Reset

High-Speed PWM

•

•

•

•

Up to Four PWM Pairs with Independent Timing

Dead Time for Rising and Falling Edges

1.04 ns PWM Resolution

PWM Support for:

- DC/DC, AC/DC, Inverters, PFC and Lighting

• Programmable Fault Inputs

• Flexible Trigger Configurations for ADC Conversions

Advanced Analog Features

• ADC module:

- 10-bit resolution with up to 2 Successive Approximation

Register (SAR) converters (4 Msps) and up to

six Sample-and-Hold (S&H) circuits

- Up to 12 input channels grouped into six conversion

pairs, plus two voltage reference monitoring inputs

- Dedicated result buffer for each analog channel

• Flexible and Independent ADC Trigger Sources

2008-2014 Microchip Technology Inc.

Communication Interfaces

• UART module (12.5 Mbps):

- With support for LIN/J2602 protocols and IrDA®

• 4-Wire SPI module

• I2C™ module (up to 1 Mbaud) with SMBus Support

• PPS to allow Function Remap

Input/Output

• Sink/Source 18 mA on 8 Pins, 10 mA on 10 Pins

and 6 mA on 17 Pins

• 5V Tolerant Pins

• Selectable Open-Drain and Pull-ups

• External Interrupts on up to 30 I/O Pins

Qualification and Class B Support

•

•

•

•

AEC-Q100 REVG (Grade 1, -40ºC to +125ºC)

AEC-Q100 REVG (Grade 0, -40ºC to +150ºC)

Class B Safety Library, IEC 60730, VDE Certified

6x6x0.5 mm UQFN Package Designed and

Optimized to ease IPC9592A 2nd Level Temperature

Cycle Qualification

Debugger Development Support

•

•

•

•

In-Circuit and In-Application Programming

Two Breakpoints

IEEE 1149.2-Compatible (JTAG) Boundary Scan

Trace and Run-Time Watch

DS70000318G-page 1

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

dsPIC33FJ06GS101/X02 AND

dsPIC33FJ16GSX02/X04 PRODUCT

FAMILIES

The device names, pin counts, memory sizes and

peripheral availability of each device are listed below.

The following pages show their pinout diagrams.

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 CONTROLLER FAMILIES

1

1

2x2(1)

0

3

0

1

1

3

6

13

SOIC

dsPIC33FJ06GS102

28

6

256

16

2

0

1

1

1

2x2

0

3

0

1

1

3

6

21

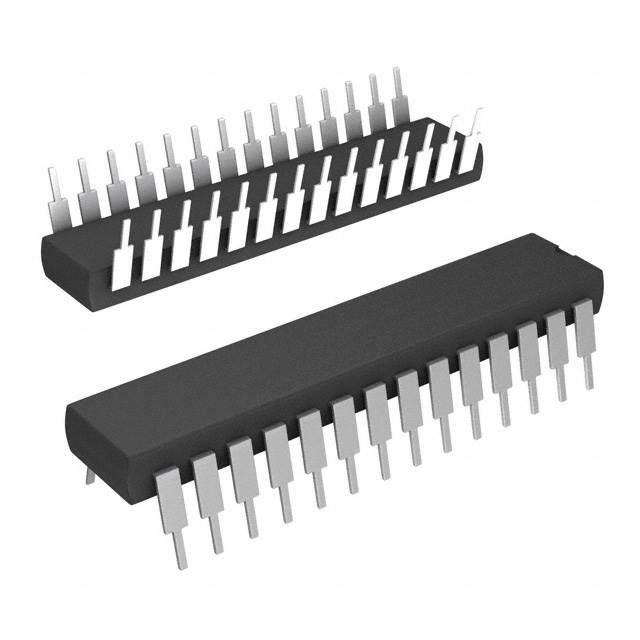

SPDIP,

SOIC,

QFN-S

dsPIC33FJ06GS202

28

6

1K

16

2

1

1

1

1

2x2

2

3

1

1

1

3

6

21

SPDIP,

SOIC,

QFN-S

dsPIC33FJ16GS402

28

16

2K

16

3

2

2

1

1

3x2

0

3

0

1

1

4

8

21

SPDIP,

SOIC,

QFN-S

dsPIC33FJ16GS404

44

16

2K

30

3

2

2

1

1

3x2

0

3

0

1

1

4

8

35

QFN,

TQFP,

VTLA

dsPIC33FJ16GS502

28

16

2K

16

3

2

2

1

1

4x2(1)

4

3

1

1

2

6

8

21

SPDIP,

SOIC,

QFN-S,

UQFN

dsPIC33FJ16GS504

44

16

2K

30

3

2

2

1

1

4x2(1)

4

3

1

1

2

6

12

35

QFN,

TQFP,

VTLA

Note 1:

2:

3:

Packages

1

I/O Pins

PWM(2)

0

Analog-to-Digital Inputs

SPI

2

Sample-and-Hold (S&H) Circuit

UART

8

SARs

Output Compare

256

I2C™

Input Capture

6

DAC Output

16-Bit Timer

18

External Interrupts(3)

Remappable Pins

dsPIC33FJ06GS101

Analog Comparator

Device

RAM (Bytes)

ADC

Program Flash Memory (Kbytes)

Remappable Peripherals

Pins

TABLE 1:

The PWM4H:PWM4L pins are remappable.

The PWM Fault pins and PWM synchronization pins are remappable.

Only two out of three interrupts are remappable.

DS70000318G-page 2

2008-2014 Microchip Technology Inc.

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

Pin Diagrams

= Pins are up to 5V tolerant

18-Pin SOIC

1

2

AN1/RA1

3

AN2/RA2

4

AN3/RP0(1)/CN0/RB0

5

OSC1/CLKI/AN6/RP1(1)/CN1/RB1

6

OSC2/CLKO/AN7/RP2(1)/CN2/RB2

TCK/PGED2/INT0/RP3(1)/CN3/RB3

7

8

TMS/PGEC2/RP4(1)/CN4/RB4

9

dsPIC33FJ06GS101

MCLR

AN0/RA0

18

VDD

17

VSS

16

PWM1L/RA3

15

PWM1H/RA4

14

VCAP

13

VSS

PGEC1/SDA1/RP7(1)/CN7/RB7

12

11

PGED1/TDI/SCL1/RP6(1)/CN6/RB6

TDO/RP5(1)/CN5/RB5

10

= Pins are up to 5V tolerant

28-Pin SOIC, SPDIP

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

dsPIC33FJ06GS102

MCLR

AN0/RA0

AN1/RA1

AN2/RA2

(1)/CN0/RB0

AN3/RP0

AN4/RP9(1)/CN9/RB9

AN5/RP10(1)/CN10/RB10

VSS

OSC1/CLKIN/RP1(1)/CN1/RB1

(1)

OSC2/CLKO/RP2 /CN2/RB2

TCK/PGED2/INT0/RP3(1)/CN3/RB3

TMS/PGEC2/RP4(1)/CN4/RB4

VDD

PGED3/RP8(1)/CN8/RB8

= Pins are up to 5V tolerant

28-Pin SPDIP, SOIC

Note 1:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

dsPIC33FJ06GS202

MCLR

AN0/CMP1A/RA0

AN1/CMP1B/RA1

AN2/CMP1C/CMP2A/RA2

AN3/CMP1D/CMP2B/RP0(1)/CN0/RB0

AN4/CMP2C/RP9(1)/CN9/RB9

AN5/CMP2D/RP10(1)/CN10/RB10

VSS

OSC1/CLKIN/RP1(1)/CN1/RB1

OSC2/CLKO/RP2(1)/CN2/RB2

PGED2/DACOUT/INT0/RP3(1)/CN3/RB3

PGEC2/EXTREF/RP4(1)/CN4/RB4

VDD

PGED3/RP8(1)/CN8/RB8

AVDD

AVSS

PWM1L/RA3

PWM1H/RA4

PWM2L/RP14(1)/CN14/RB14

PWM2H/RP13(1)/CN13/RB13

RP12(1)/CN12/RB12

RP11(1)/CN11/RB11

VCAP

VSS

PGEC1/SDA/RP7(1)/CN7/RB7

PGED1/TDI/SCL/RP6(1)/CN6/RB6

TDO/RP5(1)/CN5/RB5

PGEC3/RP15(1)/CN15/RB15

28

27

26

25

24

23

22

21

20

19

18

17

16

15

AVDD

AVSS

PWM1L/RA3

PWM1H/RA4

PWM2L/RP14(1)/CN14/RB14

PWM2H/RP13(1)/CN13/RB13

TCK/RP12(1)/CN12/RB12

TMS/RP11(1)/CN11/RB11

VCAP

VSS

PGEC1/SDA/RP7(1)/CN7/RB7

PGED1/TDI/SCL/RP6(1)/CN6/RB6

TDO/RP5(1)/CN5/RB5

PGEC3/RP15(1)/CN15/RB15

The RPn pins can be used by any remappable peripheral. See Table 1 for the list of available

peripherals.

2008-2014 Microchip Technology Inc.

DS70000318G-page 3

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

Pin Diagrams (Continued)

28-Pin SPDIP, SOIC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

dsPIC33FJ16GS402

MCLR

AN0/RA0

AN1/RA1

AN2/RA2

AN3/RP0(1)/CN0/RB0

AN4/RP9(1)/CN9/RB9

AN5/RP10(1)/CN10/RB10

VSS

OSC1/CLKIN/AN6/RP1(1)/CN1/RB1

(1)

OSC2/CLKO/AN7/RP2 /CN2/RB2

PGED2/INT0/RP3(1)/CN3/RB3

PGEC2/RP4(1)/CN4/RB4

VDD

PGED3/RP8(1)/CN8/RB8

= Pins are up to 5V tolerant

28

27

26

25

24

23

22

21

20

19

18

17

16

15

AVDD

AVSS

PWM1L/RA3

PWM1H/RA4

PWM2L/RP14(1)/CN14/RB14

PWM2H/RP13(1)/CN13/RB13

TCK/PWM3L/RP12(1)/CN12/RB12

TMS/PWM3H/RP11(1)/CN11/RB11

VCAP

VSS

PGEC1/SDA/RP7(1)/CN7/RB7

PGED1/TDI/SCL/RP6(1)/CN6/RB6

TDO/RP5(1)/CN5/RB5

PGEC3/RP15/CN15/RB15

= Pins are up to 5V tolerant

28-Pin SPDIP, SOIC

Note 1:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

dsPIC33FJ16GS502

MCLR

AN0/CMP1A/RA0

AN1/CMP1B/RA1

AN2/CMP1C/CMP2A/RA2

AN3/CMP1D/CMP2B/RP0(1)/CN0/RB0

AN4/CMP2C/CMP3A/RP9(1)/CN9/RB9

AN5/CMP2D/CMP3B/RP10(1)/CN10/RB10

VSS

OSC1/CLKIN/AN6/CMP3C/CMP4A/RP1(1)/CN1/RB1

OSC2/CLKO/AN7/CMP3D/CMP4B/RP2(1)/CN2/RB2

PGED2/DACOUT/INT0/RP3(1)/CN3/RB3

PGEC2/EXTREF/RP4(1)/CN4/RB4

VDD

CN8/RB8/PGED3/RP8(1)/CN8/RB8

28

27

26

25

24

23

22

21

20

19

18

17

16

15

AVDD

AVSS

PWM1L/RA3

PWM1H/RA4

PWM2L/RP14(1)/CN14/RB14

PWM2H/RP13(1)/CN13/RB13

TCK/PWM3L/RP12(1)/CN12/RB12

TMS/PWM3H/RP11(1)/CN11/RB11

VCAP

VSS

PGEC1/SDA/RP7(1)/CN7/RB7

PGED1/TDI/SCL/RP6(1)/CN6/RB6

TDO/RP5(1)/CN5/RB5

PGEC3/RP15(1)/CN15/RB15

The RPn pins can be used by any remappable peripheral. See Table 1 for the list of available

peripherals.

DS70000318G-page 4

2008-2014 Microchip Technology Inc.

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

Pin Diagrams (Continued)

28-Pin QFN-S(2)

AN1/RA1

AN0/RA0

MCLR

AVDD

AVSS

PWM1L/RA3

PWM1H/RA4

= Pins are up to 5V tolerant

28 27 26 25 24 23 22

1

21

2

20

3

19

4 dsPIC33FJ06GS102 18

5

17

6

16

7

15

8 9 10 11 12 13 14

PWM2L/RP14(1)/CN14/RB14

PWM2H/RP13(1)/CN13/RB13

TCK/RP12(1)/CN12/RB12

TMS/RP11(1)/CN11/RB11

VCAP

VSS

PGEC1/SDA/RP7(1)/CN7/RB7

28 27 26 25 24 23 22

1

21

2

20

3

19

4 dsPIC33FJ06GS202 18

5

17

6

16

7

15

8 9 10 11 12 13 14

PGED2/DACOUT/INT0/RP3(1)/CN3/RB3

AN2/CMP1C/CMP2A/RA2

AN3/CMP1D/CMP2B/RP0(1)/CN0/RB0

AN4/CMP2C/RP9(1)/CN9/RB9

AN5/CMP2D/RP10(1)/CN10/RB10

VSS

OSC1/CLKIN/RP1(1)/CN1/RB1

(1)

OSC2/CLKO/RP2 /CN2/RB2

Note 1:

2:

= Pins are up to 5V tolerant

PWM2L/RP14(1)/CN14/RB14

PWM2H/RP13(1)/CN13/RB13

TCK/RP12(1)/CN12/RB12

TMS/RP11(1)/CN11/RB11

VCAP

VSS

PGEC1/SDA/RP7(1)/CN7/RB7

PGEC2/EXTREF/RP4(1)/CN4/RB4

VDD

PGED3/RP8(1)/CN8/RB8

PGEC3/RP15(1)/CN15/RB15

TDO/RP5(1)/CN5/RB5

PGED1/TDI/SCL/RP6(1)/CN6/RB6

28-Pin QFN-S

AN1/CMP1B/RA1

AN0/CMP1A/RA0

MCLR

AVDD

AVSS

PWM1L/RA3

PWM1H/RA4

PGED2/INT0/RP3(1)/CN3/RB3

PGEC2/RP4(1)/CN4/RB4

VDD

PGED3/RP8(1)/CN8/RB8

(1)/CN15/RB15

PGEC3/RP15

TDO/RP5(1)/CN5/RB5

PGED1/TDI/SCL/RP6(1)/CN6/RB6

AN2/RA2

AN3/RP0(1)/CN0/RB0

AN4/RP9(1)/CN9/RB9

AN5/RP10(1)/CN10/RB10

VSS

OSC1/CLKIN/RP1(1)/CN1/RB1

(1)

OSC2/CLKO/RP2 /CN2/RB2

The RPn pins can be used by any remappable peripheral. See Table 1 for the list of available peripherals.

The metal plane at the bottom of the device is not connected to any pins and is recommended to be

connected to VSS externally.

2008-2014 Microchip Technology Inc.

DS70000318G-page 5

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

28-Pin QFN-S(2)

28 27 26 25 24 23 22

1

21

2

20

3

19

4 dsPIC33FJ16GS402 18

5

17

6

16

7

15

8 9 10 11 12 13 14

= Pins are up to 5V tolerant

PWM2L/RP14(1)/CN14/RB14

PWM2H/RP13(1)/CN13/RB13

TCK/PWM3L/RP12(1)/CN12/RB12

TMS/PWM3H/RP11(1)/CN11/RB11

VCAP

VSS

PGEC1/SDA/RP7(1)/CN7/RB7

PGED2/INT0/RP3(1)/CN3/RB3

PGEC2/RP4(1)/CN4/RB4

VDD

PGED3/RP8(1)/CN8/RB8

PGEC3/RP15(1)/CN15/RB15

TDO/RP5(1)/CN5/RB5

PGED1/TDI/SCL/RP6(1)/CN6/RB6

AN2/RA2

AN3/RP0(1)/CN0/RB0

AN4/RP9(1)/CN9/RB9

AN5/RP10(1)/CN10/RB10

VSS

OSC1/CLKIN/AN6/RP1(1)/CN1/RB1

OSC2/CLKO/AN7/RP2(1)/CN2/RB2

AN1/RA1

AN0/RA0

MCLR

AVDD

AVSS

PWM1L/RA3

PWM1H/RA4

Pin Diagrams (Continued)

28-Pin QFN-S, UQFN(2,3)

AN1/CMP1B/RA1

AN0/CMP1A/RA0

MCLR

AVDD

AVSS

PWM1L/RA3

PWM1H/RA4

= Pins are up to 5V tolerant

28 27 26 25 24 23 22

1

21

2

20

3

19

4 dsPIC33FJ16GS502 18

5

17

6

16

7

15

8 9 10 11 12 13 14

PWM2L/RP14(1)/CN14/RB14

PWM2H/RP13(1)/CN13/RB13

TCK/PWM3L/RP12(1)/CN12/RB12

TMS/PWM3H/RP11(1)/CN11/RB11

VCAP

VSS

PGEC1/SDA/RP7(1)/CN7/RB7

PGED2/DACOUT/INT0/RP3(1)/CN3/RB3

PGEC2/EXTREF/RP4(1)/CN4/RB4

VDD

PGED3/RP8(1)/CN8/RB8

(1)/CN15/RB15

PGEC3/RP15

TDO/RP5(1)/CN5/RB5

PGED1/TDI/SCL/RP6(1)/CN6/RB6

AN2/CMP1C/CMP2A/RA2

AN3/CMP1D/CMP2B/RP0(1)/CN0/RB0

AN4/CMP2C/CMP3A/RP9(1)/CN9/RB9

AN5/CMP2D/CMP3B/RP10(1)/CN10/RB10

VSS

OSC1/CLKIN/AN6/CMP3C/CMP4A/RP1(1)/CN1/RB1

OSC2/CLKO/AN7/CMP3D/CMP4B/RP2(1)/CN2/RB2

Note 1:

2:

3:

The RPn pins can be used by any remappable peripheral. See Table 1 for the list of available peripherals.

The metal plane at the bottom of the device is not connected to any pins and is recommended to be

connected to VSS externally.

This package is available only in Extended temperature and not Industrial temperature (applies to

dsPIC33FJ16GS502 UQFN package only).

DS70000318G-page 6

2008-2014 Microchip Technology Inc.

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

Pin Diagrams (Continued)

44-Pin VTLA(2)

PGEC1/SDA/RP7(1)/CN7/RB7

PGED2/INT0/RP3(1)/CN3/RB3

PGEC2/RP4(1)/CN4/RB4

RP18(1)/CN18/RC2

RP23(1)/CN23/RC7

RP24(1)/CN24/RC8

VDD

VSS

PGED3/RP8(1)/CN8/RB8

PGEC3/RP15(1)/CN15/RB15

TDO/RP5(1)/CN5/RB5

PGED1/TDI/SCL/RP6(1)/CN6/RB6

= Pins are up to 5V tolerant

44 43 42 41 40 39 38 37 36 35 34 33

OSC2/CLKO/AN7/RP2(1)/CN2/RB2

1

32

OSC1/CLKI/AN6/RP1(1)/CN1/RB1

(1)

2

31

RP17(1)/CN17/RC1

(1)

RP21 /CN21/RC5

3

30

VSS

RP22(1)/CN22/RC6

4

29

VDD

RP19(1)/CN19/RC3

5

28

RP26(1)/CN26/RC10

RP20 /CN20/RC4

dsPIC33FJ16GS404

9

24

AN3/RP0(1)/CN0/RB0

PWM2H/RP13(1)/CN13/RB13

10

23

AN2/RA2

PWM2L/RP14(1)/CN14/RB14

11 12 13 14 15 16 17 18 19 20 21 22

Note 1:

2:

(1)

RP27

PWM1H/RA4

TCK/PWM3L/RP12

AN1/RA1

AN4/RP9(1)/CN9/RB9

AN0/RA0

25

RP28 /CN28/RC12

8

(1)/CN12/RB12

MCLR

TMS/PWM3H/RP11 /CN11/RB11

(1)/CN27/RC11

AN5/RP10(1)/CN10/RB10

AVDD

26

(1)

AVSS

RP25(1)/CN25/RC9

RP16(1)/CN16/RC0

27

7

RP29(1)/CN29/RC13

6

PWM1L/RA3

VSS

VCAP

The RPn pins can be used by any remappable peripheral. See Table 1 for the list of available peripherals.

The metal plane at the bottom of the device is not connected to any pins and is recommended to be

connected to VSS externally.

2008-2014 Microchip Technology Inc.

DS70000318G-page 7

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

Pin Diagrams (Continued)

44-Pin VTLA(2)

PGED2/DACOUT/INT0/RP3(1)/CN3/RB3

PGEC2/RP4(1)/CN4/RB4

RP23(1)/CN23/RC7

AN9/EXTREF/CMP4D/RP18(1)/CN18/RC2

VSS

RP24(1)/CN24/RC8

VDD

PGED3/RP8(1)/CN8/RB8

PGEC3/RP15(1)/CN15/RB15

TDO/RP5(1)/CN5/RB5

PGED1/TDI/SCL/RP6(1)/CN6/RB6

= Pins are up to 5V tolerant

44 43 42 41 40 39 38 37 36 35 34 33

OSC2/CLKO/AN7/CMP3D/CMP4B/RP2(1)/CN2/RB2

PGEC1/SDA/RP7 /CN7/RB7

1

32

OSC1/CLKI/AN6/CMP3C/CMP4A/RP1(1)/CN1/RB1

RP20(1)/CN20/RC4

2

31

AN8/CMP4C/RP17(1)/CN17/RC1

RP21(1)/CN21/RC5

3

30

VSS

RP22(1)/RN22/RC6

4

29

VDD

RP19(1)/CN19/RC3

5

28

AN10/RP26(1)/CN26/RC10

(1)

dsPIC33FJ16GS504

24

AN3/CMP1D/CMP2B/RP0(1)/CN0/RB0

10

23

AN2/CMP1C/CMP2A/RA2

PWM2L/RP14(1)/CN14/RB14

11 12 13 14 15 16 17 18 19 20 21 22

RP16

PWM1H/RA4

Note 1:

2:

AN1/CMP1B/RA1

9

PWM2H/RP13(1)/CN13/RB13

AN0/CMP1A/RA0

TCK/PWM3L/RP12 /CN12/RB12

RP28(1)/CN28/RC12

AN4/CMP2C/CMP3A/RP9(1)/CN9/RB9

MCLR

25

RP27(1)/CN27/RC11

8

(1)

TMS/PWM3H/RP11

AVSS

AN5/CMP2D/CMP3B/RP10(1)/CN10/RB10

AVDD

26

(1)/CN11/RB11

RP29(1)/CN29/RC13

27

7

PWM1L/RA3

6

VCAP

(1)/CN16/RC0

VSS

AN11/RP25(1)/CN25/RC9

The RPn pins can be used by any remappable peripheral. See Table 1 for the list of available peripherals.

The metal plane at the bottom of the device is not connected to any pins and is recommended to be

connected to VSS externally.

DS70000318G-page 8

2008-2014 Microchip Technology Inc.

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

Pin Diagrams (Continued)

44-Pin QFN(2)

PGED2/INT0/RP3(1)/CN3/RB3

RP18(1)/CN18/RC2

PGEC2/RP4(1)/CN4/RB4

RP23(1)/CN23/RC7

VDD

VSS

RP24(1)/CN24/RC8

PGED3/RP8(1)/CN8/RB8

PGEC3/RP15(1)/CN15/RB15

PGED1/TDI/SCL/RP6(1)/CN6/RB6

TDO/RP5(1)/CN5/RB5

= Pins are up to 5V tolerant

44 43 42 41 40 39 38 37 36 35 34

PGEC1/SDA/RP7(1)/CN7/RB7

RP20(1)/CN20/RC4

RP21(1)/CN21/RC5

RP22(1)/CN22/RC6

RP19(1)/CN19/RC3

VSS

VCAP

TMS/PWM3H/RP11(1)/CN11/RB11

TCK/PWM3L/RP12(1)/CN12/RB12

PWM2H/RP13(1)/CN13/RB13

PWM2L/RP14(1)/CN14/RB14

1

2

3

4

5

6

7

8

9

10

11

33

32

31

30

29

28

27

26

25

24

23

dsPIC33FJ16GS404

OSC2/CLKO/AN7/RP2(1)/CN2/RB2

OSC1/CLKI/AN6/RP1(1)/CN1/RB1

RP17(1)/CN17/RC1

VSS

VDD

RP26(1)/CN26/RC10

RP25(1)/CN25/RC9

AN5/RP10(1)/CN10/RB10

AN4/RP9(1)/CN9/RB9

AN3/RP0(1)/CN0/RB0

AN2/RA2

Note 1:

2:

AN1/RA1

MCLR

RP27(1)/CN27/RC11

RP28(1)/CN28/RC12

AN0/RA0

AVDD

AVSS

RP16(1)/CN16/RC0

RP29(1)/CN29/RC13

PWM1L/RA3

PWM1H/RA4

12 13 14 15 16 17 18 19 20 21 22

The RPn pins can be used by any remappable peripheral. See Table 1 for the list of available peripherals.

The metal plane at the bottom of the device is not connected to any pins and is recommended to be

connected to VSS externally.

2008-2014 Microchip Technology Inc.

DS70000318G-page 9

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

Pin Diagrams (Continued)

44-Pin QFN(2)

PGED2/DACOUT/INT0/RP3(1)/CN3/RB3

RP23(1)/CN23/RC7

AN9/EXTREF/CMP4D/RP18(1)/CN18/RC2

PGEC2/RP4(1)/CN4/RB4

VDD

VSS

RP24(1)/CN24/RC8

PGEC3/RP15(1)/CN15/RB15

PGED3/RP8(1)/CN8/RB8

PGED1/TDI/SCL/RP6(1)/CN6/RB6

TDO/RP5(1)/CN5/RB5

= Pins are up to 5V tolerant

44 43 42 41 40 39 38 37 36 35 34

PGEC1/SDA/RP7(1)/CN7/RB7

RP20(1)/CN20/RC4

RP21(1)/CN21/RC5

RP22(1)/RN22/RC6

RP19(1)/CN19/RC3

VSS

VCAP

TMS/PWM3H/RP11(1)/CN11/RB11

TCK/PWM3L/RP12(1)/CN12/RB12

PWM2H/RP13(1)/CN13/RB13

PWM2L/RP14(1)/CN14/RB14

1

2

3

4

5

33

32

31

30

29

28

27

dsPIC33FJ16GS504

6

7

8

9

10

11

26

25

24

23

OSC2/CLKO/AN7/CMP3D/CMP4B/RP2(1)/CN2/RB2

OSC1/CLKI/AN6/CMP3C/CMP4A/RP1(1)/CN1/RB1

AN8/CMP4C/RP17(1)/CN17/RC1

VSS

VDD

AN10/RP26(1)/CN26/RC10

AN11/RP25(1)/CN25/RC9

AN5/CMP2D/CMP3B/RP10(1)/CN10/RB10

AN4/CMP2C/CMP3A/RP9(1)/CN9/RB9

AN3/CMP1D/CMP2B/RP0(1)/CN0/RB0

AN2/CMP1C/CMP2A/RA2

Note 1:

2:

AN1/CMP1B/RA1

MCLR

RP27(1)/CN27/RC11

RP28(1)/CN28/RC12

AN0/CMP1A/RA0

AVSS

AVDD

PWM1L/RA3

RP16(1)/CN16/RC0

RP29(1)/CN29/RC13

PWM1H/RA4

12 13 14 15 16 17 18 19 20 21 22

The RPn pins can be used by any remappable peripheral. See Table 1 for the list of available peripherals.

The metal plane at the bottom of the device is not connected to any pins and is recommended to be

connected to VSS externally.

DS70000318G-page 10

2008-2014 Microchip Technology Inc.

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

Pin Diagrams (Continued)

44-Pin TQFP

VDD

VSS

RP24(1)/CN24/RC8

RP23(1)/CN23/RC7

RP18(1)/CN18/RC2

PGEC2/RP4(1)/CN4/RB4

PGED2/INT0/RP3(1)/CN3/RB3

40

39

38

37

36

35

34

42

41

43

PGED1/TDI/SCL/RP6(1)/CN6/RB6

TDO/RP5(1)/CN5/RB5

PGEC3/RP15(1)/CN15/RB15

PGED3/RP8(1)/CN8/RB8

26

AN5/RP10(1)/CN10/RB10

AN4/RP9(1)/CN9/RB9

AN3/RP0(1)/CN0/RB0

AN2/RA2

AN0/RA0

AN1/RA1

RP28 /CN28/RC12

25

24

23

OSC2/CLKO/AN7/RP2(1)/CN2/RB2

OSC1/CLKI/AN6/RP1(1)/CN1/RB1

RP17(1)/CN17/RC1

VSS

VDD

RP26(1)/CN26/RC10

RP25(1)/CN25/RC9

(1)

MCLR

RP27(1)/CN27/RC11

AVDD

RP29(1)/CN29/RC13

AVSS

22

21

20

19

18

17

16

15

14

Note 1:

27

13

12

PWM2L/RP14 /CN14/RB14

33

32

31

30

29

28

dsPIC33FJ16GS404

RP16(1)/CN16/RC0

(1)

6

7

8

9

10

11

PWM1L/RA3

RP19(1)/CN19/RC3

VSS

VCAP

TMS/PWM3H/RP11(1)/CN11/RB11

TCK/PWM3L/RP12(1)/CN12/RB12

PWM2H/RP13(1)/CN13/RB13

1

2

3

4

5

PWM1H/RA4

PGEC1/SDA/RP7(1)/CN7/RB7

RP20(1)/CN20/RC4

RP21(1)/CN21/RC5

RP22(1)/CN22/RC6

44

= Pins are up to 5V tolerant

The RPn pins can be used by any remappable peripheral. See Table 1 for the list of available peripherals.

2008-2014 Microchip Technology Inc.

DS70000318G-page 11

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

Pin Diagrams (Continued)

44-Pin TQFP

VDD

VSS

RP24(1)/CN24/RC8

RP23(1)/CN23/RC7

AN9/EXTREF/CMP4D/RP18(1)/CN18/RC2

PGEC2/RP4(1)/CN4/RB4

PGED2/DACOUT/INT0/RP3(1)/CN3/RB3

40

39

38

37

36

35

34

42

41

PGED1/TDI/SCL/RP6(1)/CN6/RB6

TDO/RP5(1)/CN5/RB5

PGEC3/RP15(1)/CN15/RB15

PGED3/RP8(1)/CN8/RB8

43

44

33

32

31

30

29

28

27

dsPIC33FJ16GS504

25

24

23

OSC2/CLKO/AN7/CMP3D/CMP4B/RP2(1)/CN2/RB2

OSC1/CLKI/AN6/CMP3C/CMP4A/RP1(1)/CN1/RB1

AN8/CMP4C/RP17(1)/CN17/RC1

VSS

VDD

AN10/RP26(1)/CN26/RC10

AN11/RP25(1)/CN25/RC9

AN5/CMP2D/CMP3B/RP10(1)/CN10/RB10

AN4/CMP2C/CMP3A/RP9(1)/CN9/RB9

AN3/CMP1D/CMP2B/RP0(1)/CN0/RB0

AN2/CMP1C/CMP2A/RA2

AN0/CMP1A/RA0

AN1/CMP1B/RA1

RP28(1)/CN28/RC12

MCLR

RP27(1)/CN27/RC11

AVDD

RP29(1)/CN29/RC13

AVSS

PWM1L/RA3

22

21

20

19

RP16(1)/CN16/RC0

26

18

17

16

15

14

Note 1:

6

7

8

9

10

11

13

12

RP19(1)/CN19/RC3

VSS

VCAP

TMS/PWM3H/RP11(1)/CN11/RB11

TCK/PWM3L/RP12(1)/CN12/RB12

PWM2H/RP13(1)/CN13/RB13

PWM2L/RP14(1)/CN14/RB14

1

2

3

4

5

PWM1H/RA4

PGEC1/SDA/RP7(1)/CN7/RB7

RP20(1)/CN20/RC4

RP21(1)/CN21/RC5

RP22(1)/CN22/RC6

= Pins are up to 5V tolerant

The RPn pins can be used by any remappable peripheral. See Table 1 for the list of available peripherals.

DS70000318G-page 12

2008-2014 Microchip Technology Inc.

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

Table of Contents

dsPIC33FJ06GS101/X02 AND dsPIC33FJ16GSX02/X04 Product Families......................................................................................... 2

1.0 Device Overview ........................................................................................................................................................................ 17

2.0 Guidelines for Getting Started with 16-bit Digital Signal Controllers .......................................................................................... 21

3.0 CPU............................................................................................................................................................................................ 31

4.0 Memory Organization ................................................................................................................................................................. 43

5.0 Flash Program Memory.............................................................................................................................................................. 83

6.0 Resets ....................................................................................................................................................................................... 89

7.0 Interrupt Controller ..................................................................................................................................................................... 97

8.0 Oscillator Configuration ......................................................................................................................................................... 135

9.0 Power-Saving Features............................................................................................................................................................ 147

10.0 I/O Ports ................................................................................................................................................................................... 155

11.0 Timer1 ...................................................................................................................................................................................... 183

12.0 Timer2/3 Features ................................................................................................................................................................... 185

13.0 Input Capture............................................................................................................................................................................ 191

14.0 Output Compare....................................................................................................................................................................... 193

15.0 High-Speed PWM..................................................................................................................................................................... 197

16.0 Serial Peripheral Interface (SPI)............................................................................................................................................... 219

17.0 Inter-Integrated Circuit (I2C™) ................................................................................................................................................. 225

18.0 Universal Asynchronous Receiver Transmitter (UART) ........................................................................................................... 233

19.0 High-Speed 10-bit Analog-to-Digital Converter (ADC) ............................................................................................................. 239

20.0 High-Speed Analog Comparator .............................................................................................................................................. 263

21.0 Special Features ...................................................................................................................................................................... 267

22.0 Instruction Set Summary .......................................................................................................................................................... 275

23.0 Development Support............................................................................................................................................................... 283

24.0 Electrical Characteristics .......................................................................................................................................................... 287

25.0 High-Temperature Electrical Characteristics............................................................................................................................ 333

26.0 50 MIPS Electrical Characteristics ........................................................................................................................................... 341

27.0 DC and AC Device Characteristics Graphs.............................................................................................................................. 347

28.0 Packaging Information.............................................................................................................................................................. 351

The Microchip Web Site ..................................................................................................................................................................... 393

Customer Change Notification Service .............................................................................................................................................. 393

Customer Support .............................................................................................................................................................................. 393

Product Identification System ............................................................................................................................................................ 395

2008-2014 Microchip Technology Inc.

DS70000318G-page 13

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at docerrors@microchip.com. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are

using.

Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

DS70000318G-page 14

2008-2014 Microchip Technology Inc.

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

Referenced Sources

This device data sheet is based on the following

individual chapters of the “dsPIC33/PIC24 Family Reference Manual”. These documents should be

considered as the primary reference for the operation

of a particular module or device feature.

Note:

To access the documents listed below,

browse to the documentation section

of the dsPIC33FJ16GS504 product

page of the Microchip web site

(www.microchip.com).

In addition to parameters, features, and

other documentation, the resulting page

provides links to the related family

reference manual sections.

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

“Introduction” (DS70197)

“CPU” (DS70204)

“Data Memory” (DS70202)

“Program Memory” (DS70203)

“Flash Programming” (DS70191)

“Reset” (DS70192)

“Watchdog Timer (WDT) and Power-Saving Modes” (DS70196)

“I/O Ports” (DS70193)

“Timers” (DS70205)

“Input Capture” (DS70198)

“Output Compare” (DS70005157)

“Analog-to-Digital Converter (ADC)” (DS70621)

“UART” (DS70188)

“Serial Peripheral Interface (SPI)” (DS70206)

“Inter-Integrated Circuit™ (I2C™)” (DS70000195)

“CodeGuard™ Security (DS70199)

“Programming and Diagnostics” (DS70207)

“Device Configuration” (DS70194)

“Interrupts (Part IV)” (DS70300)

“Oscillator (Part IV)” (DS70307)

“High- Speed PWM Module” (DS70000323)

“High-Speed 10-Bit ADC” (DS70000321)

“High-Speed Analog Comparator” (DS70296)

“Oscillator (Part VI)” (DS70644)

2008-2014 Microchip Technology Inc.

DS70000318G-page 15

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

NOTES:

DS70000318G-page 16

2008-2014 Microchip Technology Inc.

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

1.0

DEVICE OVERVIEW

Note 1: This data sheet summarizes the features

of the dsPIC33FJ06GS101/X02 and

dsPIC33FJ16GSX02/X04 families of

devices. It is not intended to be a comprehensive reference source. To complement

the information in this data sheet, refer to

the “dsPIC33F/PIC24H Family Reference

Manual”. Please see the Microchip web

site (www.microchip.com) for the latest

“dsPIC33F/PIC24H Family Reference

Manual” sections.

2: Some registers and associated bits

described in this section may not be

available on all devices. Refer to

Section 4.0 “Memory Organization” in

this data sheet for device-specific register

and bit information.

2008-2014 Microchip Technology Inc.

This document contains device-specific information for

the following dsPIC33F Digital Signal Controller (DSC)

devices:

•

•

•

•

•

•

•

dsPIC33FJ06GS101

dsPIC33FJ06GS102

dsPIC33FJ06GS202

dsPIC33FJ16GS402

dsPIC33FJ16GS404

dsPIC33FJ16GS502

dsPIC33FJ16GS504

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/

X04 devices contain extensive Digital Signal Processor

(DSP) functionality with a high-performance, 16-bit

microcontroller (MCU) architecture.

Figure 1-1 shows a general block diagram of the core and

peripheral modules in the dsPIC33FJ06GS101/X02 and

dsPIC33FJ16GSX02/X04 devices. Table 1-1 lists the

functions of the various pins shown in the pinout diagrams.

DS70000318G-page 17

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

FIGURE 1-1:

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 BLOCK DIAGRAM

PSV & Table

Data Access

Control Block

Y Data Bus

X Data Bus

Interrupt

Controller

16

8

PORTA

16

16

16

Data Latch

Data Latch

X RAM

Y RAM

Address

Latch

Address

Latch

23

23

PCU PCH PCL

Program Counter

Loop

Stack

Control

Control

Logic

Logic

PORTB

16

23

16

16

PORTC

Address Generator Units

Address Latch

Program Memory

EA MUX

Data Latch

ROM Latch

24

Instruction Reg

Control Signals

to Various Blocks

Timing

OSC2/CLKO

OSC1/CLKI Generation

FRC/LPRC

Oscillators

Literal Data

16

Instruction

Decode &

Control

Voltage

Regulator

VCAP

16

16

DSP Engine

Power-up

Timer

Divide Support

16 x 16

W Register Array

16

Oscillator

Start-up Timer

Power-on

Reset

16-Bit ALU

Watchdog

Timer

Note:

Remappable

Pins

16

Brown-out

Reset

VDD, VSS

MCLR

Timers

1-3

UART1

ADC1

OC1

OC2

PWM

4x2

Analog

Comparators 1-4

IC1

IC2

CNx

I2C1

SPI1

Not all pins or features are implemented on all device pinout configurations. See pinout diagrams for the specific pins and

features present on each device.

DS70000318G-page 18

2008-2014 Microchip Technology Inc.

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

TABLE 1-1:

Pin Name

PINOUT I/O DESCRIPTIONS

Pin

Type

Buffer

Type

PPS

Capable

Description

AN0-AN11

I

Analog

No

Analog input channels

CLKI

I

ST/CMOS

No

CLKO

O

—

No

External clock source input. Always associated with OSC1 pin

function.

Oscillator crystal output. Connects to crystal or resonator in Crystal

Oscillator mode. Optionally functions as CLKO in RC and EC

modes. Always associated with OSC2 pin function.

OSC1

I

ST/CMOS

No

OSC2

I/O

—

No

I

ST

No

CN0-CN29

Oscillator crystal input. ST buffer when configured in RC mode;

CMOS otherwise.

Oscillator crystal output. Connects to crystal or resonator in Crystal

Oscillator mode. Optionally functions as CLKO in RC and EC

modes.

Change Notification inputs. Can be software programmed for

internal weak pull-ups on all inputs.

IC1-IC2

I

ST

Yes

Capture Inputs 1/2.

OCFA

OC1-OC2

I

O

ST

—

Yes

Yes

Compare Fault A input (for Compare Channels 1 and 2)

Compare Outputs 1 through 2.

INT0

INT1

INT2

I

I

I

ST

ST

ST

No

Yes

Yes

External Interrupt 0.

External Interrupt 1.

External Interrupt 2.

RA0-RA4

I/O

ST

No

PORTA is a bidirectional I/O port.

RB0-RB15

I/O

ST

No

PORTB is a bidirectional I/O port.

RC0-RC13

I/O

ST

No

PORTC is a bidirectional I/O port.

RP0-RP29

I/O

ST

No

Remappable I/O pins.

T1CK

T2CK

T3CK

I

I

I

ST

ST

ST

Yes

Yes

Yes

Timer1 external clock input.

Timer2 external clock input.

Timer3 external clock input.

U1CTS

U1RTS

U1RX

U1TX

I

O

I

O

ST

—

ST

—

Yes

Yes

Yes

Yes

UART1 Clear-To-Send.

UART1 Ready-To-Send.

UART1 receive.

UART1 transmit.

SCK1

SDI1

SDO1

SS1

I/O

I

O

I/O

ST

ST

—

ST

Yes

Yes

Yes

Yes

Synchronous serial clock input/output for SPI1.

SPI1 data in.

SPI1 data out.

SPI1 slave synchronization or frame pulse I/O.

SCL1

SDA1

I/O

I/O

ST

ST

No

No

Synchronous serial clock input/output for I2C1.

Synchronous serial data input/output for I2C1.

TMS

TCK

TDI

TDO

I

I

I

O

TTL

TTL

TTL

—

No

No

No

No

JTAG Test mode select pin.

JTAG test clock input pin.

JTAG test data input pin.

JTAG test data output pin.

Legend: CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

TTL = Transistor-Transistor Logic

2008-2014 Microchip Technology Inc.

Analog = Analog input

P = Power

PPS = Peripheral Pin Select

I = Input

O = Output

DS70000318G-page 19

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

TABLE 1-1:

Pin Name

PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin

Type

Buffer

Type

PPS

Capable

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

Analog

Analog

Analog

Analog

Analog

Analog

Analog

Analog

Analog

Analog

Analog

Analog

Analog

Analog

Analog

Analog

No

No

No

No

No

No

No

No

No

No

No

No

No

No

No

No

CMP1A

CMP1B

CMP1C

CMP1D

CMP2A

CMP2B

CMP2C

CMP2D

CMP3A

CMP3B

CMP3C

CMP3D

CMP4A

CMP4B

CMP4C

CMP4D

Description

Comparator 1 Channel A.

Comparator 1 Channel B.

Comparator 1 Channel C.

Comparator 1 Channel D.

Comparator 2 Channel A.

Comparator 2 Channel B.

Comparator 2 Channel C.

Comparator 2 Channel D.

Comparator 3 Channel A.

Comparator 3 Channel B.

Comparator 3 Channel C.

Comparator 3 Channel D.

Comparator 4 Channel A.

Comparator 4 Channel B.

Comparator 4 Channel C.

Comparator 4 Channel D.

DACOUT

O

—

No

DAC output voltage.

ACMP1-ACMP4

O

—

Yes

DAC trigger to PWM module.

EXTREF

I

Analog

No

External voltage reference input for the reference DACs.

REFCLKO

O

—

Yes

REFCLKO output signal is a postscaled derivative of the system

clock.

FLT1-FLT8

SYNCI1-SYNCI2

SYNCO1

PWM1L

PWM1H

PWM2L

PWM2H

PWM3L

PWM3H

PWM4L

PWM4H

I

I

O

O

O

O

O

O

O

O

O

ST

ST

—

—

—

—

—

—

—

—

—

Yes

Yes

Yes

No

No

No

No

No

No

Yes

Yes

Fault Inputs to PWM module.

External synchronization signal to PWM master time base.

PWM master time base for external device synchronization.

PWM1 low output.

PWM1 high output.

PWM2 low output.

PWM2 high output.

PWM3 low output.

PWM3 high output.

PWM4 low output.

PWM4 high output.

PGED1

PGEC1

I/O

I

ST

ST

No

No

PGED2

PGEC2

I/O

I

ST

ST

No

No

PGED3

PGEC3

I/O

I

ST

ST

No

No

Data I/O pin for programming/debugging Communication Channel 1.

Clock input pin for programming/debugging Communication

Channel 1.

Data I/O pin for programming/debugging Communication Channel 2.

Clock input pin for programming/debugging Communication

Channel 2.

Data I/O pin for programming/debugging Communication Channel 3.

Clock input pin for programming/debugging Communication

Channel 3.

MCLR

I/P

ST

No

Master Clear (Reset) input. This pin is an active-low Reset to the

device.

AVDD

P

P

No

Positive supply for analog modules. This pin must be connected at

all times. AVDD is connected to VDD.

AVSS

P

P

No

Ground reference for analog modules. AVSS is connected to VSS.

VDD

P

—

No

Positive supply for peripheral logic and I/O pins.

VCAP

P

—

No

CPU logic filter capacitor connection.

VSS

P

—

No

Ground reference for logic and I/O pins.

Legend: CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

TTL = Transistor-Transistor Logic

DS70000318G-page 20

Analog = Analog input

P = Power

PPS = Peripheral Pin Select

I = Input

O = Output

2008-2014 Microchip Technology Inc.

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

2.0

GUIDELINES FOR GETTING

STARTED WITH 16-BIT

DIGITAL SIGNAL

CONTROLLERS

Note 1: This data sheet summarizes the features

of the dsPIC33FJ06GS101/X02 and

dsPIC33FJ16GSX02/X04

family

of

devices. It is not intended to be a

comprehensive reference source. To

complement the information in this data

sheet, refer to the “dsPIC33F/PIC24H

Family Reference Manual”, which is

available from the Microchip web site

(www.microchip.com).

2: Some registers and associated bits

described in this section may not be

available on all devices. Refer to

Section 4.0 “Memory Organization” in

this data sheet for device-specific register

and bit information.

2.1

Basic Connection Requirements

Getting started with the dsPIC33FJ06GS101/X02 and

dsPIC33FJ16GSX02/X04 family of 16-bit Digital Signal

Controllers (DSC) requires attention to a minimal set of

device pin connections before proceeding with

development. The following is a list of pin names, which

must always be connected:

• All VDD and VSS pins

(see Section 2.2 “Decoupling Capacitors”)

• All AVDD and AVSS pins (regardless if ADC module

is not used)

(see Section 2.2 “Decoupling Capacitors”)

• VCAP

(see Section 2.3 “Capacitor on Internal Voltage

Regulator (VCAP)”)

• MCLR pin

(see Section 2.4 “Master Clear (MCLR) Pin”)

• PGECx/PGEDx pins used for In-Circuit Serial

Programming™ (ICSP™) and debugging purposes

(see Section 2.5 “ICSP™ Pins”)

• OSC1 and OSC2 pins when external oscillator

source is used

(see Section 2.6 “External Oscillator Pins”)

2008-2014 Microchip Technology Inc.

2.2

Decoupling Capacitors

The use of decoupling capacitors on every pair of

power supply pins, such as VDD, VSS, AVDD and

AVSS is required.

Consider the following criteria when using decoupling

capacitors:

• Value and type of capacitor: Recommendation

of 0.1 µF (100 nF), 10-20V. This capacitor should

be a low-ESR and have resonance frequency in

the range of 20 MHz and higher. It is

recommended that ceramic capacitors be used.

• Placement on the printed circuit board: The

decoupling capacitors should be placed as close

to the pins as possible. It is recommended to

place the capacitors on the same side of the

board as the device. If space is constricted, the

capacitor can be placed on another layer on the

PCB using a via; however, ensure that the trace

length from the pin to the capacitor is within

one-quarter inch (6 mm) in length.

• Handling high frequency noise: If the board is

experiencing high frequency noise, upward of

tens of MHz, add a second ceramic-type capacitor

in parallel to the above described decoupling

capacitor. The value of the second capacitor can

be in the range of 0.01 µF to 0.001 µF. Place this

second capacitor next to the primary decoupling

capacitor. In high-speed circuit designs, consider

implementing a decade pair of capacitances as

close to the power and ground pins as possible.

For example, 0.1 µF in parallel with 0.001 µF.

• Maximizing performance: On the board layout

from the power supply circuit, run the power and

return traces to the decoupling capacitors first,

and then to the device pins. This ensures that the

decoupling capacitors are first in the power chain.

Equally important is to keep the trace length

between the capacitor and the power pins to a

minimum thereby reducing PCB track inductance.

DS70000318G-page 21

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

FIGURE 2-1:

RECOMMENDED

MINIMUM CONNECTION

0.1 µF

Ceramic

10 µF

Tantalum

R1

VDD

R

VSS

2.4

VCAP

VDD

dsPIC33F

VSS

VDD

VSS

VDD

AVSS

VDD

AVDD

VSS

0.1 µF

Ceramic

0.1 µF

Ceramic

0.1 µF

Ceramic

L1(1)

1:

As an option, instead of a hard-wired connection, an

inductor (L1) can be substituted between VDD and

AVDD to improve ADC noise rejection. The inductor

impedance should be less than 1 and the inductor

capacity greater than 10 mA.

Where:

F CNVf = ------------(i.e., ADC conversion rate/2)

2

1

f = ---------------------- 2 LC

1

L = ----------------------

2f C

pin

provides

two

specific

device

• Device Reset

• Device programming and debugging.

C

Note

Master Clear (MCLR) Pin

The MCLR

functions:

MCLR

0.1 µF

Ceramic

The placement of this capacitor should be close to the

VCAP. It is recommended that the trace length not

exceed one-quarter inch (6 mm). Refer to Section 21.2

“On-Chip Voltage Regulator” for details.

During device programming and debugging, the

resistance and capacitance that can be added to the

pin must be considered. Device programmers and

debuggers drive the MCLR pin. Consequently,

specific voltage levels (VIH and VIL) and fast signal

transitions must not be adversely affected. Therefore,

specific values of R and C will need to be adjusted

based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is

recommended that the capacitor C, be isolated from

the MCLR pin during programming and debugging

operations.

Place the components shown in Figure 2-2 within

one-quarter inch (6 mm) from the MCLR pin.

FIGURE 2-2:

EXAMPLE OF MCLR PIN

CONNECTIONS

VDD

2

R

R1

MCLR

2.2.1

TANK CAPACITORS

On boards with power traces running longer than six

inches in length, it is suggested to use a tank capacitor

for integrated circuits including DSCs to supply a local

power source. The value of the tank capacitor should

be determined based on the trace resistance that connects the power supply source to the device, and the

maximum current drawn by the device in the application. In other words, select the tank capacitor so that it

meets the acceptable voltage sag at the device. Typical

values range from 4.7 µF to 47 µF.

2.3

Capacitor on Internal Voltage

Regulator (VCAP)

JP

dsPIC33F

C

Note 1:

R 10 k is recommended. A suggested

starting value is 10 k. Ensure that the MCLR

pin VIH and VIL specifications are met.

2:

R1 470 will limit any current flowing into

MCLR from the external capacitor, C, in the

event of MCLR pin breakdown, due to

Electrostatic Discharge (ESD) or Electrical

Overstress (EOS). Ensure that the MCLR pin

VIH and VIL specifications are met.

A low-ESR ( 5.5V.

Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical “absolute instantaneous” sum of the input injection currents from all pins do not

exceed the specified limit. Characterized but not tested.

2008-2014 Microchip Technology Inc.

DS70000318G-page 295

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

TABLE 24-9:

DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

Standard Operating Conditions: 3.0V to 3.6V

(unless otherwise stated)

Operating temperature -40°C TA +85°C for Industrial

-40°C TA +125°C for Extended

DC CHARACTERISTICS

Param

Symbol

No.

IICL

Characteristic

IICT

3:

4:

5:

6:

7:

8:

9:

Units

Conditions

0

—

-5(5,8)

mA

All pins except VDD, VSS,

AVDD, AVSS, MCLR,

VCAP and RB5

0

—

+5(6,7,8)

mA

All pins except VDD, VSS,

AVDD, AVSS, MCLR,

VCAP, RB5 and digital

5V-tolerant designated

pins

-20(9)

—

+20(9)

mA

Absolute instantaneous

sum of all ± input

injection currents from

all I/O pins

( | IICL + | IICH | ) IICT

Total Input Injection Current

(sum of all I/O and control pins)

Note 1:

2:

Max

Input High Injection Current

DI60b

DI60c

Typ(1)

Input Low Injection Current

DI60a

IICH

Min

Data in “Typ” column is at 3.3V, +25°C unless otherwise stated.

The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified

levels represent normal operating conditions. Higher leakage current may be measured at different input

voltages.

Negative current is defined as current sourced by the pin.

See “Pin Diagrams” for the list of 5V tolerant I/O pins.

VIL source < (VSS – 0.3). Characterized but not tested.

Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not

tested.

Digital 5V tolerant pins cannot tolerate any “positive” input injection current from input sources > 5.5V.

Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical “absolute instantaneous” sum of the input injection currents from all pins do not

exceed the specified limit. Characterized but not tested.

DS70000318G-page 296

2008-2014 Microchip Technology Inc.

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

TABLE 24-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Standard Operating Conditions: 3.0V to 3.6V

(unless otherwise stated)

Operating temperature -40°C TA +85°C for Industrial

-40°C TA +125°C for Extended

DC CHARACTERISTICS

Param. Symbol

DO10

DO20

VOL

VOH

Characteristic

Min.

Typ.

Max.

Units

Output Low Voltage

I/O Pins:

4x Sink Driver Pins – RA0-RA2,

RB0-RB2, RB5-RB10, RB15,

RC1, RC2, RC9, RC10

—

—

0.4

V

IOL 6 mA, VDD = 3.3V

See Note 1

Output Low Voltage

I/O Pins:

8x Sink Driver Pins – RC0,

RC3-RC8, RC11-RC13

—

—

0.4

V

IOL 10 mA, VDD = 3.3V

See Note 1

Output Low Voltage

I/O Pins:

16x Sink Driver Pins – RA3,

RA4, RB3, RB4, RB11-RB14

—

—

0.4

V

IOL 18 mA, VDD = 3.3V

See Note 1

Output High Voltage

I/O Pins:

4x Source Driver Pins –

RA0-RA2, RB0-RB2, RB5RB10, RB15, RC1, RC2, RC9,

RC10

2.4

—

—

V

IOH -6 mA, VDD = 3.3V

See Note 1

Output High Voltage

I/O Pins:

8x Source Driver Pins – RC0,

RC3-RC8, RC11-RC13

2.4

—

—

V

IOH -10 mA, VDD = 3.3V

See Note 1

Output High Voltage

I/O Pins:

16x Source Driver Pins – RA3,

RA4, RB3, RB4, RB11-RB14

2.4

—

—

V

IOH -18 mA, VDD = 3.3V

See Note 1

1.5

—

—

2.0

—

—

3.0

—

—

IOH -3 mA, VDD = 3.3V

See Note 1

1.5

—

—

IOH -16 mA, VDD = 3.3V

See Note 1

2.0

—

—

3.0

—

—

IOH -4 mA, VDD = 3.3V

See Note 1

1.5

—

—

IOH -30 mA, VDD = 3.3V

See Note 1

2.0

—

—

3.0

—

—

Output High Voltage

I/O Pins:

4x Source Driver Pins –

RA0-RA2, RB0-RB2,

RB5-RB10, RB15, RC1, RC2,

RC9, RC10

Output High Voltage

8x Source Driver Pins – RC0,

RC3-RC8, RC11-RC13

DO20A VOH1

Output High Voltage

I/O Pins:

16x Source Driver Pins – RA3,

RA4, RB3, RB4, RB11-RB14

Note 1:

Conditions

IOH -12 mA, VDD = 3.3V

See Note 1

V

V

V

IOH -11 mA, VDD = 3.3V

See Note 1

IOH -12 mA, VDD = 3.3V

See Note 1

IOH -25 mA, VDD = 3.3V

See Note 1

IOH -8 mA, VDD = 3.3V

See Note 1

Parameters are characterized, but not tested.

2008-2014 Microchip Technology Inc.

DS70000318G-page 297

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

TABLE 24-11: ELECTRICAL CHARACTERISTICS: BOR

DC CHARACTERISTICS

Param

No.

Symbol

Standard Operating Conditions (see Note 3): 3.0V to 3.6V

(unless otherwise stated)

Operating temperature -40°C TA +85°C for Industrial

-40°C TA +125°C for Extended

Characteristic

Min(1)

Typ

Max

Units

2.55

—

2.79

V

Conditions

See Note 2

BO10

VBOR

Note 1:

2:

3:

Parameters are for design guidance only and are not tested in manufacturing.

The device will operate as normal until the VDDMIN threshold is reached.

Overall functional device operation at VBORMIN < VDD < VDDMIN is tested but not characterized. All device

analog modules such as the ADC, etc., will function but with degraded performance below VDDMIN.

DS70000318G-page 298

BOR Event on VDD Transition

High-to-Low

BOR Event is Tied to VDD Core

Voltage Decrease

2008-2014 Microchip Technology Inc.

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

TABLE 24-12: DC CHARACTERISTICS: PROGRAM MEMORY

Standard Operating Conditions: 3.0V to 3.6V

(unless otherwise stated)

Operating temperature -40°C TA +85°C for Industrial

-40°C TA +125°C for Extended

DC CHARACTERISTICS

Param

Symbol

No.

Characteristic

Min

Typ(1)

Max

Units

Conditions

Program Flash Memory

D130

EP

Cell Endurance

10,000

—

—

D131

VPR

VDD for Read

VMIN

—

3.6

V

VMIN = Minimum operating

voltage

D132B

VPEW

VDD for Self-Timed Write

VMIN

—

3.6

V

VMIN = Minimum operating

voltage

D134

TRETD

Characteristic Retention

20

—

—

Year Provided no other specifications

are violated, -40C to +125C

D135

IDDP

Supply Current during

Programming

—

10

—

mA

D136a

TRW

Row Write Time

1.477

—

1.538

ms

TRW = 11064 FRC cycles,

TA = +85°C, See Note 2

D136b

TRW

Row Write Time

1.435

—

1.586

ms

TRW = 11064 FRC cycles,

TA = +125°C, See Note 2

D137a

TPE

Page Erase Time

22.5

—

23.4

ms

TPE = 168517 FRC cycles,

TA = +85°C, See Note 2

D137b

TPE

Page Erase Time

21.9

—

24.2

ms

TPE = 168517 FRC cycles,

TA = +125°C, See Note 2

D138a

TWW

Word Write Cycle Time

47.4

—

49.3

µs

TWW = 355 FRC cycles,

TA = +85°C, See Note 2

D138b

TWW

Word Write Cycle Time

46

—

50.9

µs

TWW = 355 FRC cycles,

TA = +125°C, See Note 2

Note 1:

2:

E/W -40C to +125C

Data in “Typ” column is at 3.3V, +25°C unless otherwise stated.

Other conditions: FRC = 7.37 MHz, TUN = b'011111 (for Min), TUN = b'100000 (for Max).

This parameter depends on the FRC accuracy (see Table 24-20) and the value of the FRC Oscillator Tuning register (see Register 9-4). For complete details on calculating the Minimum and Maximum time see

Section 5.3 “Programming Operations”.

TABLE 24-13: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

Operating Conditions:

Param

No.

—

Note 1:

Symbol

CEFC

-40°C TA +85°C for Industrial

-40°C TA +125°C for Extended

Characteristics

External Filter Capacitor

Value(1)

Min

Typ

Max

Units

4.7

10

—

F

Comments

Capacitor must be low

series resistance

(< 5 ohms)

Typical VCAP voltage = 2.5 volts when VDD VDDMIN.

2008-2014 Microchip Technology Inc.

DS70000318G-page 299

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

24.2

AC Characteristics and Timing Parameters

This section defines dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 AC characteristics and timing parameters.

TABLE 24-14: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

Standard Operating Conditions: 3.0V to 3.6V

(unless otherwise stated)

Operating temperature -40°C TA +85°C for Industrial

-40°C TA +125°C for Extended

Operating voltage VDD range as described in Table 24-1.

AC CHARACTERISTICS

FIGURE 24-1:

LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

Load Condition 1 – for all pins except OSC2

Load Condition 2 – for OSC2

VDD/2

CL

Pin

RL

VSS

CL

Pin

RL = 464

CL = 50 pF for all pins except OSC2

15 pF for OSC2 output

VSS

TABLE 24-15: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

Param

Symbol

No.

Characteristic

Min

Typ

Max

Units

Conditions

DO50

COSCO

OSC2 Pin

—

—

15

pF

In XT and HS modes when external

clock is used to drive OSC1

DO56

CIO

All I/O Pins and OSC2

—

—

50

pF

EC mode

DO58

CB

SCLx, SDAx

—

—

400

pF

In I2C™ mode

DS70000318G-page 300

2008-2014 Microchip Technology Inc.

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

FIGURE 24-2:

EXTERNAL CLOCK TIMING

Q1

Q2

Q3

Q4

Q1

Q2

OS30

OS30

Q3

Q4

OSC1

OS20

OS31

OS31

OS25

CLKO

OS41

OS40

TABLE 24-16: EXTERNAL CLOCK TIMING REQUIREMENTS

Standard Operating Conditions: 3.0V to 3.6V

(unless otherwise stated)

Operating temperature -40°C TA +85°C for Industrial

-40°C TA +125°C for Extended

AC CHARACTERISTICS

Param

No.

OS10

Symb

FIN

Min

Typ(1)

Max

Units

External CLKI Frequency

(External clocks allowed only

in EC and ECPLL modes)

DC

—

40

MHz

EC

Oscillator Crystal Frequency

3.5

10

—

—

10

40

MHz

MHz

XT

HS

Characteristic

Conditions

OS20

TOSC

TOSC = 1/FOSC

12.5

—

DC

ns

OS25

TCY

Instruction Cycle Time(2)

25

—

DC

ns

OS30

TosL,

TosH

External Clock in (OSC1)

High or Low Time

0.375 x TOSC

—

0.625 x TOSC

ns

EC

OS31

TosR,

TosF

External Clock in (OSC1)

Rise or Fall Time

—

—

20

ns

EC

OS40

TckR

CLKO Rise Time(3)

—

5.2

—

ns

—

5.2

—

ns

14

16

18

mA/V

Time(3)

OS41

TckF

CLKO Fall

OS42

GM

External Oscillator

Transconductance(4)

Note 1:

2:

3:

4:

VDD = 3.3V,

TA = +25ºC

Data in “Typ” column is at 3.3V, +25°C unless otherwise stated.

Instruction cycle period (TCY) equals two times the input oscillator time-base period. All specified values

are based on characterization data for that particular oscillator type under standard operating conditions

with the device executing code. Exceeding these specified limits may result in an unstable oscillator

operation and/or higher than expected current consumption. All devices are tested to operate at “min.”

values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the

“max.” cycle time limit is “DC” (no clock) for all devices.

Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

Data for this parameter is Preliminary. This parameter is characterized, but not tested in manufacturing.

2008-2014 Microchip Technology Inc.

DS70000318G-page 301

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

TABLE 24-17: PLL CLOCK TIMING SPECIFICATIONS (VDD = 3.0V TO 3.6V)

AC CHARACTERISTICS

Param

No.

Symbol

Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)

Operating temperature -40°C TA +85°C for Industrial

-40°C TA +125°C for Extended

Characteristic

Min

Typ(1)

Max

Units

OS50

FPLLI

PLL Voltage Controlled

Oscillator (VCO) Input

Frequency Range

0.8

—

8

MHz

OS51

FSYS

On-Chip VCO System

Frequency

100

—

200

MHz

OS52

TLOCK

PLL Start-up Time (Lock Time)

0.9

1.5

3.1

mS

OS53

DCLK

CLKO Stability (Jitter)(2)

-3

0.5

3

%

Note 1:

2:

Conditions

ECPLL, XTPLL modes

Measured over 100 ms

period

Data in “Typ” column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only

and are not tested in manufacturing.

These parameters are characterized by similarity, but are not tested in manufacturing. This specification is

based on clock cycle by clock cycle measurements. To calculate the effective jitter for individual time bases

or communication clocks use this formula:

D CLK

Peripheral Clock Jitter = -----------------------------------------------------------------------F OSC

-------------------------------------------------------------

Peripheral Bit Rate Clock

For example: FOSC = 32 MHz, DCLK = 3%, SPI bit rate clock (i.e., SCKx) is 2 MHz.

D CLK

3%

3%

SPI SCK Jitter = ------------------------------ = ---------- = -------- = 0.75%

4

16

MHz

32

--------------------

2 MHz

TABLE 24-18: AUXILIARY PLL CLOCK TIMING SPECIFICATIONS (VDD = 3.0V TO 3.6V)

AC CHARACTERISTICS

Param

No.

Symbol

Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)

Operating temperature -40°C TA +85°C for Industrial

-40°C TA +125°C for Extended

Characteristic

Min

Typ(1)

Max

Units

OS56

FHPOUT

On-Chip 16x PLL CCO

Frequency

112

118

120

MHz

OS57

FHPIN

On-Chip 16x PLL Phase

Detector Input Frequency

7.0

7.37

7.5

MHz

OS58

TSU

Frequency Generator Lock

Time

—

—

10

µs

Note 1:

Conditions

Data in “Typ” column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only

and are not tested in manufacturing.

DS70000318G-page 302

2008-2014 Microchip Technology Inc.

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

TABLE 24-19: AC CHARACTERISTICS: INTERNAL FRC ACCURACY

AC CHARACTERISTICS

Param

No.

Characteristic

Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)

Operating temperature

-40°C TA +85°C for industrial

-40°C TA +125°C for Extended

Min

Typ

Max

Units

Conditions

Internal FRC Accuracy @ FRC Frequency = 7.37 MHz(1)

F20a

FRC

-2

—

+2

%

-40°C TA +85°C

VDD = 3.0-3.6V

F20b

FRC

-5

—

+5

%

-40°C TA +125°C

VDD = 3.0-3.6V

Note 1:

Frequency calibrated at +25°C and 3.3V. TUNx bits can be used to compensate for temperature drift.

TABLE 24-20: AC CHARACTERISTICS: INTERNAL LPRC ACCURACY

AC CHARACTERISTICS

Param

No.

Characteristic

Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)

Operating temperature -40°C TA +85°C for Industrial

-40°C TA +125°C for Extended

Min

Typ

Max

Units

Conditions

LPRC @ 32.768 kHz(1)

F21a

LPRC

-20

±6

+20

%

-40°C TA +85°C

VDD = 3.0-3.6V

F21b

LPRC

-70

—

+70

%

-40°C TA +125°C

VDD = 3.0-3.6V

Note 1:

Change of LPRC frequency as VDD changes.

2008-2014 Microchip Technology Inc.

DS70000318G-page 303

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

FIGURE 24-3:

I/O TIMING CHARACTERISTICS

I/O Pin

(Input)

DI35

DI40

I/O Pin

(Output)

New Value

Old Value

DO31

DO32

Note: Refer to Figure 24-1 for load conditions.

TABLE 24-21: I/O TIMING REQUIREMENTS

AC CHARACTERISTICS

Param

No.

Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)

Operating temperature -40°C TA +85°C for Industrial

-40°C TA +125°C for Extended

Min

Typ(1)

Max

Units

4x Source Driver Pins – RA0-RA2,

RB0-RB2, RB5-RB10, RB15, RC1,

RC2, RC9, RC10

—

10

25

ns

8x Source Driver Pins – RC0,

RC3-RC8, RC11-RC13

—

8

20

ns

16x Source Driver Pins – RA3,

RA4, RB3, RB4, RB11-RB14

—

6

15

ns

4x Source Driver Pins – RA0-RA2,

RB0-RB2, RB5-RB10, RB15, RC1,

RC2, RC9, RC10

—

10

25

ns

8x Source Driver Pins – RC0,

RC3-RC8, RC11-RC13

—

8

20

ns

16x Source Driver Pins – RA3,

RA4, RB3, RB4, RB11-RB14

—

6

15

ns

TINP

INTx Pin High or Low Time (input)

20

—

—

ns

DI40

TRBP

CNx High or Low Time (input)

2

—

—

TCY

Note 1:

Data in “Typ” column is at 3.3V, +25°C unless otherwise stated.

DO31

DO32

DI35

Symbol

TIOR

TIOF

DS70000318G-page 304

Characteristic

Conditions

Port Output Rise Time:

Refer to Figure 24-1

for test conditions

Port Output Fall Time:

Refer to Figure 24-1

for test conditions

2008-2014 Microchip Technology Inc.

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

FIGURE 24-4:

VDD

RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP

TIMER TIMING CHARACTERISTICS

SY12

MCLR

SY10

Internal

POR

SY11

PWRT

Time-out

OSC

Time-out

SY30

Internal

Reset

Watchdog

Timer

Reset

SY13

SY20

SY13

I/O Pins

FSCM

Delay

SY35

Note: Refer to Figure 24-1 for load conditions.

2008-2014 Microchip Technology Inc.

DS70000318G-page 305

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

TABLE 24-22: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER

TIMING REQUIREMENTS

Standard Operating Conditions: 3.0V to 3.6V

(unless otherwise stated)

Operating temperature -40°C TA +85°C for Industrial

-40°C TA +125°C for Extended

AC CHARACTERISTICS

Param

Symbol

No.

Characteristic(1)

Min

Typ(2)

Max

Units

Conditions

SY10

TMCL

MCLR Pulse Width (low)

2

—

—

s

-40°C to +85°C

SY11

TPWRT

Power-up Timer Period

—

2

4

8

16

32

64

128

—

ms

-40°C to +85°C,

User programmable

SY12

TPOR

Power-on Reset Delay

3

10

30

s

-40°C to +85°C

SY13

TIOZ

I/O High-Impedance from MCLR

Low or Watchdog Timer Reset

0.68

0.72

1.2

s

SY20

TWDT1

Watchdog Timer Time-out Period

—

—

—

ms

See Section 21.4 “Watchdog Timer (WDT)” and

LPRC Parameter F21a

(Table 24-20)

SY30

TOST

Oscillator Start-up Time

—

1024 TOSC

—

—

TOSC = OSC1 period

Note 1:

2:

These parameters are characterized but not tested in manufacturing.

Data in “Typ” column is at 3.3V, +25°C unless otherwise stated.

DS70000318G-page 306

2008-2014 Microchip Technology Inc.

�dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

FIGURE 24-5:

TIMER1, 2 AND 3 EXTERNAL CLOCK TIMING CHARACTERISTICS

TxCK

Tx11

Tx10

Tx15

OS60

Tx20

TMRx

Note: Refer to Figure 24-1 for load conditions.

TABLE 24-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS(1)