物料型号:文档中没有明确列出特定的物料型号,但提到了Microsemi公司的IGLOO2 FPGA和SmartFusion2 SoC FPGA产品。

器件简介:文档是Microsemi公司关于IGLOO2 FPGA和SmartFusion2 SoC FPGA的数据手册,涵盖了这些FPGA的详细电气特性和操作条件。

引脚分配:文档中包含了关于FPGA的引脚分配信息,但没有提供具体的图表或详细分配图。

参数特性:文档详细列出了各种电气参数的特性,如电源电压、输入/输出电压规格、时钟频率、数据速率等。

功能详解:文档提供了关于FPGA功能的详细解释,包括不同的输入/输出标准(如LVDS、B-LVDS、M-LVDS、Mini-LVDS、RSDS、LVPECL等),以及它们的DC和AC特性。

应用信息:文档中没有直接提供应用信息,但通过详细描述的电气特性和功能,可以推断这些FPGA适用于高速数据通信和复杂的数字信号处理应用。

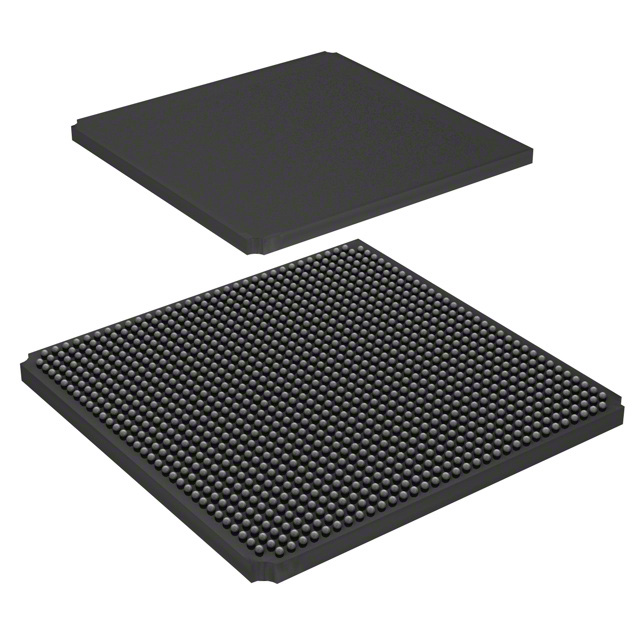

封装信息:文档中没有提供封装信息,但通常这类信息可以在产品的具体数据手册或技术规格书中找到。