MCP2021A/2A

LIN Transceiver with Voltage Regulator

Features:

Description:

• The MCP2021A/2A are compliant with LIN Bus

Specifications Version 1.3, 2.1 and with SAE

J2602-2

• Support Baud Rates up to 20 kBaud

• 43V Load Dump Protected

• Maximum Continuous Input Voltage: 30V

• Wide LIN-Compliant Supply Voltage: 6.0 – 18.0V

• Extended Temperature Range: -40 to +125°C

• Interface to PIC® MCU EUSART and Standard

USARTs

• Wake-Up on LIN Bus Activity or Local Wake Input

• Local Interconnect Network (LIN) Bus Pin:

- Internal Pull-Up Termination Resistor and

Diode for Slave Node

- Protected Against VBAT Shorts

- Protected Against Loss of Ground

- High-Current Drive

• TXD and LIN Bus Dominant Time-Out Function

• Two Low-Power Modes:

- Transmitter Off: 90 µA (typical)

- Power Down: 4.5 µA (typical)

• Output Indicating Internal Reset State (POR or

Sleep Wake)

• MCP2021A/2A On-Chip Voltage Regulator:

- Output Voltage of 5.0V or 3.3V

at 70 mA Capability with Tolerances of ±3%

Over the Temperature Range

- Internal Short Circuit Current Limit

- External Components Limited to Filter

Capacitor and Load Capacitor

• Automatic Thermal Shutdown

• High Electromagnetic Immunity (EMI), Low

Electromagnetic Emission (EME)

• Robust ESD Performance: ±15 kV for LBUS and

VBB pin (IEC61000-4-2)

• Transient Protection for LBUS and VBB Pins in

Automotive Environment (ISO7637)

• Meets Stringent Automotive Design

Requirements, including “OEM Hardware

Requirements for LIN, CAN and FlexRay

Interfaces in Automotive Applications”, Version

1.2, March 2011

• Multiple Package Options, including Small

4x4 mm DFN Package

The MCP2021A/2A provide a bidirectional, half-duplex

communication physical interface to meet the LIN bus

specification Revision 2.1 and SAE J2602-2. The

devices incorporate a voltage regulator with 5V or 3.3V

at 70 mA regulated power supply output. The devices

have been designed to meet the stringent quiescent

current requirements of the automotive industry and

will survive +43V load dump transients and double

battery jumps.

2012-2014 Microchip Technology Inc.

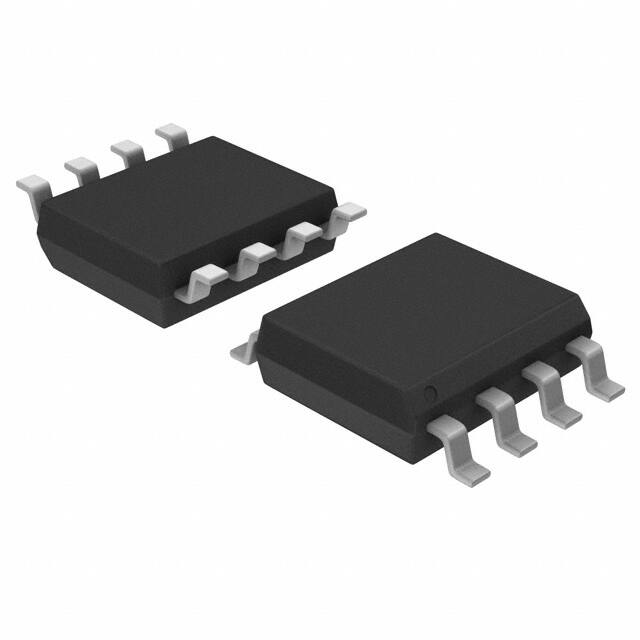

Package Types

MCP2021A

PDIP, SOIC

RXD

CS/LWAKE

VREG

TXD

1

2

3

4

FAULT/TXE

VBB

LBUS

VSS

8

7

6

5

MCP2021A

4x4 DFN

RXD 1

CS/LWAKE 2

VREG 3

TXD 4

EP

9

8 FAULT/TXE

7 VBB

6 LBUS

5 VSS

MCP2022A

PDIP, SOIC, TSSOP

RXD

CS/LWAKE

VREG

TXD

RESET

NC

NC

1

2

3

4

5

6

7

14

13

12

11

10

9

8

FAULT/TXE

VBB

LBUS

VSS

NC

NC

NC

* Includes Exposed Thermal Pad (EP), see Table 1-2.

DS20002298C-page 1

�MCP2021A/2A

MCP2021A/2A Block Diagram

VREG

RESET

(MCP2022A only)

Thermal

Protection

Short Circuit

Protection

Voltage

Regulator

VBB

Ratiometric

Reference

VREG

Internal Circuits

VREG

4.2V

Wake-Up Logic

and

Power Control

Bus Wake-Up

RXD

~ 30 k

Slope Control

CS/LWAKE

LBUS

TXD

Bus

Dominant

Timer

FAULT/TXE

VSS

Thermal and

Short Circuit

Protection

DS20002298C-page 2

2012-2014 Microchip Technology Inc.

�MCP2021A/2A

1.0

DEVICE OVERVIEW

1.1

The MCP2021A/2A devices provide a physical

interface between a microcontroller and a LIN

half-duplex bus. They are intended for automotive and

industrial applications with serial bus baud rates up to

20 kBaud. These devices will translate the CMOS/TTL

logic levels to LIN logic levels and vice versa.

Modes of Operation

The MCP2021A/2A work in five modes: Power-On

Reset, Power-Down, Ready, Operation and

Transmitter Off. For an overview of all operational

modes, please refer to Table 1-1. For the operational

mode transition, please refer to Figure 1-1.

The MCP2021A/2A offer optimum EMI and ESD

performance and can withstand high voltage on the LIN

bus. The devices support two low-power modes to

meet automotive industry power consumption

requirements. The MCP2021A/2A also provide a +5V

or 3.3V regulated power output at 70 mA.

FIGURE 1-1:

STATE DIAGRAM

CS/LWAKE = 0

POR(2)

VREG OFF

RX OFF

TX OFF

VBB > VON

READY

VREG ON

RX ON

TX OFF

CS/LWAKE = 1 &

FAULT/TXE = 1 (3) &

TXD = 1&

VREG_OK = 1 (1)

CS/LWAKE = 1&

FAULT/TXE = 0&

CS/LWAKE = 1 OR

Voltage Rising Edge on LBUS

TX OFF

VREG ON

RX ON

TX OFF

CS/LWAKE = 1&

FAULT/TXE = 1 (3)&

TXD = 1

CS/LWAKE = 0

POWER-DOWN

VREG OFF

RX OFF

TX OFF

CS/LWAKE = 1&

FAULT/TXE = 0

OPERATION

VREG ON

RX ON

TX ON

CS/LWAKE = 0

Note 1: VREG_OK: Regulator Output Voltage > 0.8VREG_NOM.

2: If the voltage on pin VBB falls below VOFF, the device will enter Power-On Reset mode from all other

modes, which is not shown in the figure.

3: FAULT/TXE = 1 represents input high and no fault conditions. FAULT/TXE = 0 represents input low or a

fault condition. Refer to Table 1-5.

2012-2014 Microchip Technology Inc.

DS20002298C-page 3

�MCP2021A/2A

1.1.1

POWER-ON RESET MODE

Upon application of VBB or whenever the voltage on

VBB is below the threshold of regulator turn-off voltage

VOFF (typically 4.50V), the device enters Power-On

Reset (POR) mode. During this mode, the device

maintains the digital section in a Reset mode and waits

until the voltage on the VBB pin rises above the

threshold of regulator turn-on voltage VON (typically

5.75V) to enter Ready mode. In Power-On Reset

mode, the LIN physical layer and voltage regulator are

disabled and the RESET output (MCP2022A only) is

forced to low.

1.1.2

READY MODE

The device enters Ready mode from POR mode after

the voltage on VBB rises above the threshold of

regulator turn-on voltage VON or from Power-Down

mode when a remote or local wake-up event happens.

Upon entering Ready mode, the voltage regulator and

the receiver section of the transceiver are powered up.

The transmitter remains in an off state. The device is

ready to receive data but not to transmit. In order to

minimize the power consumption, the regulator

operates in a reduced-power mode. It has a lower

GBW product and it is thus slower. However, the 70 mA

drive capability is unchanged.

The device stays in Ready mode until the output of the

voltage regulator has stabilized and the CS/LWAKE pin

is high (‘1’).

1.1.3

OPERATION MODE

If VREG is OK (VREG > 0.8 VREG_NORM) and the

CS/LWAKE, FAULT/TXE and TXD pins are high, the

part enters Operation mode from either Ready or

Transmitter Off mode.

In this mode, all internal modules are operational. The

internal pull-up resistor between LBUS and VBB is

connected only in this mode.

The device goes into Power-Down mode at the falling

edge on CS/LWAKE or into Transmitter Off mode at the

falling edge on FAULT/TXE while CS/LWAKE stays

high.

DS20002298C-page 4

1.1.4

TRANSMITTER OFF MODE

In Transmitter Off mode, the receiver is enabled but the

LBUS transmitter is off. It is a lower power mode.

In order to minimize power consumption, the regulator

operates in a reduced-power mode. It has a lower

GBW product and it is thus slower. However, the 70 mA

drive capability is unchanged.

The transmitter may be re-enabled whenever the

FAULT/TXE signal returns high, by removing the

internal fault condition and by driving FAULT/TXE high.

The transmitter will not be enabled even if the

FAULT/TXE pin is brought high externally, when the

internal fault is still present. However, externally forcing

the FAULT/TXE high while the internal fault is still

present should be avoided, since this will induce high

current and power dissipation in the FAULT/TXE pin.

The transmitter is also turned off whenever the voltage

regulator is unstable or recovering from a fault. This

prevents unwanted disruption of the bus during times of

uncertain operation.

1.1.5

POWER-DOWN MODE

In Power-Down mode, the transceiver and the voltage

regulator are both off. Only the bus wake-up section

and the CS/LWAKE pin wake-up circuits are in

operation. This is the lowest power mode.

If any bus activity (e.g., a Break character) occurs

during Power-Down mode, the device will immediately

enter Ready mode and enable the voltage regulator.

Then, once the regulator output has stabilized

(approximately 0.3 ms to 1.2 ms), it goes into

Operation mode. Refer to Section 1.1.6 “Remote

Wake-Up”.

The part will also enter Ready mode from Power-Down

mode, followed by the Operation mode, if the

CS/LWAKE pin becomes active high (‘1’).

1.1.6

REMOTE WAKE-UP

The Remote Wake-Up sub-module observes the LBUS

in order to detect bus activity. In Power-Down mode,

normal LIN recessive/dominant threshold is disabled

and the LIN bus wake-up voltage threshold VWK(LBUS)

is used to detect bus activities. Bus activity is detected

when the voltage on the LBUS falls below the LIN bus

wake-up voltage threshold VWK(LBUS) (approximately

3.5V) for at least tBDB (a typical duration of 80 µs)

followed by a rising edge. Such a condition causes the

device to leave Power-Down mode.

2012-2014 Microchip Technology Inc.

�MCP2021A/2A

TABLE 1-1:

State

OVERVIEW OF OPERATIONAL MODES

Transmitter Receiver

Internal

Voltage

Wake

Regulator

Module

Operation

Comments

POR

OFF

OFF

OFF

OFF

Proceed to Ready mode after

VBB > VON

Ready

OFF

ON

OFF

ON

If CS/LWAKE is high, then proceed to Bus Off

Operation or Transmitter Off mode.

state

Operation

ON

ON

OFF

ON

If CS/LWAKE is low, then proceed to

Power-Down mode.

If FAULT/TXE is low, then proceed to

Transmitter Off mode.

Power-Down

OFF

OFF

ON

Activity

Detect

OFF

On LIN bus rising edge or CS/LWAKE Lowest

high level, go to Ready mode.

power mode

Transmitter Off

OFF

ON

OFF

ON

If CS/LWAKE is low, then proceed to

Power-Down mode.

If FAULT/TXE is high, then proceed to

Operation mode.

2012-2014 Microchip Technology Inc.

Normal

Operation

mode

Bus Off

state,

lower power

mode

DS20002298C-page 5

�MCP2021A/2A

1.2

Pin Descriptions

The descriptions of the pins are listed in Table 1-2.

TABLE 1-2:

PIN FUNCTION TABLE

Pin Number

Pin Name

8-lead

PDIP, SOIC

14-lead

PDIP, SOIC, TSSOP

Pin Type

4x4 DFN

RXD

1

1

1

Output

CS/LWAKE

2

2

2

TTL Input,

HV-tolerant

VREG

3

3

3

TXD

4

4

4

Description

Receive Data Output

Output

Chip Select and Local Wake-up

Input

Voltage Regulator Output

Input, HV-tolerant Transmit Data Input

RESET

—

—

5

Output

NC

—

—

6–10

—

Reset Output

No Connection

VSS

5

5

11

Power

Ground

LBUS

6

6

12

I/O, HV

LIN Bus

Battery

VBB

7

7

13

Power

FAULT/TXE

8

8

14

I/O, HV-tolerant

EP

—

9

—

—

1.2.1

RECEIVE DATA OUTPUT (RXD)

1.2.3

Fault Detect Output/Transmitter

Enable Input

Exposed Thermal Pad

POWER OUTPUT (VREG)

Receive Data Output pin. The RXD pin is a standard

CMOS output pin and it follows the state of the LBUS

pin.

Positive Supply Voltage Regulator Output pin. An

on-chip LDO gives +5.0 or +3.3V at 70 mA regulated

voltage on this pin.

1.2.2

1.2.4

CHIP SELECT AND LOCAL

WAKE-UP INPUT (CS/LWAKE)

Chip Select and Local Wake-up Input pin (TTL level,

high-voltage tolerant). This pin controls the device state

transition. Refer to Figure 1-1.

If CS/LWAKE = 1, the device can work in Operation

mode (FAULT/TXE = 1) or in Transmitter Off mode

(FAULT/TXE = 0). If CS/LWAKE = 0, the device can

work in Power-Down mode or in Ready mode.

An internal pull-down resistor will keep the CS/LWAKE

pin low to ensure that no disruptive data will be present

on the bus while the microcontroller is executing a

Power-On Reset and I/O initialization sequence. When

CS/LWAKE is ‘1’, a weak pull-down (~600 kΩ) is used

to reduce current. When CS/LWAKE is ‘0’, a stronger

pull-down (~300 kΩ) is used to maintain the logic level.

This pin may also be used as a local wake-up input

(see Figure 1-1). The microcontroller will set the I/O pin

to control the CS/LWAKE. An external switch or

another source can then wake up both the transceiver

and the microcontroller.

Note:

CS/LWAKE should NOT be tied directly to

the VREG pin as this could force the

MCP2021A/2A into Operation mode

before the microcontroller is initialized.

DS20002298C-page 6

TRANSMIT DATA INPUT (TXD)

Transmit Data Input pin (TTL level, HV-compliant,

adaptive pull-up). The transmitter reads the data

stream on the TXD pin and sends it to the LIN bus. The

LBUS pin is low (dominant) when TXD is low and high

(recessive) when TXD is high.

TXD is internally pulled up to approximately 4.2V. When

TXD is ‘0’, a weak pull-up (~900 kΩ) is used to reduce

current. When TXD is ‘1’, a stronger pull-up (~300 kΩ)

is used to maintain the logic level. A series

reverse-blocking diode allows applying TXD input

voltages greater than the internally generated 4.2V and

renders the TXD pin HV-compliant up to 30V (see

MCP2021A/2A Block Diagram).

1.2.5

RESET (MCP2022A ONLY)

RESET output pin. This pin is open-drain with ~90 kΩ

pull-up to VREG. It indicates the internal voltage has

reached a valid, stable level. As long as the internal

voltage is valid (above 0.8 VREG), this pin will remain

high (‘1’); otherwise, the RESET pin switches to low

(‘0’).

1.2.6

NO CONNECTION (NC)

No internal connection.

2012-2014 Microchip Technology Inc.

�MCP2021A/2A

1.2.7

GROUND (VSS)

1.2.10

Ground pin.

1.2.8

LIN BUS (LBUS)

Fault Detect Output/Transmitter Enable Input pin. The

output section is HV-tolerant open-drain (up to 30V).

The input section is identical to the TXD section (TTL

level, HV-compliant, adaptive pull-up). The internal

pull-up resistor may be too weak for some applications.

We recommend adding a 10 k external pull-up

resistor to ensure a logic high level. Its state is defined

as shown in Table 1-5. The device is placed in

Transmitter Off mode whenever this pin is low (‘0’),

either from an internal fault condition or by external

drive.

LIN Bus pin. LBUS is a bidirectional LIN bus interface

pin and is controlled by the signal TXD. It has an open

collector output with a current limitation. To reduce

electromagnetic emission, the slopes during signal

changes are controlled and the LBUS pin has

corner-rounding control for both falling and rising

edges.

The internal LIN receiver observes the activities on the

LIN bus and generates the output signal RXD that

follows the state of the LBUS. A 1st degree 160 kHz

low-pass input filter optimizes electromagnetic

immunity.

1.2.9

FAULT DETECT

OUTPUT/TRANSMITTER ENABLE

INPUT (FAULT/TXE)

If CS/LWAKE is high (‘1’), the FAULT/TXE signals a

mismatch between the TXD input and the LBUS level.

This can be used to detect a bus contention. Since the

bus exhibits a propagation delay, the sampling of the

internal compare is debounced to eliminate false faults.

BATTERY POSITIVE SUPPLY

VOLTAGE (VBB)

After the device wakes up, the FAULT/TXE indicates

what wakes the device if CS/LWAKE remains low (‘0’)

(refer to Table 1-5).

Battery Positive Supply Voltage pin. An external diode

is connected in series to prevent the device from being

reversely powered (refer to Figure 1-7).

The FAULT/TXE pin sampled at a rate faster than every

10 µs.

TABLE 1-3:

FAULT/TXE TRUTH TABLE

FAULT/TXE

TXD

In

RXD

Out

LINBUS

I/O

Thermal

Override

External

Input

Definition

Driven

Output

CS = 1

VBB

OFF

H

L

FAULT, TXD driven low, LBUS shorted to VBB (Note 1)

or LBUS/TXD permanent dominant detected and Transmit time-out shutdown.

H

H

OK

H

H

OK

L

H

H

H

VBB

OFF

L

L

GND

OFF

H

L

GND

OFF

H

H

OK, data is being received from LBUS

x

x

VBB

ON

H

L

FAULT, Transceiver in thermal shutdown

x

x

VBB

x

L

x

NO FAULT, the CPU is commanding the transceiver

to turn off the transmitter driver

CS = 0

x

x

x

x

x

L

Wake-up from LIN bus activity

x

x

x

x

x

H

Wake-up from POR

Legend: x = Don’t care

Note 1: The FAULT/TXE is valid after approximately 25 µs after the TXD falling edge. This is to eliminate false fault

reporting during bus propagation delays.

2012-2014 Microchip Technology Inc.

DS20002298C-page 7

�MCP2021A/2A

1.3

1.3.3

Fail-Safe Features

1.3.1

GENERAL FAIL-SAFE FEATURES

• An internal pull-down resistor on CS/LWAKE pin

disables the transmitter if the pin is floating.

• An internal pull-up resistor on the TXD pin places

TXD in high and the LBUS in recessive if the TXD

pin is floating.

• High-impedance and low-leakage current on LBUS

during loss of power or ground.

• The current limit on LBUS protects the transceiver

from being damaged if the pin is shorted to VBB.

1.3.2

THERMAL PROTECTION

The thermal protection circuit monitors the die

temperature and is able to shut down the LIN

transmitter and voltage regulator.

There are three causes for a thermal overload. A

thermal shutdown can be triggered by any one, or a

combination of, the following thermal overload

conditions:

• Voltage regulator overload

• LIN bus output overload

• Increase in die temperature due to increase in

environment temperature

The recovery time from the thermal shutdown is equal

to adequate cooling time.

Driving the TXD and checking the RXD pin make it

possible to determine whether there is a bus contention

(TXD = high, RXD = low) or a thermal overload

condition (TXD = low, RXD = high).

FIGURE 1-2:

THERMAL SHUTDOWN

STATE DIAGRAMS

Output

Overload

Voltage

Regulator

Shutdown

LIN Bus

Shorted to

VBB

Operation

Mode

Transmitter

Shutdown

Temp < SHUTDOWNTEMP Temp < SHUTDOWNTEMP

The LIN bus can be driven to a dominant level either

from the TXD pin or externally. An internal timer

deactivates the LBUS transmitter if a dominant status

(low) on the LIN bus lasts longer than Bus Dominant

Time-out

Time,

tTO(LIN)

(approximately

20 milliseconds). At the same time, the RXD output is

put in recessive (high), FAULT/TXE is also driven to low

and the internal LIN pull-up resistor is disconnected.

The timer is reset on any recessive LBUS status or POR

mode. The recessive status on LBUS can be caused

either by the bus being externally pulled up or by the

TXD pin being returned high.

1.4

Internal Voltage Regulator

The MCP2021A/2A have a positive regulator capable

of supplying +5.00 or +3.30 VDC ±3% at up to 70 mA of

load current over the entire operating temperature

range of -40°C to +125°C. The regulator uses a LDO

design, is short-circuit-protected and will turn the

regulator output off if its output falls below the shutdown

voltage threshold, VSD.

With a load current of 70 mA, the minimum input to

output voltage differential required for the output to

remain in regulation is typically +0.5V (+1V maximum

over the full operating temperature range). Quiescent

current is less than 100 µA with a full 70 mA load

current when the input to output voltage differential is

greater than +3.00V.

Regarding the correlation between VBB, VREG and IDD,

please refer to Figures 1-4 and 1-5. When the input

voltage (VBB) drops below the differential needed to

provide stable regulation, the voltage regulator output,

VREG, will track the input down to approximately VOFF,

at which point the regulator will turn off the output. This

will allow PIC® microcontrollers with internal POR

circuits to generate a clean arming of the POR trip

point. The MCP2021A/2A will then monitor VBB and

turn on the regulator when VBB is above the threshold

of regulator turn-on voltage, VON.

In Power-Down mode, the VBB monitor is turned off.

Under specific ambient temperature and battery

voltage range, the voltage regulator can output as high

as 150 mA current. For current load capability of the

voltage regulator, refer to Figures 2-8 and 2-9.

Note:

DS20002298C-page 8

TXD/LBUS TIME-OUT TIMER

The regulator has an overload current limit

of approximately 250 mA. The regulator

output voltage, VREG, is monitored. If

output voltage VREG is lower than VSD, the

voltage regulator will turn off. After a

recovery time of about 3 ms, the VREG will

be checked again. If there is no short

circuit (VREG > VSD), then the voltage

regulator remains on.

2012-2014 Microchip Technology Inc.

�MCP2021A/2A

The regulator requires an external output bypass

capacitor for stability. See Figure 2-1 for correct

capacity and ESR for stable operation.

Note:

TABLE 1-4:

A ceramic capacitor of at least 10 µF or a

tantalum capacitor of at least 2.2 µF is

recommended for stability.

In worst-case scenarios, the ceramic capacitor may

derate by 50%, based on tolerance, voltage and

temperature. Therefore, in order to ensure stability,

ceramic capacitors smaller than 10 µF may require a

small series resistance to meet the ESR requirements,

as shown in Table 1-4.

FIGURE 1-3:

RECOMMENDED SERIES

RESISTANCE FOR CERAMIC

CAPACITORS

Resistance

Capacitor

1

1 µF

0.47

2.2 µF

0.22

4.7 µF

0.1

6.8 µF

VOLTAGE REGULATOR BLOCK DIAGRAM

Pass

Element

VREG

VBB

Sampling

Network

Fast

Transient

Loop

Buffer

VSS

VREF

2012-2014 Microchip Technology Inc.

DS20002298C-page 9

�MCP2021A/2A

FIGURE 1-4:

VOLTAGE REGULATOR OUTPUT ON POWER-ON RESET

VBB

V

8

Minimum VBB to maintain regulation

VON

6

VOFF

4

2

0

t

VREG

V

5

VREG-NOM

4

3

2

1

0

t

Note 1:

2:

3:

4:

FIGURE 1-5:

(4)

(1)

(2)

(3)

Start-up, VBB < VON, regulator off.

VBB > VON, regulator on.

VBB Minimum VBB to maintain regulation.

VBB < VOFF, regulator will turn off.

VOLTAGE REGULATOR OUTPUT ON OVERCURRENT PROTECTION

IREG

mA

lLIM

0

t

VREG

6

5

V

VREG-NOM

4

VSD

3

2

1

0

Note 1:

2:

t

(1)

(2)

IREG less than lLIM, regulator on.

After IREG exceeds lLIM, the voltage regulator output will be reduced until VSD is reached.

DS20002298C-page 10

2012-2014 Microchip Technology Inc.

�MCP2021A/2A

1.5

1.5.1

Optional External Protection

V RECESSIVE

R TP ---------------------------------I REGMAX

REVERSE BATTERY PROTECTION

An external reverse-battery-blocking diode should be

used to provide polarity protection (see Figure 1-7).

1.5.2

EQUATION 1-2:

TRANSIENT VOLTAGE

PROTECTION (LOAD DUMP)

An external 43V transient suppressor (TVS) diode,

between VBB and ground, with a transient protection

resistor (RTP) in series with the battery supply and the

VBB pin, protects the device from power transients and

ESD events greater than 43V (see Figure 1-7). The

maximum value for the RTP protection resistor depends

upon two parameters: the minimum voltage the part will

start at and the impacts of this RTP resistor on the VBB

value, thus on the bus recessive level and slopes.

This leads to a set of three equations to fulfill.

Equation 1-1 provides a maximum RTP value

according to the minimum battery voltage the user

wants.

Equation 1-2 provides a maximum RTP value

according to the maximum error on the recessive level,

thus VBB, since the part uses VBB as the reference

value for the recessive level.

Equation 1-3 provides a maximum RTP value

according to the maximum relative variation the user

can accept on the slope when IREG varies.

Since both Equations 1-1 and 1-2 must be fulfilled, the

maximum allowed value for RTP is thus the smaller of

the two values found when solving Equations 1-1

and 1-2.

Usually Equation 1-1 gives the higher constraint

(smaller value) for RTP, as shown in the following

example where VBATmin is 8V.

However, the user needs to check that the value found

with Equation 1-1 fulfills Equations 1-2 and 1-3.

While this protection is optional, it should be

considered as good engineering practice.

EQUATION 1-1:

Where:

VRECESSIVE = Maximum variation tolerated on

the recessive level

Assume VRECESSIVE = 1V and IREGMAX = 50 mA.

Equation 1-2 shows 20.

EQUATION 1-3:

Slope VBATmin – 1V

RTP --------------------------------------------------------------I REGMAX

Where:

Slope = Maximum variation tolerated on the

slope level

IREGMAX = Maximum current the current will

provide to the load

VBATmin > VOFF + 1.0V

Assume

Slope = 15%,

VBATMIN = 8V

IREGMAX = 50 mA. Equation 1-2 shows 20.

1.5.3

and

CBAT CAPACITOR

Selecting CBAT = 10 x CREG is recommended.

However, this leads to a high value capacitor. Lower

values for CBAT capacitor can be used with respect to

some rules. In any case, the voltage at the VBB pin

should remain above VOFF when the device is turned

on.

The current peak at start-up (due to the fast charge of

the CREG and CBAT capacitors) may induce a

significant drop on the VBB pin. This drop is

proportional to the impedance of the VBAT connection

(see Figure 1-7).

The VBAT connection is mainly inductive and resistive.

Therefore, it can be modeled as a resistor (RTOT) in

series with an inductor (L). RTOT and L can be

measured.

V BATmin – 5.5V

R TP -------------------------------------250 mA

The following formula gives an indication of the

minimum value of CBAT using RTOT and L:

5.5V = V OFF + 1.0V

EQUATION 1-4:

Where:

CBAT

-------------- =

C REG

250 mA = Peak current at power-on when

VBB = 5.5V

2

2

100L + R TOT

-----------------------------------2

R TOT

2

1 + L + ------------100

Where:

Assume VBATmin = 8V. Equation 1-1 shows 10

L = Inductor (measured in mH)

RTOT = RLINE + RTP (measured in )

2012-2014 Microchip Technology Inc.

DS20002298C-page 11

�MCP2021A/2A

Equation 1-4 allows lower CBAT/CREG values than the

10x ratio we recommend.

Assume that we have a good quality VBAT connection

with RTOT = 0.1 and L = 0.1 mH.

Solving the equation gives CBAT/CREG = 1.

If we increase RTOT up to 1 the result becomes

CBAT/CREG = 1.4. However, if the connection is highly

resistive or highly inductive (poor connection), the

CBAT/CREG ratio greatly increases.

TABLE 1-5:

CBAT/CREG RATIO BY VBAT

CONNECTION TYPE

Connection

Type

RTOT

L

CBAT/CREG

Ratio

Good

0.1

0.1 mH

1

Typical

1

0.1 mH

1.4

Highly inductive

0.1

1 mH

7

Highly resistive

10

0.1 mH

7

Figure 1-6 shows the minimum recommended

CBAT/CREG ratio as a function of the impedance of the

VBAT connection.

FIGURE 1-6:

MINIMUM

RECOMMENDED

CBAT/CREG RATIO

CBAT/CREG

10

RBAT

BAT=10

=0.1

R

RBAT

BAT=4

=0.3

R

BAT=2

RBAT

=1

R

RBAT=1

RBAT=0.3

RBAT=0.1

1

0.1

VBAT Line Inductance [mH]

DS20002298C-page 12

1

2012-2014 Microchip Technology Inc.

�MCP2021A/2A

1.6

Typical Applications

FIGURE 1-7:

TYPICAL APPLICATION CIRCUIT

VBAT

VBAT

RTP

220 k

43V (5)

CBAT

VBB

CREG

Wake-Up

VDD

VBB

VREG

TXD

TXD

1 k

(6)

RXD

RXD

I/O

Microcontroller

I/O

Master Node Only

LIN Bus

LBUS

CS/LWAKE

(3)

MMBZ27V (4)

FAULT/TXE

220 pF

I/O

RESET

RESET

VSS

VSS

100 nF

Note 1: CREG, the load capacitor, should be ceramic or tantalum rated for extended temperatures, 1.0 – 22 µF.

See Figure 2-1 to select the correct ESR.

2: CBAT is the filter capacitor for the external voltage supply. Typically 10 x CREG, with no ESR restriction.

See Figure 1-6 to select the minimum recommended value for CBAT. The RTP value is added to the line

resistance.

3: This diode is only needed if CS/LWAKE is connected to the VBAT supply.

4: ESD protection diode.

5: This component is for additional load dump protection.

6: An external 10 kΩ resistor is recommended for some applications.

FIGURE 1-8:

TYPICAL LIN NETWORK CONFIGURATION

40m

+ Return

LIN bus

1 k

VBB

LIN bus

MCP202XA

LIN bus

MCP205X

Slave 1

(MCU)

LIN bus

MCP202XA

Slave 2

(MCU)

LIN bus

MCP2003

Slave n