PIC16(L)F1885X/7X

Full-Featured 28/40-Pin Microcontroller Product Brief

Description

PIC16(L)F1885X/7X microcontrollers feature Analog, Core Independent Peripherals and communication peripherals,

combined with eXtreme Low Power (XLP) for a wide range of general purpose and low-power applications. The family

will feature the CRC/SCAN, HLT and Windowed WDT to support customers looking to add safety to their application.

Additionally, this family includes up to 56 KB of Flash memory, along with a 10-bit ADC with MATHPAK extensions for

automated signal analysis to reduce the complexity of the application.

Core Features

Power-Saving Functionality

• C Compiler Optimized RISC Architecture

• Only 49 Instructions

• Operating Speed:

- DC – 32 MHz clock input

- 125 ns minimum instruction cycle

• Interrupt Capability

• 16-Level Deep Hardware Stack

• Three 8-Bit Timers (TMR2/4/6) with Hardware

Limit Timer (HLT) Extensions

• Four 16-Bit Timers (TMR0/1/3/5)

• Low Current Power-on Reset (POR)

• Configurable Power-up Timer (PWRTE)

• Brown-out Reset (BOR) with Fast Recovery

• Low-Power BOR (LPBOR) Option

• Windowed Watchdog Timer (WWDT):

- Variable prescaler selection

- Variable window size selection

- All sources configurable in hardware or software

• Programmable Code Protection

• Doze mode: Ability to run the CPU core slower

than the system clock

• Idle mode: Ability to halt CPU core while internal

peripherals continue operating

• Sleep mode: Lowest Power Consumption

• Peripheral Module Disable (PMD):

- Ability to disable hardware module to

minimize power consumption of unused

peripherals

Memory

•

•

•

•

Up to 56 KB Flash Program Memory

Up to 4 KB Data SRAM Memory

256B of EEPROM

Direct, Indirect and Relative Addressing modes

Operating Characteristics

• Operating Voltage Range:

- 1.8V to 3.6V (PIC16LF188XX)

- 2.3V to 5.5V (PIC16F188XX)

• Temperature Range:

- Industrial: -40°C to 85°C

- Extended: -40°C to 125°C

2014 Microchip Technology Inc.

eXtreme Low-Power (XLP) Features

•

•

•

•

Sleep mode: 50 nA @ 1.8V, typical

Watchdog Timer: 500 nA @ 1.8V, typical

Secondary Oscillator: 500 nA @ 32 kHz

Operating Current:

- 8 uA @ 32 kHz, 1.8V, typical

- 32 uA/MHz @ 1.8V, typical

Digital Peripherals

• Four Configurable Logic Cells (CLC):

- Integrated combinational and sequential logic

• Complementary Waveform Generator (CWG):

- Rising and falling edge dead-band control

- Full-bridge, half-bridge, 1-channel drive

- Multiple signal sources

• Five Capture/Compare/PWM (CCP) modules

• PWM: Two 10-bit Pulse-Width Modulators

• Numerically Controlled Oscillator (NCO):

- Generates true linear frequency control and

increased frequency resolution

- Input Clock: 0 Hz < fNCO < 32 MHz

- Resolution: fNCO/220

• Two Signal Measurement Timers (SMT):

- 24-bit Signal Measurement Timer

- Up to 12 different Acquisition modes

• Cyclical Redundancy Check (CRC/SCAN):

- 16-bit CRC

- Scans memory for NVM integrity

Advance Information

DS40001768A-page 1

�PIC16(L)F1885X/7X

• Serial Communications:

- SPI, I2C™, EUSART

- RS-232, RS-485, LIN compatible

- Auto-Baud Detect, Auto-Wake-up on start

• Up to 36 I/O Pins:

- Individually programmable pull-ups, slew rate

control interrupt-on-change with edge-select

• Peripheral Pin Select (PPS):

- Enables pin mapping of digital I/O

• Data Signal Modulator (DSM)

• 5-Bit Digital-to-Analog Converter (DAC):

- 5-bit resolution, rail-to-rail

- Positive Reference Selection

- Unbuffered I/O pin output

- Internal connections to ADCs and

comparators

• Voltage Reference:

- Fixed Voltage Reference with 1.024V, 2.048V

and 4.096V output levels

Clocking Structure

Analog Peripherals

• High-Precision Internal Oscillator:

- Selectable frequency range up to 32 MHz

• x2/x4 PLL with Internal and External Sources

• Low-Power Internal 31 kHz Oscillator

(LFINTOSC)

• External 32 kHz Crystal Oscillator (SOSC)

• Analog-to-Digital Converter (ADC) with MATHPAK

Extensions:

- 10-bit with up to 35 external channels

- Automated post-processing

- Automates math functions on input signals:

averaging, filter calculations, oversampling

and threshold comparison

- Operates in Sleep

• Two Comparators:

- Fixed Voltage Reference at (non) inverting

input(s)

- Comparator outputs externally accessible

PIC16(L)F188XX FAMILY TYPES

Device

Data Sheet Index

Program Flash Memory

(words)

Program Flash Memory

(KB)

EEPROM

(bytes)

Data SRAM

(bytes)

I/O Pins(2)

10-bit ADC MATHPAK (ch)

5-bit DAC

Comparator

8-bit (w/HLT)/16-bit Timers

SMT

Windowed Watchdog Timer

CRC + Memory Scan

CCP/10-bit PWM

Zero-Cross Detect

CWG

NCO

CLC

DSM

EUSART/I2C™/SPI

Peripheral Pin Select

TABLE 1:

PIC16(L)F18854

(A)

4096

7

256

512

25

24

1

2

3/4

2

Y

Y

5/2

Y

3

1

4

1

1/2

Y

PIC16(L)F18855

(B)

8192

14

256

1024

25

24

1

2

3/4

2

Y

Y

5/2

Y

3

1

4

1

1/2

Y

PIC16(L)F18875

(B)

8192

14

256

1024

36

35

1

2

3/4

2

Y

Y

5/2

Y

3

1

4

1

1/2

Y

PIC16(L)F18856

(C)

16384

28

256

2048

25

24

1

2

3/4

2

Y

Y

5/2

Y

3

1

4

1

1/2

Y

PIC16(L)F18876

(C)

16384

28

256

2048

36

35

1

2

3/4

2

Y

Y

5/2

Y

3

1

4

1

1/2

Y

PIC16(L)F18857

(D)

32768

56

256

4096

25

24

1

2

3/4

2

Y

Y

5/2

Y

3

1

4

1

1/2

Y

PIC16(L)F18877

(D)

32768

56

256

4096

36

35

1

2

3/4

2

Y

Y

5/2

Y

3

1

4

1

1/2

Y

Note 1:

One pin is input-only.

Data Sheet Index:

A

Future Release PIC16(L)F18854 Data Sheet, 28-Pin, Full-Featured 8-bit Microcontrollers

B

Future Release

PIC16(L)F18855/75 Data Sheet, 28/40-Pin, Full-Featured 8-bit Microcontrollers

C

Future Release

PIC16(L)F18856/76 Data Sheet, 28/40-Pin, Full-Featured 8-bit Microcontrollers

D

Future Release

PIC16(L)F18857/77 Data Sheet, 28/40-Pin, Full-Featured 8-bit Microcontrollers

Note:

For other small form-factor package availability and marking information, please visit

http://www.microchip.com/packaging or contact your local sales office.

DS40001768A-page 2

Advance Information

2014 Microchip Technology Inc.

�PIC16(L)F1885X/7X

TABLE 2:

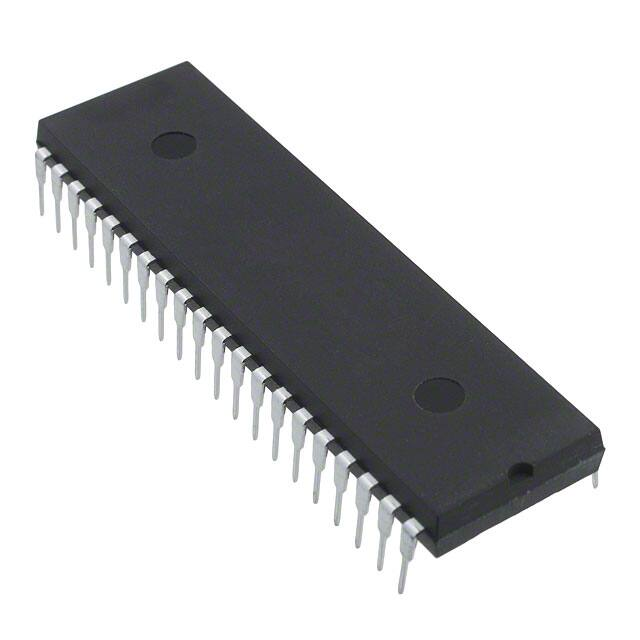

PACKAGES

Packages

(S)PDIP

SOIC

SSOP

QFN

(6x6)

UQFN

(4x4)

PIC16(L)F18854

X

X

X

X

X

PIC16(L)F18855

X

X

X

X

X

PIC16(L)F18875

X

PIC16(L)F18856

X

X

X

X

X

PIC16(L)F18876

X

PIC16(L)F18857

X

X

X

X

PIC16(L)F18877

X

Note:

TQFP

QFN

(8x8)

UQFN

(5x5)

X

X

X

X

X

X

X

X

X

Pin details are subject to change.

2014 Microchip Technology Inc.

Advance Information

DS40001768A-page 3

�PIC16(L)F1885X/7X

PIN DIAGRAMS

Pin Diagram – 28-Pin (S)PDIP, SOIC, SSOP

2

RA1

3

RA2

4

RA3

5

RA4

6

RA5

VSS

7

RA7

9

RA6

10

RC0

11

RC1

12

RC2

13

RC3

Note 1:

2:

1

RA0

PIC16(L)F18854/18855/18856/18857

VPP/MCLR/RE3

8

14

28

RB7

27

RB6

26

RB5

25

RB4

24

23

RB3

22

21

RB1

RB0

20

VDD

19

18

VSS

RC7

17

RC6

16

RC5

15

RC4

RB2

See Table 3 for location of all peripheral functions.

All VDD and all VSS pins must be connected at the circuit board level. Allowing one or more VSS or VDD pins to float

may result in degraded electrical performance or non-functionality.

28

27

26

25

24

23

22

RA1

RA0

RE3/MCLR/VPP

RB7

RB6

RB5

RB4

Pin Diagram – 28-Pin UQFN (4x4) (except for PIC16F18857) and QFN (6x6)

16

8

18

)F

(L

75

8

/1

87

18

6/

87

RC0 8

RC1 9

RC2 10

RC3 11

RC4 12

RC5 13

RC6 14

7

1

2

3

4

5

6

7

C

PI

RA2

RA3

RA4

RA5

VSS

RA7

RA6

21

20

19

18

17

16

15

RB3

RB2

RB1

RB0

VDD

VSS

RC7

Note 1: See Table 3 for location of all peripheral functions.

2:

All VDD and all VSS pins must be connected at the circuit board level. Allowing one or more VSS or VDD pins to float

may result in degraded electrical performance or non-functionality.

3:

The bottom pad of the QFN/UQFN package should be connected to VSS at the circuit board level.

DS40001768A-page 4

Advance Information

2014 Microchip Technology Inc.

�PIC16(L)F1885X/7X

Pin Diagram – 40-Pin PDIP

Note 1:

2:

VPP/MCLR/RE3

1

40

RB7/ICSPDAT

RA0

2

39

RB6/ICSPCLK

RA1

3

38

RB5

RA2

37

RB4

5

36

RB3

RA4

6

35

RB2

RA5

RE0

7

34

RB1

RB0

RE1

9

PIC16(L)F18875/18876/18877

4

RA3

8

33

32

VDD

31

VSS

30

RD7

29

RD6

28

RD5

27

RD4

26

RC7

16

25

RC6

17

24

RC5

18

23

RD0

19

22

RC4

RD3

RD1

20

21

RD2

RE2

10

VDD

11

VSS

12

RA7

13

RA6

14

RC0

15

RC1

RC2

RC3

See Table 4 for location of all peripheral function.

All VDD and all VSS pins must be connected at the circuit board level. Allowing one or more VSS or VDD pins to float

may result in degraded electrical performance or non-functionality.

44

43

42

41

40

39

38

37

36

35

34

RC6

RC5

RC4

RD3

RD2

RD1

RD0

RC3

RC2

RC1

NC

Pin Diagram – 44-Pin TQFP

C

16

1

)F

(L

88

75

/1

88

76

/1

88

2:

NC

RC0

RA6

RA7

VSS

VDD

RE2

RE1

RE0

RA5

RA4

NC

RB4

RB5

ICSPCLK/RB6

ICSPDAT/RB7

VPP/MCLR/RE3

AN0/RA0

RA1

RA2

RA3

NC

Note 1:

33

32

31

30

29

28

27

26

25

24

23

12

13

14

15

16

17

18

19

20

21

22

77

RD5

RD6

RD7

VSS

VDD

RB0

RB1

RB2

RB3

1

2

3

4

5

6

7

8

9

10

11

PI

RC7

RD4

See Table 4 for location of all peripheral functions.

All VDD and all VSS pins must be connected at the circuit board level. Allowing one or more VSS or VDD pins to float

may result in degraded electrical performance or non-functionality.

2014 Microchip Technology Inc.

Advance Information

DS40001768A-page 5

�PIC16(L)F1885X/7X

29 RA6

28 RA7

27 VSS

F1

L)

3

4

88

5

/

75

26 VDD

25 RE2

8

18

6

88

/1

76

7

8

24 RE1

23 RE0

20

18

17

16

15

14

13

22 RA5

21 RA4

RB3

RB4

RB5

ICSPCLK/RB6

ICSPDAT/RB7

VPP/MCLR/RE3

RA0

RA1

RA2

RA3

11

10

19

77

9

12

31

32

34

33

35

36

37

39

38

30 RC0

(

16

RD5

RD6

RD7

VSS

VDD

RB0

RB1

RB2

C

PI

RC7 1

RD4 2

40

RC6

RC5

RC4

RD3

RD2

RD1

RD0

RC3

RC2

RC1

Pin Diagram – 40-Pin UQFN (5x5)

Note 1:

2:

3:

See Table 4 for location of all peripheral functions.

All VDD and all VSS pins must be connected at the circuit board level. Allowing one or more VSS or VDD pins to float

may result in degraded electrical performance or non-functionality.

The bottom pad of the QFN/UQFN package should be connected to VSS at the circuit board level.

1

2

3

4

5

6

7

8

9

10

11

C1

PI

8

F1

L)

6(

87

18

5/

87

18

6/

87

33

32

31

30

29

28

27

26

25

24

23

RA6

RA7

VSS

VSS

VDD

VDD

RE2

RE1

RE0

RA5

RA4

RB3

NC

RB4

RB5

ICSPCLK/RB6

ICSPDAT/RB7

VPP/MCLR/RE3

RA0

RA1

RA2

RA3

12

13

14

15

16

17

18

19

20

21

22

7

RC7

RD4

RD5

RD6

RD7

VSS

VDD

VDD

RB0

RB1

RB2

44

43

42

41

40

39

38

37

36

35

34

RC6

RC5

RC4

RD3

RD2

RD1

RD0

RC3

RC2

RC1

RC0

Pin Diagram – 44-Pin QFN (8x8)

Note 1:

2:

3:

See Table 4 for location of all peripheral functions.

All VDD and all VSS pins must be connected at the circuit board level. Allowing one or more VSS or VDD pins to float

may result in degraded electrical performance or non-functionality.

The bottom pad of the QFN/UQFN package should be connected to VSS at the circuit board level.

DS40001768A-page 6

Advance Information

2014 Microchip Technology Inc.

�Voltage Reference

DAC

Zero-Cross Detect

MSSP (SPI/I2C™)

EUSART

DSM

Timers/SMT

CCP and PWM

CWG

CLC

NCO

Clock Reference (CLKR)

Interrupt-on-Change

Basic

2

27

ANA0

—

—

C1IN0C2IN0-

—

—

—

—

—

—

—

CLCIN0(1)

—

—

IOCA0

—

RA1

3

28

ANA1

—

—

C1IN1C2IN1-

—

—

—

—

—

—

—

CLCIN1(1)

—

—

IOCA1

—

RA2

4

1

ANA2

VREF-

DAC1OUT1

C1IN0+

C2IN0+

—

—

—

—

—

—

—

—

—

—

IOCA2

—

RA3

5

2

ANA3

VREF+

—

C1IN1+

—

—

—

MDCIN1(1)

—

—

—

—

—

—

IOCA3

—

—

MDCIN2(1)

T0CKI(1)

CCP5(1)

—

—

—

—

IOCA4

—

(1)

RA4

6

3

ANA4

—

—

Comparators

ADC

RA0

—

—

—

(1)

DS40001768A-page 7

RA5

7

4

ANA5

—

—

—

—

SS1

—

—

—

—

—

—

—

IOCA5

—

RA6

10

7

ANA6

—

—

—

—

—

—

—

—

—

—

—

—

—

IOCA6

OSC2

CLKOUT

RA7

9

6

ANA7

—

—

—

—

—

—

—

—

—

—

—

—

—

IOCA7

OSC1

CLKIN

RB0

21

18

ANB0

—

—

C2IN1+

ZCD

SS2(1)

—

—

—

CCP4(1)

CWG1IN(1)

—

—

—

INT(1)

IOCB0

—

RB1

22

19

ANB1

—

—

C1IN3C2IN3-

—

SCL2(3,4)

SCK2(1)

—

—

—

—

CWG2IN(1)

—

—

—

IOCB1

—

RB2

23

20

ANB2

—

—

—

—

SDA2(3,4)

SDI2(1)

—

—

—

—

CWG3IN(1)

—

—

—

IOCB2

—

RB3

24

21

ANB3

—

—

C1IN2C2IN2-

—

—

—

—

—

—

—

—

—

—

IOCB3

—

RB4

25

22

ANB4

ADCACT(1)

—

—

—

—

—

—

—

T5G(1)

SMTWIN2(1)

—

—

—

—

—

IOCB4

—

Note

1:

2:

3:

4:

MDMIN

This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 5 for details on which PORT pins may

be used for this signal.

All output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 6.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for I2C™ logic levels.; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but

input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I2C specific or SMBUS input buffer thresholds.

PIC16(L)F1885X/7X

Advance Information

28-Pin (U)QFN

28-PIN ALLOCATION TABLE (PIC16(L)F1885X)

28-Pin SPDIP/SOIC/SSOP

TABLE 3:

I/O

2014 Microchip Technology Inc.

PIN ALLOCATION TABLES

�DAC

Comparators

Zero-Cross Detect

MSSP (SPI/I2C™)

EUSART

DSM

Timers/SMT

CCP and PWM

CWG

—

—

—

—

—

—

—

T1G(1)

SMTSIG2(1)

CCP3(1)

—

RB6

27

24

ANB6

—

—

—

—

—

—

—

—

—

—

RB7

28

25

ANB7

—

DAC1OUT2

—

—

—

—

—

T6IN

(1)

Basic

Voltage Reference

ANB5

Interrupt-on-Change

ADC

23

Clock Reference (CLKR)

28-Pin (U)QFN

26

NCO

28-Pin SPDIP/SOIC/SSOP

RB5

CLC

I/O

28-PIN ALLOCATION TABLE (PIC16(L)F1885X)

—

—

—

IOCB5

—

CLCIN2(1)

—

—

IOCB6

ICSPCLK

(1)

—

—

IOCB7

ICSPDAT

Advance Information

—

—

CLCIN3

—

—

—

—

—

IOCC0

SOSCO

RC0

11

6

ANC0

—

—

—

—

—

—

—

T1CKI(1)

T3CKI(1)

T3G(1)

SMTWIN1(1)

RC1

12

9

ANC1

—

—

—

—

—

—

—

SMTSIG1(1)

CCP2(1)

—

—

—

—

IOCC1

SOSCI

RC2

13

10

ANC2

—

—

—

—

—

—

—

T5CKI(1)

CCP1(1)

—

—

—

—

IOCC2

—

—

SCL1(3,4)

(1)

—

—

T2IN(1)

—

—

—

—

—

IOCC3

—

—

—

—

—

IOCC4

—

RC3

14

11

ANC3

—

—

—

SCK1

2014 Microchip Technology Inc.

RC4

15

12

ANC4

—

—

—

—

SDA1(3,4)

SDI1(1)

—

—

—

—

RC5

16

13

ANC5

—

—

—

—

—

—

—

T4IN(1)

—

—

—

—

—

IOCC5

—

RC6

17

14

ANC6

—

—

—

—

—

CK(3)

—

—

—

—

—

—

—

IOCC6

—

RC7

18

15

ANC7

—

—

—

—

—

RX(1)

DT(3)

—

—

—

—

—

—

—

IOCC7

—

RE3

1

26

—

—

—

—

—

—

—

—

—

—

—

—

—

—

IOCE3

MCLR

VPP

VDD

20

17

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

VSS

8,

19

5,

16

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Note

1:

2:

3:

4:

This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 5 for details on which PORT pins may

be used for this signal.

All output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 6.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for I2C™ logic levels.; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but

input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I2C specific or SMBUS input buffer thresholds.

PIC16(L)F1885X/7X

DS40001768A-page 8

TABLE 3:

�1:

2:

3:

4:

NCO

Clock Reference (CLKR)

Interrupt-on-Change

Basic

CCP1

CCP2

CCP3

CCP4

CCP5

PWM6OUT

PWM7OUT

CLC

TMR0

CCP and PWM

DSM

CWG

TX/

CK(3)

DT(3)

Timers/SMT

SDO1

SCK1

SDO2

SCK2

EUSART

—

DSM

C1OUT

C2OUT

MSSP (SPI/I2C™)

—

Zero-Cross Detect

—

CWG1A

CWG1B

CWG1C

CWG1D

CWG2A

CWG2B

CWG2C

CWG2D

CWG3A

CWG3B

CWG3C

CWG3D

CLC1OUT

CLC2OUT

CLC3OUT

CLC4OUT

NCO

CLKR

—

—

This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 5 for details on which PORT pins may

be used for this signal.

All output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 6.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for I2C™ logic levels.; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but

input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I2C specific or SMBUS input buffer thresholds.

DS40001768A-page 9

PIC16(L)F1885X/7X

Advance Information

Note

ADGRDA

ADGRDB

Comparators

—

DAC

—

Voltage Reference

28-Pin (U)QFN

OUT(2)

ADC

28-Pin SPDIP/SOIC/SSOP

28-PIN ALLOCATION TABLE (PIC16(L)F1885X)

I/O

2014 Microchip Technology Inc.

TABLE 3:

�44-Pin TQFP

40-Pin UQFN

44-Pin QFN

ADC

Voltage Reference

DAC

Zero-Cross Detect

MSSP (SPI/I2C™)

EUSART

DSM

Timers/SMT

CCP and PWM

CWG

CLC

NCO

Clock Reference (CLKR)

Interrupt-on-Change

Basic

RA0

2

19

17

19

ANA0

—

—

C1IN0C2IN0-

—

—

—

—

—

—

—

CLCIN0(1)

—

—

IOCA0

—

RA1

3

20

18

20

ANA1

—

—

C1IN1C2IN1-

—

—

—

—

—

—

—

CLCIN1(1)

—

—

IOCA1

—

RA2

4

21

19

21

ANA2

VREF-

DAC1OUT1

C1IN0+

C2IN0+

—

—

—

—

—

—

—

—

—

—

IOCA2

—

RA3

5

22

20

22

ANA3

VREF+

—

C1IN1+

—

—

—

MDCIN1(1)

—

—

—

—

IOCA3

—

(1)

Comparators

40-Pin PDIP

Advance Information

!/O

40/44-PIN ALLOCATION TABLE (PIC16(L)F1887X)

—

—

(1)

2014 Microchip Technology Inc.

RA4

6

23

21

23

ANA4

—

—

—

—

—

—

MDCIN2

—

—

—

—

IOCA4

—

RA5

7

24

22

24

ANA5

—

—

—

—

SS1(1)

—

MDMIN(1)

—

—

—

—

—

—

IOCA5

—

RA6

14

31

29

33

ANA6

—

—

—

—

—

—

—

—

—

—

—

—

—

IOCA6

OSC2

CLKOUT

RA7

13

30

28

32

ANA7

—

—

—

—

—

—

—

—

—

—

—

—

—

IOCA7

OSC1

CLKIN

RB0

33

8

8

9

ANB0

—

—

C2IN1+

ZCD

SS2(1)

—

—

—

CCP4(1)

CWG1IN(1)

—

—

—

INT(1)

IOCB0

—

RB1

34

9

9

10

ANB1

—

—

C1IN3C2IN3-

—

SCL2(3,4)

SCK2(1)

—

—

—

—

CWG2IN(1)

—

—

—

IOCB1

—

RB2

35

10

10

11

ANB2

—

—

—

—

SDA2(3,4)

SDI2(1)

—

—

—

—

CWG3IN(1)

—

—

—

IOCB2

—

RB3

36

11

11

12

ANB3

—

—

C1IN2C2IN2-

—

—

—

—

—

—

—

—

—

—

IOCB3

—

RB4

37

14

12

14

ANB4

ADCACT(1)

—

—

—

—

—

—

—

T5G(1)

SMTWIN2(1)

—

—

—

—

—

IOCB4

—

RB5

38

15

13

15

ANB5

—

—

—

—

—

—

—

T1G(1)

SMTSIG2(1)

CCP3(1)

—

—

—

—

IOCB5

—

RB6

39

16

14

16

ANB6

—

—

—

—

—

—

—

—

—

—

CLCIN2(1)

—

—

IOCB6

ICSPCLK

RB7

40

17

15

17

ANB7

—

DAC1OUT2

—

—

—

—

—

T6IN(1)

—

—

CLCIN3(1)

—

—

IOCB7

ICSPDAT

Note

1:

2:

3:

4:

T0CKI

CCP5

(1)

This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 5 for details on which PORT pins may

be used for this signal.

All output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 6.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for I2C™ logic levels.; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but

input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I2C specific or SMBUS input buffer thresholds.

PIC16(L)F1885X/7X

DS40001768A-page 10

TABLE 4:

�Zero-Cross Detect

MSSP (SPI/I2C™)

EUSART

DSM

—

—

—

—

—

—

T1CKI(1)

T3CKI(1)

T3G(1)

SMTWIN1(1)

RC1

16

35

31

35

ANC1

—

—

—

—

—

—

—

SMTSIG1(1)

RC2

17

36

32

36

ANC2

—

—

—

—

—

(1)

—

—

T5CKI

—

—

T2IN

(1)

—

—

—

—

—

IOCC0

SOSCO

CCP2(1)

—

—

—

—

IOCC1

SOSCI

(1)

—

—

—

—

IOCC2

—

—

—

—

—

—

IOCC3

—

—

—

—

—

IOCC4

—

CCP1

RC3

18

37

33

37

ANC3

—

—

—

—

SCL1(3,4)

SCK1(1)

RC4

23

42

38

42

ANC4

—

—

—

—

SDA1(3,4)

SDI1(1)

—

—

—

—

RC5

24

43

39

43

ANC5

—

—

—

—

—

—

—

T4IN(1)

—

—

—

—

—

IOCC5

—

RC6

25

44

40

44

ANC6

—

—

—

—

—

CK(3)

—

—

—

—

—

—

—

IOCC6

—

RC7

26

1

1

1

ANC7

—

—

—

—

—

RX(1)

DT(3)

—

—

—

—

—

—

—

IOCC7

—

RD0

19

38

34

38

AND0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

RD1

20

39

35

39

AND1

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

RD2

21

40

36

40

AND2

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

RD3

22

41

37

41

AND3

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

RD4

27

2

2

2

AND4

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

RD5

28

3

3

3

AND5

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

DS40001768A-page 11

RD6

29

4

4

4

AND6

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

RD7

30

5

5

5

AND7

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

RE0

8

25

23

25

ANE0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

RE1

9

26

24

26

ANE1

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

RE2

10

27

25

27

ANE2

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Note

1:

2:

3:

4:

This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 5 for details on which PORT pins may

be used for this signal.

All output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 6.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for I2C™ logic levels.; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but

input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I2C specific or SMBUS input buffer thresholds.

PIC16(L)F1885X/7X

Advance Information

Basic

Comparators

—

Interrupt-on-Change

DAC

ANC0

Clock Reference (CLKR)

Voltage Reference

34

NCO

ADC

30

CLC

44-Pin QFN

32

CWG

40-Pin UQFN

15

CCP and PWM

44-Pin TQFP

RC0

Timers/SMT

40-Pin PDIP

40/44-PIN ALLOCATION TABLE (PIC16(L)F1887X)

!/O

2014 Microchip Technology Inc.

TABLE 4:

�44-Pin TQFP

40-Pin UQFN

44-Pin QFN

ADC

Voltage Reference

DAC

Comparators

Zero-Cross Detect

MSSP (SPI/I2C™)

EUSART

DSM

Timers/SMT

CCP and PWM

CWG

CLC

NCO

Clock Reference (CLKR)

Interrupt-on-Change

RE3

1

18

16

18

—

—

—

—

—

—

—

—

—

—

—

—

—

—

IOCE3

MCLR

VPP

VDD

11,

32

7,

28

7,

26

8,

28

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

VSS

12,

31

6,

29

6,

27

6,

31,

30

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

OUT(2)

—

—

—

—

ADGRDA

ADGRDB

—

—

C1OUT

C2OUT

—

SDO1

SCK1

SDO2

SCK2

TX/

CK(3)

DT(3)

DSM

TMR0

CCP1

CCP2

CCP3

CCP4

CCP5

PWM6OUT

PWM7OUT

CWG1A

CWG1B

CWG1C

CWG1D

CWG2A

CWG2B

CWG2C

CWG2D

CWG3A

CWG3B

CWG3C

CWG3D

CLC1OUT

CLC2OUT

CLC3OUT

CLC4OUT

—

—

Note

1:

2:

3:

4:

NCO CLKR

Basic

40-Pin PDIP

Advance Information

!/O

40/44-PIN ALLOCATION TABLE (PIC16(L)F1887X)

This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 5 for details on which PORT pins may

be used for this signal.

All output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 6.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for I2C™ logic levels.; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but

input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I2C specific or SMBUS input buffer thresholds.

PIC16(L)F1885X/7X

DS40001768A-page 12

TABLE 4:

2014 Microchip Technology Inc.

�PIC16(L)F1885X/7X

TABLE 5:

PPS INPUT SIGNAL ROUTING OPTIONS DETAILS

Input Signal

Name

Input Register

Name

Default

Location at

POR

INT

INTPPS

RB0

T0CKI

T0CKIPPS

RA4

T1CKI

T1CKIPPS

RC0

T1G

T1GPPS

RB5

T3CKI

T3CKIPPS

Re-mappable to any one of these

PORTx pins

PPS Input Register Value to PORT

Pin Mapping Reference Table

PIC16F1885X

(28-Pin devices)

PIC16F1887X

(40/44-Pin

devices)

Desired Input

Pin

Value to Write

to Register(1)

PORTA, PORTB

PORTA, PORTB

RA0

0x00

PORTA, PORTB

PORTA, PORTB

RA1

0x01

PORTA, PORTC

PORTA, PORTC

RA2

0x02

PORTB, PORTC

PORTB, PORTC

RA3

0x03

RC0

PORTB, PORTC

PORTB, PORTC

RA4

0x04

T3G

T3GPPS

RC0

PORTA, PORTC

PORTA, PORTC

RA5

0x05

T5CKI

T5CKIPPS

RC2

PORTA, PORTC

PORTA, PORTC

RA6

0x06

T5G

T5GPPS

RB4

PORTB, PORTC

PORTB, PORTD

RA7

0x07

T2IN

T2INPPS

RC3

PORTA, PORTC

PORTA, PORTC

RB0

0x08

T4IN

T4INPPS

RC5

PORTB, PORTC

PORTB, PORTC

RB1

0x09

T6IN

T6INPPS

RB7

PORTB, PORTC

PORTB, PORTD

RB2

0x0A

CCP1

CCP1PPS

RC2

PORTB, PORTC

PORTB, PORTC

RB3

0x0B

CCP2

CCP2PPS

RC1

PORTB, PORTC

PORTB, PORTC

RB4

0x0C

CCP3

CCP3PPS

RB5

PORTB, PORTC

PORTB, PORTD

RB5

0x0D

CCP4

CCP4PPS

RB0

PORTB, PORTC

PORTB, PORTD

RB6

0x0E

CCP5

CCP5PPS

RA4

PORTA, PORTC

PORTA, PORTE

RB7

0x0F

SMTWIN1

SMTWIN1PPS

RC0

PORTB, PORTC

PORTB, PORTC

RC0

0x10

SMTSIG1

SMTSIG1PPS

RC1

PORTB, PORTC

PORTB, PORTC

RC1

0x11

SMTWIN2

SMTWIN2PPS

RB4

PORTB, PORTC

PORTB, PORTD

RC2

0x12

SMTSIG2

SMTSIG2PPS

RB5

PORTB, PORTC

PORTB, PORTD

RC3

0x13

CWG1IN

CWG1PPS

RB0

PORTB, PORTC

PORTB, PORTD

RC4

0x14

CWG2IN

CWG2PPS

RB1

PORTB, PORTC

PORTB, PORTD

RC5

0x15

CWG3IN

CWG3PPS

RB2

PORTB, PORTC

PORTB, PORTD

RC6

0x16

MDCIN1

MDCIN1PPS

RA3

PORTA, PORTC

PORTA, PORTD

RC7

0x17

MDCIN2

MDCIN2PPS

RA4

PORTA, PORTC

PORTA, PORTD

RD0

0x18

MDMIN

MDMINPPS

RA5

PORTA, PORTC

PORTA, PORTD

RD1

0x19

CLCIN0

CLCIN0PPS

RA0

PORTA, PORTC

PORTA, PORTC

RD2

0x1A

CLCIN1

CLCIN1PPS

RA1

PORTB, PORTC

PORTA, PORTC

RD3

0x1B

CLCIN2

CLCIN2PPS

RB6

PORTB, PORTC

PORTB, PORTD

RD4

0x1C

CLCIN3

CLCIN3PPS

RB7

PORTB, PORTC

PORTB, PORTD

RD5

0x1D

ADCACT

ADCACTPPS

RB4

PORTB, PORTC

PORTB, PORTD

RD6

0x1E

SCK1/SCL1

SSP1CLKPPS

RC3

PORTB, PORTC

PORTB, PORTC

RD7

0x1F

SDI1/SDA1

SSP1DATPPS

RC4

PORTA, PORTC

PORTB, PORTC

RE0

0x20

SS1

SSPSS1PPS

RA5

PORTB, PORTC

PORTA, PORTD

RE1

0x21

SCK2/SCL2

SSP2CLKPPS

RB1

PORTB, PORTC

PORTB, PORTD

RE2

0x22

SDI2/SDA2

SSP2DATPPS

RB2

PORTB, PORTC

PORTB, PORTD

RE3

0x23

SS2

SSP2SSPPS

RB0

PORTB, PORTC

PORTB, PORTD

RX/DT

RXPPS

RC7

PORTB, PORTC

PORTB PORTC

TX/CK

CKPPS

RC6

PORTA, PORTB

PORTB PORTC

Note 1:

Only a few of the values in this column are valid for any given signal. For example, since the INT signal can only be

mapped to PORTA or PORTB pins, only the register values 0x00-0x0F (corresponding to RA0-RA7 and RB0-RB7) are

valid values to write to the INTPPS register.

2014 Microchip Technology Inc.

Advance Information

DS40001768A-page 13

�PIC16(L)F1885X/7X

TABLE 6:

PPS OUTPUT SIGNAL ROUTING OPTIONS

Re-mappable to any one of these PORTx pins

Output Signal Name

PIC16F1885X

(28-Pin devices)

PIC16F1887X

(40/44-Pin devices)

By writing this value to the

Corresponding RxyPPS(2)

Register

ADGRDB

PORTA, PORTC

PORTA, PORTC

0x25

ADGRDA

PORTA, PORTC

PORTA, PORTC

0x24

CWG3D

PORTA, PORTC

PORTA, PORTD

0x23

CWG3C

PORTA, PORTC

PORTA, PORTD

0x22

CWG3B

PORTA, PORTC

PORTA, PORTE(1)

0x21

CWG3A

PORTB, PORTC

PORTB, PORTC

0x20

CWG2D

PORTB, PORTC

PORTB, PORTD

0x1F

CWG2C

PORTB, PORTC

PORTB, PORTD

0x1E

CWG2B

PORTB, PORTC

PORTB, PORTD

0x1D

CWG2A

PORTB, PORTC

PORTB, PORTC

0x1C

DSM

PORTA, PORTC

PORTA, PORTD

0x1B

CLKR

PORTB, PORTC

PORTB, PORTC

0x1A

NCO

PORTA, PORTC

PORTA, PORTD

0x19

TMR0

PORTB, PORTC

PORTB, PORTC

0x18

SDO2/SDA2

PORTB, PORTC

PORTB, PORTD

0x17

SCK2/SCL2

PORTB, PORTC

PORTB, PORTD

0x16

SDO1/SDA1

PORTB, PORTC

PORTB, PORTC

0x15

SCK1/SCL1

PORTB, PORTC

PORTB, PORTC

0x14

C2OUT

PORTA, PORTC

PORTA, PORTE(1)

0x13

C1OUT

PORTA, PORTC

PORTA, PORTD

0x12

DT

PORTB, PORTC

PORTB, PORTC

0x11

TX/CK

PORTB, PORTC

PORTB, PORTC

0x10

PWM7OUT

PORTA, PORTC

PORTA, PORTC

0x0F

PWM6OUT

PORTA, PORTC

PORTA, PORTD

0x0E

CCP5

PORTA, PORTC

PORTA, PORTE(1)

0x0D

CCP4

PORTB, PORTC

PORTB, PORTD

0x0C

CCP3

PORTB, PORTC

PORTB, PORTD

0x0B

CCP2

PORTB, PORTC

PORTB, PORTC

0x0A

CCP1

PORTB, PORTC

PORTB, PORTC

0x09

CWG1D

PORTB, PORTC

PORTB, PORTD

0x08

CWG1C

PORTB, PORTC

PORTB, PORTD

0x07

CWG1B

PORTB, PORTC

PORTB, PORTD

0x06

CWG1A

PORTB, PORTC

PORTB, PORTC

0x05

CLC4OUT

PORTB, PORTC

PORTB, PORTD

0x04

CLC3OUT

PORTB, PORTC

PORTB, PORTD

0x03

CLC2OUT

PORTA, PORTC

PORTA, PORTC

0x02

CLC1OUT

PORTA, PORTC

PORTA, PORTC

0x01

Note 1:

2:

RE3 is an input-only pin. Therefore, this signal may only be mapped to RE0, RE1 or RE2 (or a PORTA

pin).

In “RxyPPS”, the “x” is a PORT letter (e.g., “C”), and the “y” is a port pin number (e.g., “6”). For example,

to map the UART TX/CK signal to output onto RC6, write 0x10 to the RC6PPS register.

DS40001768A-page 14

Advance Information

2014 Microchip Technology Inc.

�Note the following details of the code protection feature on Microchip devices:

•

Microchip products meet the specification contained in their particular Microchip Data Sheet.

•

Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

•

There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

•

Microchip is willing to work with the customer who is concerned about the integrity of their code.

•

Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device

applications and the like is provided only for your convenience

and may be superseded by updates. It is your responsibility to

ensure that your application meets with your specifications.

MICROCHIP MAKES NO REPRESENTATIONS OR

WARRANTIES OF ANY KIND WHETHER EXPRESS OR

IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION,

INCLUDING BUT NOT LIMITED TO ITS CONDITION,

QUALITY, PERFORMANCE, MERCHANTABILITY OR

FITNESS FOR PURPOSE. Microchip disclaims all liability

arising from this information and its use. Use of Microchip

devices in life support and/or safety applications is entirely at

the buyer’s risk, and the buyer agrees to defend, indemnify and

hold harmless Microchip from any and all damages, claims,

suits, or expenses resulting from such use. No licenses are

conveyed, implicitly or otherwise, under any Microchip

intellectual property rights.

Trademarks

The Microchip name and logo, the Microchip logo, dsPIC,

FlashFlex, flexPWR, JukeBlox, KEELOQ, KEELOQ logo, Kleer,

LANCheck, MediaLB, MOST, MOST logo, MPLAB,

OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC,

SST, SST Logo, SuperFlash and UNI/O are registered

trademarks of Microchip Technology Incorporated in the

U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are

registered trademarks of Microchip Technology Incorporated

in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo,

CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit

Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet,

KleerNet logo, MiWi, MPASM, MPF, MPLAB Certified logo,

MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code

Generation, PICDEM, PICDEM.net, PICkit, PICtail,

RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total

Endurance, TSHARC, USBCheck, VariSense, ViewSpan,

WiperLock, Wireless DNA, and ZENA are trademarks of

Microchip Technology Incorporated in the U.S.A. and other

countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

Silicon Storage Technology is a registered trademark of

Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology

Germany II GmbH & Co. KG, a subsidiary of Microchip

Technology Inc., in other countries.

All other trademarks mentioned herein are property of their

respective companies.

© 2014, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

ISBN: 978-1-63276-622-9

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

== ISO/TS 16949 ==

2014 Microchip Technology Inc.

Microchip received ISO/TS-16949:2009 certification for its worldwide

headquarters, design and wafer fabrication facilities in Chandler and

Tempe, Arizona; Gresham, Oregon and design centers in California

and India. The Company’s quality system processes and procedures

are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchip’s quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

Advance Information

DS40001768A-page 15

�Worldwide Sales and Service

AMERICAS

ASIA/PACIFIC

ASIA/PACIFIC

EUROPE

Corporate Office

2355 West Chandler Blvd.

Chandler, AZ 85224-6199

Tel: 480-792-7200

Fax: 480-792-7277

Technical Support:

http://www.microchip.com/

support

Web Address:

www.microchip.com

Asia Pacific Office

Suites 3707-14, 37th Floor

Tower 6, The Gateway

Harbour City, Kowloon

Hong Kong

Tel: 852-2943-5100

Fax: 852-2401-3431

India - Bangalore

Tel: 91-80-3090-4444

Fax: 91-80-3090-4123

Austria - Wels

Tel: 43-7242-2244-39

Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828

Fax: 45-4485-2829

Australia - Sydney

Tel: 61-2-9868-6733

Fax: 61-2-9868-6755

Atlanta

Duluth, GA

Tel: 678-957-9614

Fax: 678-957-1455

China - Beijing

Tel: 86-10-8569-7000

Fax: 86-10-8528-2104

Austin, TX

Tel: 512-257-3370

China - Chengdu

Tel: 86-28-8665-5511

Fax: 86-28-8665-7889

Boston

Westborough, MA

Tel: 774-760-0087

Fax: 774-760-0088

Chicago

Itasca, IL

Tel: 630-285-0071

Fax: 630-285-0075

Cleveland

Independence, OH

Tel: 216-447-0464

Fax: 216-447-0643

Dallas

Addison, TX

Tel: 972-818-7423

Fax: 972-818-2924

Detroit

Novi, MI

Tel: 248-848-4000

Houston, TX

Tel: 281-894-5983

Indianapolis

Noblesville, IN

Tel: 317-773-8323

Fax: 317-773-5453

Los Angeles

Mission Viejo, CA

Tel: 949-462-9523

Fax: 949-462-9608

New York, NY

Tel: 631-435-6000

San Jose, CA

Tel: 408-735-9110

Canada - Toronto

Tel: 905-673-0699

Fax: 905-673-6509

DS40001768A-page 16

China - Chongqing

Tel: 86-23-8980-9588

Fax: 86-23-8980-9500

China - Hangzhou

Tel: 86-571-8792-8115

Fax: 86-571-8792-8116

China - Hong Kong SAR

Tel: 852-2943-5100

Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460

Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355

Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533

Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829

Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8864-2200

Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300

Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252

Fax: 86-29-8833-7256

India - New Delhi

Tel: 91-11-4160-8631

Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-3019-1500

Japan - Osaka

Tel: 81-6-6152-7160

Fax: 81-6-6152-9310

Japan - Tokyo

Tel: 81-3-6880- 3770

Fax: 81-3-6880-3771

Korea - Daegu

Tel: 82-53-744-4301

Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200

Fax: 82-2-558-5932 or

82-2-558-5934

France - Paris

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Dusseldorf

Tel: 49-2129-3766400

Germany - Munich

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

Germany - Pforzheim

Tel: 49-7231-424750

Italy - Milan

Tel: 39-0331-742611

Fax: 39-0331-466781

Italy - Venice

Tel: 39-049-7625286

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857

Fax: 60-3-6201-9859

Netherlands - Drunen

Tel: 31-416-690399

Fax: 31-416-690340

Malaysia - Penang

Tel: 60-4-227-8870

Fax: 60-4-227-4068

Poland - Warsaw

Tel: 48-22-3325737

Philippines - Manila

Tel: 63-2-634-9065

Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870

Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-5778-366

Fax: 886-3-5770-955

Spain - Madrid

Tel: 34-91-708-08-90

Fax: 34-91-708-08-91

Sweden - Stockholm

Tel: 46-8-5090-4654

UK - Wokingham

Tel: 44-118-921-5800

Fax: 44-118-921-5820

Taiwan - Kaohsiung

Tel: 886-7-213-7830

Taiwan - Taipei

Tel: 886-2-2508-8600

Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351

Fax: 66-2-694-1350

China - Xiamen

Tel: 86-592-2388138

Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040

Fax: 86-756-3210049

Advance Information

03/25/14

2014 Microchip Technology Inc.

�