SST26WF016B/

SST26WF016BA

1.8V 16 Mbit Serial Quad I/O (SQI) Flash Memory

Features

• Single Voltage Read and Write Operations

- 1.65-1.95V

• Serial Interface Architecture

- Mode 0 and Mode 3

- Nibble-wide multiplexed I/O’s with SPI-like serial

command structure

- x1/x2/x4 Serial Peripheral Interface (SPI) Protocol

• High Speed Clock Frequency

- 104 MHz max

• Burst Modes

- Continuous linear burst

- 8/16/32/64 Byte linear burst with wrap-around

• Superior Reliability

- Endurance: 100,000 Cycles (min)

- Greater than 100 years Data Retention

• Low Power Consumption:

- Active Read current: 15 mA (typical @ 104 MHz)

- Standby current: 10 μA (typical)

- Deep Power-Down current: 2.5 μA (typical)

• Fast Erase Time

- Sector/Block Erase: 18 ms (typ), 25 ms (max)

- Chip Erase: 35 ms (typ), 50 ms (max)

• Page-Program

- 256 Bytes per page in x1 or x4 mode

• End-of-Write Detection

- Software polling the BUSY bit in status register

• Flexible Erase Capability

- Uniform 4 KByte sectors

- Four 8 KByte top and bottom parameter overlay

blocks

- One 32 KByte top and bottom overlay block

- Uniform 64 KByte overlay blocks

• Write-Suspend

- Suspend Program or Erase operation to access

another block/sector

• Software Reset (RST) mode

• Software Protection

- Individual-Block Write Protection with permanent

lock-down capability

- 64 KByte blocks, two 32 KByte blocks, and

eight 8 KByte parameter blocks

- Read Protection on top and bottom 8 KByte

parameter blocks

2014 Microchip Technology Inc.

• Security ID

- One-Time Programmable (OTP) 2 KByte,

Secure ID

- 64 bit unique, factory pre-programmed identifier

- User-programmable area

• Temperature Range

- Industrial: -40°C to +85°C

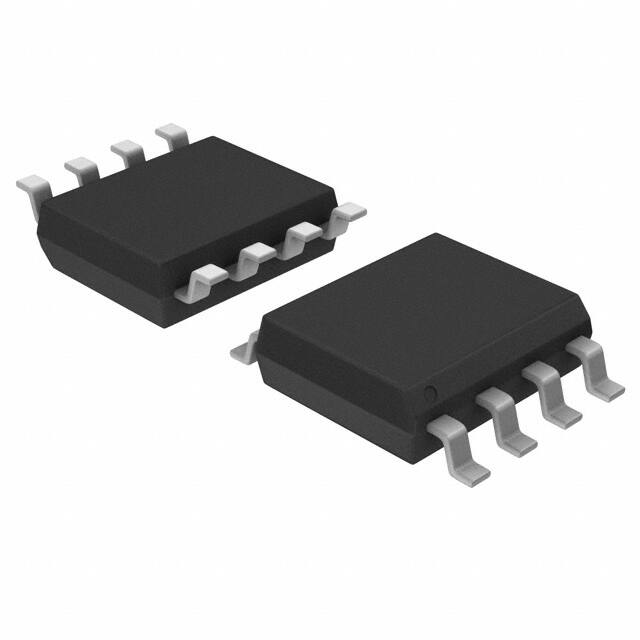

• Packages Available

- 8-contact WDFN (6mm x 5mm)

- 8-lead SOIC (150 mil)

- 8-ball Chip Scale Package (Z-Scale™)

• All devices are RoHS compliant

Product Description

The Serial Quad I/O™ (SQI™) family of flash-memory

devices features a six-wire, 4-bit I/O interface that

allows for low-power, high-performance operation in a

low pin-count package. SST26WF016B/016BA also

support full command-set compatibility to traditional

Serial Peripheral Interface (SPI) protocol. System

designs using SQI flash devices occupy less board

space and ultimately lower system costs.

All members of the 26 Series, SQI family are manufactured with SST proprietary, high-performance CMOS

SuperFlash® technology. The split-gate cell design

and thick-oxide tunneling injector attain better reliability

and manufacturability compared with alternate

approaches.

The SST26WF016B/SST26WF016BA significantly

improves performance and reliability, while lowering

power consumption. This device writes (Program or

Erase) with a single power supply of 1.65-1.95V. The

total energy consumed is a function of the applied voltage, current, and time of application. Since for any

given voltage range, the SuperFlash technology uses

less current to program and has a shorter erase time,

the total energy consumed during any Erase or Program operation is less than alternative flash memory

technologies.

SST26WF016B/016BA is offered in 8-contact WDFN

(6 mm x 5 mm), 8-lead SOIC (150 mil), and 8-ball

XFBGA (Z-Scale™) packages. See Figure 2-1 for pin

assignments.

Two configurations are available upon order:

SST26WF016B default at power-up has the WP# and

Hold# pins enabled and SST26WF016BA default at

power-up has the WP# and Hold# pins disabled.

DS20005013D-page 1

�SST26WF016B/SST26WF016BA

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via Email at docerrors@microchip.com. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The

last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of

silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are

using.

Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

DS20005013D-page 2

2014 Microchip Technology Inc.

�SST26WF016B/SST26WF016BA

1.0

BLOCK DIAGRAM

FIGURE 1-1:

FUNCTIONAL BLOCK DIAGRAM

OTP

Address

Buffers

and

Latches

X - Decoder

SuperFlash

Memory

Y - Decoder

Page Buffer,

I/O Buffers

and

Data Latches

Control Logic

Serial Interface

WP# HOLD# SCK

CE#

SIO [3:0]

1432 B1.0

2014 Microchip Technology Inc.

DS20005013D-page 3

�SST26WF016B/SST26WF016BA

2.0

PIN DESCRIPTION

FIGURE 2-1:

PIN DESCRIPTION FOR 8-LEAD SOIC, 8-CONTACT WDFN, AND 8-BALL XFBGA

CE#

1

SO/SIO1

2

8

VDD

7

HOLD/SIO3

CE#

1

SO/SIO1

2

Top View

8

VDD

7

HOLD/SIO3

Top View

WP#/SIO2

3

6

SCK

VSS

4

5

SI/SIO0

WP#/SIO2

3

6

SCK

VSS

4

5

SI/SIO0

1432 08-soic S2A P1.0

1432 08-wson QA P1.0

8-Contact WDFN

8-Lead SOIC

Top View

(Balls Facing Down)

2

CE# SO/SIO1 WP#/

SIO2

VSS

1

VDD

HOLD/

SIO3

A

B

SCK SI/SIO0

C

D

8-xfbga P1.0

8-Ball XFBGA

DS20005013D-page 4

2014 Microchip Technology Inc.

�SST26WF016B/SST26WF016BA

TABLE 2-1:

PIN DESCRIPTION

Symbol

Pin Name

Functions

SCK

Serial Clock

To provide the timing of the serial interface.

Commands, addresses, or input data are latched on the rising edge of the clock

input, while output data is shifted out on the falling edge of the clock input.

SIO[3:0]

Serial Data

Input/Output

To transfer commands, addresses, or data serially into the device or data out of

the device. Inputs are latched on the rising edge of the serial clock. Data is

shifted out on the falling edge of the serial clock. The Enable Quad I/O (EQIO)

command instruction configures these pins for Quad I/O mode.

SI

Serial Data Input

for SPI mode

To transfer commands, addresses or data serially into the device. Inputs are

latched on the rising edge of the serial clock. SI is the default state after a

power on reset.

SO

Serial Data Output

for SPI mode

To transfer data serially out of the device. Data is shifted out on the falling edge

of the serial clock. SO is the default state after a power on reset.

CE#

Chip Enable

The device is enabled by a high to low transition on CE#. CE# must remain low

for the duration of any command sequence; or in the case of Write operations,

for the command/data input sequence.

WP#

Write Protect

The WP# pin is used in conjunction with the WPEN and IOC bits in the configuration register to prohibit Write operations to the Block-Protection register. This

pin only works in SPI, single-bit and dual-bit Read mode.

HOLD#

Hold

Temporarily stops serial communication with the SPI Flash memory while the

device is selected. This pin only works in SPI, single-bit and dual-bit Read

mode. This pin must be tied high when not in use.

VDD

Power Supply

To provide power supply voltage.

VSS

Ground

2014 Microchip Technology Inc.

DS20005013D-page 5

�SST26WF016B/SST26WF016BA

3.0

MEMORY ORGANIZATION

The SST26WF016B/016BA SQI memory array is organized in uniform, 4 KByte erasable sectors with the following erasable blocks: eight 8 KByte parameter, two

32 KByte overlay, and thirty 64 KByte overlay blocks.

See Figure 3-1.

FIGURE 3-1:

MEMORY MAP

Top of Memory Block

8 KByte

8 KByte

8 KByte

8 KByte

32 KByte

...

64 KByte

2 Sectors for 8 KByte blocks

8 Sectors for 32 KByte blocks

16 Sectors for 64 KByte blocks

64 KByte

...

4 KByte

4 KByte

4 KByte

4 KByte

64 KByte

32 KByte

8 KByte

8 KByte

8 KByte

8 KByte

Bottom of Memory Block

1432 F41.0

DS20005013D-page 6

2014 Microchip Technology Inc.

�SST26WF016B/SST26WF016BA

4.0

DEVICE OPERATION

the two modes is the state of the SCK signal when the

bus master is in stand-by mode and no data is being

transferred. The SCK signal is low for Mode 0 and SCK

signal is high for Mode 3. For both modes, the Serial

Data I/O (SIO[3:0]) is sampled at the rising edge of the

SCK clock signal for input, and driven after the falling

edge of the SCK clock signal for output. The traditional

SPI protocol uses separate input (SI) and output (SO)

data signals as shown in Figure 4-1. The SQI protocol

uses four multiplexed signals, SIO[3:0], for both data in

and data out, as shown in Figure 4-2. This means the

SQI protocol quadruples the traditional bus transfer

speed at the same clock frequency, without the need

for more pins on the package.

The SST26WF016B/016BA support both Serial

Peripheral Interface (SPI) bus protocol and a 4-bit multiplexed SQI bus protocol. To provide backward compatibility to traditional SPI Serial Flash devices, the

device’s initial state after a power-on reset is SPI mode

which supports multi-I/O (x1/x2/x4) Read/Write commands. A command instruction configures the device

to SQI mode. The dataflow in the SQI mode is similar

to the SPI mode, except it uses four multiplexed I/O signals for command, address, and data sequence.

SQI Flash Memory supports both Mode 0 (0,0) and

Mode 3 (1,1) bus operations. The difference between

FIGURE 4-1:

SPI PROTOCOL (TRADITIONAL 25 SERIES SPI DEVICE)

CE#

SCK

MODE 3

MODE 3

MODE 0

MODE 0

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

SI

MSB

SO

HIGH IMPEDANCE

DON T CARE

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

MSB

FIGURE 4-2:

1432 F03.0

SQI SERIAL QUAD I/O PROTOCOL

CE#

MODE 3

MODE 3

CLK

MODE 0

SIO(3:0)

MODE 0

C1 C0

A5

A4

A3

A2

A1

A0

H0

L0

H1

L1

H2

L2

H3

L3

MSB

1432 F04.0

4.1

Device Protection

The SST26WF016B/016BA offers a flexible memory

protection scheme that allows the protection state of

each individual block to be controlled separately. In addition, the Write-Protection Lock-Down register prevents

any change of the lock status during device operation.

To avoid inadvertent writes during power-up, the device

is write-protected by default after a power-on reset cycle.

A Global Block-Protection Unlock command offers a single command cycle that unlocks the entire memory array

for faster manufacturing throughput.

For extra protection, there is an additional non-volatile

register that can permanently write-protect the BlockProtection register bits for each individual block. Each

of the corresponding lock-down bits are one time programmable (OTP)—once written, they cannot be

erased. Data that had been previously programmed

into these blocks cannot be altered by programming or

erase and is not reversible

2014 Microchip Technology Inc.

4.1.1

INDIVIDUAL BLOCK PROTECTION

The SST26WF016B/016BA has a Block-Protection

register which provides a software mechanism to writelock the individual memory blocks and write-lock, and/

or read-lock, the individual parameter blocks. The

Block-Protection register is 48 bits wide: two bits each

for the eight 8 KByte parameter blocks (write-lock and

read-lock), and one bit each for the remaining 32 KByte

and 64 KByte overlay blocks (write-lock). See Table 56 for address range protected per register bit.

Each bit in the Block-Protection register (BPR) can be

written to a ‘1’ (protected) or ‘0’ (unprotected). For the

parameter blocks, the most significant bit is for read-lock,

and the least significant bit is for write-lock. Read-locking

the parameter blocks provides additional security for sensitive data after retrieval (e.g., after initial boot). If a block

is read-locked all reads to the block return data 00H.

The Write Block-Protection Register command is a

two-cycle command which requires that Write-Enable

(WREN) is executed prior to the Write Block-Protection

DS20005013D-page 7

�SST26WF016B/SST26WF016BA

Register command. The Global Block-Protection

Unlock command clears all write protection bits in the

Block-Protection register.

4.1.2

WRITE-PROTECTION LOCKDOWN (VOLATILE)

To prevent changes to the Block-Protection register,

use the Lock-Down Block-Protection Register (LBPR)

command to enable Write-Protection Lock-Down.

Once Write-Protection Lock-Down is enabled, the

Block-Protection register can not be changed. To avoid

inadvertent lock down, the WREN command must be

executed prior to the LBPR command.

To reset Write-Protection Lock-Down, performing a

power cycle on the device is required. The Write-Protection Lock-Down status may be read from the Status register.

4.1.3

WRITE-LOCK LOCK-DOWN (NONVOLATILE)

The non-Volatile Write-Lock Lock-Down register is an

alternate register that permanently prevents changes

to the block-protect bits. The non-Volatile Write-Lock

Lock-Down register (nVWLDR) is 40 bits wide per

device: one bit each for the eight 8-KByte parameter

blocks, and one bit each for the remaining 32 KByte

and 64 KByte overlay blocks. See Table 5-6 for

address range protected per register bit.

Writing ‘1’ to any or all of the nVWLDR bits disables the

change mechanism for the corresponding Write-Lock

bit in the BPR, and permanently sets this bit to a ‘1’

(protected) state. After this change, both bits will be set

to ‘1’, regardless of the data entered in subsequent

writes to either the nVWLDR or the BPR. Subsequent

writes to the nVWLDR can only alter available locations

that have not been previously written to a ‘1’. This

method provides write-protection for the corresponding

memory-array block by protecting it from future program or erase operations.

Writing a ‘0’ in any location in the nVWLDR has no effect

TABLE 4-1:

WP#

L

L

L

L

H

H

X

X

on either the nVWLDR or the corresponding Write-Lock

bit in the BPR.

Note that if the Block-Protection register had been previously locked down, see “ Write-Protection LockDown (Volatile)”, the device must be power cycled

before using the nVWLDR. If the Block-Protection register is locked down and the Write nVWLDR command

is accessed, the command will be ignored.

4.2

Hardware Write Protection

The hardware Write Protection pin (WP#) is used in conjunction with the WPEN and IOC bits in the configuration

register to prohibit write operations to the Block-Protection and Configuration registers. The WP# pin function

only works in SPI single-bit and dual-bit read mode when

the IOC bit in the configuration register is set to ‘0’.

The WP# pin function is disabled when the WPEN bit

in the configuration register is ‘0’. This allows installation of the SST26WF016B/016BA in a system with a

grounded WP# pin while still enabling Write to the

Block-Protection register. The Lock-Down function of

the Block-Protection Register supersedes the WP# pin,

see Table 4-1 for Write Protection Lock-Down states.

The factory default setting at power-up of the WPEN bit

is ‘0’, disabling the Write Protect function of the WP#

after power-up. WPEN is a non-volatile bit; once the bit

is set to ‘1’, the Write Protect function of the WP# pin

continues to be enabled after power-up. The WP# pin

only protects the Block-Protection Register and Configuration Register from changes. Therefore, if the WP#

pin is set to low before or after a Program or Erase

command, or while an internal Write is in progress, it

will have no effect on the Write command.

The IOC bit takes priority over the WPEN bit in the configuration register. When the IOC bit is ‘1’, the function

of the WP# pin is disabled and the WPEN bit serves no

function. When the IOC bit is ‘0’ and WPEN is ‘1’, setting the WP# pin active low prohibits Write operations

to the Block Protection Register.

WRITE PROTECTION LOCK-DOWN STATES

IOC

0

0

0

01

0

0

1

13

WPEN

1

0

1

02

X

X

X

02

WPLD

1

1

0

0

1

0

1

0

Execute WBPR Instruction

Not Allowed

Not Allowed

Not Allowed

Allowed

Not Allowed

Allowed

Not Allowed

Allowed

Configuration Register

Protected

Writable

Protected

Writable

Writable

Writable

Writable

Writable

1. Default at power-up Register settings for SST26WF016B

2. Factory default setting is ‘0’. This is a non-volatile bit; default at power-up is the value set prior to power-down.

3. Default at power-up Register settings for SST26WF016BA

DS20005013D-page 8

2014 Microchip Technology Inc.

�SST26WF016B/SST26WF016BA

4.3

Security ID

SST26WF016B/016BA offers a 2 KByte Security ID

(Sec ID) feature. The Security ID space is divided into

two parts – one factory-programmed, 64-bit segment

and one user-programmable segment. The factoryprogrammed segment is programmed during manufacturing with a unique number and cannot be changed.

The user-programmable segment is left unprogrammed for the customer to program as desired.

Use the Program Security ID (PSID) command to program the Security ID using the address shown in Table

5-5. The Security ID can be locked using the Lockout

Security ID (LSID) command. This prevents any future

write operations to the Security ID.

The factory-programmed portion of the Security ID

can’t be programmed by the user; neither the factoryprogrammed nor user-programmable areas can be

erased.

4.4

Hold Operation

The HOLD# pin pauses active serial sequences without resetting the clocking sequence. This pin is active

after every power up and only operates during SPI

single-bit and dual-bit modes. Two factory configurations are available: SST26WF016B ships with the IOC

FIGURE 4-3:

bit set to ‘0’ and the HOLD# pin function enabled;

SST26WF016BA ships with the IOC bit set to ‘1’ and

the HOLD# pin function disabled. The HOLD# pin is

always disabled in SQI mode and only works in SPI single-bit and dual-bit read mode.

To activate the Hold mode, CE# must be in active low

state. The Hold mode begins when the SCK active low

state coincides with the falling edge of the HOLD# signal. The Hold mode ends when the HOLD# signal’s rising edge coincides with the SCK active low state.

If the falling edge of the HOLD# signal does not coincide with the SCK active low state, then the device

enters Hold mode when the SCK next reaches the

active low state. Similarly, if the rising edge of the

HOLD# signal does not coincide with the SCK active

low state, then the device exits Hold mode when the

SCK next reaches the active low state. See Figure 4-3.

Once the device enters Hold mode, SO will be in high

impedance state while SI and SCK can be VIL or VIH.

If CE# is driven active high during a Hold condition, it

resets the internal logic of the device. As long as

HOLD# signal is low, the memory remains in the Hold

condition. To resume communication with the device,

HOLD# must be driven active high, and CE# must be

driven active low.

HOLD CONDITION WAVEFORM.

SCK

HOLD#

Active

Hold

Active

Hold

Active

1432 F46.0

2014 Microchip Technology Inc.

DS20005013D-page 9

�SST26WF016B/SST26WF016BA

4.5

Status Register

The Status register is a read-only register that provides

the following status information: whether the flash

memory array is available for any Read or Write operation, if the device is write-enabled, whether an erase

or program operation is suspended, and if the Block-

TABLE 4-2:

Protection register and/or Security ID are locked down.

During an internal Erase or Program operation, the Status register may be read to determine the completion of

an operation in progress. Table 4-2 describes the function of each bit in the Status register.

STATUS REGISTER

Default at

Power-up

Read/Write (R/

W)

Write operation status

1 = Internal Write operation is in progress

0 = No internal Write operation is in progress

0

R

WEL

Write-Enable Latch status

1 = Device is write-enabled

0 = Device is not write-enabled

0

R

2

WSE

Write Suspend-Erase status

1 = Erase suspended

0 = Erase is not suspended

0

R

3

WSP

Write Suspend-Program status

1 = Program suspended

0 = Program is not suspended

0

R

4

WPLD

Write Protection Lock-Down status

1 = Write Protection Lock-Down enabled

0 = Write Protection Lock-Down disabled

0

R

5

SEC1

Security ID status

1 = Security ID space locked

0 = Security ID space not locked

01

R

Bit

Name

Function

0

BUSY

1

6

RES

Reserved for future use

0

R

7

BUSY

Write operation status

1 = Internal Write operation is in progress

0 = No internal Write operation is in progress

0

R

1. The Security ID status will always be ‘1’ at power-up after a successful execution of the Lockout Security ID instruction,

otherwise default at power-up is ‘0’.

4.5.1

WRITE-ENABLE LATCH (WEL)

The Write-Enable Latch (WEL) bit indicates the status

of the internal memory’s Write-Enable Latch. If the

WEL bit is set to ‘1’, the device is write enabled. If the

bit is set to ‘0’ (reset), the device is not write enabled

and does not accept any memory Program or Erase,

Protection Register Write, or Lock-Down commands.

The Write-Enable Latch bit is automatically reset under

the following conditions:

•

•

•

•

•

•

•

•

•

Power-up

Reset

Write-Disable (WRDI) instruction

Page-Program instruction completion

Sector-Erase instruction completion

Block-Erase instruction completion

Chip-Erase instruction completion

Write-Block-Protection register instruction

Lock-Down Block-Protection register instruction

DS20005013D-page 10

•

•

•

•

•

Program Security ID instruction completion

Lockout Security ID instruction completion

Write-Suspend instruction

SPI Quad Page Program

Write Status Register

4.5.2

WRITE SUSPEND ERASE STATUS

(WSE)

The Write Suspend-Erase status (WSE) indicates

when an Erase operation has been suspended. The

WSE bit is ‘1’ after the host issues a suspend command

during an Erase operation. Once the suspended Erase

resumes, the WSE bit is reset to ‘0’.

2014 Microchip Technology Inc.

�SST26WF016B/SST26WF016BA

4.5.3

WRITE SUSPEND PROGRAM

STATUS (WSP)

The Write Suspend-Program status (WSP) bit indicates when a Program operation has been suspended.

The WSP is ‘1’ after the host issues a suspend command during the Program operation. Once the suspended Program resumes, the WSP bit is reset to ‘0’.

4.5.4

WRITE PROTECTION LOCK-DOWN

STATUS (WPLD)

The Write Protection Lock-Down status (WPLD) bit

indicates when the Block-Protection register is lockeddown to prevent changes to the protection settings.

The WPLD is ‘1’ after the host issues a Lock-Down

Block-Protection command. After a power cycle, the

WPLD bit is reset to ‘0’.

4.5.5

SECURITY ID STATUS (SEC)

The Security ID Status (SEC) bit indicates when the

Security ID space is locked to prevent a Write command. The SEC is ‘1’ after the host issues a Lockout

SID command. Once the host issues a Lockout SID

command, the SEC bit can never be reset to ‘0.’

4.5.6

BUSY

The Busy bit determines whether there is an internal

Erase or Program operation in progress. If the BUSY

bit is ‘1’, the device is busy with an internal Erase or

Program operation. If the bit is ‘0’, no Erase or Program

operation is in progress.

2014 Microchip Technology Inc.

DS20005013D-page 11

�SST26WF016B/SST26WF016BA

4.6

Configuration Register

The Configuration register is a Read/Write register that

stores a variety of configuration information. See Table

4-3 for the function of each bit in the register.

TABLE 4-3:

Bit

0

CONFIGURATION REGISTER

Name

Function

Default at Power-up

Read/Write (R/W)

RES

Reserved

0

R

I/O Configuration for SPI Mode

1 = WP# and HOLD# pins disabled

0 = WP# and HOLD# pins enabled

01

R/W

IOC

1

2

RES

Reserved

0

R

BPNV

Block-Protection Volatility State

1 = No memory block has been permanently locked

0 = Any block has been permanently locked

1

R

3

4

RES

Reserved

0

R

5

RES

Reserved

0

R

6

RES

Reserved

0

R

WPEN

Write-Protection Pin (WP#) Enable

1 = WP# enabled

0 = WP# disabled

02

R/W

7

1. SST26WF016B default at Power-up is ‘0’

SST26WF016BA default at Power-up is ‘1’

2. Factory default setting. This is a non-volatile bit; default at power-up will be the setting prior to power-down.

4.6.1

I/O CONFIGURATION (IOC)

The I/O Configuration (IOC) bit re-configures the I/O

pins. The IOC bit is set by writing a ‘1’ to Bit 1 of the

Configuration register. When IOC bit is ‘0’ the WP# pin

and HOLD# pin are enabled (SPI or Dual Configuration

setup). When IOC bit is set to ‘1’ the SIO2 pin and SIO3

pin are enabled (SPI Quad I/O Configuration setup).

The IOC bit must be set to ‘1’ before issuing the following SPI commands: SQOR (6BH), SQIOR (EBH),

RBSPI (ECH), and SPI Quad page program (32H).

Without setting the IOC bit to ‘1’, those SPI commands

are not valid. The I/O configuration bit does not apply

when in SQI mode. The default at power-up for

SST26WF016B is ‘0’ and for SST26WF016BA is ‘1’.

4.6.2

BLOCK-PROTECTION VOLATILITY

STATE (BPNV)

4.6.3

WRITE-PROTECT ENABLE (WPEN)

The Write-Protect Enable (WPEN) bit is a non-volatile

bit that enables the WP# pin.

The Write-Protect (WP#) pin and the Write-Protect

Enable (WPEN) bit control the programmable hardware write-protect feature. Setting the WP# pin to low,

and the WPEN bit to ‘1’, enables Hardware write-protection. To disable Hardware write protection, set either

the WP# pin to high or the WPEN bit to ‘0’. There is

latency associated with writing to the WPEN bit. Poll

the BUSY bit in the Status register, or wait TWPEN, for

the completion of the internal, self-timed Write operation. When the chip is hardware write protected, only

Write operations to Block-Protection and Configuration

registers are disabled. See “Hardware Write Protection” on page 8 and Table 4-1 for more information

about the functionality of the WPEN bit.

The Block-Protection Volatility State bit indicates

whether any block has been permanently locked with

the non-Volatile Write-Lock Lock-Down register

(nVWLDR). When no bits in the nVWLDR have been

set (the default state from the factory) the BPNV bit is

`1'; when one or more bits in the nVWLDR are set to `1'

the BPNV bit will also be `0' from that point forward,

even after power-up.

DS20005013D-page 12

2014 Microchip Technology Inc.

�SST26WF016B/SST26WF016BA

5.0

INSTRUCTIONS

Instructions are used to read, write (erase and program), and configure the SST26WF016B/016BA. The

complete list of the instructions is provided in Table 5-1.

TABLE 5-1:

Instruction

DEVICE OPERATION INSTRUCTIONS FOR SST26WF016B/016BA (1 OF 2)

Description

Mode

Command

Cycle1

SPI

SQI

Address

Cycle(s)2, 3

Dummy

Cycle(s)3

Data

Cycle(s)3

Max

Freq

00H

X

X

0

0

0

104

MHz

Configuration

NOP

No Operation

RSTEN

Reset Enable

66H

X

X

0

0

0

RST4

Reset Memory

99H

X

X

0

0

0

EQIO

Enable Quad I/O

38H

X

RSTQIO5

Reset Quad I/O

FFH

X

RDSR

Read Status Register

05H

X

WRSR

Write Status Register

01H

X

RDCR

Read Configuration

Register

35H

X

Read

Read Memory

03H

High-Speed

Read

Read Memory at

Higher Speed

0BH

SQOR6

SPI Quad Output Read

SQIOR7

SPI Quad I/O Read

0

0

0

X

0

0

0

0

0

1 to

X

0

1

1 to

X

0

0

2

0

0

1 to

0

1

1 to

3

0

1 to

40 MHz

104

MHz

X

Read

8

X

3

3

1 to

X

3

1

1 to

6BH

X

3

1

1 to

EBH

X

3

3

1 to

X

SPI Dual Output Read

3BH

X

3

1

1 to

SDIOR9

SPI Dual I/O Read

BBH

X

3

1

1 to

80 MHz

SB

Set Burst Length

C0H

X

X

0

0

1

RBSQI

SQI nB Burst with

Wrap

0CH

X

3

3

n to

104

MHz

RBSPI7

SPI nB Burst with

Wrap

ECH

X

3

3

n to

JEDEC-ID Read

9FH

X

0

0

3 to

Quad J-ID

Quad I/O J-ID Read

AFH

SFDP

Serial Flash Discoverable Parameters

5AH

X

Write Enable

06H

X

SDOR

Identification

JEDEC-ID

X

0

1

3 to

3

1

1 to

0

0

0

104

MHz

Write

WREN

X

WRDI

Write Disable

04H

X

X

0

0

0

SE10

Erase 4 KBytes of

Memory Array

20H

X

X

3

0

0

BE11

Erase 64, 32 or 8

KBytes of Memory

Array

D8H

X

X

3

0

0

CE

Erase Full Array

C7H

X

X

0

0

0

PP

Page Program

02H

X

X

3

0

1 to 256

2014 Microchip Technology Inc.

104

MHz

DS20005013D-page 13

�SST26WF016B/SST26WF016BA

TABLE 5-1:

DEVICE OPERATION INSTRUCTIONS FOR SST26WF016B/016BA (CONTINUED) (2

Mode

Command

Cycle1

SPI

Instruction

Description

SPI Quad

PP6

SQI Quad Page

Program

32H

X

WRSU

Suspends Program/

Erase

B0H

X

WRRE

Resumes Program/

Erase

30H

X

Read Block-Protection

Register

72H

X

WBPR

Write Block-Protection

Register

42H

LBPR

Lock Down BlockProtection Register

nVWLDR

Address

Cycle(s)2, 3

Dummy

Cycle(s)3

Data

Cycle(s)3

Max

Freq

3

0

1 to 256

104

MHz

X

0

0

0

X

0

0

0

SQI

Protection

RBPR

0

0

1 to6

X

0

1

1 to6

X

X

0

0

1 to 6

8DH

X

X

0

0

0

non-Volatile Write

Lock-Down Register

E8H

X

X

0

0

1 to 6

ULBPR

Global Block Protection Unlock

98H

X

X

0

0

0

RSID

Read Security ID

88H

X

2

1

1 to 2048

X

2

3

1 to 2048

PSID

Program User

Security ID area

A5H

X

X

2

0

1 to 256

LSID

Lockout Security ID

Programming

85H

X

X

0

0

0

104

MHz

Power Saving

DPD

Deep Power-down Mode

B9H

X

X

0

0

0

RDPD

Release from Deep

Power-down and Read

ID

ABH

X

X

3

0

1 to

104

MHz

0

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

Command cycle is two clock periods in SQI mode and eight clock periods in SPI mode.

Address bits above the most significant bit of each density can be VIL or VIH.

Address, Dummy/Mode bits, and Data cycles are two clock periods in SQI and eight clock periods in SPI mode.

RST command only executed if RSTEN command is executed first. Any intervening command will disable Reset.

Device accepts eight-clock command in SPI mode, or two-clock command in SQI mode.

Data cycles are two clock periods. IOC bit must be set to ‘1’ before issuing the command.

Address, Dummy/Mode bits, and data cycles are two clock periods. IOC bit must be set to ‘1’ before issuing the command.

Data cycles are four clock periods.

Address, Dummy/Mode bits, and Data cycles are four clock periods.

Sector Addresses: Use AMS - A12, remaining address are don’t care, but must be set to VIL or VIH.

Blocks are 64 KByte, 32 KByte, or 8KByte, depending on location. Block Erase Address: AMS - A16 for 64 KByte; AMS - A15

for 32 KByte; AMS - A13 for 8 KByte. Remaining addresses are don’t care, but must be set to VIL or VIH.

DS20005013D-page 14

2014 Microchip Technology Inc.

�SST26WF016B/SST26WF016BA

5.1

No Operation (NOP)

The Reset operation requires the Reset-Enable command followed by the Reset command. Any command

other than the Reset command after the Reset-Enable

command will disable the Reset-Enable.

The No Operation command only cancels a Reset

Enable command. NOP has no impact on any other

command.

5.2

Once the Reset-Enable and Reset commands are successfully executed, the device returns to normal operation Read mode and then does the following: resets the

protocol to SPI mode, resets the burst length to 8

Bytes, clears all the bits, except for bit 4 (WPLD) and

bit 5 (SEC), in the Status register to their default states,

and clears bit 1 (IOC) in the configuration register to its

default state. A device reset during an active Program

or Erase operation aborts the operation, which can

cause the data of the targeted address range to be corrupted or lost. Depending on the prior operation, the

reset timing may vary. Recovery from a Write operation

requires more latency time than recovery from other

operations. See Table 8-2 on page 46 for Rest timing

parameters.

Reset-Enable (RSTEN) and Reset

(RST)

The Reset operation is used as a system (software)

reset that puts the device in normal operating Ready

mode. This operation consists of two commands:

Reset-Enable (RSTEN) followed by Reset (RST).

To reset the SST26WF016B/016BA, the host drives

CE# low, sends the Reset-Enable command (66H),

and drives CE# high. Next, the host drives CE# low

again, sends the Reset command (99H), and drives

CE# high, see Figure 5-1.

FIGURE 5-1:

RESET SEQUENCE

TCPH

CE#

MODE 3

MODE 3

MODE 3

MODE 0

MODE 0

MODE 0

CLK

SIO(3:0)

C1 C0

C3 C2

1432 F05.0

Note: C[1:0] = 66H; C[3:2] = 99H

5.3

Read (40 MHz)

will automatically increment until the highest memory

address is reached. Once the highest memory address

is reached, the address pointer will automatically return

to the beginning (wrap-around) of the address space.

The Read instruction, 03H, is supported in SPI bus protocol only with clock frequencies up to 40 MHz. This

command is not supported in SQI bus protocol. The

device outputs the data starting from the specified

address location, then continuously streams the data

output through all addresses until terminated by a lowto-high transition on CE#. The internal address pointer

FIGURE 5-2:

Initiate the Read instruction by executing an 8-bit command, 03H, followed by address bits A[23:0]. CE# must

remain active low for the duration of the Read cycle.

See Figure 5-2 for Read Sequence.

READ SEQUENCE (SPI)

CE#

MODE 3

SCK

0 1 2 3 4 5 6 7 8

15 16

23 24

31 32

39 40

47 48

55 56

63 64

70

MODE 0

03

SI

MSB

SO

ADD.

MSB

HIGH IMPEDANCE

ADD.

ADD.

N

DOUT

MSB

2014 Microchip Technology Inc.

N+1

DOUT

N+2

DOUT

N+3

DOUT

N+4

DOUT

1432 F29.0

DS20005013D-page 15

�SST26WF016B/SST26WF016BA

5.4

Enable Quad I/O (EQIO)

expected to be 4-bit multiplexed input/output (SQI

mode) until a power cycle or a “Reset Quad I/O instruction” is executed. See Figure 5-3.

The Enable Quad I/O (EQIO) instruction, 38H, enables

the flash device for SQI bus operation. Upon completion of the instruction, all instructions thereafter are

FIGURE 5-3:

ENABLE QUAD I/O SEQUENCE

CE#

MODE 3

SCK

0

2

1

3

4

5

6

7

MODE 0

SIO0

38

SIO[3:1]

1432 F43.0

Note: SIO[3:1] must be driven VIH

5.5

Reset Quad I/O (RSTQIO)

where it can accept new SQI command instruction. An

additional RSTQIO is required to reset the device to

SPI mode.

The Reset Quad I/O instruction, FFH, resets the device

to 1-bit SPI protocol operation or exits the Set Mode

configuration during a read sequence. This command

allows the flash device to return to the default I/O state

(SPI) without a power cycle, and executes in either 1bit or 4-bit mode. If the device is in the Set Mode configuration, while in SQI High-Speed Read mode, the

RSTQIO command will only return the device to a state

FIGURE 5-4:

To execute a Reset Quad I/O operation, the host

drives CE# low, sends the Reset Quad I/O command

cycle (FFH) then, drives CE# high. Execute the instruction in either SPI (8 clocks) or SQI (2 clocks) command

cycles. For SPI, SIO[3:1] are don’t care for this command, but should be driven to VIH or VIL. See Figures

5-4 and 5-5.

RESET QUAD I/O SEQUENCE (SPI)

CE#

MODE 3

SCK

0

1

2

3

4

5

6

7

MODE 0

FF

SIO0

SIO[3:1]

25119 F73.0

Note: SIO[3:1] must be driven VIH

FIGURE 5-5:

RESET QUAD I/O SEQUENCE (SQI)

CE#

MODE 3

SCK

SIO(3:0)

0

1

F

F

MODE 0

25119 F74.0

DS20005013D-page 16

2014 Microchip Technology Inc.

�SST26WF016B/SST26WF016BA

5.6

High-Speed Read (104 MHz)

Initiate High-Speed Read by executing an 8-bit command, 0BH, followed by address bits A[23-0] and a

dummy byte. CE# must remain active low for the duration of the High-Speed Read cycle. See Figure 5-6 for

the High-Speed Read sequence for SPI bus protocol.

The High-Speed Read instruction, 0BH, is supported in

both SPI bus protocol and SQI protocol. On power-up,

the device is set to use SPI.

FIGURE 5-6:

HIGH-SPEED READ SEQUENCE (SPI) (C[1:0] = 0BH)

CE#

MODE 3

0 1 2 3 4 5 6 7 8

15 16

23 24

31 32

39 40

47 48

55 56

63 64

80

71 72

SCK MODE 0

ADD.

0B

SI/SIO0

ADD.

ADD.

X

N

DOUT

MSB

HIGH IMPEDANCE

SO/SIO1

N+1

DOUT

N+2

DOUT

N+3

DOUT

N+4

DOUT

1432 F31.0

mand, 0BH, and does not require the op-code to be

entered again. The host may initiate the next Read

cycle by driving CE# low, then sending the four-bits

input for address A[23:0], followed by the Set Mode

configuration bits M[7:0], and two dummy cycles. After

the two dummy cycles, the device outputs the data

starting from the specified address location. There are

no restrictions on address location access.

In SQI protocol, the host drives CE# low then send the

Read command cycle command, 0BH, followed by

three address cycles, a Set Mode Configuration cycle,

and two dummy cycles. Each cycle is two nibbles

(clocks) long, most significant nibble first.

After the dummy cycles, the device outputs data on the

falling edge of the SCK signal starting from the specified address location. The device continually streams

data output through all addresses until terminated by a

low-to-high transition on CE#. The internal address

pointer automatically increments until the highest

memory address is reached, at which point the address

pointer returns to address location 000000H. During

this operation, blocks that are Read-locked will output

data 00H.

When M[7:0] is any value other than AXH, the device

expects the next instruction initiated to be a command

instruction. To reset/exit the Set Mode configuration,

execute the Reset Quad I/O command, FFH. While in

the Set Mode configuration, the RSTQIO command will

only return the device to a state where it can accept

new SQI command instruction. An additional RSTQIO

is required to reset the device to SPI mode. See Figure

5-10 for the SPI Quad I/O Mode Read sequence when

M[7:0] = AXH.

The Set Mode Configuration bit M[7:0] indicates if the

next instruction cycle is another SQI High-Speed Read

command. When M[7:0] = AXH, the device expects the

next continuous instruction to be another Read com-

FIGURE 5-7:

HIGH-SPEED READ SEQUENCE (SQI)

CE#

0

1

MODE 0 MSN

LSN

C0

C1

MODE 3

2

3

4

5

6

7

8

9

A5

A4

A3

A2

A1

A0

M1

M0

10

11

12

13

14

15

20

21

SCK

SIO(3:0)

Command

Address

Mode

Note: MSN= Most Significant Nibble, LSN = Least Significant Nibble

Hx = High Data Nibble, Lx = Low Data Nibble C[1:0] = 0BH

2014 Microchip Technology Inc.

X

X

X

Dummy

X

H0

L0

Data Byte 0

H8

L8

Data Byte 7

1432 F47.0

DS20005013D-page 17

�SST26WF016B/SST26WF016BA

5.7

SPI Quad-Output Read

Following the dummy byte, the device outputs data

from SIO[3:0] starting from the specified address location. The device continually streams data output

through all addresses until terminated by a low-to-high

transition on CE#. The internal address pointer automatically increments until the highest memory address

is reached, at which point the address pointer returns

to the beginning of the address space.

The SPI Quad-Output Read instruction supports up to

104 MHz frequency. SST26WF016B requires the IOC

bit in the configuration register to be set to ‘1’ prior to

executing the command. Initiate SPI Quad-Output

Read by executing an 8-bit command, 6BH, followed

by address bits A[23-0] and a dummy byte. CE# must

remain active low for the duration of the SPI Quad

Mode Read. See Figure 5-8 for the SPI Quad Output

Read sequence.

FIGURE 5-8:

SPI QUAD OUTPUT READ

CE#

MODE 3

SCK

0 1 2 3 4 5 6 7 8

15 16

23 24

31 32

39 40 41

MODE 0

SIO0

6BH

OP Code

A[23:16]

A[15:8]

Address

A[7:0]

X

b4 b0

b4 b0

Dummy

Data

Byte 0

Data

Byte N

SIO1

b5 b1

b5 b1

SIO2

b6 b2

b6 b2

SIO3

b7 b3

b7 b3

Note: MSN= Most Significant Nibble, LSN = Least Significant Nibble

DS20005013D-page 18

1432 F48.3

2014 Microchip Technology Inc.

�SST26WF016B/SST26WF016BA

5.8

SPI Quad I/O Read

The Set Mode Configuration bit M[7:0] indicates if the

next instruction cycle is another SPI Quad I/O Read

command. When M[7:0] = AXH, the device expects the

next continuous instruction to be another Read command, EBH, and does not require the op-code to be

entered again. The host may set the next SQIOR cycle

by driving CE# low, then sending the four-bit wide input

for address A[23:0], followed by the Set Mode configuration bits M[7:0], and two dummy cycles. After the two

dummy cycles, the device outputs the data starting

from the specified address location. There are no

restrictions on address location access.

The SPI Quad I/O Read (SQIOR) instruction supports

up to 104 MHz frequency. SST26WF016B requires the

IOC bit in the configuration register to be set to ‘1’ prior

to executing the command. Initiate SQIOR by executing an 8-bit command, EBH. The device then switches

to 4-bit I/O mode for address bits A[23-0], followed by

the Set Mode configuration bits M[7:0], and two dummy

bytes.CE# must remain active low for the duration of

the SPI Quad I/O Read. See Figure 5-9 for the SPI

Quad I/O Read sequence.

Following the dummy bytes, the device outputs data

from the specified address location. The device continually streams data output through all addresses until

terminated by a low-to-high transition on CE#. The

internal address pointer automatically increments until

the highest memory address is reached, at which point

the address pointer returns to the beginning of the

address space.

FIGURE 5-9:

When M[7:0] is any value other than AXH, the device

expects the next instruction initiated to be a command

instruction. To reset/exit the Set Mode configuration,

execute the Reset Quad I/O command, FFH. See Figure 5-10 for the SPI Quad I/O Mode Read sequence

when M[7:0] = AXH.

SPI QUAD I/O READ SEQUENCE

CE#

MODE 3

SCK

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

MODE 0

SIO0

EBH

A20 A16 A12 A8 A4 A0 M4 M0 X X X X b4 b0 b4 b0

SIO1

A21 A17 A13 A9 A5 A1 M5 M1 X X X X b5 b1 b5 b1

SIO2

A22 A18 A14 A10 A6 A2 M6 M2 X X X X b6 b2 b6 b2

SIO3

A23 A19 A15 A11 A7 A3 M7 M3 X X X X b7 b3 b7 b3

MSN LSN

Address

Note: MSN= Most Significant Nibble, LSN = Least Significant Nibble

2014 Microchip Technology Inc.

Set

Mode

Dummy

Data Data

Byte 0 Byte 1

1432 F49.2

DS20005013D-page 19

�SST26WF016B/SST26WF016BA

FIGURE 5-10:

BACK-TO-BACK SPI QUAD I/O READ SEQUENCES WHEN M[7:0] = AXH

CE#

0 1 2 3 4 5 6 7 8 9 10 11 12 13

SCK

SIO0

b4 b0 b4 b0

A20 A16 A12 A8 A4 A0 M4 M0 X X X X b4 b0

SIO1

b5 b1 b5 b1

A21 A17 A13 A9 A5 A1 M5 M1 X X X X b5 b1

SIO2

b6 b2 b6 b2

A22 A18 A14 A10 A6 A2 M6 M2 X X X X b6 b2

MSN LSN

SIO3

b7 b3 b7 b3

A23 A19 A15 A11 A7 A3 M7 M3 X X X X b7 b3

Data Data

Byte Byte

N+1

N

Set

Mode

Address

Dummy

Data

Byte 0

1432 F50.2

Note: MSN= Most Significant Nibble, LSN = Least Significant Nibble

5.9

Set Burst

sends the Set Burst command cycle (C0H) and one

data cycle, then drives CE# high. After power-up or

reset, the burst length is set to eight Bytes (00H). See

Table 5-2 for burst length data and Figures 5-11 and 512 for the sequences.

The Set Burst command specifies the number of bytes

to be output during a Read Burst command before the

device wraps around. It supports both SPI and SQI protocols. To set the burst length the host drives CE# low,

TABLE 5-2:

BURST LENGTH DATA

Burst Length

High Nibble (H0)

Low Nibble (L0)

8 Bytes

0h

0h

16 Bytes

0h

1h

32 Bytes

0h

2h

64 Bytes

0h

3h

FIGURE 5-11:

SET BURST LENGTH SEQUENCE (SQI)

CE#

MODE 3

SCK

SIO(3:0)

0

1

2

3

MODE 0

C1 C0 H0 L0

MSN LSN

1432 F32.0

Note: MSN = Most Significant Nibble, LSN = Least Significant Nibble, C[1:0] = C0H

DS20005013D-page 20

2014 Microchip Technology Inc.

�SST26WF016B/SST26WF016BA

FIGURE 5-12:

SET BURST LENGTH SEQUENCE (SPI)

CE#

MODE 3

SCK

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

MODE 0

C0

SIO0

DIN

SIO[3:1]

1432 F51.0

Note: SIO[3:1] must be driven VIH.

5.10

SQI Read Burst with Wrap (RBSQI)

SQI Read Burst with wrap is similar to High Speed

Read in SQI mode, except data will output continuously

within the burst length until a low-to-high transition on

CE#. To execute a SQI Read Burst operation, drive

CE# low then send the Read Burst command cycle

(0CH), followed by three address cycles, and then

three dummy cycles. Each cycle is two nibbles (clocks)

long, most significant nibble first.

After the dummy cycles, the device outputs data on the

falling edge of the SCK signal starting from the specified address location. The data output stream is continuous through all addresses until terminated by a low-tohigh transition on CE#.

During RBSQI, the internal address pointer automatically increments until the last byte of the burst is

reached, then it wraps around to the first byte of the

burst. All bursts are aligned to addresses within the

burst length, see Table 5-3. For example, if the burst

length is eight Bytes, and the start address is 06h, the

burst sequence would be: 06h, 07h, 00h, 01h, 02h,

03h, 04h, 05h, 06h, etc. The pattern repeats until the

command is terminated by a low-to-high transition on

CE#.

During this operation, blocks that are Read-locked will

output data 00H.

TABLE 5-3:

5.11

SPI Read Burst with Wrap (RBSPI)

SPI Read Burst with Wrap (RBSPI) is similar to SPI

Quad I/O Read except the data will output continuously

within the burst length until a low-to-high transition on

CE#. To execute a SPI Read Burst with Wrap operation, drive CE# low, then send the Read Burst command cycle (ECH), followed by three address cycles,

and then three dummy cycles.

After the dummy cycle, the device outputs data on the

falling edge of the SCK signal starting from the specified address location. The data output stream is continuous through all addresses until terminated by a low-tohigh transition on CE#.

During RBSPI, the internal address pointer automatically increments until the last byte of the burst is

reached, then it wraps around to the first byte of the

burst. All bursts are aligned to addresses within the

burst length, see Table 5-3. For example, if the burst

length is eight Bytes, and the start address is 06h, the

burst sequence would be: 06h, 07h, 00h, 01h, 02h,

03h, 04h, 05h, 06h, etc. The pattern repeats until the

command is terminated by a low-to-high transition on

CE#.

During this operation, blocks that are Read-locked will

output data 00H.

BURST ADDRESS RANGES

Burst Length

Burst Address Ranges

8 Bytes

00-07H, 08-0FH, 10-17H, 18-1FH...

16 Bytes

00-0FH, 10-1FH, 20-2FH, 30-3FH...

32 Bytes

00-1FH, 20-3FH, 40-5FH, 60-7FH...

64 Bytes

00-3FH, 40-7FH, 80-BFH, C0-FFH

2014 Microchip Technology Inc.

DS20005013D-page 21

�SST26WF016B/SST26WF016BA

5.12

SPI Dual-Output Read

Following the dummy byte, the SST26WF016B/

SST26WF016BA outputs data from SIO[1:0] starting

from the specified address location. The device continually streams data output through all addresses until

terminated by a low-to-high transition on CE#. The

internal address pointer automatically increments until

the highest memory address is reached, at which point

the address pointer returns to the beginning of the

address space.

The SPI Dual-Output Read instruction supports up to

104 MHz frequency. Initiate SPI Dual-Output Read by

executing an 8-bit command, 3BH, followed by address

bits A[23-0] and a dummy byte. CE# must remain

active low for the duration of the SPI Dual-Output Read

operation. See Figure 5-13 for the SPI Quad Output

Read sequence.

FIGURE 5-13:

FAST READ, DUAL-OUTPUT SEQUENCE

CE#

MODE 3

SCK

0 1 2 3 4 5 6 7 8

15 16

23 24

SIO0

3BH

A[23:16]

A[15:8]

SIO1

OP Code

Note: MSB = Most Significant Bit.

5.13

39 40 41

31 32

MODE 0

SPI Dual I/O Read

The SPI Dual I/O Read (SDIOR) instruction supports

up to 80 MHz frequency. Initiate SDIOR by executing

an 8-bit command, BBH. The device then switches to

2-bit I/O mode for address bits A[23-0], followed by the

Set Mode configuration bits M[7:0]. CE# must remain

active low for the duration of the SPI Dual I/O Read.

See Figure 5-14 for the SPI Dual I/O Read sequence.

Address

A[7:0]

b6 b5 b3 b1

b6 b5 b3 b1

MSB

b7 b4 b2 b0

b7 b4 b2 b0

X

Dummy

Data

Byte 0

Data

Byte N

1432 F52.3

execute the Reset Quad I/O command, FFH. See Figure 5-15 for the SPI Dual I/O Read sequence when

M[7:0] = AXH.

Following the Set Mode configuration bits, the

SST26WF016B/SST26WF016BA outputs data from

the specified address location. The device continually

streams data output through all addresses until terminated by a low-to-high transition on CE#. The internal

address pointer automatically increments until the

highest memory address is reached, at which point the

address pointer returns to the beginning of the address

space.

The Set Mode Configuration bit M[7:0] indicates if the

next instruction cycle is another SPI Dual I/O Read

command. When M[7:0] = AXH, the device expects the

next continuous instruction to be another SDIOR command, BBH, and does not require the op-code to be

entered again. The host may set the next SDIOR cycle

by driving CE# low, then sending the two-bit wide input

for address A[23:0], followed by the Set Mode configuration bits M[7:0]. After the Set Mode configuration bits,

the device outputs the data starting from the specified

address location. There are no restrictions on address

location access.

When M[7:0] is any value other than AXH, the device

expects the next instruction initiated to be a command

instruction. To reset/exit the Set Mode configuration,

DS20005013D-page 22

2014 Microchip Technology Inc.

�SST26WF016B/SST26WF016BA

FIGURE 5-14:

SPI DUAL I/O READ SEQUENCE

CE#

MODE 3

SCK

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

MODE 0

SIO0

6 4 2 0 6 4 2 0 6 4 2 0 6 4

BBH

SIO1

7 5 3 1 7 5 3 1 7 5 3 1 7 5

A[23:16]

A[7:0]

A[15:8]

M[7:0]

CE#(cont’)

23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39

SCK(cont’)

I/O Switches from Input to Output

SIO0(cont’)

6 4 2 0 6 4 2 0 6 4 2 0 6 4 2 0 6

MSB

SIO1(cont’)

MSB

MSB

MSB

7 5 3 1 7 5 3 1 7 5 3 1 7 5 3 1 7

Byte 0

Byte 2

Byte 1

Byte 3

1432 F53.1

Note: MSN= Most Significant Nibble, LSN = Least Significant Nibble

FIGURE 5-15:

BACK-TO-BACK SPI DUAL I/O READ SEQUENCES WHEN M[7:0] = AXH

CE#

MODE 3

0 1 2

3 4 5 6 7 8 9 10 11 12 13 14 15

MODE 0

SCK

I/O Switch

SIO0 6 4

MSB

SIO1 7 5

6 4 2 0 6 4 2 0 6 4 2 0 6 4

6 4 2 0

MSB

7 5 3 1 7 5 3 1 7 5 3 1 7 5

7 5 3 1

A[23:16]

A[15:8]

A[7:0]

M[7:0]

CE#(cont’)

15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

SCK(cont’)

I/O Switches from Input to Output

SIO0(cont’)

6 4 2 0 6 4 2 0 6 4 2 0 6 4 2 0 6

MSB

SIO1(cont’)

MSB

MSB

MSB

7 5 3 1 7 5 3 1 7 5 3 1 7 5 3 1 7

Byte 0

Byte 1

Byte 2

Byte 3

1432 F54.1

Note: MSN= Most Significant Nibble, LSN = Least Significant Nibble

2014 Microchip Technology Inc.

DS20005013D-page 23

�SST26WF016B/SST26WF016BA

5.14

JEDEC-ID Read (SPI Protocol)

Immediately

following

the

command

cycle,

SST26WF016B/016BA outputs data on the falling

edge of the SCK signal. The data output stream is continuous until terminated by a low-to-high transition on

CE#. The device outputs three bytes of data: manufacturer, device type, and device ID, see Table 5-4. See

Figure 5-16 for instruction sequence.

Using traditional SPI protocol, the JEDEC-ID Read

instruction identifies the device as SST26WF016B/

016BA and the manufacturer as SST. To execute a

JECEC-ID operation the host drives CE# low then

sends the JEDEC-ID command cycle (9FH).

TABLE 5-4:

DEVICE ID DATA OUTPUT

Device ID

Product

Manufacturer ID (Byte 1)

Device Type (Byte 2)

Device ID (Byte 3)

SST26WF016B/

SST26WF016BA

BFH

26H

51H

FIGURE 5-16:

JEDEC-ID SEQUENCE (SPI MODE)

CE#

MODE 3

SCK

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34

MODE 0

SI

SO

9F

HIGH IMPEDANCE

26

BF

MSB

Device ID

MSB

1432 F38.0

5.15

Read Quad J-ID Read (SQI

Protocol)

Immediately following the command cycle, and one

dummy cycle, SST26WF016B/016BA outputs data on

the falling edge of the SCK signal. The data output

stream is continuous until terminated by a low-to-high

transition of CE#. The device outputs three bytes of

data: manufacturer, device type, and device ID, see

Table 5-4. See Figure 5-17 for instruction sequence.

The Read Quad J-ID Read instruction identifies the

device as SST26WF016B/016BA and manufacturer as

SST. To execute a Quad J-ID operation the host drives

CE# low and then sends the Quad J-ID command cycle

(AFH). Each cycle is two nibbles (clocks) long, most

significant nibble first.

FIGURE 5-17:

QUAD J-ID READ SEQUENCE

CE#

MODE 3

0

1

2

C0

C1

X

3

4

5

MSN

LSN

H0

L0

6

7

8

9

H2

L2

10

11

12

13

N

SCK

MODE 0

SIO(3:0)

X

Dummy

BFH

H1

L1

26H

Device ID

H0

L0

BFH

H1

L1

26H

HN

LN

N

1432 F55.0

Note: MSN = Most significant Nibble; LSN= Least Significant Nibble, C[1:0]=AFH

DS20005013D-page 24

2014 Microchip Technology Inc.

�SST26WF016B/SST26WF016BA

5.16

Serial Flash Discoverable

Parameters (SFDP)

ware support for all future Serial Flash device families.

See Table 11-1 on page 55 for address and data values.

The Serial Flash Discoverable Parameters (SFDP)

contain information describing the characteristics of the

device. This allows device-independent, JEDEC IDindependent, and forward/backward compatible soft-

FIGURE 5-18:

Initiate SFDP by executing an 8-bit command, 5AH, followed by address bits A[23-0] and a dummy byte. CE#

must remain active low for the duration of the SFDP

cycle. For the SFDP sequence, see Figure 5-18.

SERIAL FLASH DISCOVERABLE PARAMETERS SEQUENCE

CE#

MODE 3

SCK

0 1 2 3 4 5 6 7 8

15 16

23 24

31 32

39 40

47 48

55 56

63 64

71 72

80

MODE 0

5A

SI

ADD.

ADD.

ADD.

X

N

DOUT

MSB

HIGH IMPEDANCE

SO

N+1

DOUT

N+2

DOUT

N+3

DOUT

N+4

DOUT

1432 F56.0

5.17

Sector-Erase

To execute a Sector-Erase operation, the host drives

CE# low, then sends the Sector Erase command cycle

(20H) and three address cycles, and then drives CE#

high. Address bits [AMS:A12] (AMS = Most Significant

Address) determine the sector address (SAX); the

remaining address bits can be VIL or VIH. To identify the

completion of the internal, self-timed, Write operation,

poll the BUSY bit in the Status register, or wait TSE. See

Figures 5-19 and 5-20 for the Sector-Erase sequence.

The Sector-Erase instruction clears all bits in the

selected 4 KByte sector to ‘1,’ but it does not change a

protected memory area. Prior to any write operation,

the Write-Enable (WREN) instruction must be executed.

FIGURE 5-19:

4 KBYTE SECTOR-ERASE SEQUENCE– SQI MODE (C[1:0] = 20 H)

CE#

MODE 3

SCK

0

1

2

4

6

MODE 0

SIO(3:0)

C1 C0 A5 A4 A3 A2 A1 A0

MSN LSN

1432 F07.0

Note: MSN = Most Significant Nibble, LSN = Least Significant Nibble, C[1:0]=20H

FIGURE 5-20:

4 KBYTE SECTOR-ERASE SEQUENCE (SPI)

CE#

MODE 3

SCK

0 1 2 3 4 5 6 7 8

20

SI

MSB

SO

15 16

23 24

31

MODE 0

ADD.

ADD.

ADD.

MSB

HIGH IMPEDANCE

1432 F57.0

2014 Microchip Technology Inc.

DS20005013D-page 25

�SST26WF016B/SST26WF016BA

5.18

Block-Erase

To execute a Block-Erase operation, the host drives

CE# low then sends the Block-Erase command cycle

(D8H), three address cycles, then drives CE# high.

Address bits AMS-A13 determine the block address

(BAX); the remaining address bits can be VIL or VIH. For

32 KByte blocks, A14:A13 can be VIL or VIH; for 64

KByte blocks, A15:A13 can be VIL or VIH. Poll the BUSY

bit in the Status register, or wait TBE, for the completion

of the internal, self-timed, Block-Erase operation. See

Figures 5-21 and 5-22 for the Block-Erase sequence.

The Block-Erase instruction clears all bits in the

selected block to ‘1’. Block sizes can be 8 KByte, 32

KByte or 64 KByte depending on address, see Figure

3-1, Memory Map, for details. A Block-Erase instruction

applied to a protected memory area will be ignored.

Prior to any write operation, execute the WREN instruction. Keep CE# active low for the duration of any command sequence.

FIGURE 5-21:

BLOCK-ERASE SEQUENCE (SQI)

CE#

MODE 3

SCK

0

1

2

4

6

MODE 0

SIO(3:0)

C1 C0 A5 A4 A3 A2 A1 A0

MSN LSN

1432 F08.0

Note: MSN = Most Significant Nibble,

LSN = Least Significant Nibble

C[1:0] = D8H

FIGURE 5-22:

BLOCK-ERASE SEQUENCE (SPI)

CE#

MODE 3

SCK

0 1 2 3 4 5 6 7 8

D8

SI

MSB

SO

15 16

23 24

31

MODE 0

ADDR

ADDR

ADDR

MSB

HIGH IMPEDANCE

1432 F58.0

DS20005013D-page 26

2014 Microchip Technology Inc.

�SST26WF016B/SST26WF016BA

5.19

Chip-Erase

To execute a Chip-Erase operation, the host drives

CE# low, sends the Chip-Erase command cycle (C7H),

then drives CE# high. Poll the BUSY bit in the Status

register, or wait TSCE, for the completion of the internal,

self-timed, Write operation. See Figures 5-23 and 5-24

for the Chip Erase sequence.

The Chip-Erase instruction clears all bits in the device

to ‘1.’ The Chip-Erase instruction is ignored if any of the

memory area is protected. Prior to any write operation,

execute the WREN instruction.

FIGURE 5-23:

CHIP-ERASE SEQUENCE (SQI)

CE#

MODE 3

SCK

0

1

MODE 0

SIO(3:0)

C1 C10

1432 F09.1

Note: C[1:0] = C7H

FIGURE 5-24:

CHIP-ERASE SEQUENCE (SPI)

CE#

MODE 3

SCK

0 1 2 3 4 5 6 7

MODE 0

C7

SI

MSB

SO

HIGH IMPEDANCE

1432 F59.0

2014 Microchip Technology Inc.

DS20005013D-page 27

�SST26WF016B/SST26WF016BA

5.20

Page-Program

partial Byte to be ignored. Poll the BUSY bit in the Status register, or wait TPP, for the completion of the internal, self-timed, Block-Erase operation. See Figures 525 and 5-26 for the Page-Program sequence.

The Page-Program instruction programs up to 256

Bytes of data in the memory, and supports both SPI

and SQI protocols. The data for the selected page

address must be in the erased state (FFH) before initiating the Page-Program operation. A Page-Program

applied to a protected memory area will be ignored.

Prior to the program operation, execute the WREN

instruction.

When executing Page-Program, the memory range for

the SST26WF016B/016BA is divided into 256 Byte

page boundaries. The device handles shifting of more

than 256 Bytes of data by maintaining the last 256

Bytes of data as the correct data to be programmed. If

the target address for the Page-Program instruction is

not the beginning of the page boundary (A[7:0] are not

all zero), and the number of bytes of data input exceeds

or overlaps the end of the address of the page boundary, the excess data inputs wrap around and will be programmed at the start of that target page.

To execute a Page-Program operation, the host drives

CE# low then sends the Page Program command cycle

(02H), three address cycles followed by the data to be

programmed, then drives CE# high. The programmed

data must be between 1 to 256 Bytes and in whole Byte

increments; sending less than a full Byte will cause the

FIGURE 5-25:

PAGE-PROGRAM SEQUENCE (SQI)

CE#

MODE 3

SCK

0

2

4

6

8

10

12

MODE 0

SIO(3:0)

C1 C0 A5 A4 A3 A2 A1 A0 H0 L0 H1 L1 H2 L2

HN LN

MSN LSN

Data Byte 0 Data Byte 1 Data Byte 2

Data Byte 255

Note: MSN = Most Significant Nibble, LSN = Least Significant Nibble, C[1:0] = 02H

FIGURE 5-26:

1432 F10.1

PAGE-PROGRAM SEQUENCE (SPI)

CE#

MODE 3

SCK

0 1 2 3 4 5 6 7 8

23 24

15 16

31 32

39

MODE 0

SI

ADD.

02

MSB

SO

ADD.

ADD.

Data Byte 0

LSB MSB

LSB MSB

LSB

HIGH IMPEDANCE

2079

2078

2077

2076

2075

2074

2073

40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55

2072

CE#(cont’)

SCK(cont’)

SI(cont’)

Data Byte 1

MSB

SO(cont’)

Note: C[1:0] = 02H

DS20005013D-page 28

Data Byte 255

Data Byte 2

LSB MSB

LSB

MSB

LSB

HIGH IMPEDANCE

1432 F60.1

2014 Microchip Technology Inc.

�SST26WF016B/SST26WF016BA

5.21

SPI Quad Page-Program

The SPI Quad Page-Program instruction programs up

to 256 Bytes of data in the memory. The data for the

selected page address must be in the erased state

(FFH) before initiating the SPI Quad Page-Program

operation. A SPI Quad Page-Program applied to a protected memory area will be ignored. SST26WF016B

requires the ICO bit in the configuration register to be

set to ‘1’ prior to executing the command.Prior to the

program operation, execute the WREN instruction.

To execute a SPI Quad Page-Program operation, the

host drives CE# low then sends the SPI Quad PageProgram command cycle (32H), three address cycles

followed by the data to be programmed, then drives

CE# high. The programmed data must be between 1 to

256 Bytes and in whole Byte increments. The command cycle is eight clocks long, the address and data

FIGURE 5-27:

cycles are each two clocks long, most significant bit

first. Poll the BUSY bit in the Status register, or wait

TPP, for the completion of the internal, self-timed, Write

operation.See Figure 5-27.

When executing SPI Quad Page-Program, the memory

range for the SST26WF016B/016BA is divided into 256

Byte page boundaries. The device handles shifting of

more than 256 Bytes of data by maintaining the last

256 Bytes of data as the correct data to be programmed. If the target address for the SPI Quad PageProgram instruction is not the beginning of the page

boundary (A[7:0] are not all zero), and the of bytes of

data input exceeds or overlaps the end of the address

of the page boundary, the excess data inputs wrap

around and will be programmed at the start of that target page.

SPI QUAD PAGE-PROGRAM SEQUENCE

CE#

MODE 3

SCK

SIO0

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17

MODE 0

32H

A20A16A12 A8 A4 A0 b4 b0 b4 b0

b4 b0

SIO1

A21 A17A13 A9 A5 A1 b5 b1 b5 b1

b5 b1

SIO2

A22 A18A14A10 A6 A2 b6 b2 b6 b2

b6 b2

MSN LSN

SIO3

A23 A19 A15 A11 A7 A3 b7 b3 b7 b3

b7 b3

Data Data

Byte 0 Byte 1

Data

Byte

255

Address

5.22

Write-Suspend and Write-Resume

Write-Suspend allows the interruption of Sector-Erase,

Block-Erase, SPI Quad Page-Program, or Page-Program operations in order to erase, program, or read

data in another portion of memory. The original operation can be continued with the Write-Resume command. This operation is supported in both SQI and SPI

protocols.

Only one write operation can be suspended at a time;

if an operation is already suspended, the device will

ignore the Write-Suspend command. Write-Suspend

during Chip-Erase is ignored; Chip-Erase is not a valid

command while a write is suspended. The WriteResume command is ignored until any write operation

(Program or Erase) initiated during the Write-Suspend

is complete. The device requires a minimum of 500 μs

between each Write-Suspend command.

2014 Microchip Technology Inc.

5.23

Write-Suspend During SectorErase or Block-Erase

Issuing a Write-Suspend instruction during SectorErase or Block-Erase allows the host to program or

read any sector that was not being erased. The device

will ignore any programming commands pointing to the

suspended sector(s). Any attempt to read from the suspended sector(s) will output unknown data because the

Sector- or Block-Erase will be incomplete.

To execute a Write-Suspend operation, the host drives

CE# low, sends the Write Suspend command cycle

(B0H), then drives CE# high. The Status register indicates that the erase has been suspended by changing

the WSE bit from ‘0’ to ‘1,’ but the device will not accept

another command until it is ready. To determine when

the device will accept a new command, poll the BUSY

bit in the Status register or wait TWS.

DS20005013D-page 29

�SST26WF016B/SST26WF016BA

5.24

Write Suspend During Page

Programming or SPI Quad Page

Programming

Issuing a Write-Suspend instruction during Page Programming allows the host to erase or read any sector

that is not being programmed. Erase commands pointing to the suspended sector(s) will be ignored. Any

attempt to read from the suspended page will output

unknown data because the program will be incomplete.

To execute a Write Suspend operation, the host drives

CE# low, sends the Write Suspend command cycle

(B0H), then drives CE# high. The Status register indicates that the programming has been suspended by

changing the WSP bit from ‘0’ to ‘1,’ but the device will

not accept another command until it is ready. To determine when the device will accept a new command, poll

the BUSY bit in the Status register or wait TWS.

5.25

Write-Resume

Write-Resume restarts a Write command that was suspended, and changes the suspend status bit in the Status register (WSE or WSP) back to ‘0’.

To execute a Write-Resume operation, the host drives

CE# low, sends the Write Resume command cycle

(30H), then drives CE# high. To determine if the internal, self-timed Write operation completed, poll the

BUSY bit in the Status register, or wait the specified

time TSE, TBE or TPP for Sector-Erase, Block-Erase, or

Page-Programming, respectively. The total write time

before suspend and after resume will not exceed the

uninterrupted write times TSE, TBE or TPP.

5.26

Read Security ID

The Read Security ID operation is supported in both

SPI and SQI modes. To execute a Read Security ID

(SID) operation in SPI mode, the host drives CE# low,

sends the Read Security ID command cycle (88H), two

address cycles, and then one dummy cycle. To exe-

TABLE 5-5:

cute a Read Security ID operation in SQI mode, the

host drives CE# low and then sends the Read Security

ID command, two address cycles, and three dummy

cycles.