USB4640/USB4640i

High-Speed Inter-Chip (HSIC) USB 2.0 Hub and Flash Media Controller

General Description

Features

The Microchip USB4640/USB4640i is a Hi-Speed

HSIC USB hub and card reader combo solution with an

upstream port that is compliant to HSIC 1.0 (supplement to the USB 2.0 Specification). The two downstream ports are compliant with the USB 2.0

Specification.

• Compliance with the following flash media card

specifications SD 2.0; MMC 4.2; MS 1.43; MSPro 1.02; MS-Pro-HG 1.01; MS-Duo 1.10; and

xD 1.2

• Low-power digital HSIC interface offers a replacement for onboard host and device connection for

analog USB bus cable

• HSIC interface enables printers, mobile PCs,

ultra-mobile PCs, and cell phone products to

reduce the total power budget

• HSIC interface provides use of USB connectivity

and compatibility with existing USB drivers and

software

• External 1.2 V reference allows upstream/downstream HSIC links to use the same voltage reference

• Supports a single external 3.3 V supply source;

internal regulators provide 1.8 V internal core voltage for additional bill of materials and power savings

• The hub transaction translator (TT) supports FullSpeed and Low-Speed peripheral operation

• 9 KB RAM | 64 KB on-chip ROM

• Enhanced EMI rejection and ESD protection performance

• Hub and flash media reader/writer configuration

from a single source:

- Configures internal code using an external

I2C EEPROM

- Supports external code using an SPI Flash

EEPROM

- Customizable vendor ID, product ID, and language ID if using an external EEPROM

• The USB4640 supports the commercial temperature range of 0°C to +70°C

• The USB4640i supports the industrial temperature range of -40°C to +85°C

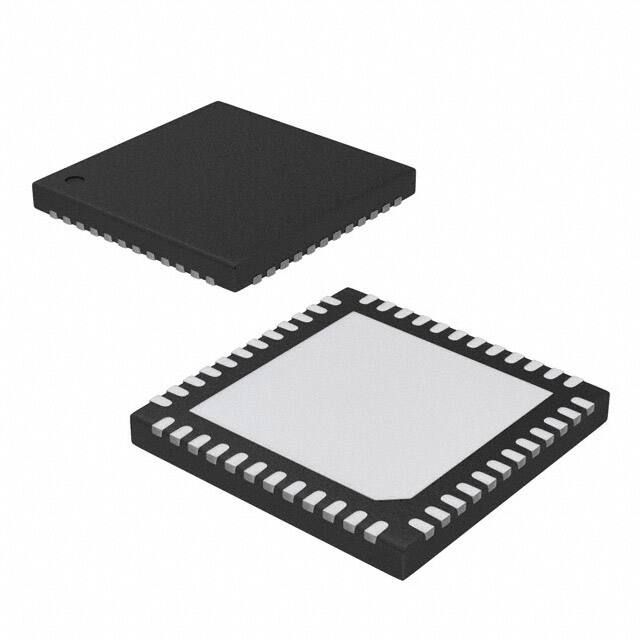

• 48-pin QFN (7 x 7 mm) RoHS compliant package

High-Speed Inter-Chip (HSIC) is a digital interconnect

bus that enables the use of USB technology as a lowpower chip-to-chip interconnect at speeds up to

480 Mb/s. The HSIC interface is an industry standard

2-pin digital interface which uses standard USB software. The USB4640/USB4640i provides an ultra fast

interface between an HSIC enabled host and several

popular flash media formats. The controller allows

read/write capability to flash media from the following

families:

- Secure DigitalTM (SD)

- MultiMediaCardTM (MMC)

- Memory Stick® (MS)

- xD-Picture CardTM (xD)1

The USB4640/USB4640i combo solution leverages

Microchip’s innovative technology that delivers industry-leading data throughput in mixed-speed USB environments. Average sustained transfer rates exceeding

35 MB/s are possible.2

Highlights

• Upstream HSIC port and 2 exposed Hi-Speed

USB 2.0 downstream ports for external peripheral

expansion

• Dedicated flash media reader internally attached

to a 3rd downstream port of the hub as a USB

compound device

- single or multiplexed flash media reader

interface

• PortMap - Flexible port mapping and disable

sequencing

• PortSwap - Programmable USB differential-pair

pin locations ease PCB design by aligning USB

signal lines directly to connectors

• PHYBoost - Programmable USB signal drive

strength for recovering signal integrity using 4level driving strength resolution

1. Obtain user license from the x-D-Picture Card License

Office.

2. Host and Media dependent.

2013- 2018 Microchip Technology Inc.

Applications

• 3G/4G handsets, smartphones, cell phones, and

other mobile devices

• Desktop and mobile PCs

• Printers

• GPS navigation systems

• Media players/viewers

• Consumer A/V

• Set-top boxes

• Industrial products

DS00001922B-page 1

�USB4640/USB4640i

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at docerrors@microchip.com. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the

revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Website; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are

using.

Customer Notification System

Register on our website at www.microchip.com to receive the most current information on all of our products.

DS00001922B-page 2

2013- 2018 Microchip Technology Inc.

�USB4640/USB4640i

Table of Contents

1.0 Overview ......................................................................................................................................................................................... 4

2.0 Block Diagram ................................................................................................................................................................................. 7

3.0 Pinning Information ......................................................................................................................................................................... 8

4.0 Configuration Options ................................................................................................................................................................... 21

5.0 AC Specifications .......................................................................................................................................................................... 41

6.0 DC Parameters ............................................................................................................................................................................. 43

7.0 Temperature Specifications .......................................................................................................................................................... 48

8.0 Package Specifications ................................................................................................................................................................. 49

Appendix A: Acronyms ........................................................................................................................................................................ 53

Appendix B: References ..................................................................................................................................................................... 54

Appendix C: Data Sheet Revision History .......................................................................................................................................... 55

The Microchip Website ....................................................................................................................................................................... 57

Customer Change Notification Service ............................................................................................................................................... 57

Customer Support ............................................................................................................................................................................... 57

Product Identification System ............................................................................................................................................................. 58

2013-2018 Microchip Technology Inc.

DS00001922B-page 3

�USB4640/USB4640i

1.0

OVERVIEW

The USB4640/USB4640i is a Hi-Speed HSIC USB hub and card reader combo solution with an upstream port compliant

to the High-Speed Inter-Chip USB Electrical Specification Revision 1.0 [2]. The two downstream ports are USB 2.0 compliant, and the dedicated flash media reader/writer is internally attached to a 3rd downstream port as a USB compound

device.

High-Speed Inter-Chip (HSIC) is a digital interconnect bus that enables the use of USB technology as a low-power chipto-chip interconnect at speeds up to 480 Mb/s (see the High-Speed Inter-Chip USB Electrical Specification Revision

1.0). This combo solution supports several multi-format flash media cards. This multi-format flash media controller and

USB hub combo features two exposed downstream USB ports available for external peripheral expansion.

The USB4640/USB4640i can attach to an upstream port as a Full- or Full/Hi-Speed hub. The hub supports Low-Speed,

Full-Speed, and Hi-Speed downstream devices (if operating as a Hi-Speed hub) on all of the enabled downstream ports.

All required resistors on the USB ports are integrated into the hub, including all series termination resistors on D+ and

D– pins and all required pull-down and pull-up resistors. The over-current sense inputs for the downstream facing ports

have internal pull-up resistors.

The USB4640/USB4640i includes programmable features, such as:

• PortMap: provides flexible port mapping and disable sequences. The downstream ports of a USB4640/USB4640i hub can be reordered or disabled in any

sequence to support multiple platform designs with minimum effort. For any port

that is disabled, the USB4640/USB4640i hub controllers automatically reorder

the remaining ports to match the USB host controller’s port numbering scheme.

• PortSwap: adds per-port programmability to USB differential-pair pin locations.

PortSwap also allows direct alignment of USB signals (D+/D-) to connectors to

avoid uneven trace length or crossing of the USB differential signals on the PCB.

• PHYBoost: enables 4 programmable levels of USB signal drive strength in downstream port transceivers. PHYBoost will also attempt to restore USB signal integrity.

Note:

1.1

PHYBoost is only available on the two USB downstream ports.

Hardware Features

•

•

•

•

•

•

•

•

•

Single-chip HSIC hub and flash media controller combo

USB4640/USB4640i supports the commercial temperature range of 0°C to +70°C.

USB4640/USB4640i supports the industrial temperature range of -40°C to +85°C.

Transaction translator (TT) in the hub supports operation of FS and LS peripherals

Full power management with individual or ganged power control of each downstream port

Optional support for external firmware access via SPI interface

Onboard 24 MHz crystal driver circuit

Optional external 24 MHz clock input (must be a 1.8 V signal)

Code execution via SPI ROM which must meet the following criteria:2013-2018

- 30 MHz or 60 MHz operation support

- Single-bit or dual-bit mode support

- Mode 0 or Mode 3 SPI support

• Compliance with the following flash media card specifications:

- Secure Digital 2.0 and MultiMediaCard 4.2

- SD 2.0, SD-HS, SD-HC

- TransFlash™ and reduced form factor media

- 1/4/8 bit MMC 4.2

- Memory Stick 1.43

- Memory Stick Pro Format 1.02

DS00001922B-page 4

2013-2018 Microchip Technology Inc.

�USB4640/USB4640i

- Memory Stick Pro-HG Duo Format 1.01

- Memory Stick, MS Duo, MS-HS, MS Pro-HG, MS Pro

- Memory Stick Duo 1.10

- xD-Picture Card 1.2

• 8051 8-bit microprocessor

- 60 MHz - single-cycle execution

- 64 KB ROM | 9 KB RAM

• Integrated regulator for 1.8 V core operation

1.2

Software Features

• Hub and flash media reader/writer configuration from a single source: External I2C ROM or external SPI ROM,

where the following features are then available:

- Customizable vendor ID, product ID, and device ID

- 12-hex digits maximum for the serial number string

- 28-character manufacturer ID and product strings for the flash media reader/writer

1.3

OEM Selectable Hub Features

The USB4640/USB4640i provides a default configuration that may be sufficient for most applications following a reset.

The USB4640/USB4640i can instead be configured by an external I2C EEPROM or SPI ROM.

• Compound device support on a port-by-port basis

- a port is permanently hardwired to a downstream USB peripheral device

• Select over-current sensing and port power control on an individual or ganged (all ports together) basis to match

the OEM’s choice of circuit board component selection

• Port power control and over-current detection/delay features

• Configure the delay time for filtering the over-current sense inputs

• Configure the delay time for turning on downstream port power

• Bus-powered or self-powered selection

• Hub port disable or non-removable configurations

• Flexible port mapping and disable sequencing supports multiple platform designs

• Programmable USB differential-pair pin location eases PCB layout by aligning USB signal lines directly to connectors

• Programmable USB signal drive strength recovers USB signal integrity using 4 levels of signal drive strength

• Indicate the maximum current that the 2-port hub consumes

• Indicate the maximum current required for the hub controller

2013-2018 Microchip Technology Inc.

DS00001922B-page 5

�USB4640/USB4640i

Conventions

Within this manual, the following abbreviations and symbols are used to improve readability.

Example

BIT

FIELD.BIT

x…y

BITS[m:n]

PIN

Description

Name of a single bit within a field

Name of a single bit (BIT) in FIELD

Range from x to y, inclusive

Groups of bits from m to n, inclusive

Pin name

zzzzb

Binary number (value zzzz)

0xzzz

Hexadecimal number (value zzz)

zzh

Hexadecimal number (value zz)

rsvd

Reserved memory location. Must write 0, read value indeterminate

code

Instruction code, or API function or parameter

Multi Word Name

Used for multiple words that are considered a single unit, such as:

Resource Allocate message, or Connection Label, or Decrement Stack Pointer instruction.

Section Name

Section or document name.

VAL

x

Over-bar indicates active low pin or register bit

Don’t care

indicate a parameter is optional or is only used under some conditions.

{,Parameter}

Braces indicate parameter(s) that repeat one or more times.

[Parameter]

Brackets indicate a nested parameter. This parameter is not real and actually

decodes into one or more real parameters.

DS00001922B-page 6

2013-2018 Microchip Technology Inc.

�3.3 V

2013-2018 Microchip Technology Inc.

USB Data

Downstream

PHY

Transaction

Translator

Serial

Interface

Engine

PLL

24 MHz

Crystal

USB Data

OC Sense/

Downstream Pwr Switch

PHY

Port #2

OC

Sense

Switch

Driver

Routing & Port Re-Ordering Logic

OC Sense/

Pwr Switch

Port #3

OC

Sense

Switch

Driver

VDDCR

1.8 V Reg

Repeater

1.8 V Reg

3.3 V

1.8 V

SIE

CTL

3K

total

BUS

INTFC

ADDR

MAP

EP2

EP2 RX

RX

EP2 TX

RAM

EP0 TX

EP0 RX

ROM

64 K

RAM

6K

SFR

RAM

BUS

INTFC

PWR_FET0

SPI

MS

BUS

INTFC

SD/

MMC

FMI

FMDU

CTL

AUTO_CBW

PROC

Flash Media Cards

(require Combo socket)

xD*

XDATA BRIDGE

+ BUS ARBITER

Program Memory I/O Bus

8051

PROCESSOR

*For xD-Picture CardTM support, please obtain a user

license from the xD-Picture Card License office.

BRIDGE

Port Controller

Controller

Serial

Interface

(CRD_PWR)

SPI (4 pins)

FIGURE 2-1:

HSIC

HSIC

Data & Strobe

2.0

HSIC

Impedance

1.2 V

USB4640/USB4640i

BLOCK DIAGRAM

USB4640/USB4640I BLOCK DIAGRAM

DS00001922B-page 7

�USB4640/USB4640i

3.0

PINNING INFORMATION

This chapter outlines the pinning configuration, followed by a corresponding pin list grouped by function. The detailed

pin descriptions are listed then outlined in Section 3.3, "Pin Descriptions," on page 10.

Pin Configurations

NC

CRD_PWR

VDD33

SD_D2/xD_D5

SD_D3/MS_D3/xD_D6

MS_INS

SD_D4/MS_D2/xD_D7

xD_nCD

xD_nB/R

xD_nRE

xD_nCE

VDD33

35

34

33

32

31

30

29

28

27

26

25

USB4640/USB4640I 48-PIN QFN

36

FIGURE 3-1:

LED/TXD

37

24

SD_CMD/MS_D0/xD_CLE

nRESET

38

23

SD_D5/MS_D1/xD_ALE

HSIC_IMP

39

22

xD_nWE

TEST

40

21

SD_CLK/MS_BS/xD_nWP

VDD12

41

20

SD_D6/MS_D7/xD_D0

HSIC_DAT

42

19

SD_D7/MS_D6/xD_D1

HSIC_STROBE

43

18

SD_D0/MS_D4/xD_D2

XTAL2

44

17

SD_D1/MS_D5/xD_D3

XTAL1 (CLKIN)

45

16

VDD33

PLLFILT

46

15

CRFILT

14

SD_nCD

13

SD_WP/MS_SCLK/xD_D4

12

9

SPI_CLK

VDD33

8

SPI_CE_n

11

7

PRTCTL3

SPI_DI

6

PRTCTL2

10

5

VDD33

SPI_DO/SDA/SPI_SPD_SEL

4

USBDN_DP3

USBDN_DM2

3

48

USBDN_DM3

VDD33

2

47

Ground Pad

(must be connected to VSS)

1

RBIAS

USB4640/40i

(Top View QFN-48)

USBDN_DP2

3.1

Indicates pins on the bottom of the device.

DS00001922B-page 8

2013-2018 Microchip Technology Inc.

�USB4640/USB4640i

3.2

48-Pin List

TABLE 3-1:

USB4640/USB4640I 48-PIN LIST

UPSTREAM HSIC INTERFACE (3 PINS)

HSIC_IMP

HSIC_DAT

HSIC_STROBE

DOWNSTREAM USB INTERFACE (3 PINS)

XTAL1 (CLKIN)

XTAL2

RBIAS

DOWNSTREAM 2-PORT USB INTERFACE (6 PINS)

USBDN_DP2

USBDN_DM2

USBDN_DP3

USBDN_DM3

PRTCTL2

PRTCTL3

SECURE DIGITAL/MEMORY STICK/xD INTERFACE (18 PINS)

SD_D7/

MS_D6/

xD_D1

SD_D6/

MS_D7/

xD_D0

SD_D5/

MS_D1/

xD_ALE

SD_D4/

MS_D2/

xD_D7

SD_D3/

MS_D3/

xD_D6

SD_D2/

xD_D5

SD_D1/

MS_D5/

xD_D3

SD_D0/

MS_D4/

xD_D2

SD_CLK/

MS_BS/

xD_nWP

SD_CMD/

MS_D0/

xD_CLE

SD_nCD

MS_INS

SD_WP/

MS_SCLK/

xD_D4

xD_nCD

xD_nWE

xD_nB/R

xD_nRE

xD_nCE

SPI INTERFACE (4 PINS)

SPI_CE_N

SPI_DO/

SDA/

SPI_SPD_SEL

SPI_CLK/

SCL

SPI_DI

MISC (5 PINS)

nRESET

TEST

LED

NC

CRFILT

PLLFILT

(CRD_PWR)

POWER (9 PINS)

(6) VDD33

VDD12

TOTAL 48

2013-2018 Microchip Technology Inc.

DS00001922B-page 9

�USB4640/USB4640i

3.3

Pin Descriptions

This section provides a detailed description of each pin. The pins are arranged in functional groups according to their

associated interface. The pin descriptions below are applied when using the internal default firmware and can be referenced in Section 4.0, "Configuration Options," on page 21. See Appendix A:, "Acronyms," on page 53 for details.

An n in the signal name indicates that the active (asserted) state occurs when the signal is at a low-voltage level. When

the n is not present, the signal is asserted when it is at a high-voltage level. The terms assertion and negation are used

exclusively in order to avoid confusion when working with a mixture of active-low and active-high signals. The term

assert, or assertion, indicates that a signal is active, independent of whether that level is represented by a high or low

voltage. The term negate, or negation indicates that a signal is inactive.

TABLE 3-2:

USB4640/USB4640I PIN DESCRIPTIONS

Symbol

48-Pin

QFN

Buffer Type

Description

UPSTREAM HSIC INTERFACE

HSIC_IMP

39

I

HSIC Impedance Control

Selects the driver impedance of HSIC_DAT and HSIC_STROBE

1 : Approximately 50 impedance

0 : Approximately 40 impedance

HSIC_DAT

42

I/O

HSIC Data

Bi-directional double data rate (DDR) data signal that is synchronous

to the HSIC_STROBE signal as defined in the High-Speed Inter-Chip

USB Specification, Version 1.0.

HSIC_STROBE

43

I/O

HSIC Strobe

Bi-directional data strobe signal defined in the High-Speed Inter-Chip

USB Specification, Version 1.0.

DOWNSTREAM USB INTERFACE

USBDN_DM

[3:2]

USBDN_DP

[3:2]

3

1

4

2

I/O-U

PRTCTL[3:2]

7

6

I/OD6PU

47

I-R

RBIAS

USB Bus Data

Connect to the downstream USB bus data signals and can be

swapped using the PortSwap feature (See Section 4.4.4.20, "F1h: Port

Swap," on page 36).

USB Power Enable, when used as an:

• Output: enables power to downstream USB peripheral devices and

have weak internal pull-up resistors. (See Section 3.5, "Port Power

Control," on page 15 for diagram and usage instructions.)

• Input: monitor the Over-current condition (when the power is

enabled). When an Over-current condition is detected, the pins

turn the power off.

USB Transceiver Bias

Sets the transceiver's internal bias currents using a 12.0 k, 1.0%

resistor attached from VSS.

XTAL1 (CLKIN)

45

ICLKx

24 MHz Crystal Input or External Clock Input

Can be connected to one terminal of the crystal or connected to an

external 24 MHz clock when a crystal is not used.

XTAL2

44

OCLKx

24 MHz Crystal Output

The other terminal of the crystal, or it is left open when an external

clock source is used to drive XTAL1(CLKIN).

DS00001922B-page 10

2013-2018 Microchip Technology Inc.

�USB4640/USB4640i

TABLE 3-2:

Symbol

USB4640/USB4640I PIN DESCRIPTIONS (CONTINUED)

48-Pin

QFN

Buffer Type

Description

SECURE DIGITAL INTERFACE

SD_D[7:0]

SD_CLK

19

20

23

30

32

33

17

18

I/O8PU

21

O8

Secure Digital Data 7-0

Bi-directional data signals SD_D0 - SD_D7 with weak pull-up resistor.

Secure Digital Clock

The output clock signal to the SD/MMC device

SD_CMD

24

I/O8PU

Secure Digital Command

Bi-directional signal that connects to the CMD signal of the SD/MMC

device. The bi-directional signal has a weak internal pull-up resistor.

SD_nCD

14

I/O8PU

Secure Digital Card Detect

Designates as the Secure Digital card detection pin and has an

internal pull-up.

SD_WP

13

I/O8

Secure Digital Write Protected

Designates as the Secure Digital card interface mechanical write

protect detect pin.

MEMORY STICK INTERFACE

MS_BS

21

O8

Memory Stick Bus State

Connected to the bus state pin of the MS device. It is used to control

the Bus States 0, 1, 2, and 3 (BS0, BS1, and BS3) of the MS device.

MS_INS

31

IPU

Memory Stick Card Insertion

Designates as the Memory Stick card detection pin and has a weak

internal pull-up resistor.

MS_SCLK

13

O8

Memory Stick System Clock

Output clock signal to the MS device.

MS_D[7:0]

20

19

17

18

32

30

23

24

I/O8PD

30

32

33

13

17

18

19

20

I/O8PD

23

O8PD

Memory Stick System Data In/Out

Bi-directional data signals for the MS device. In Serial mode, the most

significant bit (MSB) of each byte is transmitted first by either the

memory stick controller MSC or the MS device on MS_D0.

MS_D0, MS_D2, and MS_D3 have weak pull-down resistors. MS_D1

has a pull-down resistor when in Parallel mode. Otherwise, it is

disabled. In 4-bit or 8-bit Parallel modes, all MS_D7 - MS_D0 signals

have weak pull-down resistors.

xD-PICTURE CARD INTERFACE

xD_D[7:0]

xD_ALE

xD-Picture Card Data 7-0

Bi-directional data signals xD_D7 - xD_D0 and have weak internal pulldown resistors.

xD-Picture Card Address Strobe

Active-high Address Latch Enable (ALE) signal for the xD-Picture Card

device. This pin has a weak pull-down resistor that is permanently

enabled.

2013-2018 Microchip Technology Inc.

DS00001922B-page 11

�USB4640/USB4640i

TABLE 3-2:

USB4640/USB4640I PIN DESCRIPTIONS (CONTINUED)

Symbol

48-Pin

QFN

xD_nB/R

28

xD_nCE

26

Buffer Type

O8PU

Description

xD-Picture Card Chip Enable

Active-low chip enable signal for the xD-Picture Card device.

When using the internal FET, this pin has weak internal pull-up resistor

that is tied to the output of the internal power FET.

If an external FET is used (internal FET is disabled), then the internal

pull-up is not available (an external pull-up is required).

xD_CLE

24

O8PD

xD-Picture Card Command Strobe

An active-high Command Latch Enable signal for the xD-Picture Card

device. This pin has a weak pull-down resistor that is permanently

enabled.

xD_nCD

29

I/O8

xD-Picture Card Detection

Designates as the xD-Picture Card detection pin and has an internal

pull-up.

xD_nRE

27

O8PU

xD-Picture Card Read Enable

Active-low read strobe signal for the xD-Picture Card device.

When using the internal FET, this pin has a weak internal pull-up

resistor that is tied to the output of the internal power FET.

If an external FET is used (internal FET is disabled), then the internal

pull-up is not available (an external pull-up is required).

xD_nWE

22

O8PU

xD-Picture Card Write Enable

Active-low write strobe signal for the xD-Picture Card device.

When using the internal FET, this pin has a weak internal pull-up

resistor that is tied to the output of the internal power FET.

If an external FET is used (internal FET is disabled), then the internal

pull-up is not available (an external pull-up is required).

xD_nWP

21

O8PD

xD-Picture Card Write Protect

An active-low write-protect signal for the xD-Picture Card device. This

pin has a weak pull-down resistor that is permanently enabled.

SPI INTERFACE

SPI_CE_n

8

O12

SPI Chip Enable

An active-low chip enable output. If the SPI interface is enabled, this

pin must be driven high in power down states.

SPI_CLK/

9

I/O12

SPI Clock Out

Clock signal out to the serial ROM. See Section 3.6, "ROM BOOT

Sequence," on page 17 for diagram and usage instructions. During

reset, this pin must be driven low.

SCL

I/O6

Serial Clock

The I2C EEPROM clock pin when the device is connected to the

optional I2C EEPROM.

DS00001922B-page 12

2013-2018 Microchip Technology Inc.

�USB4640/USB4640i

TABLE 3-2:

USB4640/USB4640I PIN DESCRIPTIONS (CONTINUED)

Symbol

48-Pin

QFN

Buffer Type

SPI_DO/

10

I/O12

Description

SPI Serial Data Out

The output for the SPI port. See Section 3.6, "ROM BOOT Sequence"

for diagram and usage instructions.

SDA/

I/O6

Serial Data Line

The I2C EEPROM data pin when the device is connected to the

optional I2C EEPROM.

SPI_SPD_SEL

I/O12

SPI Speed Select

Selects the speed of the SPI interface. During nRESET assertion, this

pin will be tri-stated with the weak pull-down resistor enabled. When

nRESET is negated, the value on the pin will be internally latched, and

the pin will revert to SPI_DO functionality, where the internal pull-down

will be disabled.

0 : 30 MHz (no external resistor should be applied)

1 : 60 MHz (a 10 k external pull-up resistor must be applied)

If the latched value is 1, then the pin is tri-stated when the chip is in

the suspend state.

If the latched value is 0, then the pin is driven low during a suspend

state.

SPI_DI

11

I/O12PD

SPI Serial Data In

The SPI data in to the controller from the ROM. This pin has a weak

internal pull-down applied at all times to prevent floating.

MISC

LED

37

NC

36

CRD_PWR

35

I/O6

I/O200

Can be used as an LED output.

Card Power Drive: 3.3 V (100 mA or 200 mA)

This must be the only FET used to power devices. Failure to do this

will violate voltage specifications on device pins.

Please see Section 4.4.2.3, "A4h-A5h: Smart Media Device Power

Configuration," on page 28 for more information.

nRESET

38

IS

Reset Input

The system uses this active low signal to reset the chip. The active

low pulse should be at least 1 s wide.

TEST

40

I

Test Input

Tie to ground for normal operation.

DIGITAL/POWER/GROUND

CRFILT

15

PLLFILT

46

VDD Core Regulator Filter Capacitor

Requires a 1.0 F (or greater) 20% (ESR