FEATURES

FUNCTIONAL BLOCK DIAGRAM

VDD

GND

VREF

AD5686R-EP

VLOGIC

INPUT

REGISTER

2.5V

REFERENCE

DAC

REGISTER

STRING

DAC A

SCLK

SYNC

SDIN

SDO

VOUTA

BUFFER

INPUT

REGISTER

DAC

REGISTER

STRING

DAC B

VOUTB

BUFFER

INPUT

REGISTER

DAC

REGISTER

STRING

DAC C

VOUTC

BUFFER

INPUT

REGISTER

DAC

REGISTER

STRING

DAC D

VOUTD

BUFFER

LDAC RESET

POWER-ON

RESET

GAIN

×1/×2

RSTSEL

GAIN

POWERDOWN

LOGIC

12975-001

High relative accuracy (INL): ±4 LSB maximum at 16 bits

Low drift 2.5 V reference: 4 ppm/°C typical

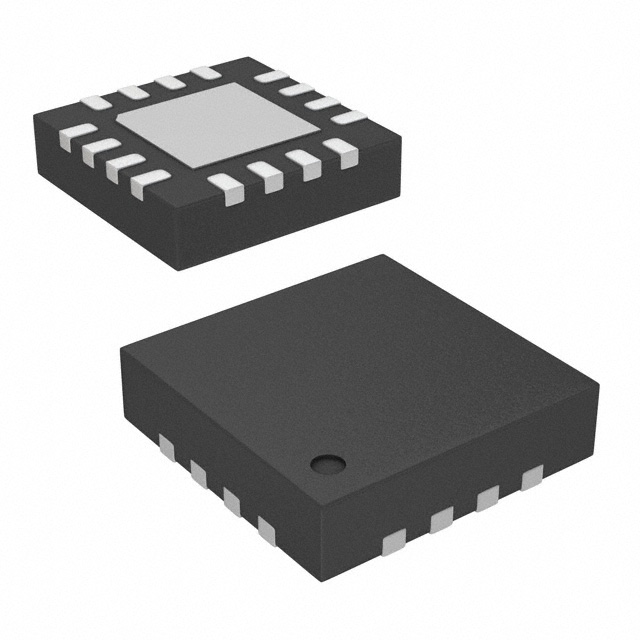

Tiny package: 3 mm × 3 mm, 16-lead LFCSP

Total unadjusted error (TUE): ±0.1% of FSR maximum

Offset error: ±1.5 mV maximum

Gain error: ±0.1% of FSR maximum

High drive capability: 15 mA, 0.5 V from supply rails

User selectable gain of 1 or 2 (GAIN pin)

Reset to zero scale or midscale (RSTSEL pin)

1.8 V logic compatibility

50 MHz SPI with readback or daisy chain

Low glitch: 0.5 nV-sec

Low power: 3.3 mW at 3 V

2.7 V to 5.5 V power supply

INTERFACE LOGIC

Enhanced Product

Quad, 16-Bit nanoDAC+

with 4 ppm/°C Reference, SPI Interface

AD5686R-EP

Figure 1.

ENHANCED PRODUCT FEATURES

Supports defense and aerospace applications (AQEC)

Temperature range: −55°C to +125°C

Controlled manufacturing baseline

1 assembly/test site

1 fabrication site

Enhanced product change notification

Qualification data available on request

APPLICATIONS

Optical transceivers

Base-station power amplifiers

Process control (PLC input/output cards)

Industrial automation

Data acquisition systems

GENERAL DESCRIPTION

The AD5686R-EP, a member of the nanoDAC+® family, is a low

power, quad, 16-bit buffered voltage output digital-to-analog

converter (DAC). The device includes a 2.5 V, 4 ppm/°C internal

reference (enabled by default) and a gain select pin giving a fullscale output of 2.5 V (gain = 1) or 5 V (gain = 2). The device

operates from a single 2.7 V to 5.5 V supply, is guaranteed

monotonic by design, and exhibits less than 0.1% FSR gain error

and 1.5 mV offset error performance. The device is available in

a 3 mm × 3 mm LFCSP package.

The AD5686R-EP also incorporates a power-on reset circuit and a

RSTSEL pin that ensures that the DAC outputs power up to zero

scale or midscale and remains there until a valid write occurs.

The device contains a per-channel power-down feature that

Rev. A

reduces the current consumption of the device to 4 μA at 3 V

while in power-down mode.

The AD5686R-EP employs a versatile serial peripheral interface

(SPI) that operates at clock rates up to 50 MHz, and contains a

VLOGIC pin that is intended for 1.8 V/3 V/5 V logic.

Additional application and technical information can be found

in the AD5686R/AD5685R/AD5684R data sheet.

PRODUCT HIGHLIGHTS

1.

2.

High Relative Accuracy (INL).

±4 LSB maximum.

Low Drift 2.5 V On-Chip Reference.

4 ppm/°C typical temperature coefficient.

13 ppm/°C maximum temperature coefficient.

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2015–2016 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

�AD5686R-EP

Enhanced Product

TABLE OF CONTENTS

Features .............................................................................................. 1

Timing Characteristics .................................................................6

Enhanced Product Features ............................................................ 1

Daisy-Chain and Readback Timing Characteristics ................7

Applications ....................................................................................... 1

Absolute Maximum Ratings ............................................................9

Functional Block Diagram .............................................................. 1

ESD Caution...................................................................................9

General Description ......................................................................... 1

Pin Configuration and Function Descriptions........................... 10

Product Highlights ....................................................................... 1

Typical Performance Characteristics ........................................... 11

Revision History ........................................................................... 2

Outline Dimensions ....................................................................... 17

Specifications..................................................................................... 3

Ordering Guide .......................................................................... 17

AC Characteristics ........................................................................ 5

REVISION HISTORY

11/2016—Rev. 0 to Rev. A

Changed 1.8 V ≤ VLOGIC ≤ 5.5 V to

1.62 V ≤ VLOGIC ≤ 5.5 V ................................................. Throughout

Changes to Features Section............................................................ 1

Changes to VLOGIC Parameter, Table 1 ...................................................... 4

Changes to Output Noise Spectral Density (NSD) Parameter,

Test Conditions/Comments Column, Table 2 .............................. 5

Changes to Table 3 ............................................................................ 6

Changes to Table 4 and Figure 4 ..................................................... 7

Changes to Figure 5 .......................................................................... 8

Deleted ESD Parameter, Table 5 and FICDM Parameter, Table 5.... 9

Changes to Pin 9 Description Column, Table 6 and Pin 13

Description Column, Table 6 ........................................................ 10

Changes to Figure 9 ........................................................................ 11

Changes to Figure 15 to Figure 18 ................................................ 12

Changes to Figure 19 to Figure 23 ................................................ 13

Changes to Figure 25, Figure 26, and Figure 29 ......................... 14

Changes to Figure 31 and Figure 36............................................. 16

Changes to Figure 37 ...................................................................... 16

7/2015—Revision 0: Initial Version

Rev. A | Page 2 of 17

�Enhanced Product

AD5686R-EP

SPECIFICATIONS

VDD = 2.7 V to 5.5 V, 1.62 V ≤ VLOGIC ≤ 5.5 V, all specifications TMIN to TMAX, unless otherwise noted. RL = 2 kΩ; CL = 200 pF.

Table 1.

Parameter

STATIC PERFORMANCE 1

Resolution

Relative Accuracy

Min

Offset Error Drift 2

Gain Temperature Coefficient (TC)2

DC Power Supply Rejection Ratio2

DC Crosstalk2

LOGIC INPUTS2

Input Current

Input Voltage

Low (VINL)

High (VINH)

Pin Capacitance

±4

±5

±1

1.5

±1.5

±0.1

±0.1

±0.15

±0.1

±0.2

Unit

Test Conditions/Comments

±1

±1

0.15

Bits

LSB

LSB

LSB

mV

mV

% of FSR

% of FSR

% of FSR

% of FSR

% of FSR

µV/°C

ppm

mV/V

±2

±3

±2

µV

µV/mA

µV

Due to single channel, full-scale output change

Due to load current change

Due to powering down (per channel)

V

V

nF

nF

kΩ

µV/mA

µV/mA

mA

Ω

µs

Gain = 1

Gain = 2, see Figure 27

RL = ∞

RL = 1 kΩ

0

0

Capacitive Load Stability

Short-Circuit Current 4

Load Impedance at Rails 5

Power-Up Time

REFERENCE OUTPUT

Output Voltage 6

Reference TC 7, 8

Output Impedance2

Output Voltage Noise2

Output Voltage Noise Density2

Load Regulation Sourcing2

Load Regulation Sinking2

Output Current Load Capability2

Line Regulation2

Thermal Hysteresis2

±1

±1

0.4

+0.1

+0.01

±0.02

±0.02

±0.01

Total Unadjusted Error

Resistive Load 3

Load Regulation

Max

16

Differential Nonlinearity (DNL)

Zero-Code Error

Offset Error

Full-Scale Error

Gain Error

OUTPUT CHARACTERISTICS2

Output Voltage Range

Typ

VREF

2 × VREF

2

10

1

80

80

40

25

2.5

2.4975

4

0.04

12

240

20

40

±5

100

125

25

0.7 × VLOGIC

2

2.5025

13

Gain = 2

Gain = 1

Guaranteed monotonic by design

All zeros loaded to DAC register

All ones loaded to DAC register

Gain = 2

Gain = 1

External reference; gain = 2

Internal reference; gain = 1

Of FSR/°C

DAC code = midscale; VDD = 5 V ± 10%

5 V ± 10%, DAC code = midscale; −30 mA ≤ IOUT ≤ 30 mA

3 V ± 10%, DAC code = midscale; −20 mA ≤ IOUT ≤ 20 mA

See Figure 27

Coming out of power-down mode; VDD = 5 V

V

ppm/°C

Ω

µV p-p

nV/√Hz

µV/mA

µV/mA

mA

µV/V

ppm

ppm

0.1 Hz to 10 Hz

At ambient; f = 10 kHz, CL = 10 nF

At ambient

At ambient

VDD ≥ 3 V

At ambient

First cycle

Additional cycles

±2

µA

Per pin

0.3 × VLOGIC

V

V

pF

Rev. A | Page 3 of 17

At ambient

�AD5686R-EP

Parameter

LOGIC OUTPUTS (SDO)2

Output Voltage

Low (VOL)

High (VOH)

Floating State Output

Capacitance

POWER REQUIREMENTS

VLOGIC

ILOGIC

VDD

VDD

IDD

Normal Mode9

All Power-Down Modes10

Enhanced Product

Min

Typ

Max

Unit

Test Conditions/Comments

0.4

V

V

pF

ISINK = 200 μA

ISOURCE = 200 μA

5.5

3

5.5

5.5

V

μA

V

V

0.7

1.3

4

6

mA

mA

μA

μA

VLOGIC − 0.4

4

1.62

2.7

VREF + 1.5

0.59

1.1

1

1

Gain = 1

Gain = 2

VIH = VDD, VIL = GND, VDD = 2.7 V to 5.5 V

Internal reference off

Internal reference on, at full scale

−40°C to +85°C

−55°C to +125°C

DC specifications tested with the outputs unloaded, unless otherwise noted. Upper dead band = 10 mV and exists only when VREF = VDD with gain = 1 or when VREF/2 =

VDD with gain = 2. Linearity calculated using a reduced code range of 256 to 65,280.

Guaranteed by design and characterization; not production tested.

3

Channel A and Channel B can have a combined output current of up to 15 mA. Similarly, Channel C and Channel D can have a combined output current of up to

15 mA up to a junction temperature of 135°C.

4

VDD = 5 V. The device includes current limiting that is intended to protect the device during temporary overload conditions. Junction temperature can be exceeded

during current limit. Operation above the specified maximum operation junction temperature may impair device reliability.

5

When drawing a load current at either rail, the output voltage headroom, with respect to that rail, is limited by the 25 Ω typical channel resistance of the output

device. For example, when sinking 1 mA, the minimum output voltage = 25 Ω × 1 mA = 25 mV (see Figure 27).

6

Initial accuracy presolder reflow is ±750 μV; output voltage includes the effects of preconditioning drift. See the AD5686R/AD5685R/AD5684R data sheet for more

information.

7

Reference is trimmed and tested at two temperatures and is characterized from −55°C to +125°C.

8

Reference temperature coefficient calculated as per the box method. See the AD5686R/AD5685R/AD5684R data sheet for further information.

9

Interface inactive. All DACs active. DAC outputs unloaded.

10

All DACs powered down.

2

Rev. A | Page 4 of 17

�Enhanced Product

AD5686R-EP

AC CHARACTERISTICS

VDD = 2.7 V to 5.5 V, RL = 2 kΩ to GND, CL = 200 pF to GND, 1.62 V ≤ VLOGIC ≤ 5.5 V, and all specifications TMIN to TMAX, unless otherwise noted.

Guaranteed by design and characterization, not production tested.

Table 2.

Parameter1

Output Voltage Settling Time

Slew Rate

Digital-to-Analog Glitch Impulse

Digital Feedthrough

Digital Crosstalk

Analog Crosstalk

DAC-to-DAC Crosstalk

Total Harmonic Distortion (THD)3

Output Noise Spectral Density (NSD)

Output Noise

Signal-to-Noise Ratio (SNR)

Spurious Free Dynamic Range (SFDR)

Signal-to-Noise-and-Distortion Ratio (SINAD)

Min

Typ

5

0.8

0.5

0.13

0.1

0.2

0.3

−80

300

6

90

83

80

Max

8

Unit

μs

V/μs

nV-sec

nV-sec

nV-sec

nV-sec

nV-sec

dB

nV/√Hz

μV p-p

dB

dB

dB

1

See the AD5686R/AD5685R/AD5684R data sheet.

Temperature range is −55°C to +125°C, typical at 25°C.

3

Digitally generated sine wave at 1 kHz.

2

Rev. A | Page 5 of 17

Test Conditions/Comments2

¼ to ¾ scale settling to ±2 LSB

1 LSB change around major carry

At ambient, bandwidth (BW) = 20 kHz, VDD = 5 V, fOUT = 1 kHz

DAC code = midscale, 10 kHz; gain = 2, internal reference

0.1 Hz to 10 Hz

At ambient, BW = 20 kHz, VDD = 5 V, fOUT = 1 kHz

At ambient, BW = 20 kHz, VDD = 5 V, fOUT = 1 kHz

At ambient, BW = 20 kHz, VDD = 5 V, fOUT = 1 kHz

�AD5686R-EP

Enhanced Product

TIMING CHARACTERISTICS

All input signals are specified with tR = tF = 1 ns/V (10% to 90% of VDD) and timed from a voltage level of (VIL + VIH)/2. See Figure 2.

VDD = 2.7 V to 5.5 V, 1.62 V ≤ VLOGIC ≤ 5.5 V, and VREF = 2.5 V. All specifications TMIN to TMAX, unless otherwise noted.

Table 3

Parameter1

SCLK Cycle Time

SCLK High Time

SCLK Low Time

SYNC to SCLK Falling Edge Setup Time

Data Setup Time

Data Hold Time

SCLK Falling Edge to SYNC Rising Edge

Minimum SYNC High Time

SYNC Rising Edge to SYNC Rising Edge (DAC Register Update/s)

SYNC Falling Edge to SCLK Fall Ignore

LDAC Pulse Width Low

SYNC Rising Edge to LDAC Rising Edge

SYNC Rising Edge to LDAC Falling Edge

LDAC Falling Edge to SYNC Rising Edge

Minimum Pulse Width Low

Pulse Activation Time

Power-Up Time2

E

E

E

E

E

E

E

E

E

E

E

E

1.62 V ≤ VLOGIC < 2.7 V

Min

Max

20

10

10

15

5

5

10

20

870

16

15

20

30

840

30

30

4.5

Symbol

t1

t2

t3

t4

t5

t6

t7

t8

t9

t10

t11

t12

t13

t14

t15

t16

E

2.7 V ≤ VLOGIC ≤ 5.5 V

Min

Max

20

10

10

10

5

5

10

20

830

10

15

20

30

800

30

30

4.5

1

Guaranteed by design and characterization; not production tested.

Time to exit power-down to normal mode of AD5686R-EP operation, SYNC rising edge to 90% of DAC midscale value, with output unloaded.

2

E

t10

t1

SCLK

t8

t3

t4

t2

t7

t14

SYNC

t5

SDIN

t6

DB23

t9

DB0

t11

t13

LDAC1

t12

LDAC2

VOUT

t15

t16

12975-002

RESET

1ASYNCHRONOUS LDAC UPDATE MODE.

2SYNCHRONOUS LDAC UPDATE MODE.

Figure 2. Serial Write Operation

Rev. A | Page 6 of 17

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

μs

�Enhanced Product

AD5686R-EP

DAISY-CHAIN AND READBACK TIMING CHARACTERISTICS

All input signals are specified with tR = tF = 1 ns/V (10% to 90% of VDD) and timed from a voltage level of (VIL + VIH)/2. See Figure 4

and Figure 5. VDD = 2.7 V to 5.5 V, 1.62 V ≤ VLOGIC ≤ 5.5 V, and VREF = 2.5 V. All specifications TMIN to TMAX, unless otherwise noted.

Table 4.

Parameter1

SCLK Cycle Time

SCLK High Time

SCLK Low Time

SYNC to SCLK Falling Edge

Data Setup Time

Data Hold Time

SCLK Falling Edge to SYNC Rising Edge

Minimum SYNC High Time

SDO Data Valid from SCLK Rising Edge

SYNC Rising Edge to SCLK Rising Edge

SYNC Rising Edge to SDO Disable

Symbol

t1

t2

t3

t4

t5

t6

t7

t8

t9

t10

t11

E

E

E

E

E

1

Min

66

33

33

33

5

5

15

60

1.62 V ≤ VLOGIC < 2.7 V

Max

Min

40

20

20

20

5

5

10

30

2.7 V ≤ VLOGIC ≤ 5.5 V

Max

45

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

30

15

60

10

60

Guaranteed by design and characterization; not production tested.

Circuit and Timing Diagrams

200µA

VOH (MIN)

CL

20pF

200µA

12975-003

TO OUTPUT

PIN

IOL

IOH

Figure 3. Load Circuit for Digital Output (SDO) Timing Specifications

t1

SCLK

24

48

t7

t2

t8

t3

t4

t10

SYNC

SDIN

t6

DB23

DB0

INPUT WORD FOR DAC N

DB23

DB0

t9

INPUT WORD FOR DAC N + 1

DB23

SDO

UNDEFINED

DB0

INPUT WORD FOR DAC N

Figure 4. Daisy-Chain Timing Diagram

Rev. A | Page 7 of 17

12975-004

t5

�AD5686R-EP

Enhanced Product

t1

SCLK

24

1

t8

t4

t3

24

1

t7

t2

t8

t10

SYNC

t6

t5

DB23

DB0

DB23

INPUT WORD SPECIFIES

REGISTER TO BE READ

DB0

NOP CONDITION

t9

DB23

SDO

t11

DB0

HI-Z

SELECTED REGISTER DATA

CLOCKED OUT

Figure 5. Readback Timing Diagram

Rev. A | Page 8 of 17

12975-005

SDIN

�Enhanced Product

AD5686R-EP

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 5.

Parameter

VDD to GND

VLOGIC to GND

VOUT to GND

VREF to GND

Digital Input Voltage to GND

Operating Temperature Range

Storage Temperature Range

Junction Temperature

16-Lead LFCSP, θJA Thermal Impedance,

θJA Airflow (4-Layer Board)

Reflow Soldering Peak Temperature,

Pb Free (J-STD-020)

Rating

−0.3 V to +7 V

−0.3 V to +7 V

−0.3 V to VDD + 0.3 V

−0.3 V to VDD + 0.3 V

−0.3 V to VLOGIC + 0.3 V

−55°C to +125°C

−65°C to +150°C

135°C

70°C/W

Stresses at or above those listed under Absolute Maximum

Ratings may cause permanent damage to the product. This is a

stress rating only; functional operation of the product at these

or any other conditions above those indicated in the operational

section of this specification is not implied. Operation beyond

the maximum operating conditions for extended periods may

affect product reliability.

ESD CAUTION

260°C

Rev. A | Page 9 of 17

�AD5686R-EP

Enhanced Product

13 RESET

14 RSTSEL

15 VREF

16 VOUTB

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

VOUTA 1

GND 2

VDD 3

12 SDIN

AD5686R-EP

11 SYNC

10 SCLK

9 VLOGIC

GAIN 8

LDAC 7

SDO 6

VOUTD 5

VOUTC 4

NOTES

1. THE EXPOSED PAD MUST BE TIED TO GND.

12975-006

TOP VIEW

(Not to Scale)

Figure 6. 16-Lead LFCSP Pin Configuration

Table 6. Pin Function Descriptions

Pin No.

1

2

3

Mnemonic

VOUTA

GND

VDD

4

5

6

VOUTC

VOUTD

SDO

7

LDAC

8

GAIN

9

10

VLOGIC

SCLK

11

SYNC

12

SDIN

13

RESET

E

Description

Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation.

Ground Reference Point for All Circuitry on the Device.

Power Supply Input. The AD5686R-EP can be operated from 2.7 V to 5.5 V, and the supply must be decoupled

with a 10 μF capacitor in parallel with a 0.1 μF capacitor to GND.

Analog Output Voltage from DAC C. The output amplifier has rail-to-rail operation.

Analog Output Voltage from DAC D. The output amplifier has rail-to-rail operation.

Serial Data Output. SDO can be used to daisy-chain a number of AD5686R-EP devices together, or it can be used

for readback. The serial data is transferred on the rising edge of SCLK and is valid on the falling edge of the clock.

LDAC can be operated in two modes, asynchronously and synchronously. Pulsing this pin low allows any or all

DAC registers to be updated if the input registers have new data. This allows all DAC outputs to update

simultaneously. This pin can also be tied permanently low.

Span Set Pin. When this pin is tied to GND, all four DAC outputs have a span from 0 V to VREF. If this pin is tied to

VLOGIC, all four DACs output a span of 0 V to 2 × VREF.

Digital Power Supply. Voltage ranges from 1.62 V to 5.5 V.

Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. Data

can be transferred at rates of up to 50 MHz.

Active Low Control Input. This is the frame synchronization signal for the input data. When SYNC goes low,

data is transferred in on the falling edges of the next 24 clocks.

Serial Data Input. This device has a 24-bit input shift register. Data is clocked into the register on the falling

edge of the serial clock input.

Asynchronous Reset Input. The RESET input is falling edge sensitive. When RESET is low, all LDAC pulses are

ignored. When RESET is activated, the input register and the DAC register are updated with zero scale or midscale,

depending on the state of the RSTSEL pin. If this pin is forced low at power-up, the power-on reset (POR) circuit

will not initialize the device correctly until this pin is released.

Power-On Reset Pin. Tying this pin to GND powers up all four DACs to zero scale. Tying this pin to VLOGIC powers

up all four DACs to midscale.

Reference Voltage. The AD5686R-EP has a common reference pin. When using the internal reference, this is the

reference output pin. When using an external reference, this is the reference input pin. The default for this pin

is as a reference output.

Analog Output Voltage from DAC B. The output amplifier has rail-to-rail operation.

Exposed Pad. The exposed pad must be tied to GND.

E

E

E

E

E

E

14

RSTSEL

15

VREF

16

17

VOUTB

EPAD

Rev. A | Page 10 of 17

E

E

�Enhanced Product

AD5686R-EP

TYPICAL PERFORMANCE CHARACTERISTICS

2.5020

DEVICE 1

DEVICE 2

DEVICE 3

DEVICE 4

DEVICE 5

2.5015

2.5010

VDD = 5V

VDD = 5V

TA = 25°C

T

VREF (V)

2.5005

2.5000

1

2.4995

2.4990

–20

0

20

40

60

80

100

120

TEMPERATURE (°C)

CH1 2µV

A CH1

160mV

Figure 10. Internal Reference Noise, 0.1 Hz to 10 Hz

Figure 7. Internal Reference Voltage (VREF) vs. Temperature

90

M1.0s

12975-112

2.4980

–40

12975-212

2.4985

2.5000

VDD = 5V

80

2.4999

VDD = 5V

TA = 25°C

70

VREF (V)

NUMBER OF UNITS

2.4998

60

50

40

30

2.4997

2.4996

2.4995

20

0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

4.0

4.5

5.0

TEMPERATURE DRIFT (ppm/°C)

2.4993

–0.005

12975-250

0

1400

–0.001

0.001

0.003

0.005

ILOAD (A)

Figure 11. VREF vs. Load Current (ILOAD)

Figure 8. Reference Output Temperature Drift Histogram

1600

–0.003

12975-113

2.4994

10

2.5002

TA = 25°C

VDD = 5V

TA = 25°C

D1

2.5000

1200

VREF (V)

NSD (nV/ Hz)

2.4998

1000

800

600

D3

2.4996

2.4994

400

2.4992

100

1k

10k

FREQUENCY (Hz)

100k

1M

12975-111

0

10

Figure 9. Internal Reference Noise Spectral Density (NSD) vs. Frequency

Rev. A | Page 11 of 17

2.4990

2.5

3.0

3.5

4.0

4.5

5.0

VDD (V)

Figure 12. VREF vs. Supply Voltage (VDD)

5.5

12975-117

D2

200

�Enhanced Product

10

8

8

6

6

4

4

ERROR (LSB)

10

2

0

–2

2

–6

–6

VDD = 5V

TA = 25°C

INTERNAL REFERENCE = 2.5V

20000

30000

40000

50000

60000

CODE

0

8

0.6

6

0.4

4

ERROR (LSB)

0.8

0.2

0

–0.2

–6

60000

CODE

4.0

4.5

5.0

INL

DNL

4.7

5.2

SUPPLY VOLTAGE (V)

Figure 17. INL Error and DNL Error vs. Supply Voltage

0.10

8

0.08

6

0.06

4

0.04

ERROR (% of FSR)

10

INL

DNL

–2

–4

0.02

0

FULL-SCALE ERROR

GAIN ERROR

–0.02

–0.04

–0.06

–6

VDD = 5V

INTERNAL REFERENCE = 2.5V

–10

–40

10

60

110

TEMPERATURE (°C)

12975-124

ERROR (LSB)

3.5

–8 TA = 25°C

INTERNAL REFERENCE = 2.5V

–10

2.7

3.2

3.7

4.2

Figure 14. Differential Nonlinearity (DNL) vs. Code

–8

3.0

–2

–0.6

0

2.5

0

–4

2

2.0

2

–0.4

12975-121

DNL (LSB)

10

50000

1.5

Figure 16. INL Error and DNL Error vs. VREF

1.0

40000

1.0

VREF (V)

Figure 13. Integral Nonlinearity (INL) vs. Code

V = 5V

–0.8 DD

TA = 25°C

INTERNAL REFERENCE = 2.5V

–1.0

0

10000

20000

30000

0.5

12975-125

10000

–8

–10

12975-126

0

VDD = 5V

TA = 25°C

–0.08 VDD = 5V

INTERNAL REFERENCE = 2.5V

–0.10

–40

–20

0

20

40

60

80

100

120

TEMPERATURE (°C)

Figure 18. Gain Error and Full-Scale Error vs. Temperature

Figure 15. INL Error and DNL Error vs. Temperature

Rev. A | Page 12 of 17

12975-127

–10

DNL

–2

–4

–8

INL

0

–4

12975-118

INL (LSB)

AD5686R-EP

�Enhanced Product

AD5686R-EP

0.10

1.2

0.8

0.6

ZERO-CODE ERROR

0.2

0

–40

–20

0

20

40

60

80

100

120

TEMPERATURE (°C)

0.06

0.05

0.04

0.03

0.02

0.01

0

–40

12975-128

OFFSET ERROR

0.07

0.08

0.08

TOTAL UNADJUSTED ERROR (% of FSR)

0.10

ERROR (% of FSR)

0.06

0.04

0.02

GAIN ERROR

0

FULL-SCALE ERROR

–0.04

5.2

SUPPLY VOLTAGE (V)

60

80

100

120

0.04

0.02

0

–0.02

–0.04

–0.06

–0.08

TA = 25°C

INTERNAL REFERENCE = 2.5V

3.2

3.7

4.2

4.7

5.2

SUPPLY VOLTAGE (V)

Figure 23. Total Unadjusted Error (TUE) vs. Supply Voltage, Gain = 1

Figure 20. Gain Error and Full-Scale Error vs. Supply Voltage

0

TOTAL UNADJUSTED ERROR (% of FSR)

1.5

1.0

0.5

ZERO-CODE ERROR

0

OFFSET ERROR

–0.5

–1.0

TA = 25°C

INTERNAL REFERENCE = 2.5V

–1.5

2.7

3.2

3.7

4.2

4.7

5.2

SUPPLY VOLTAGE (V)

12975-130

ERROR (mV)

40

0.06

–0.10

2.7

12975-129

–0.06

4.7

20

Figure 22. Total Unadjusted Error (TUE) vs. Temperature

0.10

–0.08 TA = 25°C

INTERNAL REFERENCE = 2.5V

–0.10

2.7

3.2

3.7

4.2

0

TEMPERATURE (°C)

Figure 19. Zero-Code Error and Offset Error vs. Temperature

–0.02

–20

12975-132

0.4

0.08

–0.01

–0.02

–0.03

–0.04

–0.05

–0.06

–0.07

–0.08

VDD = 5V

–0.09 T = 25°C

A

INTERNAL REFERENCE = 2.5V

–0.10

0

10000

20000

30000

40000

50000

60000 65535

CODE

Figure 24. Total Unadjusted Error (TUE) vs. Code

Figure 21. Zero-Code Error and Offset Error vs. Supply Voltage

Rev. A | Page 13 of 17

12975-133

ERROR (mV)

1.0

VDD = 5V

0.09 INTERNAL REFERENCE = 2.5V

12975-131

TOTAL UNADJUSTED ERROR (% of FSR)

VDD = 5V

1.4 INTERNAL REFERENCE = 2.5V

�AD5686R-EP

Enhanced Product

7

VDD = 5V

TA = 25°C

EXTERNAL

REFERENCE = 2.5V

25

VDD = 5V

6 TA = 25°C

GAIN = 2

INTERNAL

5 REFERENCE = 2.5V

20

0xFFFF

15

VOUT (V)

HITS

4

10

0xC000

3

0x8000

2

0x4000

1

0x0000

0

5

560

580

600

620

640

IDD (µA)

–2

–0.06

12975-135

540

–0.04

–0.02

0.02

0.04

0.06

LOAD CURRENT (A)

Figure 25. IDD Histogram with External Reference, 5 V

Figure 28. Source and Sink Capability at 5 V

5

VDD = 5V

30 T = 25°C

A

INTERNAL

REFERENCE = 2.5V

25

VDD = 3V

TA = 25°C

GAIN = 1

EXTERNAL

REFERENCE = 2.5V

4

3

0xFFFF

VOUT (V)

20

15

10

0xC000

2

0x8000

1

0x4000

0x0000

0

5

–1

1000

1020

1040

1060

1080

1100

1120

1140

IDD (µA)

–2

–60

12975-136

0

–40

–20

0

20

40

60

IOUT (mA)

12975-139

HITS

0

12975-138

–1

0

Figure 29. Source and Sink Capability at 3 V

Figure 26. IDD Histogram with Internal Reference, VREFOUT = 2.5 V, Gain = 2

1.0

1.4

0.8

0.6

1.2

0.4

CURRENT (mA)

SINKING 5V

0

–0.2

SOURCING 5V

–0.4

1.0

ZERO CODE

0.8

0.6

EXTERNAL REFERENCE, FULL-SCALE

0.4

–0.6

SOURCING 2.7V

0.2

–1.0

0

5

10

15

20

25

LOAD CURRENT (mA)

30

0

–40

10

60

TEMPERATURE (°C)

Figure 30. Supply Current vs. Temperature

Figure 27. Headroom/Footroom vs. Load Current

Rev. A | Page 14 of 17

110

12975-140

–0.8

12975-200

∆VOUT (V)

SINKING 2.7V

0.2

FULL SCALE

�Enhanced Product

4.0

3.5

AD5686R-EP

2.5008

DAC A

DAC B

DAC C

DAC D

2.5003

3.0

VOUT (V)

VOUT (V)

2.5

2.0

2.4998

1.5

60

80

2.4988

12975-141

VDD = 5V

0.5 TA = 25°C

INTERNAL REFERENCE = 2.5V

¼ TO ¾ SCALE

0

0

20

40

100

TIME (µs)

0

6

8

10

12

0.003

CH B

CH C

CH D

5

0.03

3

0.02

2

0.01

1

0

0

VDD (V)

4

VOUT AC-COUPLED (V)

0.002

0.04

0.001

0

–0.001

–1

15

10

TIME (µs)

–0.002

0

CH A

CH B

CH C

CH D

SYNC

10

15

20

25

TIME (µs)

Figure 32. Power-On Reset to 0 V

3

5

12975-145

5

12975-142

TA = 25°C

INTERNAL REFERENCE = 2.5V

–0.01

–10

–5

0

Figure 35. Analog Crosstalk, Channel A

T

GAIN = 2

2

VOUT (V)

GAIN = 1

1

0

–5

VDD = 5V

TA = 25°C

INTERNAL REFERENCE = 2.5V

0

5

TIME (µs)

10

Figure 33. Exiting Power-Down to Midscale

VDD = 5V

TA = 25°C

EXTERNAL REFERENCE = 2.5V

CH1 2µV

M1.0s

A CH1

802mV

Figure 36. 0.1 Hz to 10 Hz Output Noise Plot, External Reference

Rev. A | Page 15 of 17

12975-146

1

12975-143

VOUT (V)

6

Figure 34. Digital-to-Analog Glitch Impulse

CH A

CH B

CH C

CH D

VDD

0.05

4

TIME (µs)

Figure 31. Settling Time

0.06

2

12975-144

CHANNEL B

TA = 25°C

VDD = 5.25V

INTERNAL REFERENCE

CODE = 7FFF TO 8000

ENERGY = 0.227206nV-sec

2.4993

1.0

�AD5686R-EP

Enhanced Product

4.0

T

0nF

0.1nF

10nF

0.22nF

4.7nF

3.9

3.8

VDD = 5V

TA = 25°C

INTERNAL REFERENCE = 2.5V

VOUT (V)

3.7

1

3.6

3.5

3.4

3.3

3.2

VDD = 5V

TA = 25°C

INTERNAL REFERENCE = 2.5V

A CH1

802mV

1.600

1.605

1.610

1.615

1.620

1.625

1.630

TIME (ms)

Figure 40. Settling Time for Various Capacitive Loads

Figure 37. 0.1 Hz to 10 Hz Output Noise Plot, 2.5 V Internal Reference

1600

VDD = 5V

TA = 25°C

1400 INTERNAL REFERENCE = 2.5V

1.595

12975-150

M1.0s

3.0

1.590

12975-147

CH1 2µV

3.1

0

FULL-SCALE

MIDSCALE

ZERO-SCALE

–10

BANDWIDTH (dB)

NSD (nV/ Hz)

1200

1000

800

600

–20

–30

–40

400

100

1k

10k

100k

1M

FREQUENCY (Hz)

FREQUENCY (Hz)

VDD = 5V

TA = 25°C

INTERNAL REFERENCE = 2.5V

0

–20

–60

–80

–100

–120

–140

–160

0

2000 4000 6000 8000 10000 12000 14000 16000 18000 20000

FREQUENCY (Hz)

12975-149

THD (dBV)

–40

–180

100k

1M

10M

Figure 41. Multiplying Bandwidth, External Reference = 2.5 V, ±0.1 V p-p,

10 kHz to 10 MHz

Figure 38. Noise Spectral Density (NSD)

20

–60

10k

12975-148

0

10

VDD = 5V

TA = 25°C

EXTERNAL REFERENCE = 2.5V, ±0.1V p-p

12975-151

–50

200

Figure 39. Total Harmonic Distortion at 1 kHz

Rev. A | Page 16 of 17

�Enhanced Product

AD5686R-EP

OUTLINE DIMENSIONS

0.30

0.23

0.18

0.50

BSC

13

PIN 1

INDICATOR

16

1

12

1.75

1.60 SQ

1.45

EXPOSED

PAD

9

TOP VIEW

0.80

0.75

0.70

0.50

0.40

0.30

4

8

BOTTOM VIEW

0.05 MAX

0.02 NOM

COPLANARITY

0.08

0.20 REF

SEATING

PLANE

5

0.25 MIN

FOR PROPER CONNECTION OF

THE EXPOSED PAD, REFER TO

THE PIN CONFIGURATION AND

FUNCTION DESCRIPTIONS

SECTION OF THIS DATA SHEET.

COMPLIANT TO JEDEC STANDARDS MO-220-WEED-6.

08-16-2010-E

PIN 1

INDICATOR

3.10

3.00 SQ

2.90

Figure 42. 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ]

3 mm × 3 mm Body, Very Very Thin Quad

(CP-16-22)

Dimensions shown in millimeters

ORDERING GUIDE

Model1

AD5686RTCPZ-EP-RL7

1

Resolution

16 Bits

Temperature Range

−55°C to +125°C

Package Description

16-Lead LFCSP_WQ

Z = RoHS Compliant Part.

©2015–2016 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D12975-0-11/16(A)

Rev. A | Page 17 of 17

Package Option

CP-16-22

Branding

DNG

�