a

FEATURES

User Programmed Gains of 1 to 10,000

Low Gain Error: 0.02% Max

Low Gain TC: 5 ppm/�C Max

Low Nonlinearity: 0.001% Max

Low Offset Voltage: 25 �V

Low Noise 4 nV/√Hz (at 1 kHz) RTI

Gain Bandwidth Product: 25 MHz

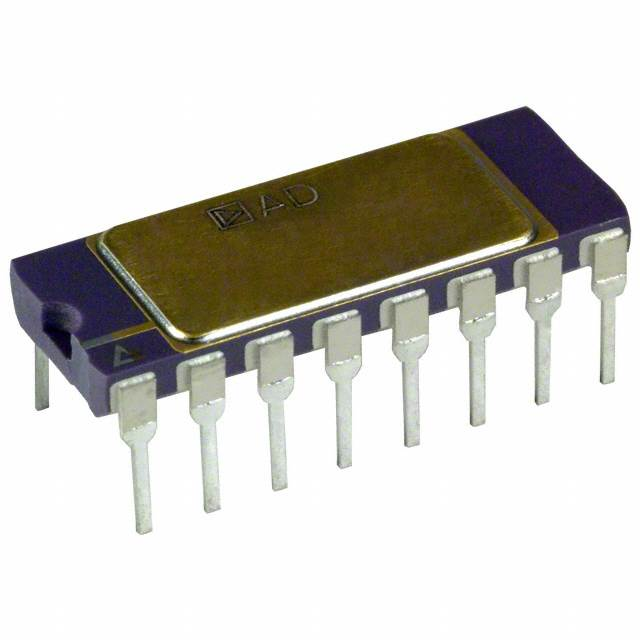

16-Lead Ceramic or Plastic DIP Package,

20-Terminal LCC Package

Standard Military Drawing Available

MlL-Standard Parts Available

Low Cost

Programmable Gain

Instrumentation Amplifier

AD625

FUNCTIONAL BLOCK DIAGRAM

50�

–INPUT

–

+

–

AD625

+

–GAIN

SENSE

10k�

SENSE

–GAIN

DRIVE

10k�

VB

+GAIN

DRIVE

–

OUTPUT

+

10k�

REFERENCE

+GAIN

SENSE

50�

+INPUT

10k�

–

+

–

+

PRODUCT DESCRIPTION

PRODUCT HIGHLIGHTS

The AD625 is a precision instrumentation amplifier specifically

designed to fulfill two major areas of application: 1) Circuits requiring nonstandard gains (i.e., gains not easily achievable with

devices such as the AD524 and AD624). 2) Circuits requiring a

low cost, precision software programmable gain amplifier.

1. The AD625 affords up to 16-bit precision for user selected

fixed gains from 1 to 10,000. Any gain in this range can be

programmed by 3 external resistors.

For low noise, high CMRR, and low drift the AD625JN is the

most cost effective instrumentation amplifier solution available.

An additional three resistors allow the user to set any gain from

1 to 10,000. The error contribution of the AD625JN is less than

0.05% gain error and under 5 ppm/°C gain TC; performance

limitations are primarily determined by the external resistors.

Common-mode rejection is independent of the feedback resistor

matching.

A software programmable gain amplifier (SPGA) can be configured with the addition of a CMOS multiplexer (or other switch

network), and a suitable resistor network. Because the ON

resistance of the switches is removed from the signal path, an

AD625 based SPGA will deliver 12-bit precision, and can be

programmed for any set of gains between 1 and 10,000, with

completely user selected gain steps.

2. A 12-bit software programmable gain amplifier can be configured using the AD625, a CMOS multiplexer and a resistor

network. Unlike previous instrumentation amplifier designs,

the ON resistance of a CMOS switch does not affect the gain

accuracy.

3. The gain accuracy and gain temperature coefficient of the

amplifier circuit are primarily dependent on the user selected

external resistors.

4. The AD625 provides totally independent input and output

offset nulling terminals for high precision applications. This

minimizes the effects of offset voltage in gain-ranging

applications.

5. The proprietary design of the AD625 provides input voltage

noise of 4 nV/√Hz at 1 kHz.

6. External resistor matching is not required to maintain high

common-mode rejection.

For the highest precision the AD625C offers an input offset

voltage drift of less than 0.25 µV/°C, output offset drift below

15 µV/°C, and a maximum nonlinearity of 0.001% at G = 1. All

grades exhibit excellent ac performance; a 25 MHz gain bandwidth product, 5 V/µs slew rate and 15 µs settling time.

The AD625 is available in three accuracy grades (A, B, C) for

industrial (–40°C to +85°C) temperature range, two grades (J,

K) for commercial (0°C to +70°C) temperature range, and one

(S) grade rated over the extended (–55°C to +125°C) temperature range.

REV. D

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

World Wide Web Site: http://www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2000

�AD625–SPECIFICATIONS

Model

GAIN

Gain Equation

Gain Range

Gain Error1

Nonlinearity, Gain = 1-256

Gain>256

Gain vs. Temp. Gain 5

+

VB

–

50�A

50�A

+VS

FD333

A1

A2

C3

10k�

C4

FD333

SENSE

+IN

2k�

10k�

GAIN

DRIVE

50�

Q1, Q3

–IN

50�A

GAIN

DRIVE

RF

RF

RG

GAIN

SENSE

10k�

50�

Q2, Q4

GAIN

SENSE

10k�

RF

2N5952

VO

RG

REF

AD625

VOUT

RF

+IN

–IN

2k�

FD333

2N5952

50�A

FD333

–VS

–VS

Figure 26c. Input Protection Circuit

Figure 25. Simplified Circuit of the AD625

–8–

REV. D

�AD625

Any resistors in series with the inputs of the AD625 will degrade

the noise performance. For this reason the circuit in Figure 26b

should be used if the gains are all greater than 5. For gains less

than 5, either the circuit in Figure 26a or in Figure 26c can be

used. The two 1.4 kΩ resistors in Figure 26a will degrade the

noise performance to:

4 kTRext +(4 nV/ Hz )2 = 7.9 nV / Hz

300

200

100

10k 20k 30k 40k 50k 60k

FEEDBACK RESISTANCE – �

RESISTOR PROGRAMMABLE GAIN AMPLIFIER

In the resistor-programmed mode (Figure 27), only three external resistors are needed to select any gain from 1 to 10,000.

Depending on the application, discrete components or a

pretrimmed network can be used. The gain accuracy and gain

TC are primarily determined by the external resistors since the

AD625C contributes less than 0.02% to gain error and under

5 ppm/°C gain TC. The gain sense current is insensitive to

common-mode voltage, making the CMRR of the resistor programmed AD625 independent of the match of the two feedback

resistors, RF.

RTO OFFSET VOLTAGE DRIFT

RG

+GAIN

SENSE

RTI NULL

1

16

2

15

3

RTO

14 NULL

4

13

+VS

RTI NULL

+GAIN DRIVE

A1

5

A2

NC 6

REF

–VS 8

10k�

AD625

A3

10k�

RTO

NULL

–GAIN DRIVE

VOUT

10

9 +VS

Figure 27. AD625 in Fixed Gain Configuration

A list of standard resistors which can be used to set some common gains is shown in Table I.

20k�

50k�

10k

1

10

100

1k

FEEDBACK RESISTANCE – �

RF

RG

20 kΩ

19.6 kΩ

20 kΩ

20 kΩ

20 kΩ

19.6 kΩ

20 kΩ

20.5 kΩ

19.6 kΩ

19.6 kΩ

20 kΩ

19.6 kΩ

20 kΩ

19.6 kΩ

20 kΩ

20 kΩ

19.6 kΩ

19.6 kΩ

19.6 kΩ

∞

39.2 kΩ

10 kΩ

4.42 kΩ

2.1 kΩ

806 Ω

402 Ω

205 Ω

78.7 Ω

39.2 Ω

13.3 kΩ

5.62 kΩ

2.67 kΩ

1.27 kΩ

634 Ω

316 Ω

154 Ω

76.8 Ω

38.3 Ω

SENSE TERMINAL

The sense terminal is the feedback point for the AD625 output

amplifier. Normally it is connected directly to the output. If

heavy load currents are to be drawn through long leads, voltage

drops through lead resistance can cause errors. In these instances the sense terminal can be wired to the load thus putting

For single gain applications, only one offset null adjust is necessary; in these cases the RTI null should be used.

REV. D

FREQUENCY – Hz

MULTIPLYING FACTOR

1

2

5

10

20

50

100

200

500

1000

4

8

16

32

64

128

256

512

1024

–GAIN

SENSE

10k�

2

GAIN

11

10k�

7

12

3

10k�

Table I. Common Gains Nominally Within �0.5% Error

Using Standard 1% Resistors

RF

–INPUT

100k

4

BANDWIDTH

Figure 28. RTO Noise, Offset, Drift and Bandwidth vs.

Feedback Resistance Normalized to 20 kΩ

2RF

+1

RG

+INPUT

2

1M

1

10k 20k 30k 40k 50k 60k

FEEDBACK RESISTANCE – �

As previously stated each RF provides feedback to the input

stage and sets the unity gain transconductance. These feedback

resistors are provided by the user. The AD625 is tested and

specified with a value of 20 kΩ for RF. Since the magnitude of

RTO errors increases with increasing feedback resistance, values

much above 20 kΩ are not recommended (values below 10 kΩ

for RF may lead to instability). Refer to the graph of RTO noise,

offset, drift, and bandwidth (Figure 28) when selecting the

feedback resistors. The gain resistor (RG) is determined by the

formula RG = 2 RF/(G – l).

RF

5

3

10k 20k 30k 40k 50k 60k

FEEDBACK RESISTANCE – �

6

Selecting Resistor Values

G=

RTO OFFSET VOLTAGE

MULTIPLYING FACTOR

VOLTAGE NOISE – nV Hz

RTO NOISE

–9–

�AD625

the I × R drops “inside the loop” and virtually eliminating this

error source.

GND VDD VSS

Typically, IC instrumentation amplifiers are rated for a full ± 10

volt output swing into 2 kΩ. In some applications, however, the

need exists to drive more current into heavier loads. Figure 29

shows how a high-current booster may be connected “inside the

loop” of an instrumentation amplifier. By using an external

power boosting circuit, the power dissipated by the AD625 will

remain low, thereby, minimizing the errors induced by selfheating. The effects of nonlinearities, offset and gain inaccuracies of the buffer are reduced by the loop gain of the AD625’s

output amplifier.

+VS

A1

EN

SENSE

AD7502

VS 39k�

SENSE

AD589

VOUT

–VS

REFERENCE

VREF

+VS

1.2V

RF

RG

AD625

–IN

+VS

VIN+

+IN

A0

0.01�F

R3

20k�

RFB

AD625

X1

RF

DATA

INPUTS

RI

VIN–

MSB

LSB

OUT 1

OUT 2

AD7524

8-BIT DAC

CS

REFERENCE

+VS

C1

1/2

AD712

R4

10k�

1/2

AD712

WR

–VS

R5

2k�

5k�

–VS

Figure 29. AD625 /Instrumentation Amplifier with Output

Current Booster

Figure 30. Software Controllable Offset

REFERENCE TERMINAL

An instrumentation amplifier can be turned into a voltage-tocurrent converter by taking advantage of the sense and reference

terminals as shown in Figure 31.

The reference terminal may be used to offset the output by up

to ± 10 V. This is useful when the load is “floating” or does not

share a ground with the rest of the system. It also provides a

direct means of injecting a precise offset. However, it must be

remembered that the total output swing is ± 10 volts, from

ground, to be shared between signal and reference offset.

VIN+

SENSE

RF

The AD625 reference terminal must be presented with nearly

zero impedance. Any significant resistance, including those

caused by PC layouts or other connection techniques, will increase the gain of the noninverting signal path, thereby, upsetting the common-mode rejection of the in-amp. Inadvertent

thermocouple connections created in the sense and reference

lines should also be avoided as they will directly affect the output offset voltage and output offset voltage drift.

RG

AD625

+VX–

R1

RF

VIN–

IL

AD711

LOAD

Figure 31. Voltage-to-Current Converter

In the AD625 a reference source resistance will unbalance the

CMR trim by the ratio of 10 kΩ/RREF. For example, if the reference source impedance is 1 Ω, CMR will be reduced to 80 dB

(10 kΩ/1 Ω = 80 dB). An operational amplifier may be used to

provide the low impedance reference point as shown in Figure

30. The input offset voltage characteristics of that amplifier will

add directly to the output offset voltage performance of the

instrumentation amplifier.

By establishing a reference at the “low” side of a current setting

resistor, an output current may be defined as a function of input

voltage, gain and the value of that resistor. Since only a small

current is demanded at the input of the buffer amplifier A1, the

forced current IL will largely flow through the load. Offset and

drift specifications of A2 must be added to the output offset and

drift specifications of the In-Amp.

The circuit of Figure 30 also shows a CMOS DAC operating in

the bipolar mode and connected to the reference terminal to

provide software controllable offset adjustments. The total offset

range is equal to ± (VREF/2 × R5/R4), however, to be symmetrical about 0 V R3 = 2 × R4.

The offset per bit is equal to the total offset range divided by 2N,

where N = number of bits of the DAC. The range of offset for

Figure 30 is ± 120 mV, and the offset is incremented in steps of

0.9375 mV/LSB.

INPUT AND OUTPUT OFFSET VOLTAGE

Offset voltage specifications are often considered a figure of

merit for instrumentation amplifiers. While initial offset may be

adjusted to zero, shifts in offset voltage due to temperature

variations will cause errors. Intelligent systems can often correct

for this factor with an autozero cycle, but this requires extra

circuitry.

–10–

REV. D

�AD625

Offset voltage and offset voltage drift each have two components: input and output. Input offset is that component of offset

that is generated at the input stage. Measured at the output it is

directly proportional to gain, i.e., input offset as measured at the

output at G = 100 is 100 times greater than that measured at

G = 1. Output offset is generated at the output and is constant

for all gains.

in distributed stray capacitances. In many applications shielded

cables are used to minimize noise. This technique can create

+VS

+INPUT

SENSE

RF

100�

AD711

The input offset and drift are multiplied by the gain, while the

output terms are independent of gain, therefore, input errors

dominate at high gains and output errors dominate at low gains.

The output offset voltage (and drift) is normally specified at

G = 1 (where input effects are insignificant), while input offset

(and drift) is given at a high gain (where output effects are negligible). All input-related parameters are specified referred to the

input (RTI) which is to say that the effect on the output is “G”

times larger. Offset voltage vs. power supply is also specified as

an RTI error.

RF

–INPUT

REFERENCE

–VS

Figure 32. Common-Mode Shield Driver

common-mode rejection errors unless the shield is properly

driven. Figures 32 and 33 show active data guards which are

configured to improve ac common-mode rejection by “bootstrapping” the capacitances of the input cabling, thus minimizing differential phase shift.

By separating these errors, one can evaluate the total error independent of the gain. For a given gain, both errors can be combined to give a total error referred to the input (RTI) or output

(RTO) by the following formula:

+INPUT

+VS

AD712

100�

SENSE

RF

Total Error RTI = input error + (output error/gain)

AD625

RG

Total Error RTO = (Gain × input error) + output error

100�

The AD625 provides for both input and output offset voltage

adjustment. This simplifies nulling in very high precision applications and minimizes offset voltage effects in switched gain

applications. In such applications the input offset is adjusted

first at the highest programmed gain, then the output offset is

adjusted at G = 1. If only a single null is desired, the input offset

null should be used. The most additional drift when using only

the input offset null is 0.9 µV/°C, RTO.

COMMON-MODE REJECTION

Common-mode rejection is a measure of the change in output

voltage when both inputs are changed by equal amounts. These

specifications are usually given for a full-range input voltage

change and a specified source imbalance.

In an instrumentation amplifier, degradation of common-mode

rejection is caused by a differential phase shift due to differences

RF

–VS

–VS

Figure 33. Differential Shield Driver

GROUNDING

In order to isolate low level analog signals from a noisy digital

environment, many data-acquisition components have two or

more ground pins. These grounds must eventually be tied together at one point. It would be convenient to use a single

ground line, however, current through ground wires and pc runs

of the circuit card can cause hundreds of millivolts of error.

Therefore, separate ground returns should be provided to minimize the current flow from the sensitive points to the system

ground (see Figure 34). Since the AD625 output voltage is

developed with respect to the potential on the reference terminal, it can solve many grounding problems.

STATUS

AD583

SAMPLE

AND

HOLD

AD625

–VS

–VS

+VS

ANALOG

OUT

AD574A

+VS

HOLD

CAP

A/D

CONVERTER

VLOGIC

+VS

–VS

+VS –VS

DIGITAL

COMMON

ANALOG POWER

GROUND

Figure 34. Basic Grounding Practice for a Data Acquisition System

REV. D

VOUT

REFERENCE

–INPUT

AD7502

INPUT

SIGNAL

VOUT

AD625

RG

–11–

�AD625

GROUND RETURNS FOR BIAS CURRENTS

Input bias currents are those currents necessary to bias the input

transistors of a dc amplifier. There must be a direct return path

for these currents, otherwise they will charge external capacitances, causing the output to drift uncontrollably or saturate.

Therefore, when amplifying “floating” input sources such as

transformers, or ac-coupled sources, there must be a dc path

from each input to ground as shown in Figure 35.

high thermoelectric potential (about 35 µV°C). This means that

care must be taken to insure that all connections (especially

those in the input circuit of the AD625) remain isothermal. This

includes the input leads (1, 16) and the gain sense lines (2, 15).

These pins were chosen for symmetry, helping to desensitize the

input circuit to thermal gradients. In addition, the user should

also avoid air currents over the circuitry since slowly fluctuating

GND VDD VSS

+VS

SENSE

RF

RG

AD625

+VS

VOUT

15

RF

16

LOAD

AD7502

REFERENCE

TO POWER

SUPPLY

GROUND

–VS

Figure 35a. Ground Returns for Bias Currents with

Transformer Coupled Inputs

10 VOUT

AD625

9

14

+

VIN

–

0.1�F LOW

LEAKAGE

13

1k�

–VS

11

12

AD711

+VS

SENSE

RF

RG

AD625

VDD

VOUT

VSS

RF

LOAD

AD7510DIKD

GND

REFERENCE

200�s

TO POWER

SUPPLY

GROUND

–VS

ZERO PULSE

A1

A2

A3

A4

Figure 36. Auto-Zero Circuit

Figure 35b. Ground Returns for Bias Currents with

Thermocouple Input

+VS

SENSE

RF

RG

AD625

VOUT

RF

LOAD

REFERENCE

100k�

100k�

–VS

TO POWER

SUPPLY

GROUND

Figure 35c. Ground Returns for Bias Currents with AC

Coupled Inputs

thermocouple voltages will appear as “flicker” noise. In SPGA

applications relay contacts and CMOS mux leads are both

potential sources of additional thermocouple errors.

The base emitter junction of an input transistor can rectify out

of band signals (i.e., RF interference). When amplifying small

signals, these rectified voltages act as small dc offset errors. The

AD625 allows direct access to the input transistors’ bases and

emitters enabling the user to apply some first order filtering to

these unwanted signals. In Figure 37, the RC time constant

should be chosen for desired attenuation of the interfering signals.

In the case of a resistive transducer, the capacitance alone working against the internal resistance of the transducer may suffice.

RG

RF

R

FILTER

CAP

AUTOZERO CIRCUITS

In many applications it is necessary to maintain high accuracy.

At room temperature, offset effects can be nulled by the use of

offset trimpots. Over the operating temperature range, however,

offset nulling becomes a problem. For these applications the

autozero circuit of Figure 36 provides a hardware solution.

C

+IN

+GAIN SENSE

RTI NULL

RF

R

+IN

OTHER CONSIDERATIONS

+GAIN DRIVE

One of the more overlooked problems in designing ultralowdrift dc amplifiers is thermocouple induced offset. In a circuit

comprised of two dissimilar conductors (i.e., copper, kovar), a

current flows when the two junctions are at different temperatures. When this circuit is broken, a voltage known as the

“Seebeck” or thermocouple emf can be measured. Standard IC

lead material (kovar) and copper form a thermocouple with a

16

2

15

3

RTO

14 NULL

4

13

A1

5

A2

NC 6

REF

C

–IN

–GAIN SENSE

1

+V

RTI NULL

FILTER

CAP

–IN

11

10k�

7

–VS 8

12

10k�

AD625

RTO

NULL

–GAIN DRIVE

SENSE

10k�

A3

10k�

VOUT

10

VOUT

9 +VS

Figure 37. Circuit to Attenuate RF Interference

–12–

REV. D

�AD625

These capacitances may also be incorporated as part of the

external input protection circuit (see section on Input Protection). As a general practice every effort should be made to

match the extraneous capacitance at Pins 15 and 2, and Pins 1

and 16, to preserve high ac CMR.

–GAIN

SENSE

20k�

CS-OUT

COUT

An SPGA provides the ability to externally program precision

gains from digital inputs. Historically, the problem in systems

requiring electronic switching of gains has been the ON resistance (RON) of the multiplexer, which appears in series with the

gain setting resistor RG. This can result in substantial gain errors

and gain drifts. The AD625 eliminates this problem by making

the gain drive and gain sense pins available (Pins 2, 15, 5, 12;

see Figure 39). Consequently the multiplexer’s ON resistance is

removed from the signal current path. This transforms the ON

resistance error into a small nullable offset error. To clarify this

point, an error budget analysis has been performed in Table II

based on the SPGA configuration shown in Figure 39.

AD7502

TTL/DTL TO CMOS LEVEL TRANSLATOR

A0

DECODER/DRIVER

VDD

A1

GND

IOUT

–

VIN

+

3.9k�

975k�

12-BIT

DAS

VS

650k�

975k�

RON

IOUT

10k�

10k�

IS

CS

CS-OUT

COUT

–GAIN

DRIVE

15.6k�

RON

SOFTWARE PROGRAMMABLE GAIN AMPLIFIER

VSS

AD625

–INPUT

10k�

IS

CS

3.9k�

15.6k�

+GAIN

DRIVE

10k�

20k� +GAIN

SENSE

+INPUT

Figure 39. SPGA with Multiplexer Error Sources

Figure 39 shows a complete SPGA feeding a 12-bit DAS with a

0 V–10 V input range. This configuration was used in the error

budget analysis shown in Table II. The gain used for the RTI

calculations is set at 16. As the gain is changed, the ON resistance of the multiplexer and the feedback resistance will change,

which will slightly alter the values in the table.

EN

Table II. Errors Induced by Multiplexer to an SPGA

3.9k� 975�

20k�

650�

975� 3.9k�

15.6k�

15.6k�

+INPUT

+GAIN

SENSE

RTI NULL

20k�

–INPUT

1

16

2

15

3

14

4

13

–GAIN

SENSE

RTO NULL

Specifications

AD625C

AD7520KN Calculation

RTI Offset

Voltage

Gain Sense Switch

Offset

Resistance

Current

170 Ω

40 nA

40 nA × 170 Ω =

6.8 µV

6.8 µV

RTI Offset

Voltage

Gain Sense Differential

Current

Switch

60 nA

Resistance

6.8 Ω

60 nA × 6.8 Ω =

0.41 µV

0.41 µV

–VS

+VS

RTI NULL

+GAIN DRIVE

A1

5

A2

NC 6

REF

12

RTO NULL

–GAIN DRIVE

11

10k�

7

–VS 8

10k�

AD625

10k�

10k�

VOUT

A3

9

RG

+1=

Differential 2 (0.2 nA × 20 kΩ)

Leakage

= 8 µV/16

Current (IS)2

+0.2 nA

–0.2 nA

RTO Offset Feedback

Voltage

Resistance

20 kΩ1

Differential

Leakage

Current

(IOUT)2

+1 nA

–1 nA

+VS

Figure 38 shows an AD625 based SPGA with possible gains of

1, 4, 16, 64. RG equals the resistance between the gain sense

lines (Pins 2 and 15) of the AD625. In Figure 38, RG equals

the sum of the two 975 Ω resistors and the 650 Ω resistor, or

2600 Ω. RF equals the resistance between the gain sense and the

gain drive pins (Pins 12 and 15, or Pins 2 and 5), that is RF

equals the 15.6 kΩ resistor plus the 3.9 kΩ resistor, or 19.5 kΩ.

The gain, therefore equals:

2RF

RTO Offset Feedback

Voltage

Resistance

20 kΩ1

10

Figure 38. SPGA in a Gain of 16

2(19.5 kΩ)

+1=16

(2.6 kΩ)

As the switches of the differential multiplexer proceed synchronously, RG and RF change, resulting in the various programmed

gain settings.

REV. D

Induced

Error

2 (1 nA × 20 kΩ)

= 40 µV/16

Total error induced by a typical CMOS multiplexer

to an SPGA at +25°C

Voltage Offset

Induced RTI

0.5 µV

2.5 µV

10.21 �A

NOTES

1

The resistor for this calculation is the user-provided feedback resistance (R F).

20 kΩ is recommended value (see Resistor Programmable Gain Amplifier section).

2

The leakage currents (I S and IOUT ) will induce an offset voltage, however, the offset

will be determined by the difference between the leakages of each “half’’ of the

differential multiplexer. The differential leakage current is multiplied by the

feedback resistance (see Note 1), to determine offset voltage. Because differential

leakage current is not a parameter specified on multiplexer data sheets, the most

extreme difference (one most positive and one most negative) was used for the

calculations in Table II. Typical performance will be much better.

**The frequency response and settling will be affected by the ON resistance and

internal capacitance of the multiplexer. Figure 40 shows the settling time vs.

ON resistance at different gain settings for an AD625 based SPGA.

**Switch resistance and leakage current errors can be reduced by using relays.

–13–

�AD625

3) Begin all calculations with G0 = 1 and RF0 = 0.

1000

800

RF1 = (20 kΩ – RF0) (1–1/4): RF0 = 0 ∴ RF1 = 15 kΩ

400

RON = 1k�

RF2 = [20 kΩ – (RF0 + RF1)] (1–4/16):

SETTLING TIME – �s

200

RF0 + RF1 = 15 kΩ ∴ RF2 = 3.75 kΩ

100

80

RF3 = [20 kΩ – (RF0 + RF1 + RF2)] (1–16/64):

RON = 500�

40

RF0 + RF1 + RF2 = 18.75 kΩ ∴ RF3 = 937.5 Ω

RON = 200�

20

10

8

4) The center resistor (RG of the highest gain setting), is determined last. Its value is the remaining resistance of the 40 kΩ

string, and can be calculated with the equation:

RON = 0�

4

2

1

M

1

4

16

64

GAIN

256

1024

RG = (40 kΩ – 2 ∑ RF j )

j =0

4096

RG = 40 kΩ – 2 (RF0 + RF1 + RF2 + RF3 )

40 kΩ – 39.375 kΩ = 625 Ω

Figure 40. Time to 0.01% of a 20 V Step Input for

SPGA with AD625

DETERMINING SPGA RESISTOR NETWORK VALUES

The individual resistors in the gain network can be calculated

sequentially using the formula given below. The equation determines the resistors as labeled in Figure 41. The feedback resistors and the gain setting resistors are interactive, therefore; the

formula must be a series where the present term is dependent on

the preceding term(s). The formula

RFi + 1 = (20 kΩ –

1

Gi

j =0

Gi = 1

∑ RF j ) (1 –

)

G0 = 1

RF0 = 0

can be used to calculate the necessary feedback resistors for any

set of gains. This formula yields a network with a total resistance

of 40 kΩ. A dummy variable (j) serves as a counter to keep a

running total of the preceding feedback resistors. To illustrate

how the formula can be applied, an example similar to the

calculation used for the resistor network in Figure 38 is examined below.

5) If different resistor values are desired, all the resistors in the

network can be scaled by some convenient factor. However,

raising the impedance will increase the RTO errors, lowering

the total network resistance below 20 kΩ can result in amplifier instability. More information on this phenomenon is

given in the RPGA section of the data sheet. The scale factor

will not affect the unity gain feedback resistors. The resistor

network in Figure 38 has a scaling factor of 650/625 = 1.04,

if this factor is used on RF1, RF2, RF3, and RG, then the resistor values will match exactly.

6) Round off errors can be cumulative, therefore, it is advised to

carry as many significant digits as possible until all the values

have been calculated.

AD75xx

TO GAIN SENSE

(PIN 2)

1) Unity gain is treated as a separate case. It is implemented

with separate 20 kΩ feedback resistors as shown in Figure 41.

It is then ignored in further calculations.

2) Before making any calculations it is advised to draw a resistor

network similar to the network in Figure 41. The network

will have (2 × M) + 1 resistors, where M = number of gains.

For Figure 38 M = 3 (4, 16, 64), therefore, the resistor string

will have seven resistors (plus the two 20 kΩ “side” resistors

for unity gain).

–14–

RF2

20k�

RFN

RFG

RFN

TO GAIN SENSE

(PIN 15)

RF2

20k�

RF1

CONNECT IF UNITY

GAIN IS DESIRED

TO GAIN DRIVE

(PIN 5)

CONNECT IF UNITY

GAIN IS DESIRED

TO GAIN DRIVE

(PIN 12)

Figure 41. Resistors for a Gain Setting Network

REV. D

�AD625

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

0.430

(10.922)

0.755 (19.18)

0.745 (18.93)

16

9

1

8

0.040R 16

0.310 �0.01

7.874 �0.254)

0.26 (6.61)

0.24 (6.1)

PIN 1

0.17 (4.32)

MAX

0.175 (4.45)

SEATING

PLANE

0.12 (3.05)

0.02 (0.508) 0.015 (2.67) 0.065 (1.66)

0.015 (0.381) 0.095 (2.42) 0.045 (1.15)

9

0.265 0.290 �0.010

(6.73) (7.37 �0.254)

1

0.306 (7.78)

0.294 (7.47)

8

PIN 1

0.800 �0.010

20.32 �0.254

0.14 (3.56)

0.12 (3.05)

0.095 (2.41)

0.012 (0.305)

0.008 (0.203)

0.125 (3.175)

MIN

0.047 �0.007

(1.19 �0.18)

0.035 �0.01

(0.889 �0.254)

0.300

(7.62)

REF

0.085 (2.159)

C00780c–0–6/00 (rev. D)

16-Lead Ceramic DIP (D-16)

16-Lead Plastic DIP (N-16)

0.180 �0.03

(4.57 �0.762)

+0.003

–0.002

+0.076

0.43

–0.05

0.017

0.700 (17.78) BSC

SEATING

PLANE

0.010 �0.002

(0.254 �0.05)

0.100 (254)

BSC

20-Terminal Leadless Chip Carrier (E-20A)

0.082 �0.018

(2.085 �0.455)

0.350 �0.008

(8.89 �0.20) SQ

3

4

19

18 20

1

0.050

(1.27)

BOTTOM

VIEW

14

13

0.20 � 45°

(0.51 � 45°)

REF

0.025 �0.003

(0.635 �0.075)

8

9

PRINTED IN U.S.A.

0.040 � 45°

(1.02 � 45°)

REF 3 PLCS

REV. D

–15–

�