a

LF–2.7 GHz

RF/IF Gain and Phase Detector

AD8302

FEATURES

Measures Gain/Loss and Phase up to 2.7 GHz

Dual Demodulating Log Amps and Phase Detector

Input Range –60 dBm to 0 dBm in a 50 ⍀ System

Accurate Gain Measurement Scaling (30 mV/dB)

Typical Nonlinearity < 0.5 dB

Accurate Phase Measurement Scaling (10 mV/Degree)

Typical Nonlinearity < 1 Degree

Measurement/Controller/Level Comparator Modes

Operates from Supply Voltages of 2.7 V–5.5 V

Stable 1.8 V Reference Voltage Output

Small Signal Envelope Bandwidth from DC to 30 MHz

APPLICATIONS

RF/IF PA Linearization

Precise RF Power Control

Remote System Monitoring and Diagnostics

Return Loss/VSWR Measurements

Log Ratio Function for AC Signals

PRODUCT DESCRIPTION

The AD8302 is a fully integrated system for measuring gain/loss

and phase in numerous receive, transmit, and instrumentation

applications. It requires few external components and a single

supply of 2.7 V–5.5 V. The ac-coupled input signals can range

from –60 dBm to 0 dBm in a 50 Ω system, from low frequencies

up to 2.7 GHz. The outputs provide an accurate measurement

of either gain or loss over a ± 30 dB range scaled to 30 mV/dB,

and of phase over a 0°–180° range scaled to 10 mV/degree.

Both subsystems have an output bandwidth of 30 MHz, which

may optionally be reduced by the addition of external filter

capacitors. The AD8302 can be used in controller mode to

force the gain and phase of a signal chain toward predetermined

setpoints.

The AD8302 comprises a closely matched pair of demodulating

logarithmic amplifiers, each having a 60 dB measurement range.

By taking the difference of their outputs, a measurement of

the magnitude ratio or gain between the two input signals is

available. These signals may even be at different frequencies,

allowing the measurement of conversion gain or loss. The AD8302

may be used to determine absolute signal level by applying the

unknown signal to one input and a calibrated ac reference signal

to the other. With the output stage feedback connection disabled, a comparator may be realized, using the setpoint pins

MSET and PSET to program the thresholds.

REV. B

FUNCTIONAL BLOCK DIAGRAM

AD8302

VIDEO OUTPUT – A

INPA

OFSA

MFLT

+

+

–

VMAG

–

60dB LOG AMPS

(7 DETECTORS)

MSET

PHASE

DETECTOR

COMM

PSET

OFSB

INPB

–

60dB LOG AMPS

(7 DETECTORS)

VPHS

+

PFLT

VIDEO OUTPUT – B

1.8V

VPOS

BIAS

x3

VREF

The signal inputs are single-ended, allowing them to be matched

and connected directly to a directional coupler. Their input

impedance is nominally 3 kΩ at low frequencies.

The AD8302 includes a phase detector of the multiplier type,

but with precise phase balance driven by the fully limited signals

appearing at the outputs of the two logarithmic amplifiers.

Thus, the phase accuracy measurement is independent of signal

level over a wide range.

The phase and gain output voltages are simultaneously available

at loadable ground referenced outputs over the standard output

range of 0 V to 1.8 V. The output drivers can source or sink up

to 8 mA. A loadable, stable reference voltage of 1.8 V is available for precise repositioning of the output range by the user.

In controller applications, the connection between the gain

output pin VMAG and the setpoint control pin MSET is broken.

The desired setpoint is presented to MSET and the VMAG

control signal drives an appropriate external variable gain device.

Likewise, the feedback path between the phase output pin VPHS

and its setpoint control pin PSET may be broken to allow

operation as a phase controller.

The AD8302 is fabricated on Analog Devices’ proprietary, high

performance 25 GHz SOI complementary bipolar IC process. It is

available in a 14-lead TSSOP package and operates over a –40°C

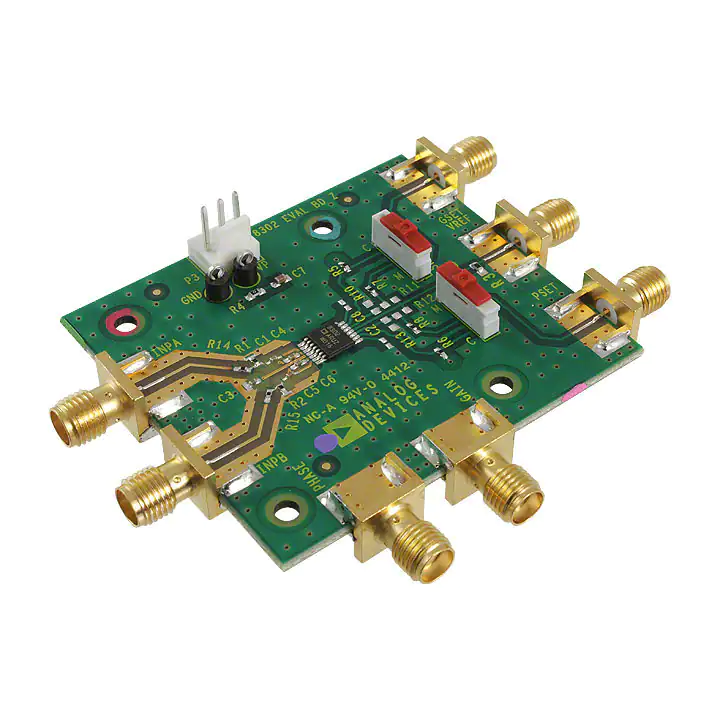

to +85°C temperature range. An evaluation board is available.

Document Feedback

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

©2018 Analog Devices, Inc. All rights reserved.

www.analog.com

Technical Support

�AD8302–SPECIFICATIONS

(TA = 25ⴗC, VS = 5 V, VMAG shorted to MSET, VPHS shorted to PSET, 52.3 ⍀ shunt

resistors connected to INPA and INPB, for Phase measurement PINPA = PINPB, unless otherwise noted.)

Parameter

Conditions

OVERALL FUNCTION

Input Frequency Range

Gain Measurement Range

Phase Measurement Range

Reference Voltage Output

PIN at INPA, PIN at INPB = –30 dBm

φIN at INPA > φIN at INPB

Pin VREF, –40°C ≤ TA ≤ +85°C

1.72

Pins INPA and INPB

To AC Ground, f ≤ 500 MHz

AC-Coupled (0 dBV = 1 V rms)

re: 50 Ω

–73

–60

INPUT INTERFACE

Input Simplified Equivalent Circuit

Input Voltage Range

Min

Typ

>0

Center of Input Dynamic Range

± 30

± 90

1.8

Max

Unit

2700

MHz

dB

Degree

V

1.88

3储2

–43

–30

kΩ储pF

dBV

dBm

dBV

dBm

–13

0

MAGNITUDE OUTPUT

Output Voltage Minimum

Output Voltage Maximum

Center Point of Output (MCP)

Output Current

Small Signal Envelope Bandwidth

Slew Rate

Response Time

Rise Time

Fall Time

Settling Time

Pin VMAG

20 × Log (VINPA/VINPB) = –30 dB

20 × Log (VINPA/VINPB) = +30 dB

VINPA = VINPB

Source/Sink

Pin MFLT Open

40 dB Change, Load 20 pF储10 kΩ

30

1.8

900

8

30

25

mV

V

mV

mA

MHz

V/µs

Any 20 dB Change, 10%–90%

Any 20 dB Change, 90%–10%

Full-Scale 60 dB Change, to 1% Settling

50

60

300

ns

ns

ns

PHASE OUTPUT

Output Voltage Minimum

Output Voltage Maximum

Phase Center Point

Output Current Drive

Slew Rate

Small Signal Envelope Bandwidth

Response Time

Pin VPHS

Phase Difference 180 Degrees

Phase Difference 0 Degrees

When φINPA = φINPB ± 90°

Source/Sink

30

1.8

900

8

25

30

40

500

mV

V

mV

mA

V/µs

MHz

ns

ns

100 MHz

Dynamic Range

MAGNITUDE OUTPUT

± 1 dB Linearity PREF = –30 dBm (VREF = –43 dBV)

± 0.5 dB Linearity PREF = –30 dBm (VREF = –43 dBV)

± 0.2 dB Linearity PREF = –30 dBm (VREF = –43 dBV)

From Linear Regression

Deviation from Output at 25°C

–40°C ≤ TA ≤ +85°C, PINPA = PINPB = –30 dBm

Deviation from Best Fit Curve at 25°C

–40°C ≤ TA ≤ +85°C, PINPA = ± 25 dB, PINPB = –30 dBm

PINPA = PINPB = –5 dBm to –50 dBm

58

55

42

29

dB

dB

dB

mV/dB

0.25

dB

0.25

0.2

dB

dB

145

143

10

Degree

Degree

mV/Degree

0.7

Degree

0.7

Degree

Slope

Deviation vs. Temperature

Gain Measurement Balance

Dynamic Range

Slope (Absolute Value)

Deviation vs. Temperature

Any 15 Degree Change, 10%–90%

120 Degree Change CFILT = 1 pF, to 1% Settling

PHASE OUTPUT

Less than ± 1 Degree Deviation from Best Fit Line

Less than 10% Deviation in Instantaneous Slope

From Linear Regression about –90° or +90°

Deviation from Output at 25°C

–40°C ≤ TA ≤ +85°C, Delta Phase = 90 Degrees

Deviation from Best Fit Curve at 25°C

–40°C ≤ TA ≤ +85°C, Delta Phase = ± 30 Degrees

–2–

REV. B

�AD8302

Parameter

Conditions

900 MHz

Dynamic Range

MAGNITUDE OUTPUT

± 1 dB Linearity PREF = –30 dBm (VREF = –43 dBV)

± 0.5 dB Linearity PREF = –30 dBm (VREF = –43 dBV)

± 0.2 dB Linearity PREF = –30 dBm (VREF = –43 dBV)

From Linear Regression

Deviation from Output at 25°C

–40°C ≤ TA ≤ +85°C, PINPA = PINPB = –30 dBm

Deviation from Best Fit Curve at 25°C

–40°C ≤ TA ≤ +85°C, PINPA = ± 25 dB, PINPB = –30 dBm

PINPA = PINPB = –5 dBm to –50 dBm

Slope

Deviation vs. Temperature

Gain Measurement Balance

Dynamic Range

Slope (Absolute Value)

Deviation

Phase Measurement Balance

1900 MHz

Dynamic Range

Slope

Deviation vs. Temperature

Gain Measurement Balance

Dynamic Range

Slope (Absolute Value)

Deviation

Phase Measurement Balance

2200 MHz

Dynamic Range

Slope

Deviation vs. Temperature

Gain Measurement Balance

Dynamic Range

Slope (Absolute Value)

Deviation

Min

PHASE OUTPUT

Less than ± 1 Degree Deviation from Best Fit Line

Less than 10% Deviation in Instantaneous Slope

From Linear Regression about –90° or +90°

Linear Deviation from Best Fit Curve at 25°C

–40°C ≤ TA ≤ +85°C, Delta Phase = 90 Degrees

–40°C ≤ TA ≤ +85°C, Delta Phase = ± 30 Degrees

Phase @ INPA = Phase @ INPB, PIN = –5 dBm to –50 dBm

MAGNITUDE OUTPUT

± 1 dB Linearity PREF = –30 dBm (VREF = –43 dBV)

± 0.5 dB Linearity PREF = –30 dBm (VREF = –43 dBV)

± 0.2 dB Linearity PREF = –30 dBm (VREF = –43 dBV)

From Linear Regression

Deviation from Output at 25°C

–40°C ≤ TA ≤ +85°C, PINPA = PINPB = –30 dBm

Deviation from Best Fit Curve at 25°C

–40°C ≤ TA ≤ +85°C, PINPA = ±25 dB, PINPB = –30 dBm

PINPA = PINPB = –5 dBm to –50 dBm

PHASE OUTPUT

Less than ± 1 Degree Deviation from Best Fit Line

Less than 10% Deviation in Instantaneous Slope

From Linear Regression about –90° or +90°

Linear Deviation from Best Fit Curve at 25°C

–40°C ≤ TA ≤ +85°C, Delta Phase = 90 Degrees

–40°C ≤ TA ≤ +85°C, Delta Phase = ± 30 Degrees

Phase @ INPA = Phase @ INPB, PIN = –5 dBm to –50 dBm

MAGNITUDE OUTPUT

± 1 dB Linearity PREF = –30 dBm (VREF = –43 dBV)

± 0.5 dB Linearity PREF = –30 dBm (VREF = –43 dBV)

± 0.2 dB Linearity PREF = –30 dBm (VREF = –43 dBV)

From Linear Regression

Deviation from Output at 25°C

–40°C ≤ TA ≤ +85°C, PINPA = PINPB = –30 dBm

Deviation from Best Fit Curve at 25°C

–40°C ≤ TA ≤ +85°C, PINPA = ± 25 dB, PINPB = –30 dBm

PINPA = PINPB = –5 dBm to –50 dBm

PHASE OUTPUT

Less than ± 1 Degree Deviation from Best Fit Line

Less than 10% Deviation in Instantaneous Slope

From Linear Regression about –90° or +90°

Linear Deviation from Best Fit Curve at 25°C

–40°C ≤ TA ≤ +85°C, Delta Phase = 90 Degrees

–40°C ≤ TA ≤ +85°C, Delta Phase = ± 30 Degrees

REFERENCE VOLTAGE

Output Voltage

PSRR

Output Current

Pin VREF

Load = 2 kΩ

VS = 2.7 V to 5.5 V

Source/Sink (Less than 1% Change)

POWER SUPPLY

Supply

Operating Current (Quiescent)

Pin VPOS

VS = 5 V

–40°C ≤ TA ≤ +85°C

Specifications subject to change without notice.

REV. B

–3–

Typ

Max

Unit

58

54

42

28.7

dB

dB

dB

mV/dB

0.25

dB

0.25

0.2

dB

dB

143

143

10.1

Degree

Degree

mV/Degree

0.75

0.75

0.8

Degree

Degree

Degree

57

54

42

27.5

dB

dB

dB

mV/dB

0.27

dB

0.33

0.2

dB

dB

128

120

10.2

Degree

Degree

mV/Degree

0.8

0.8

1

Degree

Degree

Degree

53

51

38

27.5

dB

dB

dB

mV/dB

0.28

dB

0.4

0.2

dB

dB

115

110

10

Degree

Degree

mV/Degree

0.85

0.9

Degree

Degree

1.7

1.8

0.25

5

1.9

V

mV/V

mA

2.7

5.0

19

21

5.5

25

27

V

mA

mA

�AD8302

ABSOLUTE MAXIMUM RATINGS 1

PIN CONFIGURATION

Supply Voltage VS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.5 V

PSET, MSET Voltage . . . . . . . . . . . . . . . . . . . . . . VS + 0.3 V

INPA, INPB Maximum Input . . . . . . . . . . . . . . . . . . –3 dBV

Equivalent Power Re. 50 Ω . . . . . . . . . . . . . . . . . . 10 dBm

θJA2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150°C/W

Maximum Junction Temperature . . . . . . . . . . . . . . . . 125°C

Operating Temperature Range . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature Range (Soldering 60 sec) . . . . . . . . 300°C

COMM 1

14

MFLT

INPA 2

13

VMAG

OFSA 3

12

MSET

AD8302

TOP VIEW 11 VREF

(Not to Scale)

10 PSET

OFSB 5

VPOS 4

INPB 6

9

VPHS

COMM 7

8

PFLT

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

JEDEC 1S Standard (2-layer) board data.

PIN FUNCTION DESCRIPTIONS

Equivalent

Circuit

Pin No.

Mnemonic

Function

1, 7

2

3

COMM

INPA

OFSA

4

5

VPOS

OFSB

6

8

9

INPB

PFLT

VPHS

10

PSET

11

12

VREF

MSET

13

VMAG

Device Common. Connect to low impedance ground.

High Input Impedance to Channel A. Must be ac-coupled.

A capacitor to ground at this pin sets the offset compensation filter corner

and provides input decoupling.

Voltage Supply (VS), 2.7 V to 5.5 V

A capacitor to ground at this pin sets the offset compensation filter corner

and provides input decoupling.

Input to Channel B. Same structure as INPA.

Low Pass Filter Terminal for the Phase Output

Single-Ended Output Proportional to the Phase Difference between INPA

and INPB.

Feedback Pin for Scaling of VPHS Output Voltage in Measurement Mode.

Apply a setpoint voltage for controller mode.

Internally Generated Reference Voltage (1.8 V Nominal)

Feedback Pin for Scaling of VMAG Output Voltage Measurement Mode.

Accepts a set point voltage in controller mode.

Single-Ended Output. Output voltage proportional to the decibel ratio

of signals applied to INPA and INPB.

Low Pass Filter Terminal for the Magnitude Output

14

MFLT

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD8302 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

–4–

Circuit A

Circuit A

Circuit A

Circuit A

Circuit E

Circuit B

Circuit D

Circuit C

Circuit D

Circuit B

Circuit E

WARNING!

ESD SENSITIVE DEVICE

REV. B

�AD8302

VPOS

VPOS

100mV

4k⍀

INPA(INPB)

4k⍀

OFSA(OFSB)

+

ON TO

LOG-AMP

–

25⍀

750⍀

2k⍀

10pF

VMAG

(VPHS)

CLASS A-B

CONTROL

COMM

COMM

Circuit A

Circuit B

VPOS

VPOS

VPOS

VREF

10k⍀

MSET

(PSET)

MFLT

(PFLT)

10k⍀

10k⍀

5k⍀

COMM

Circuit C

1.5pF

ACTIVE LOADS

COMM

COMM

Circuit D

Figure 1. Equivalent Circuits

REV. B

–5–

Circuit E

�AD8302–Typical Performance Characteristics

1.80

3.0

1.65

2.5

1.50

2.0

1.35

1.5

900

1.8

100

1.6

1.4

1.20

1.2

1900

0.8

0.6

0.4

0.2

0

–30 –25 –20 –15 –10 –5

0

5

10

MAGNITUDE RATIO – dB

15

20

25

TPC 1. Magnitude Output (VMAG) vs. Input Level Ratio

(Gain) VINPA/VINPB, Frequencies 100 MHz, 900 MHz,

1900 MHz, 2200 MHz, 2700 MHz, 25 ⴗC, PINPB = –30 dBm,

(Re: 50 Ω)

2.0

–0.5

0.60

–1.0

0.45

–1.5

0.30

–2.0

0.15

–2.5

–20

–10

0

10

MAGNITUDE RATIO – dB

20

1.4

3.0

1.65

2.5

1.50

2.0

1.35

1.5

1.20

2700

VMAG – V

1.2

1.0

0.8

0.6

2200

0.4

0.2

900

0

–30 –25 –20 –15 –10 –5

0

5

10

MAGNITUDE RATIO – dB

100

15

20

25

–3.0

30

1.80

1900

1.6

VMAG – V

0.0

+85ⴗC

0.75

TPC 4. VMAG and Log Conformance vs. Input Level Ratio

(Gain), Frequency 900 MHz, –40 ⴗC, +25 ⴗC, and +85ⴗ C,

Reference Level = –30 dBm

1.8

30

1.0

1.05

0.5

–40ⴗC

0.90

0.0

+25ⴗC

0.75

–0.5

+85ⴗC

0.60

–1.0

0.45

–1.5

0.30

–2.0

0.15

–2.5

0

–30

TPC 2. VMAG vs. Input Level Ratio (Gain) VINPA/VINPB,

Frequencies 100 MHz, 900 MHz, 1900 MHz, 2200 MHz,

2700 MHz, PINPA = –30 dBm

–20

–10

0

10

MAGNITUDE RATIO – dB

20

–3.0

30

TPC 5. VMAG and Log Conformance vs. Input Level Ratio

(Gain), Frequency 1900 MHz, –40 ⴗC, +25 ⴗC, and +85 ⴗC,

Reference Level = –30 dBm

1.80

3.0

1.80

3.0

1.65

2.5

1.65

2.5

1.50

2.0

1.50

2.0

1.35

1.5

1.35

1.5

1.20

1.0

0.5

+25ⴗC

0.90

0.0

+85ⴗC

0.75

–0.5

1.20

VMAG – V

–40ⴗC

1.05

ERROR IN VMAG – dB

VMAG – V

0.5

+25ⴗC

0.90

0

–30

30

1.0

–40ⴗC

1.05

1.0

1.05

0.5

–40ⴗC

0.90

0.0

+25ⴗC

0.75

–0.5

+85ⴗC

0.60

–1.0

–1.5

0.45

–1.5

0.30

–2.0

0.30

–2.0

0.15

–2.5

0.15

–2.5

0.60

–1.0

0.45

0

–30

–20

–10

0

10

MAGNITUDE RATIO – dB

20

ERROR IN VMAG – dB

2700

1.0

VMAG – V

VMAG – V

2200

–3.0

30

0

–30

TPC 3. VMAG Output and Log Conformance vs. Input

Level Ratio (Gain), Frequency 100 MHz, –40 ⴗC, +25 ⴗC,

and +85 ⴗC, Reference Level = –30 dBm

–20

–10

0

10

MAGNITUDE RATIO – dB

20

ERROR IN VMAG – dB

2.0

ERROR IN VMAG – dB

(VS = 5 V, VINPB is the reference input and VINPA is swept, unless otherwise noted. All references to dBm are referred to 50 ⍀. For the phase output

curves, the input signal levels are equal, unless otherwise noted.)

–3.0

30

TPC 6. VMAG Output and Log Conformance vs. Input

Level Ratio (Gain), Frequency 2200 MHz, –40 ⴗC, +25 ⴗC,

and +85 ⴗC, Reference Level = –30 dBm

–6–

REV. B

�AD8302

3.0

2.0

2.5

1.8

2.0

1.6

–40 C

+85 C

1.4

1.0

0.5

VMAG – V

0.0

–0.5

–1.0

0.8

+25 C

0.4

–40 C

–2.0

1.0

0.6

+85 C

–1.5

1.2

0.2

–2.5

–3.0

–30 –25 –20 –15 –10 –5

0

5

10

MAGNITUDE RATIO – dB

15

20

25

0.0

0

5

10

–30 –25 –20 –15 –10 –5

MAGNITUDE RATIO – dB

30

TPC 7. Distribution of Magnitude Error vs. Input Level

Ratio (Gain), Three Sigma to Either Side of Mean,

Frequency 900 MHz, –40 ⴗC, +25 ⴗC, and +85 ⴗC, Reference Level = –30 dBm

15

20

25

30

TPC 10. Distribution of VMAG vs. Input Level Ratio (Gain),

Three Sigma to Either Side of Mean, Frequency 1900 MHz,

Temperatures Between –40 ⴗC and +85 ⴗC, Reference Level

= –30 dBm

1.8

3.0

2.5

3.0

–45dBm

2.5

1.6

2.0

2.0

1.4

–40 C

1.0

+85 C

0.5

0.0

–0.5

–2.0

–30dBm

1.5

1.0

–15dBm

1.0

0.5

0.0

0.8

–30dBm

–0.5

–15dBm

0.6

–1.0

–1.5

–45dBm

1.2

VMAG – V

ERROR IN VMAG – dB

1.5

+25 C

–40 C

–1.0

–1.5

0.4

+85 C

–2.0

0.2

–2.5

–3.0

–30 –25 –20 –15 –10 –5

0

5

10

MAGNITUDE RATIO – dB

ERROR IN VMAG – dB

ERROR IN VMAG – dB

1.5

15

20

25

0.0

–30

30

TPC 8. Distribution of Error vs. Input Level Ratio (Gain),

Three Sigma to Either Side of Mean, Frequency 1900 MHz,

–40 ⴗC, +25 ⴗC, and +85 ⴗC, Reference Level = –30 dBm

–2.5

–20

–10

0

10

MAGNITUDE RATIO – dB

20

–3.0

30

TPC 11. VMAG Output and Log Conformance vs. Input

Level Ratio (Gain), Reference Level = –15 dBm, –30 dBm,

and –45 dBm, Frequency 1900 MHz

3.0

1.10

2.5

1.05

2.0

PINPA = PINPB + 5dB

–40 C

+85 C

1.00

1.0

0.5

VMAG – V

ERROR IN VMAG – dB

1.5

0.0

–0.5

0.95

PINPA = PINPB

0.90

–1.0

–1.5

–2.0

0.85

+25 C +85 C

–40 C

0.80

–2.5

–3.0

–30 –25 –20 –15 –10 –5

0

5

10

MAGNITUDE RATIO – dB

15

20

25

0.75

–65 –60 –55 –50 –45 –40 –35 –30 –25 –20 –15 –10 –5

INPUT LEVEL – dBm

30

TPC 9. Distribution of Magnitude Error vs. Input Level

Ratio (Gain), Three Sigma to Either Side of Mean,

Frequency 2200 MHz, Temperatures –40 ⴗC, +25 ⴗC, and

+85 ⴗC, Reference Level = –30 dBm

REV. B

PINPA = PINPB – 5dB

0

TPC 12. VMAG Output vs. Input Level for P INPA = PINPB,

PINPA = PINPB + 5 dB, PINPA = PINPB – 5 dB, Frequency 1900 MHz

–7–

�AD8302

1.06

18

1.04

1.02

PINPA = PINPB + 5dB

1.00

15

0.98

0.96

12

PERCENT

VMAG – V

0.94

0.92

0.90

PINPA = PINPB

0.88

9

0.86

6

0.84

0.82

0.80

3

PINPA = PINPB – 5dB

0.78

0.76

0.74

0

200

400

600

0

0.80

800 1000 1200 1400 1600 1800 2000 2200

FREQUENCY – MHz

0.85

0.90

0.95

1.00

MCP – V

TPC 13. VMAG Output vs. Frequency, for PINPA = PINPB, PINPA

= PINPB + 5 dB, and PINPA = PINPB – 5 dB, PINPB = –30 dBm

TPC 16. Center Point of Magnitude Output (MCP)

Distribution Frequencies 900 MHz, 17,000 Units

0.4

18

0.2

15

–0.2

12

–0.4

PERCENT

CHANGE IN SLOPE – mV

0

–0.6

–0.8

–1.0

9

6

–1.2

–1.4

3

–1.6

–1.8

–40

–20

0

20

40

60

TEMPERATURE – ⴗC

80

0

27.0

85

27.5

28.0

28.5

29.0

29.5

30.0

VMAG SLOPE – mV/dB

TPC 17. VMAG Slope, Frequency 900 MHz, 17,000 Units

TPC 14. Change in VMAG Slope vs. Temperature, Three

Sigma to Either Side of Mean, Frequencies 1900 MHz

25

0.032

20

15

0.030

SLOPE OF VMAG – V

VMAG – mV

10

5

0

–5

–10

0.028

0.026

–15

2800

2600

2400

2200

2000

1800

1600

1400

90

1200

80

800

70

1000

60

600

10 20 30 40 50

TEMPERATURE – ⴗC

400

0.024

0

0

–25

–40 –30 –20 –10

200

–20

FREQUENCY – MHz

TPC 15. Change in Center Point of Magnitude Output

(MCP) vs. Temperature, Three Sigma to Either Side of

Mean, Frequencies 1900 MHz

TPC 18. VMAG Slope vs. Frequency

–8–

REV. B

�AD8302

10000

VMAG – nV/ Hz

INPUT –50dBm

20mV PER

VERTICAL

DIVISION

25ns

HORIZONTAL

1000

INPUT –30dBm

INPUT –10dBm

100

10

1k

10k

100k

1M

FREQUENCY – Hz

10M

100M

TPC 22. Magnitude Output Noise Spectral

Density, PINPA = PINPB = –10 dBm, –30 dBm,

–50 dBm, No Filter Capacitor

TPC 19. Magnitude Output Response to 4 dB Step, for

PINPB = –30 dBm, PINPA = –32 dBm to –28 dBm, Frequency

1900 MHz, No Filter Capacitor

10000

VMAG – nV/ Hz

INPUT –50dBm

20mV PER

VERTICAL

DIVISION

1000

INPUT –30dBm

100

INPUT –10dBm

1.00s

HORIZONTAL

10

1k

TPC 20. Magnitude Output Response to 4 dB Step, for

PINPB = –30 dBm, PINPA = –32 dBm to –28 dBm, Frequency

1900 MHz, 1 nF Filter Capacitor

10k

100k

1M

FREQUENCY – Hz

10M

100M

TPC 23. Magnitude Output Noise Spectral Density, PINPA = PINPB

= –10 dBm, –30 dBm, –50 dBm, with Filter Capacitor, C = 1 nF

0.18

VMAG (PEAK-TO-PEAK) – V

0.16

200mV PER

VERTICAL

DIVISION

100ns

HORIZONTAL

0.14

0.12

0.10

0.08

2700

1900

0.06

0.02

100

0.00

–25

TPC 21. Magnitude Output Response to 40 dB Step, for

PINPB = –30 dBm, PINPA = –50 dBm to –10 dBm, Supply 5 V,

Frequency 1900 MHz, No Filter Capacitor

REV. B

2200

900

0.04

–20

–15

–10

–5

0

5

10

MAGNITUDE RATIO – dB

15

20

25

TPC 24. VMAG Peak-to-Peak Output Induced by Sweeping

Phase Difference through 360 Degrees vs. Magnitude Ratio,

Frequencies 100 MHz, 900 MHz, 1900 MHz, 2200 MHz, and

2700 MHz

–9–

�1.80

10

1.62

8

1.44

6

1.26

4

1.08

2

0.90

0

0.72

–2

0.54

–4

0.4

0.36

–6

0.2

0.18

–8

1.8

1.6

900MHz

1.4

1.2

PHASE OUT – V

PHASE OUT – V

1900MHz

2200MHz

2700MHz

1.0

0.8

0.6

0.0

–180

–140

–100 –60

–20

20

60

100

PHASE DIFFERENCE – Degrees

140

0.00

–180 –150 –120 –90 –60 –30 0

30 60 90

PHASE DIFFERENCE – Degrees

180

TPC 28. VPHS Output and Nonlinearity vs. Input Phase

Difference, Input Levels –30 dBm, Frequency 1900 MHz

1.80

10

1.80

10

1.62

8

1.62

8

1.44

6

1.44

6

1.26

4

1.26

4

1.08

2

1.08

2

0.90

0

0.72

–2

PHASE OUT – V

ERROR – Degrees

PHASE OUT – V

TPC 25. Phase Output (VPHS) vs. Input Phase Difference,

Input Levels –30 dBm, Frequencies 100 MHz, 900 MHz,

1900 MHz, 2200 MHz, Supply 5 V, 2700 MHz

0.90

0

0.72

–2

0.54

–4

0.54

–4

0.36

–6

0.36

–6

0.18

–8

0.18

–8

0.00

–180 –150 –120 –90 –60 –30 0

30 60 90

PHASE DIFFERENCE – Degrees

0.00

–180 –150 –120 –90 –60 –30 0

30 60 90

PHASE DIFFERENCE – Degrees

–10

120 150 180

10

10

1.62

8

8

1.44

6

6

1.26

4

4

1.08

2

0.90

0

0.72

–2

0.54

–4

0.36

–6

0.18

–8

ERROR – Degrees

ERROR – Degrees

1.80

0.00

–180 –150 –120 –90 –60 –30 0

30 60 90

PHASE DIFFERENCE – Degrees

–10

120 150 180

TPC 29. VPHS Output and Nonlinearity vs. Input Phase

Difference, Input Levels –30 dBm, Frequency 2200 MHz

TPC 26. VPHS Output and Nonlinearity vs. Input Phase

Difference, Input Levels –30 dBm, Frequency 100 MHz

PHASE OUT – V

–10

120 150 180

ERROR – Degrees

100MHz

ERROR – Degrees

AD8302

0

–2

–4

+85ⴗC

–40ⴗC

–6

–8

–10

–180 –150 –120 –90 –60 –30 0

30 60 90

PHASE DIFFERENCE – Degrees

–10

120 150 180

TPC 27. VPHS Output and Nonlinearity vs. Input Phase

Difference, Input Levels –30 dBm, Frequency 900 MHz

+25ⴗC

2

120 150 180

TPC 30. Distribution of VPHS Error vs. Input Phase Difference, Three Sigma to Either Side of Mean, Frequency

900 MHz, –40 ⴗC, +25 ⴗC, and +85 ⴗC, Input Levels –30 dBm

–10–

REV. B

�AD8302

0.15

8

0.10

6

0.05

CHANGE IN VPHS SLOPE – mV

10

ERROR – Degrees

4

+25ⴗC

–40ⴗC

2

0

–2

–4

+85ⴗC

–6

MEAN +3 SIGMA

0.00

–0.05

–0.10

–0.15

MEAN –3 SIGMA

–0.20

–0.25

–0.30

–8

–10

–180 –150 –120 –90 –60 –30 0

30 60 90

PHASE DIFFERENCE – Degrees

–0.35

–40 –30 –20 –10

120 150 180

TPC 31. Distribution of VPHS Error vs. Input Phase

Difference, Three Sigma to Either Side of Mean, Frequency

1900 MHz, –40 ⴗC, +25 ⴗC, and +85 ⴗC, Supply 5 V, Input

Levels PINPA = PINPB = –30 dBm

0

10 20 30 40 50

TEMPERATURE – ⴗC

60

70

80

90

TPC 34. Change in VPHS Slope vs. Temperature, Three

Sigma to Either Side of Mean, Frequency 1900 MHz

10

10

8

5

6

0

+3 SIGMA

–5

+85ⴗC +25ⴗC

2

PERCENT

ERROR – Degrees

4

0

–2

–4

–10

–20

–25

–40ⴗC

–6

–30

–8

–35

–10

–180 –150 –120 –90 –60 –30 0

30 60 90

PHASE DIFFERENCE – Degrees

–3 SIGMA

–15

–40

–40 –30 –20 –10

120 150 180

TPC 32. Distribution of VPHS Error vs. Input Phase Difference, Three Sigma to Either Side of Mean, Frequency

2200 MHz, –40 ⴗC, +25 ⴗC, and +85 ⴗC, Input Levels –30 dBm

0

10 20 30 40 50

VPHS – mV/Degree

60

70

80

90

TPC 35. Change in Phase Center Point (PCP) vs.

Temperature, Three Sigma to Either Side of Mean,

Frequency 1900 MHz

1.8

18

1.6

15

1.4

12

PERCENT

VPHS – V

1.2

1.0

0.8

0.6

9

6

0.4

3

0.2

0.0

–180 –150 –120 –90 –60 –30 0

30 60 90

PHASE DIFFERENCE – Degrees

TPC 33. Distribution of VPHS vs. Input Phase Difference, Three Sigma to Either Side of Mean, Frequency

900 MHz, Temperature between –40 ⴗC and +85 ⴗC, Input

Levels –30 dBm

REV. B

0

0.75

120 150 180

0.80

0.85

0.90

PCP – V

0.95

1.00

1.05

TPC 36. Phase Center Point (PCP) Distribution, Frequency

900 MHz, 17,000 Units

–11–

�AD8302

16

14

12

PERCENT

10

100mV PER

VERTICAL

DIVISION

8

6

4

2

50ns HORIZONTAL

0

9.5

9.7

9.9

10.1

10.3

10.5

VPHS – mV/Degree

10.7

10.9

11.1

TPC 37. VPHS Slope Distribution, Frequency

900 MHz

TPC 40. VPHS Output Response to 40 ⴗ Step with Nominal

Phase Shift of 90 ⴗ, Input Levels PINPA = PINPB = –30 dBm,

Frequency 1900 MHz,1 pF Filter Capacitor

10000

VPHS – nV/ Hz

INPUT –50dBm

10mV PER

VERTICAL

DIVISION

1000

INPUT –30dBm

INPUT –10dBm

100

50ns HORIZONTAL

10

1k

TPC 38. VPHS Output Response to 4 ⴗ Step with Nominal

Phase Shift of 90ⴗ, Input Levels –30 dBm, Frequency

1900 MHz, 25ⴗC, 1 pF Filter Capacitor

10k

100k

1M

FREQUENCY – Hz

10M

100M

TPC 41. VPHS Output Noise Spectral Density vs. Frequency,

PINPA = –30 dBm, PINPB = –10 dBm, –30 dBm, –50 dBm, and

90ⴗ Input Phase Difference

1.80

PINPA = –30dBm

1.62

1.44

PINPA = –15dBm

PHASE OUT – V

1.26

10mV PER

VERTICAL

DIVISION

1.08

0.90

PINPA = –45dBm

0.72

0.54

0.36

0.18

2s HORIZONTAL

0.00

–180 –150 –120 –90 –60 –30 0

30 60 90

PHASE DIFFERENCE – Degrees

TPC 39. VPHS Output Response to 4 ⴗ Step with Nominal

Phase Shift of 90ⴗ, Input Levels PINPA = PINPB = –30 dBm,

Supply 5 V, Frequency 1900 MHz, 25ⴗC, with 100 pF Filter

Capacitor

120 150 180

TPC 42. Phase Output vs. Input Phase Difference, PINPA =

PINPB, PINPA = PINPB + 15 dB, PINPA = PINPB – 15 dB, Frequency

900 MHz

–12–

REV. B

�AD8302

12

PINPA = –15dBm

1.80

PINPA = –30dBm

PINPA = –20dBm

1.62

8

1.44

PINPA = –45dBm

1.26

PINPA = –40dBm

PHASE OUT – V

ABSOLUTE VALUE OF VPHS

INSTANTANEOUS SLOPE – mV

10

6

4

1.08

0.90

0.72

0.54

0.36

2

0.18

0

–180 –150 –120 –90 –60 –30 0

30 60 90

PHASE DIFFERENCE – Degrees

PINPA = –30dBm

0.00

–180 –150 –120 –90 –60 –30 0

30 60 90

PHASE DIFFERENCE – Degrees

120 150 180

TPC 43. Phase Output Instantaneous Slope,

PINPA = PINPB, PINPA = PINPB + 15 dB, PINPA = PINPB – 15 dB,

Frequency 900 MHz

120 150 180

TPC 46. Phase Output vs. Input Phase Difference,

PINPA = PINPB, PINPA = PINPB + 10 dB, PINPA = PINPB – 10 dB,

Frequency 2200 MHz

12

1.80

PINPA = –20dBm

PINPA = –20dBm

1.62

10

ABSOLUTE VALUE OF VPHS

INSTANTANEOUS SLOPE – mV

1.44

PHASE OUT – V

1.26

PINPA = –40dBm

1.08

0.90

0.72

PINPA = –30dBm

0.54

0.36

PINPA = –40dBm

PINPA = –30dBm

8

6

4

2

0.18

0.00

–180 –150 –120 –90 –60 –30 0

30 60 90

PHASE DIFFERENCE – Degrees

0

–180 –150 –120 –90 –60 –30 0

30 60 90

PHASE DIFFERENCE – Degrees

120 150 180

TPC 44. Phase Output vs. Input Phase Difference,

PINPA = PINPB, PINPA = PINPB + 10 dB, PINPA = PINPB – 10 dB,

Frequency 1900 MHz, Supply 5 V

120 150 180

TPC 47. Phase Output Instantaneous Slope, PINPA = PINPB,

PINPA = PINPB + 10 dB, PINPA = PINPB – 10 dB, Frequency

2200 MHz

12

4000

4.0

3500

3.5

REAL SHUNT Z (⍀)

3.0

PINPA = –40dBm

6

4

2.5

2500

2.0

2000

SHUNT R

1.5

1500

SHUNT C

CAPACITANCE – pF

3000

PINPA = –30dBm

8

RESISTANCE – ⍀

ABSOLUTE VALUE OF VPHS

INSTANTANEOUS SLOPE – mV

10

1.0

1000

CAPACITANCE SHUNT Z (pF)

2

0.5

500

PINPA = –20dBm

0

–180 –150 –120 –90 –60 –30 0

30 60 90

PHASE DIFFERENCE – Degrees

TPC 45. Phase Output Instantaneous Slope, PINPA =

PINPB, PINPA = PINPB + 10 dB, PINPA = PINPB – 10 dB,

Frequency 1900 MHz, Supply 5 V

REV. B

0.0

0

0

120 150 180

500

1000

1500

FREQUENCY – MHz

2000

2500

TPC 48. Input Impedance, Modeled as Shunt R in Parallel

with Shunt C

–13–

�AD8302

18

8

6

15

4

PERCENT

VREF – mV

12

2

0

9

6

–2

3

–4

–6

–40 –30 –20 –10

0

10 20 30 40 50

TEMPERATURE – ⴗC

60

70

80

0

1.74

90

TPC 49. Change in VREF vs. Temperature, Three Sigma to

Either Side of Mean

1.76

1.78

1.80

1.82

VREF – V

1.84

1.86

1.88

TPC 51. VREF Distribution, 17,000 Units

120

NOISE – nV/ Hz

100

80

60

40

20

0

1k

10k

100k

1M

FREQUENCY – Hz

10M

100M

TPC 50. VREF Output Noise Spectral Density vs.

Frequency

–14–

REV. B

�AD8302

[

The AD8302 measures the magnitude ratio, defined here as

gain, and phase difference between two signals. A pair of

matched logarithmic amplifiers provide the measurement, and

their hard-limited outputs drive the phase detector.

Basic Theory

Logarithmic amplifiers (log amps) provide a logarithmic compression function that converts a large range of input signal

levels to a compact decibel-scaled output. The general mathematical form is:

VOUT = VSLP log (VIN / VZ )

(1)

where VIN is the input voltage, VZ is called the intercept (voltage),

and VSLP is called the slope (voltage). It is assumed throughout

that log(x) represents the log10(x) function. VSLP is thus the

volts/decade, and since a decade of voltage corresponds to

20 dB, V SLP /20 is the volts/dB. V Z is the value of input

signal that results in an output of zero and need not correspond

to a physically realizable part of the log amp signal range.

While the slope is fundamentally a characteristic of the log amp,

the intercept is a function of the input waveform as well.1

Furthermore, the intercept is typically more sensitive to temperature and frequency than the slope. When single log amps

are used for power measurement, this variability introduces

errors into the absolute accuracy of the measurement since the

intercept represents a reference level.

(2)

where VINA and VINB are the input voltages, VMAG is the output

corresponding to the magnitude of the signal level difference,

and VSLP is the slope. Note that the intercept, VZ, has dropped

out. Unlike the measurement of power, when measuring a dimensionless quantity such as relative signal level, no independent

reference or intercept need be invoked. In essence, one signal

serves as the intercept for the other. Variations in intercept due

to frequency, process, temperature, and supply voltage affect both

channels identically and hence do not affect the difference. This

technique depends on the two log amps being well matched

in slope and intercept to ensure cancellation. This is the case

for an integrated pair of log amps. Note that if the two signals

have different waveforms (e.g., different peak-to-average ratios)

or different frequencies, an intercept difference may appear, introducing a systematic offset.

The log amp structure consists of a cascade of linear/limiting

gain stages with demodulating detectors. Further details about

the structure and function of log amps can be found in data

sheets for other log amps produced by Analog Devices.2 The

output of the final stage of a log amp is a fully limited signal

over most of the input dynamic range. The limited outputs from

both log amps drive an exclusive-OR style digital phase detector.

Operating strictly on the relative zero-crossings of the limited signals, the extracted phase difference is independent of the original

input signal levels. The phase output has the general form:

NOTES

1

See the data sheet for the AD640 for a description of the effect of waveform on

the intercept of log amps.

2

For example, see the data sheet for the AD8307.

REV. B

(3)

where VΦ is the phase slope in mV/degree and Φ is each signal’s

relative phase in degrees.

Structure

The general form of the AD8302 is shown in Figure 2. The

major blocks consist of two demodulating log amps, a phase

detector, output amplifiers, a biasing cell, and an output reference voltage buffer. The log amps and phase detector process

the high frequency signals and deliver the gain and phase information in current form to the output amplifiers. The output

amplifiers determine the final gain and phase scaling. External

filter capacitors set the averaging time constants for the respective outputs. The reference buffer provides a 1.80 V reference

voltage that tracks the internal scaling constants.

VIDEO OUTPUT – A

INPA

OFSA

60dB LOG AMPS

(7 DETECTORS)

+

MFLT

+

–

VMAG

–

MSET

PHASE

DETECTOR

COMM

PSET

OFSB

INPB

The AD8302 takes the difference in the output of two identical

log amps, each driven by signals of similar waveforms but at

different levels. Since subtraction in the logarithmic domain

corresponds to a ratio in the linear domain, the resulting

output becomes:

VMAG = VSLP log (VINA / VINB )

]

VPHS = VΦ Φ (VINA) − Φ (VINB )

GENERAL DESCRIPTION AND THEORY

60dB LOG AMPS

(7 DETECTORS)

–

VPHS

+

PFLT

VIDEO OUTPUT – B

VPOS

BIAS

x3

1.8V

VREF

Figure 2. General Structure

Each log amp consists of a cascade of six 10 dB gain stages with

seven associated detectors. The individual gain stages have 3 dB

bandwidths in excess of 5 GHz. The signal path is fully differential to minimize the effect of common-mode signals and noise.

Since there is a total of 60 dB of cascaded gain, slight dc offsets

can cause limiting of the latter stages, which may cause measurement errors for small signals. This is corrected by a feedback

loop. The nominal high-pass corner frequency, fHP, of this loop

is set internally at 200 MHz but can be lowered by adding external

capacitance to the OFSA and OFSB pins. Signals at frequencies

well below the high-pass corner are indistinguishable from dc

offsets and are also nulled. The difference in the log amp outputs is performed in the current domain, yielding by analogy to

Equation 2:

ILA = ISLP log(VINA / VINB )

(4)

where ILA and ISLP are the output current difference and the

characteristic slope (current) of the log amps, respectively. The

slope is derived from an accurate reference designed to be insensitive to temperature and supply voltage.

The phase detector uses a fully symmetric structure with respect

to its two inputs to maintain balanced delays along both signal

paths. Fully differential signaling again minimizes the sensitivity

to common-mode perturbations. The current-mode equivalent

to Equation 3 is:

[

]

IPD = IΦ Φ (VINA) − Φ (VINB ) − 90°

(5)

where IPD and IΦ are the output current and characteristic slope

associated with the phase detector, respectively. The slope is

derived from the same reference as the log amp slope.

–15–

�AD8302

Note that by convention, the phase difference is taken in the range

from –180° to +180°. Since this style of phase detector does not

distinguish between ±90°, it is considered to have an unambiguous

180° phase difference range that can be either 0° to +180° centered

at +90° or 0° to –180° centered at –90°.

VP

C7

R4

(6)

where IFB is the feedback current equal to (VSET – VCP)/RF, VSET

is the setpoint input, and T is the integration time constant equal

to RFCAVE/K, where CAVE is the parallel combination of the internal 1.5 pF and the external capacitor CFLT.

1.5pF

MFLT/PFLT

+

K

IIN = ILA OR IPD

VMAG/VPHS

CFLT

–

VMAG

2 INPA

VMAG 13

3 OFSA

MSET 12

4 VPOS

VREF 11

5 OFSB

PSET 10

6 INPB

VPHS 9

7 COMM

PFLT 8

C2

R1

C4

C6

VINB

R2

VPHS

C5

C3

C8

Figure 4. Basic Connections in Measurement Mode with

30 mV/dB and 10 mV/Degree Scaling

In the low frequency limit, the gain and phase transfer functions

given in Equations 4 and 5 become:

VMAG = RF ISLP log(VINA / VINB ) + VCP or

(8a)

VMAG = (RF ISLP / 20) (PINA − PINB ) + VCP

(8b)

(

)

VPHS = –RF IΦ |Φ (VINA) − Φ (VINB ) |–90° + VCP

(9)

which are illustrated in Figure 5. In Equation 8b, PINA and PINB are

the power in dBm equivalent to VINA and VINB at a specified reference impedance. For the gain function, the slope represented by

RF ISLP is 600 mV/decade or, dividing by 20 dB/decade, 30 mV/dB.

With a center point of 900 mV for 0 dB gain, a range of –30 dB to

+30 dB covers the full-scale swing from 0 V to 1.8 V. For the phase

function, the slope represented by RFIΦ is 10 mV/degree. With a

center point of 900 mV for 90°, a range of 0° to 180° covers the

full-scale swing from 1.8 V to 0 V. The range of 0° to –180° covers

the same full-scale swing but with the opposite slope.

VCP = 900mV

IFB

MFLT 14

C1

VINA

The basic structure of both output interfaces is shown in Figure 3. It

accepts a setpoint input and includes an internal integrating/averaging capacitor and a buffer amplifier with gain K. External access to

these setpoints provides for several modes of operation and enables

flexible tailoring of the gain and phase transfer characteristics. The

setpoint interface block, characterized by a transresistance RF, generates a current proportional to the voltage presented to its input pin,

MSET or PSET. A precise offset voltage of 900 mV is introduced

internally to establish the center-point (VCP) for the gain and phase

functions, i.e., the setpoint voltage that corresponds to a gain of 0 dB

and a phase difference of 90°. This setpoint current is subtracted

from the signal current, IIN, coming from the log amps in the gain

channel or from the phase detector in the phase channel. The resulting difference is integrated on the averaging capacitors at either pin

MFLT or PFLT and then buffered by the output amplifier to the

respective output pins, VMAG and VPHS. With this open-loop

arrangement, the output voltage is a simple integration of the difference between the measured gain/phase and the desired setpoint:

VOUT = RF (IIN − IFB ) / (sT )

AD8302

1 COMM

1.8V

+

+

MSET/PSET

20k⍀

30mV/dB

VMAG

RF

Figure 3. Simplified Block Diagram of the Output Interface

900mV

VCP

BASIC CONNECTIONS

Measurement Mode

The basic function of the AD8302 is the direct measurement of gain

and phase. When the output pins, VMAG and VPHS, are connected

directly to the feedback setpoint input pins, MSET and PSET, the

default slopes and center points are invoked. This basic connection

shown in Figure 4 is termed the measurement mode. The current

from the setpoint interface is forced by the integrator to be equal to

the signal currents coming from the log amps and phase detector.

The closed loop transfer function is thus given by:

(7)

The time constant T represents the single-pole response to the envelope of the dB-scaled gain and the degree-scaled phase functions. A

small internal capacitor sets the maximum envelope bandwidth to

approximately 30 MHz. If no external CFLT is used, the AD8302

can follow the gain and phase envelopes within this bandwidth. If

longer averaging is desired, CFLT can be added as necessary according to T (ns) = 3.3 × CAVE (pF). For best transient response with

minimal overshoot, it is recommended that 1 pF minimum value

external capacitors be added to the MFLT and PFLT pins.

–16–

–30

0

+30

MAGNITUDE RATIO – dB

1.8V

+10mV/DEG

VPHS

VOUT = ( I IN RF + VCP ) / (1 + sT )

0V

–10mV/DEG

VCP

900mV

0V

–180

–90

0

90

180

PHASE DIFFERENCE – Degrees

Figure 5. Idealized Transfer Characteristics for the Gain

and Phase Measurement Mode

REV. B

�AD8302

Interfacing to the Input Channels

Dynamic Range

The single-ended input interfaces for both channels are identical.

Each consists of a driving pin, INPA and INPB, and an acgrounding pin, OFSA and OFSB. All four pins are internally

dc-biased at about 100 mV from the positive supply and should

be externally ac-coupled to the input signals and to ground. For

the signal pins, the coupling capacitor should offer negligible

impedance at the signal frequency. For the grounding pins, the

coupling capacitor has two functions: It provides ac grounding

and sets the high-pass corner frequency for the internal offset

compensation loop. There is an internal 10 pF capacitor to ground

that sets the maximum corner to approximately 200 MHz.

The corner can be lowered according the formula f HP (MHz) =

2/CC(nF), where CC is the total capacitance from OFSA or OFSB

to ground, including the internal 10 pF.

The maximum measurement range for the gain subsystem is limited to a total of 60 dB distributed from –30 dB to +30 dB. This

means that both gain and attenuation can be measured. The limits

are determined by the minimum and maximum levels that each

individual log amp can detect. In the AD8302, each log amp can

detect inputs ranging from –73 dBV [(223 µV, –60 dBm re: 50 Ω

to –13 dBV (223 mV, 0 dBm re: 50 Ω)]. Note that log

amps respond to voltages and not power. An equivalent power

can be inferred given an impedance level, e.g., to convert from

dBV to dBm in a 50 Ω system, simply add 13 dB. To cover

the entire range, it is necessary to apply a reference level to one log

amp that corresponds precisely to its midrange. In the AD8302,

this level is at –43 dBV, which corresponds to –30 dBm in a 50 Ω

environment. The other channel can now sweep from its low end,

30 dB below midrange, to its high end, 30 dB above midrange. If

the reference is displaced from midrange, some measurement

range will be lost at the extremes. This can occur either if the log

amps run out of range or if the rails at ground or 1.8 V are reached.

Figure 7 illustrates the effect of the reference channel level placement.

If the reference is chosen lower than midrange by 10 dB, then the

lower limit will be at –20 dB rather than –30 dB. If the reference chosen

is higher by 10 dB, the upper limit will be 20 dB rather than 30 dB.

The input impedance to INPA and INPB is a function of

frequency, the offset compensation capacitor, and package

parasitics. At moderate frequencies above fHP, the input network

can be approximated by a shunt 3 kΩ resistor in parallel with a

2 pF capacitor. At higher frequencies, the shunt resistance

decreases to approximately 500 Ω. The Smith Chart in Figure 6

shows the input impedance over the frequency range 100 MHz

to 3 GHz.

MAX RANGE FOR VREF = VREFOPT

VMAG – V

1.80

100MHz

900MHz

0.90

VREF > VREFOPT

VREF < VREFOPT

1.8GHz

2.7GHz

2.2GHz

3.0GHz

–30

0

+30

GAIN MEASUREMENT RANGE – dB

Figure 6. Smith Chart Showing the Input Impedance of a

Single Channel from 100 MHz to 3 GHz

A broadband resistive termination on the signal side of the coupling

capacitors can be used to match to a given source impedance.

The value of the termination resistor, RT, is determined by:

RT = RIN RS / (RIN − RS )

(10)

where RIN is the input resistance and RS the source impedance.

At higher frequencies, a reactive, narrow-band match might be

desirable to tune out the reactive portion of the input impedance.

An important attribute of the two-log-amp architecture is that if

both channels are at the same frequency and have the same input

network, then impedance mismatches and reflection losses become

essentially common-mode and hence do not impact the relative

gain and phase measurement. However, mismatches in these

external components can result in measurement errors.

REV. B

Figure 7. The Effect of Offsetting the Reference Level Is to

Reduce the Maximum Dynamic Range

The phase measurement range is of 0° to 180°. For phase differences of 0° to –180°, the transfer characteristics are mirrored as

shown in Figure 5, with a slope of the opposite sign. The phase

detector responds to the relative position of the zero crossings

between the two input channels. At higher frequencies, the finite

rise and fall times of the amplitude limited inputs create an

ambiguous situation that leads to inaccessible dead zones at the

0° and 180° limits. For maximum phase difference coverage, the

reference phase difference should be set to 90°.

–17–

�AD8302

Cross Modulation of Magnitude and Phase

At high frequencies, unintentional cross coupling between signals

in Channels A and B inevitably occurs due to on-chip and boardlevel parasitics. When the two signals presented to the AD8302

inputs are at very different levels, the cross coupling introduces

cross modulation of the phase and magnitude responses. If the two

signals are held at the same relative levels and the phase between

them is modulated then only the phase output should respond.

Due to phase-to-amplitude cross modulation, the magnitude output shows a residual response. A similar effect occurs when the

relative phase is held constant while the magnitude difference is

modulated, i.e., an expected magnitude response and a residual

phase response are observed due to amplitude-to-phase cross

modulation. The point where these effects are noticeable depends

on the signal frequency and the magnitude of the difference. Typically, for differences Gain SP

(13)

0 V if Gain < Gain SP

1.8 V if Phase > Phase SP

(14)

0 V if Phase < Phase SP

R2

VP

Figure 8. Increasing the Slope Requires the Inclusion of a

Voltage Divider

C7

R4

Repositioning the center point back to its original value of 0 dB

simply requires that an appropriate voltage be applied to the

grounded side of the lower resistor in the voltage divider. This

voltage may be provided externally or derived from the internal

reference voltage on pin VREF. For the specific choice of R2 =

20 kΩ, the center point is easily readjusted to 0 dB by connecting

the VREF pin directly to the lower pin of R2 as shown in Figure 9.

The increase in slope is now simplified to 1 + R1/10 kΩ. Since this

1.80 V reference voltage is derived from the same band gap

AD8302

1 COMM

MFLT 14

C1

VINA

C2

2 INPA

VMAG 13

VMAG

3 OFSA

MSET 12

VMSET

4 VPOS

VREF 11

5 OFSB

PSET 10

VPSET

6 INPB

VPHS 9

VPHS

7 COMM

PFLT 8

R1

C4

C6

VINB

R2

C5

C3

C8

Figure 10. Disconnecting the Feedback to the Setpoint

Controls, the AD8302 Operates in Comparator Mode

–18–

REV. B

�AD8302

When the insertion phase is nominal, the VPHS output is 900 mV.

Deviations from the nominal are reported with a 10 mV/degree

scaling. Table I gives suggested component values for the

measurement of an amplifier with a nominal gain of 10 dB and

an input power of –10 dBm.

The comparator mode can be turned into a controller mode by

closing the loop around the VMAG and VPHS outputs.

Figure 11 illustrates a closed loop controller that stabilizes the gain

and phase of a DUT with gain and phase adjustment elements.

If VMAG and VPHS are properly conditioned to drive gain and

phase adjustment blocks preceding the DUT, the actual gain and

phase of the DUT will be forced toward the prescribed setpoint

gain and phase given in Equations 11 and 12. These are essentially

AGC and APC loops. Note that as with all control loops of this kind,

loop dynamics and appropriate interfaces all must be considered

in more detail.

ATTENA

DCA

VP

OUTPUT

C7

AD8302

R4

1 COMM

MFLT 14

C1

2 INPA

⌬MAG

INPA

MSET

AD8302

PSET

INPB

MAG

SETPOINT

3 OFSA

MSET 12

4 VPOS

VREF 11

5 OFSB

PSET 10

6 INPB

VPHS 9

R5

C4

“BLACK BOX”

PHASE

SETPOINT

C6

R2

VPHS

⌬⌽

H

R6

C5

7 COMM

PFLT 8

C3

INPUT

Figure 11. By Applying Overall Feedback to a DUT Via

External Gain and Phase Adjusters, the AD8302 Acts

as a Controller

DCB

C8

ATTENB

Figure 12. Using the AD8302 to Measure the Gain and

Insertion Phase of an Amplifier or Mixer

APPLICATIONS

Measuring Amplifier Gain and Compression

The most fundamental application of AD8302 is the monitoring

of the gain and phase response of a functional circuit block such as

an amplifier or a mixer. As illustrated in Figure 12, directional

couplers, DCB and DCA, sample the input and output signals of

the “Black Box” DUT. The attenuators ensure that the signal

levels presented to the AD8302 fall within its dynamic range.

From the discussion in the Dynamic Range section, the optimal

choice places both channels at POPT = –30 dBm referenced to 50 Ω,

which corresponds to –43 dBV. To achieve this, the combination

of coupling factor and attenuation are given by:

Table I. Component Values for Measuring a 10 dB Amplifier

with an Input Power of –10 dBm

CB + LB = PIN − POPT

(15)

C A + L A = PIN + GAIN NOM − POPT

(16)

where CB and CA are the coupling coefficients, LB and LA are the

attenuation factors, and GAINNOM is the nominal DUT gain. If

identical couplers are used for both ports, then the difference in the

two attenuators compensates for the nominal DUT gain. When the

actual gain is nominal, the VMAG output is 900 mV, corresponding

to 0 dB. Variations from nominal gain appear as a deviation from

900 mV or 0 dB with a 30 mV/dB scaling. Depending on the nominal

insertion phase associated with DUT, the phase measurement may

require a fixed phase shift in series with one of the channels to bring

the nominal phase difference presented to the AD8302 near the

optimal 90° point.

REV. B

H

VMAG 13

R1

VMAG

C2

Component

Value

Quantity

R1, R2

R5, R6

C1, C4, C5, C6

C2, C8

C3

C7

AttenA

AttenB

DCA, DCB

52.3 Ω

100 Ω

0.001 µF

Open

100 pF

0.1 µF

10 dB (See Text)

1 dB (See Text)

20 dB

2

2

4

1

1

1

1

2

The gain measurement application can also monitor gain and

phase distortion in the form of AM-AM (gain compression) and

AM-PM conversion. In this case, the nominal gain and phase

corresponds to those at low input signal levels. As the input level

is increased, output compression and excess phase shifts are

measured as deviations from the low level case. Note that the signal

levels over which the input is swept must remain within the dynamic

range of the AD8302 for proper operation.

–19–

�AD8302

Reflectometer

The AD8302 can be configured to measure the magnitude ratio

and phase difference of signals that are incident on and reflected

from a load. The vector reflection coefficient, ⌫, is defined as,

Γ = Reflected Voltage / Incident Voltage = ( Z L − ZO ) / ( Z L + ZO ) (17)

where ZL is the complex load impedance and ZO is the characteristic system impedance.

The measurement accuracy can be compromised if board

level details are not addressed. Minimize the physical distance

between the series connected couplers since the extra path

length adds phase error to ⌫. Keep the paths from the couplers

to the AD8302 as well matched as possible since any differences

introduce measurement errors. The finite directivity, D, of the

couplers sets the minimum detectable reflection coefficient, i.e.,

| ΓMIN(dB)|