Low Power, High Output Current, Quad Op Amp,

Dual-Channel ADSL/ADSL2+ Line Driver

AD8392

PIN CONFIGURATIONS

FEATURES

GND

2

27

NC

PD1 1, 2

3

26

NC

+VIN1

4

25

+VIN2

–VIN1

5

24

–VIN2

VOUT1

6

23

VOUT2

VCC

7

22

NC

NC

8

21

VCC

VOUT3

9

20

VOUT4

–VIN3 10

19

–VIN4

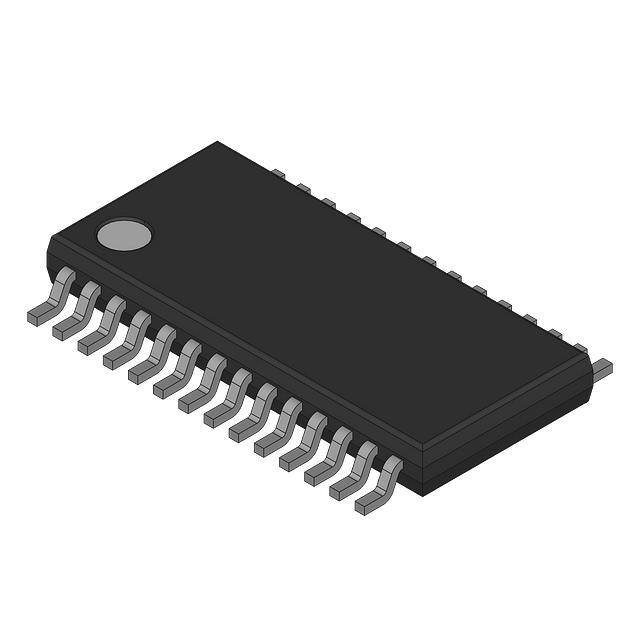

The AD8392 is available in two thermally enhanced packages, a

28-lead TSSOP/EP (AD8392ARE) and a 5 mm × 5 mm 32-lead

LFCSP (AD8392ACP). Four bias modes are available via the use

of two digital bits (PD1, PD0).

TE

3

+VIN3 11

4

+VIN4

NC 12

17

PD1 3, 4

NC 13

16

PD0 3, 4

GND 14

15

VEE

04802-0-001

18

NC = NO CONNECT

+VIN2

NC

VCOM1, 2

VEE

GND

PD0 1, 2

+VIN1

PD1 1, 2

Figure 1. AD8392ARE, 28-Lead TSSOP/EP

32 31 30 29 28 27 26 25

1

2

24

NC

23

–VIN2

–VIN1

2

VOUT1

3

22

VOUT2

VCC

4

21

NC

NC

5

VOUT3

6

–VIN3

7

NC

8

AD8392

3

VCC

VOUT4

18

–VIN4

17

NC

+VIN4

PD0 3, 4

VEE

10 11 12 13 14 15 16

GND

9

4

20

19

NC = NO CONNECT

04802-0-002

NC 1

PD1 3, 4

O

The AD8392 is comprised of four high output current, low

power consumption, operational amplifiers. It is particularly

well suited for the CO driver interface in digital subscriber line

systems, such as ADSL and ADSL2+. The driver is capable of

providing enough power to deliver 20.4 dBm to a line, while

compensating for losses due to hybrid insertion and back

termination resistors. In addition, the low distortion, fast slew

rate, and high output current capability make the AD8392 ideal

for many other applications, including medical instrumentation, DAC output drivers, and other high peak current circuits.

2

AD8392

VCOM3, 4

GENERAL DESCRIPTION

1

NC

B

SO

ADSL/ADSL2+ CO line drivers

XDSL line drives

High output current, low distortion amplifiers

DAC output buffer

28

PD0 1, 2

+VIN3

APPLICATIONS

VEE 1

LE

Four current feedback, high current amplifiers

Ideal for use as ADSL/ADSL2+ dual-channel Central Office

(CO) line drivers

Low power operation

Power supply operation from ±5 V (+10 V) up to ±12 V (+24 V)

Less than 3 mA/Amp quiescent supply current for full

power ADSL/ADSL2+ CO applications (20.4 dBm line

power, 5.5 CF)

Three active power modes plus shutdown

High output voltage and current drive

400 mA peak output drive current

44 V p-p differential output voltage

Low distortion

−72 dBc @1 MHz second harmonic

−82 dBc @ 1 MHz third harmonic

High speed: 900 V/µs differential slew rate

Additional functionality of AD8392ACP

On-chip common-mode voltage generation

Figure 2. AD8392ACP, 32-Lead LFCSP 5 mm × 5 mm

Additionally, the AD8392ACP provides VCOM pins for on-chip

common mode voltage generation.

The low power consumption, high output current, high output

voltage swing, and robust thermal packaging enable the

AD8392 to be used as the CO line drivers in ADSL and other

xDSL systems, as well as other high current, single-ended or

differential amplifier applications.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2005 Analog Devices, Inc. All rights reserved.

�AD8392

TABLE OF CONTENTS

Power Management ................................................................... 12

Absolute Maximum Ratings............................................................ 5

Driving Capacitive Loads.......................................................... 12

Thermal Resistance ...................................................................... 5

Thermal Considerations............................................................ 13

ESD Caution.................................................................................. 5

Typical ADSL/ADSL2+ Application........................................ 13

Typical Performance Characteristics ............................................. 6

Multitone Power Ratio............................................................... 14

Theory of Operation ...................................................................... 11

Lightning and AC Power Fault ................................................. 15

Applications..................................................................................... 12

Outline Dimensions ....................................................................... 16

Supplies, Grounding, and Layout............................................. 12

Ordering Guide .......................................................................... 16

Resistor Selection........................................................................ 12

LE

REVISION HISTORY

3/05—Rev. 0 to Rev. A

Changes to Figure 1 and Figure 2................................................... 1

Changes to Ordering Guide .......................................................... 16

O

B

SO

7/04—Revision 0: Initial Version

TE

Specifications..................................................................................... 3

Rev. A | Page 2 of 16

�AD8392

SPECIFICATIONS

VS = ±12 V or +24 V, RL = 100 Ω, G = +5, PD = (0, 0), T = 25°C, unless otherwise noted.

Table 1.

Typ

30

20

−5.0

64

42.0

21.0

Unit

Test Conditions/Comments

40

25

0.05

900

MHz

MHz

dB

V/µs

VOUT = 0.1 V p-p, RF = 2 kΩ

VOUT = 4 V p-p, RF = 2 kΩ

VOUT = 0.1 V p-p, RF = 2 kΩ

VOUT = 20 V p-p, RF = 2 kΩ

−72

−82

−70

4.3

10

13

dBc

dBc

dBc

nV/√Hz

pA/√Hz

pA/√Hz

fC = 1 MHz, VOUT = 2 V p-p

fC = 1 MHz, VOUT = 2 V p-p

26 kHz to 2.2 MHz, ZLINE = 100 Ω Differential Load

f = 10 kHz

f = 10 kHz

f = 10 kHz

mV

µA

µA

kΩ

pF

dB

V+IN − V−IN

∆VOUT

∆VOUT

RL = 10 Ω, fC = 100 kHz

±3.0

5.0

10.0

400

2.0

68

+5.0

10.0

15.0

44.0

22.0

400

46.0

23.0

V

V

mA

±12

24

V

V

7.0

4.0

3.3

1.2

0.8

mA/Amp

mA/Amp

mA/Amp

mA/Amp

V

V

dB

dB

LE

850

Max

TE

Min

O

B

SO

Parameter

DYNAMIC PERFORMANCE

−3 dB Small Signal Bandwidth

−3 dB Large Signal Bandwidth

Peaking

Slew Rate

NOISE/DISTORTION PERFORMANCE

Second Harmonic Distortion

Third Harmonic Distortion

Multitone Input Power Ratio

Voltage Noise (RTI)

+Input Current Noise

−Input Current Noise

INPUT CHARACTERISTICS

RTI Offset Voltage

+Input Bias Current

−Input Bias Current

Input Resistance

Input Capacitance

Common-Mode Rejection Ratio

OUTPUT CHARACTERISTICS

Differential Output Voltage Swing

Single-Ended Output Voltage Swing

Linear Output Current

POWER SUPPLY

Operating Range (Dual Supply)

Operating Range (Single Supply)

Total Quiescent Current

PD1, PD0 = (0, 0)

PD1, PD0 = (0, 1)

PD1, PD0 = (1, 0)

PD1, PD0 = (1, 1) (Shutdown State)

PD = 0 Threshold

PD = 1 Threshold

+Power Supply Rejection Ratio

−Power Supply Rejection Ratio

±5

10

6.0

3.6

2.8

0.4

1.8

64

76

68

79

Rev. A | Page 3 of 16

(∆VOS, DM (RTI))/(∆VIN, CM)

∆VOS, DM (RTI)/∆VCC, ∆VCC = ±1 V

∆VOS, DM (RTI)/∆VEE, ∆VEE = ±1 V

�AD8392

VS = ±5 V or +10 V, RL = 100 Ω, G = +5, PD = (0, 0), T = 25°C, unless otherwise noted.

Table 2.

Typ

30

20

300

400

Unit

Test Conditions/Comments

40

25

0.05

350

450

MHz

MHz

dB

V/µs

V/µs

VOUT = 0.1 V p-p, RF = 2 kΩ

VOUT = 4 V p-p, RF = 2 kΩ

VOUT = 0.1 V p-p, RF = 2 kΩ

VOUT = 7 V p-p, RF = 2 kΩ

VOUT = 7 V p-p, RF = 2 kΩ

−72

−82

4.3

10

13

dBc

dBc

nV/√Hz

pA/√Hz

pA/√Hz

fC = 1 MHz, VOUT = 2 V p-p

fC = 1 MHz, VOUT = 2 V p-p

f = 10 kHz

f = 10 kHz

f = 10 kHz

mV

µA

µA

kΩ

pF

dB

V+IN − V−IN

V

V

mA

∆VOUT

∆VOUT

RL = 10 Ω, fC = 100 kHz

±3.0

5.0

10.0

400

2.0

66

+5.0

10.0

15.0

16.0

8.0

400

18.0

9.0

LE

−5.0

Max

TE

Min

62

14.0

7.0

O

B

SO

Parameter

DYNAMIC PERFORMANCE

−3 dB Small Signal Bandwidth

−3 dB Large signal Bandwidth

Peaking

Slew Rate (Rise)

Slew Rate (Fall)

NOISE/DISTORTION PERFORMANCE

Second Harmonic Distortion

Third Harmonic Distortion

Voltage Noise (RTI)

+Input Current Noise

−Input Current Noise

INPUT CHARACTERISTICS

RTI Offset Voltage

+Input Bias Current

−Input Bias Current

Input Resistance

Input Capacitance

Common-Mode Rejection Ratio

OUTPUT CHARACTERISTICS

Differential Output Voltage Swing

Single-Ended Output Voltage Swing

Linear Output Current

POWER SUPPLY

Operating Range (Dual Supply)

Operating Range (Single Supply)

Total Quiescent Current

PD1, PD0 = (0, 0)

PD1, PD0 = (0, 1)

PD1, PD0 = (1, 0)

PD1, PD0 = (1, 1) (Shutdown State)

PD = 0 Threshold

PD = 1 Threshold

+Power Supply Rejection Ratio

−Power Supply Rejection Ratio

±5

+10

5.4

3.5

2.6

0.4

1.8

72

64

±12

+24

V

V

6.0

4.0

3.0

1.0

0.8

mA/Amp

mA/Amp

mA/Amp

mA/Amp

V

V

dB

dB

76

68

Rev. A | Page 4 of 16

(∆VOS, DM (RTI))/(∆VIN, CM)

∆VOS, DM (RTI)/∆VCC, ∆VCC = ±1 V

∆VOS, DM (RTI)/∆VEE, ∆VEE = ±1 V

�AD8392

ABSOLUTE MAXIMUM RATINGS

THERMAL RESISTANCE

In single supply with RL to VS−, worst case is VOUT = VS/2.

Airflow increases heat dissipation, effectively reducing θJA. Also,

more metal directly in contact with the package leads from

metal traces, through holes, ground, and power planes reduces

the θJA.

Figure 3 shows the maximum safe power dissipation in the

package versus the ambient temperature for the LFCSP-32 and

TSSOP-28/EP packages on a JEDEC standard 4-layer board. θJA

values are approximations.

7

θJA is specified for the worst-case conditions, i.e., θJA is specified

for device soldered in circuit board for surface-mount packages.

Table 4. Thermal Resistance

θJA

27.27

35.33

Unit

°C/W

°C/W

SO

Package Type

LFCSP-32 (CP)

TSSOP-28/EP (RE)

LFCSP-32

4

TSSOP-28/EP

3

2

1

0

10 20 30 40 50

TEMPERATURE (°C)

60

70

80

90

Figure 3. Maximum Power Dissipation vs. Temperature for a 4-Layer Board

See the Thermal Considerations section for additional thermal

design guidance.

O

B

The power dissipated in the package (PD) is the sum of the

quiescent power dissipation and the power dissipated in the

package due to the load drive for all outputs. The quiescent

power is the voltage between the supply pins (VS) times the

quiescent current (IS). Assuming that the load (RL) is midsupply,

the total drive power is VS/2 × IOUT, some of which is

dissipated in the package and some in the load (VOUT × IOUT).

5

0

–40 –30 –20 –10

Maximum Power Dissipation

TJ = 150°C

6

LE

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

RMS output voltages should be considered. If RL is referenced

to VS− as in single-supply operation, the total power is VS × IOUT.

04802-0-003

Rating

±13 V (+26 V)

See Figure 3

−65°C to +150°C

−40°C to +85°C

300°C

150°C

TE

Parameter

Supply Voltage

Power Dissipation

Storage Temperature

Operating Temperature Range

Lead Temperature Range (Soldering 10 sec)

Junction Temperature

MAXIMUM POWER DISSIPATION (W)

Table 3.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the

human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic

discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of

functionality.

Rev. A | Page 5 of 16

�AD8392

TYPICAL PERFORMANCE CHARACTERISTICS

950

–45

CREST FACTOR = 5.45

CREST FACTOR = 5.45

900

PD (0, 0)

POWER CONSUMPTION (mW)

–55

–60

PD (1, 0)

PD (0, 1)

PD (0, 0)

–65

850

800

PD (0, 1)

750

700

PD (1, 0)

650

TE

MULTITONE POWER RATIO (dBc)

–50

16

17

18

19

OUTPUT POWER (dBm)

20

21

550

15

17

18

19

OUTPUT POWER (dBm)

20

21

Figure 7. Power Consumption vs. Output Power (26 kHz to 2.2 MHz)

ADSL/ADSL2+ Circuit (Figure 32)

VS = ±12 V, RLOAD = 100 Ω, CF = 5.45

Figure 4. MTPR vs. Output Power (1.75 MHz Empty Bin)

ADSL/ADSL2+ Circuit (Figure 32)

VS = ±12 V, RLOAD = 100 Ω, CF = 5.45

HD2 PD (0, 1)

–60

–70

–80

B

SO

HD2 PD (0, 0)

HARMONIC DISTORTION (dBc)

HD2 PD (1, 0)

LE

–50

–50

HARMONIC DISTORTION (dBc)

16

04802-0-007

–70

15

04802-0-004

600

HD3 PD (1, 0)

HD3 PD (0, 0)

–90

HD2 PD (1, 0)

HD2 PD (0, 1)

–60

–70

HD2 PD (0, 0)

HD3 PD (1, 0)

–80

HD3 PD (0, 0)

–90

HD3 PD (0, 1)

10

–100

0.1

1

FREQUENCY (MHz)

Figure 8. Harmonic Distortion vs. Frequency

Dual Differential Driver Circuit (Figure 30)

VS = ±5 V, RLOAD = 100 Ω, G = +5, VOUT = 2 V p-p

Figure 5. Harmonic Distortion vs. Frequency

Dual Differential Driver Circuit (Figure 30)

VS = ±12 V, RLOAD = 100 Ω, G = +5, VOUT = 2 V p-p

–50

–50

HD2 PD (1, 0)

HD2 PD (0, 1)

O

HD2 PD (1, 0)

HD2 PD (0, 1)

–60

HARMONIC DISTORTION (dBc)

–70

–80

HD3 PD (0, 0)

HD3 PD (0, 1)

–90

HD3 PD (1, 0)

–100

–120

0.1

–70

–80

HD2 PD (0, 0)

HD3 PD (0, 0)

HD3 PD (0, 1)

–90

HD3 PD (1, 0)

–100

–110

–110

1

FREQUENCY (MHz)

10

04802-0-006

HARMONIC DISTORTION (dBc)

–60

HD2 PD (0, 0)

10

04802-0-008

1

FREQUENCY (MHz)

–120

0.1

1

FREQUENCY (MHz)

Figure 9. Harmonic Distortion vs. Frequency

Quad Op Amp Circuit (Figure 29)

VS = ±5 V, RLOAD = 100 Ω, G = +5, VOUT = 2 V p-p

Figure 6. Harmonic Distortion vs. Frequency

Quad Op Amp Circuit (Figure 29)

VS = ±12 V, RLOAD = 100 Ω, G = +5, VOUT = 2 V p-p

Rev. A | Page 6 of 16

10

04802-0-009

–100

0.1

04802-0-005

HD3 PD (0, 1)

�AD8392

15

15

10

10

PD (0, 0)

PD (0, 0)

5

5

GAIN (dB)

–5

PD (0, 1)

0

–5

–10

–10

–15

–15

PD (1, 0)

100

1000

Figure 10. Small Signal Frequency Response

Quad Op Amp Circuit (Figure 29)

VS = ±12 V, RLOAD = 100 Ω, G = +5, VOUT = 100 mV p-p

LE

–20

25Ω

50Ω

–5

–10

B

SO

1Ω

4.7Ω

SIGNAL FEEDTHROUGH (dB)

GAIN (dB)

0

–30

–40

–50

–60

–70

–80

1

10

FREQUENCY (MHz)

100

04802-0-011

10Ω

1000

–90

–100

0.1

Figure 11. Small Signal Frequency Response vs. Load

Quad Op Amp Circuit (Figure 29)

VS = ±12 V, G = +5, VOUT = 100 mV p-p

10

1000

–10

75Ω

100Ω

5

15

100

0

10

–20

0.1

10

FREQUENCY (MHz)

Figure 13. Small Signal Frequency Response

Quad Op Amp Circuit (Figure 29)

VS = ±5 V, RLOAD = 100 Ω, G = +5, VOUT = 100 mV p-p

15

–15

1

04802-0-013

10

FREQUENCY (MHz)

–20

0.1

TE

1

PD (1, 0)

04802-0-010

–20

0.1

1

10

FREQUENCY (MHz)

100

1000

Figure 14. Signal Feedthrough vs. Frequency

Quad Op Amp Circuit (Figure 29)

VS = ±12 V, G = +5, VIN = 800 mV p-p, PD (1, 1)

15

10

PD (0, 0)

PD (0, 1)

5

GAIN (dB)

0

–5

–10

–5

–10

–15

–15

PD (1, 0)

1

10

FREQUENCY (MHz)

100

1000

04802-0-012

PD (1, 0)

–20

0.1

PD (0, 0)

PD (0, 1)

0

–20

0.1

Figure 12. Large Signal Frequency Response

Quad Op Amp Circuit (Figure 29)

VS = ±12 V, RLOAD = 100 Ω, G = +5, VOUT = 4 V p-p

1

10

FREQUENCY (MHz)

100

Figure 15. Large Signal Frequency Response

Quad Op Amp Circuit (Figure 29)

VS = ±5 V, RLOAD = 100 Ω, G = +5, VOUT = 4 V p-p

Rev. A | Page 7 of 16

1000

04802-0-015

GAIN (dB)

O

5

04802-0-014

GAIN (dB)

PD (0, 1)

0

�AD8392

2.5

0.06

2.0

OUTPUT VOLTAGE (V)

1.5

0.02

0

–0.02

1.0

0.5

0

–0.5

–1.0

–1.5

–0.04

–4

–2

0

2

TIME (µs)

4

6

8

10

–2.5

–10

–8

–6

–4

–2

0

2

TIME (µs)

4

6

8

10

Figure 19. Large Signal Pulse Response

Quad Op Amp Circuit (Figure 29)

VS = ±12 V, RLOAD = 100 Ω, G = +5, 4 V Step

Figure 16. Small Signal Pulse Response

Quad Op Amp Circuit (Figure 29)

VS = ±12 V, RLOAD = 100 Ω, G = +5, 100 mV Step

LE

PD PINS

OUTPUT

1

1

OUTPUT

2

004802-0-017

004802-0-020

B

SO

2

PD PINS

CH1 200mVΩ BW CH2 1.00mVΩ BW M 50.0ns

A CH2

CH1 200mVΩBW CH2 1.00VΩBW

2.38V

∆: 420ns

@: 2.84µs

C1 p-p

27.0V

C2 p-p

21.4V

C1 p-p

6.00V

C2 p-p

21.8V

1

2

004802-0-018

CH1

004802-0-021

OUTPUT

OUTPUT

INPUT

M1.00µs

2.38V

∆: 460ns

@: –1.32µs

1

2

CH2 5.00VΩ

CH2

Figure 20. Power-Down Time: PD (0, 0) to PD (1, 1)

Quad Op Amp Circuit (Figure 29)

VS = ±12 V, RLOAD = 100 Ω, G = +5, VOUT = 1 V p-p

Figure 17. Power-Up Time: PD (1, 1) to PD (0, 0)

Quad Op Amp Circuit (Figure 29)

VS = ±12 V, RLOAD = 100 Ω, G = +5, VOUT = 1 V p-p

CH1 5.00VΩ

M 400ns

INPUT

CH1 1.00VΩ

700mV

CH2 5.00VΩ

M1.00µs

CH1

800mV

Figure 21. Output Overdrive Recovery

Quad Op Amp Circuit (Figure 29)

VS = ±12 V, RLOAD = 100 Ω, G = +5, VIN = 6 V p-p

Figure 18. Input Overdrive Recovery

Quad Op Amp Circuit (Figure 29)

VS = ±12 V, RLOAD = 100 Ω, G = +1, VIN = 27 V p-p

Rev. A | Page 8 of 16

04802-0-019

–6

TE

–8

04802-0-016

–2.0

–0.06

–10

O

OUTPUT VOLTAGE (V)

0.04

�0

0

–10

–10

–20

–20

–30

–30

CROSSTALK (dB)

–40

–50

ADSL CHANNEL 3, 4

–60

ADSL CHANNEL 1, 2

–70

–50

DIFF CHANNEL 3, 4

–60

DIFF CHANNEL 1, 2

–70

–80

1

10

FREQUENCY (MHz)

100

100

45

0

VS = ±12V

–10

LE

DIFFERENTIAL OUTPUT SWING (V)

40

–20

–30

–40

–50

–60

CHANNEL 1

B

SO

–80

1

10

FREQUENCY (MHz)

Figure 25. Crosstalk vs. Frequency

Dual Differential Driver Circuit (Figure 30)

VS = ±12 V, G = +5, RLOAD = 100 Ω, VIN = 200 mV p-p

Figure 22. Crosstalk vs. Frequency

ADSL/ADSL2+ Circuit (Figure 32)

VS = ±12 V, G = +11, RLOAD = 100 Ω, VIN = 200 mV p-p

–70

–90

0.1

TE

–90

0.1

04802-0-022

–80

CROSSTALK (dB)

–40

04802-0-025

CROSSTALK (dB)

AD8392

CHANNEL 2

CHANNEL 3

35

30

25

20

VS = ±5V

15

10

10

Figure 23. Crosstalk vs. Frequency

Quad Op Amp Circuit (Figure 29)

VS = ±12 V, G = +5, RLOAD = 100 Ω, VIN = 200 mV p-p

1

0.01

0.1

1

10

100

FREQUENCY (kHz)

1000

40

50

60

70

RESISTIVE LOAD (Ω)

80

90

100

1000

04802-0-024

10

30

Figure 26. Differential Output Swing vs. RLOAD

ADSL/ADSL2+ Circuit (Figure 32)

G = +11

CURRENT NOISE (pA/ Hz)

O

VOLTAGE NOISE (nV/ Hz)

100

20

04802-0-026

100

Figure 24. Voltage Noise vs. Frequency

100

–INOISE

10

1

0.01

+INOISE

0.1

1

10

100

FREQUENCY (kHz)

Figure 27. Current Noise vs. Frequency

Rev. A | Page 9 of 16

1000

04802-0-027

1

10

FREQUENCY (MHz)

04802-0-023

CHANNEL 4

–90

0.1

�AD8392

180

1G

60

40

10

20

1

0

0.1

–20

0.01

–40

0.001

–60

1k

10k

100k

1M

10M

–80

1G

100M

FREQUENCY (Hz)

Figure 28. Open-Loop Transimpedance and Phase

10

PD (0, 0)

PD (0, 1)

1

0.1

0.01

0.01

0.1

10

1

100

1000

TE

1k

100

OUTPUT IMPEDANCE (Ω)

80

PHASE (Degrees)

10k

04802-0-028

100

FREQUENCY (MHz)

Figure 31. Output Impedance vs. Frequency

Quad Op Amp Circuit (Figure 29)

VS = ±12 V, G = +5, PD (0, 0)

280kΩ

162Ω

49.9Ω

100Ω

2kΩ

04802-0-033

499Ω

162Ω

B

SO

Figure 29. Quad Op Amp Circuit

49.9Ω

2kΩ

1kΩ

100Ω

49.9Ω

04802-0-030

2kΩ

100nF

2kΩ

226Ω

VCM

100nF

100nF

6.19Ω

Figure 30. Dual Differential Driver Circuit

Rev. A | Page 10 of 16

100Ω

100nF

2kΩ

6.19Ω

866Ω

280kΩ

Figure 32. ADSL/ADSL2+ Circuit

04802-0-032

100nF

866Ω

LE

100nF

O

TRANSIMPEDANCE (Ω)

120

TRANSIMPEDANCE

100k

0.0001

100

PD (1, 0)

140

10M

1M

100

160

PHASE

04802-0-031

100M

�AD8392

THEORY OF OPERATION

VO

TZ (S )

= G×

VIN

TZ (S ) + G × RIN + RF

1

≈ 50 Ω

gm

RIN

IIN

TZ

VOUT

RN

VIN

The AD8392 is capable of delivering 400 mA of output current

while swinging to within 2 V of either power supply rail. The

AD8392 also has a power management system included on-chip.

It features four user-programmable power levels (three active

power modes as well as the provision for complete shutdown).

LE

R IN =

RF

RG

RG

Figure 33. Simplified Block Diagram

where:

G = 1+

RF

04802-0-034

The open-loop transimpedance is analogous to the open-loop

voltage gain of a voltage feedback amplifier. Figure 33 shows a

simplified model of a current feedback amplifier. Since RIN is

proportional to 1/gm, the equivalent voltage gain is just TZ × gm,

where gm is the transconductance of the input stage. Basic

analysis of the follower with gain circuit yields

Of course, for a real amplifier there are additional poles that

contribute excess phase, and there is a value for RF below which

the amplifier is unstable. Tolerance for peaking and desired

flatness determines the optimum RF in each application.

TE

The AD8392 is a current feedback amplifier with high

(400 mA) output current capability. With a current feedback

amplifier, the current into the inverting input is the feedback

signal, and the open-loop behavior is that of a transimpedance,

dVO/dIIN or TZ.

O

B

SO

Since G × RIN