Integrated, Dual RF Transceiver

with Observation Path

AD9371

Data Sheet

FEATURES

FUNCTIONAL BLOCK DIAGRAM

EXTERNAL

OPTION

SPI

PORT

TX1

LPF

TX2

DAC

TX2+

TX2–

pFIR,

QEC,

INTERPOLATION

LPF

DAC

LO

GENERATOR

RF

SYNTHESIZER

GPIO

AUXADC

AUXDAC

EXTERNAL

OPTION

LO

GENERATOR

RF

SYNTHESIZER

ORX1+

ORX1–

The AD9371 is a highly integrated, wideband RF transceiver

offering dual channel transmitters and receivers, integrated

synthesizers, and digital signal processing functions. The IC

delivers a versatile combination of high performance and low

power consumption required by 3G/4G micro and macro BTS

equipment in both FDD and TDD applications. The AD9371

operates from 300 MHz to 6000 MHz, covering most of the

licensed and unlicensed cellular bands. The IC supports receiver

bandwidths up to 100 MHz. It also supports observation receiver

and transmit synthesis bandwidths up to 250 MHz to

accommodate digital correction algorithms.

ORX2+

ORX2–

SNRXA+

SNRXA–

SNRXB+

SNRXB–

SNRXC+

SNRXC–

CLOCK

GENERATOR

OBSERVATION

Rx

SNIFFER

Rx

LPF

ADC

LPF

ADC

NOTES

1. FOR JESD204B PINS, SEE FIGURE 4.

DECIMATION,

pFIR,

AGC,

DC OFFSET,

QEC,

TUNING,

RSSI,

OVERLOAD

14651-001

TX1–

RF

SYNTHESIZER

SPI

TX1+

LO

GENERATOR

JESD204B

RX_EXTLO–

JESD204B

MICROCONTROLLER

RX_EXTLO+

GENERAL DESCRIPTION

Rev. B

LPF

ADC

3G/4G micro and macro base stations (BTS)

3G/4G multicarrier picocells

FDD and TDD active antenna systems

Microwave, nonline of sight (NLOS) backhaul systems

An observation receiver channel with two inputs is included to

monitor each transmitter output and implement interference

mitigation and calibration applications. This channel also connects

to three sniffer receiver inputs that can monitor radio activity in

different bands.

ADC

RX2–

TX_EXTLO+

TX_EXTLO–

The transceiver consists of wideband direct conversion signal

paths with state-of-the-art noise figure and linearity. Each complete

receiver and transmitter subsystem includes dc offset correction,

quadrature error correction (QEC), and programmable digital

filters, eliminating the need for these functions in the digital

baseband. Several auxiliary functions such as an auxiliary analogto-digital converter (ADC), auxiliary digital-to-analog converters

(DACs), and general-purpose input/outputs (GPIOs) are integrated

to provide additional monitoring and control capability.

DECIMATION,

pFIR,

DC OFFSET

QEC,

TUNING,

RSSI,

OVERLOAD

LPF

RX2

RX2+

CTRL I/F

RX1–

RX1

DEV_CLK_IN+,

DEV_CLK_IN–

APPLICATIONS

AD9371

RX1+

JESD204B

Dual differential transmitters (Tx)

Dual differential receivers (Rx)

Observation receiver (ORx) with 2 inputs

Sniffer receiver (SnRx) with 3 inputs

Tunable range: 300 MHz to 6000 MHz

Tx synthesis bandwidth (BW) to 250 MHz

Rx BW: 8 MHz to 100 MHz

Supports frequency division duplex (FDD) and time division

duplex (TDD) operation

Fully integrated independent fractional-N radio frequency (RF)

synthesizers for Tx, Rx, ORx, and clock generation

JESD204B digital interface

Figure 1.

The high speed JESD204B interface supports lane rates up to

6144 Mbps. Four lanes are dedicated to the transmitters and four

lanes are dedicated to the receiver and observation receiver channels.

The fully integrated phase-locked loops (PLLs) provide high

performance, low power fractional-N frequency synthesis for

the transmitter, the receiver, the observation receiver, and the

clock sections. Careful design and layout techniques provide the

isolation demanded in high performance base station applications.

All voltage controlled oscillator (VCO) and loop filter components

are integrated to minimize the external component count.

A 1.3 V supply is required to power the core of the AD9371, and

a standard 4-wire serial port controls it. Other voltage supplies

provide proper digital interface levels and optimize transmitter

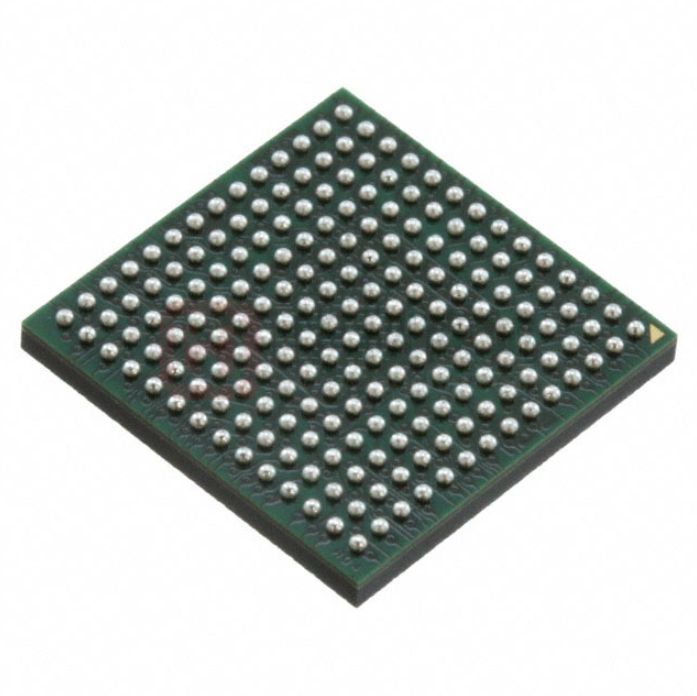

and auxiliary converter performance. The AD9371 is packaged in a

12 mm × 12 mm, 196-ball chip scale ball grid array (CSP_BGA).

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2016–2017 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

�AD9371

Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

5.5 GHz Band .............................................................................. 46

Applications ....................................................................................... 1

Theory of Operation ...................................................................... 54

General Description ......................................................................... 1

Transmitter (Tx) ......................................................................... 54

Functional Block Diagram .............................................................. 1

Receiver (Rx) ............................................................................... 54

Revision History ............................................................................... 2

Observation Receiver (ORx)..................................................... 54

Specifications..................................................................................... 3

Sniffer Receiver (SnRx) ............................................................. 54

Current and Power Consumption Specifications..................... 9

Clock Input.................................................................................. 54

Timing Specifications ................................................................ 10

Synthesizers ................................................................................. 55

Absolute Maximum Ratings.......................................................... 12

Serial Peripheral Interface (SPI) Interface .............................. 55

Reflow Profile .............................................................................. 12

GPIO_x AND GPIO_3P3_x Pins ............................................ 55

Thermal Resistance .................................................................... 12

Auxiliary Converters .................................................................. 55

ESD Caution ................................................................................ 12

JESD204B Data Interface .......................................................... 55

Pin Configuration and Function Descriptions ........................... 13

Power Supply Sequence ............................................................. 56

Typical Performance Characteristics ........................................... 16

JTAG Boundary Scan ................................................................. 56

700 MHz Band ............................................................................ 16

Outline Dimensions ....................................................................... 57

2.6 GHz Band .............................................................................. 26

Ordering Guide .......................................................................... 57

3.5 GHz Band .............................................................................. 36

REVISION HISTORY

3/2017—Rev. A to Rev. B

Change to Table 1............................................................................. 6

Deleted Figure 230 through Figure 239; Renumbered

Sequentially ..................................................................................... 55

Changes to Sniffer Receiver (SnRx) Section ............................... 55

11/2016—Rev. 0 to Rev. A

Changes to Table 1 ............................................................................ 6

Changes to Table 2 ............................................................................ 9

Changes to L3, L4 Description Column, Table 6; M3, M4

Description Column, Table 6; and M13, M14 Description

Column, Table 6 .............................................................................. 16

Changes to Figure 46 Caption....................................................... 23

Changes to Figure 48 Caption....................................................... 24

Changes to Figure 56 Caption and Figure 57 Caption .............. 25

Changes to Figure 82 Caption....................................................... 30

Changes to Figure 105 Caption .................................................... 33

Changes to Figure 107 Caption .................................................... 34

Changes to Figure 115 Caption and Figure 116 Caption .......... 35

Changes to Figure 141 Caption .................................................... 40

Changes to Figure 164 Caption .................................................... 43

Changes to Figure 166 Caption .................................................... 44

Changes to Figure 174 Caption and Figure 175 ......................... 45

Changes to Figure 194 and Figure 199 Caption ......................... 49

Changes to Figure 222 Caption .................................................... 53

Changes to Figure 224 Caption .................................................... 54

Added Figure 230 to Figure 235; Renumbered Sequentially .... 55

Added Figure 236 to Figure 239 ................................................... 56

Added External LO Inputs Section .............................................. 58

7/2016—Revision 0: Initial Version

Rev. B | Page 2 of 57

�Data Sheet

AD9371

SPECIFICATIONS

Electrical characteristics at ambient temperature range, VDDA_SER = 1.3 V, VDDA_DES = 1.3 V, JESD_VTT_DES = 1.3 V, VDDA_1P31 =

1.3 V, VDIG = 1.3 V, VDDA_1P8 = 1.8 V, VDD_IF = 2.5 V, and VDDA_3P3 = 3.3 V; all RF specifications based on measurements that

include printed circuit board (PCB) and matching circuit losses, unless otherwise noted.

Table 1.

Parameter

TRANSMITTERS (Tx)

Center Frequency

Tx Large Signal Bandwidth (BW)

Tx Synthesis BW2

Symbol

Min

Typ

300

BW Flatness

Deviation from Linear Phase

Power Control Range

Unit

6000

100

250

MHz

MHz

MHz

±0.5

dB

±0.15

dB

10

0

Power Control Resolution

ACLR5 (Four Universal Mobile

Telecommunications System

(UMTS) Carriers)

700 MHz Local Oscillator (LO)

2600 MHz LO

3500 MHz LO

5500 MHz LO

In-Band Noise

Tx to Tx Isolation

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Image Rejection

42

0.05

Degrees

dB

Test Conditions/Comments

Wider bandwidth for use in

digital processing algorithms

250 MHz BW, compensated

by programmable finite

infinite response (FIR) filter

Any 20 MHz BW span,

compensated by

programmable FIR filter

250 MHz BW

Increased calibration time,

reduced QEC3, LOL4

performance beyond 20 dB

dB

−11.2 dBFS rms, 0 dB RF

attenuation

−64

−64

−63

−61

−155

dB

dB

dB

dB

dBFS6/Hz

70

65

65

65

dB

dB

dB

dB

Up to 20 dB RF attenuation,

within large signal BW,

QEC3 active

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Maximum Output Power

65

65

65

50

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Output Third-Order Intercept Point

7

7

6

4

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Max

dB

dB

dB

dB

0 dBFS, 1 MHz signal input,

50 Ω load, 0 dB RF attenuation

dBm

dBm

dBm

dBm

OIP3

−5 dBFS rms, 0 dB RF

attenuation

27

27

25

25

Rev. B | Page 3 of 57

dBm

dBm

dBm

dBm

�AD9371

Parameter

Carrier Leakage

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Error Vector Magnitude (3GPP

Test Signals)

Data Sheet

Symbol

Min

dBFS6

dBFS6

dBFS6

dBFS6

−45

−39

−38.5

−37.5

50

300

0

Rx Alias Band Rejection

Maximum Recommended Input

Power8

75

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Test Conditions/Comments

After calibration, LOL

correction active, CW7 input

signal, 3 dB RF and 3 dB digital

attenuation, 40 kHz

measurement BW

Long-term evolution (LTE)

20 MHz downlink,

5 dB RF attenuation

8

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Input Second-Order Intercept

Point

Unit

EVM

Rx Bandwidth

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Input Third-Order Intercept Point

Max

−81

−81

−81

−75

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Output Impedance

RECEIVERS (Rx)

Center Frequency

Gain Range

Analog Gain Step

BW Ripple

Noise Figure

Typ

dB

dB

dB

dB

Ω

6000

30

0.5

±0.5

MHz

dB

dB

dB

±0.2

dB

100

MHz

−14

dB

dBm

12

13.5

14

18

dB

dB

dB

dB

NF

IIP3

Differential

100 MHz BW, compensated

by programmable FIR filter

Any 20 MHz span,

compensated by

programmable FIR filter

Analog low-pass filter (LPF)

BW is 20 MHz minimum,

programmable FIR BW

configurable over the entire

range

Due to digital filters

Input is a CW7 signal at a 0 dB

attenuation setting; this level

increases decibel for decibel

with attenuation

Maximum Rx gain, at

Rx port, matching losses

de-embedded

Maximum Rx gain, thirdorder intermodulation (IM3)

1 MHz offset from LO

22

22

20

20

dBm

dBm

dBm

dBm

IIP2

Maximum Rx gain, secondorder intermodulation (IM2)

1 MHz offset from LO

65

65

65

57

Rev. B | Page 4 of 57

dBm

dBm

dBm

dBm

�Data Sheet

Parameter

Image Rejection

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Input Impedance

Tx1 to Rx1 Signal Isolation and

Tx2 to Rx2 Signal Isolation

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Tx1 to Rx2 Signal Isolation and

Tx2 to Rx1 Signal Isolation

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Rx1 to Rx2 Signal Isolation

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Rx Band Spurs Referenced to

RF Input at Maximum Gain

AD9371

Symbol

Min

Typ

Max

Unit

75

75

75

75

200

dB

dB

dB

dB

Ω

68

68

62

60

dB

dB

dB

dB

70

70

62

60

dB

dB

dB

dB

60

60

60

60

−95

dB

dB

dB

dB

dBm

−65

−65

−62

−62

dBm

dBm

dBm

dBm

Rx LO Leakage at Rx Input at

Maximum Gain

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

OBSERVATION RECEIVER (ORx)

Center Frequency

Gain Range

Analog Gain Step

BW Ripple

300

0

1

±0.5

Deviation from Linear Phase

ORx Bandwidth

ORx Alias Band Rejection

Maximum Recommended Input

Power8

Signal-to-Noise Ratio9

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

6000

18

10

MHz

dB

dB

dB

−13

Degrees

MHz

dB

dBm

60

60

60

59

dB

dB

dB

dB

250

60

SNR

Rev. B | Page 5 of 57

Test Conditions/Comments

QEC3 active, within Rx BW

Differential

No more than one spur at

this level per 10 MHz of Rx

BW; excludes harmonics of

the reference clock

Leakage decreases decibel

for decibel with attenuation

for first 12 dB

250 MHz RF BW, compensated

by programmable FIR filter

250 MHz RF BW

Due to digital filters

Input is a CW7 signal at 0 dB

attenuation setting; this level

increases decibel for decibel

with attenuation

Maximum gain at ORx port

200 MHz BW, 245.76 MSPS

�AD9371

Parameter

Input Third-Order Intercept Point

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Input Second-Order Intercept

Point

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Image Rejection

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Input Impedance

Tx1 to ORx1 Signal and Tx2 to

ORx2 Signal Isolation

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

Tx1 to ORx2 Signal and Tx2 to

ORx1 Signal Isolation

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

SNIFFER RECEIVER (SnRx)

Center Frequency

Gain Range

Analog Gain Step

BW Ripple

Rx Bandwidth

Rx Alias Band Rejection

Maximum Recommended Input

Power8

Noise Figure

700 MHz LO

2600 MHz LO

3500 MHz LO

Input Third-Order Intercept Point

700 MHz LO

2600 MHz LO

3500 MHz LO

Data Sheet

Symbol

IIP3

Min

Typ

Max

22

22

18

18

Unit

Test Conditions/Comments

Maximum ORx gain,

IM3 1 MHz offset from LO

dBm

dBm

dBm

dBm

IIP2

Maximum ORx gain, IM2

1 MHz offset from LO

65

65

65

60

dBm

dBm

dBm

dBm

65

65

65

65

200

dB

dB

dB

dB

Ω

70

70

70

70

dB

dB

dB

dB

70

70

70

70

dB

dB

dB

dB

After online tone calibration

300

0

4000

52

1

±0.5

20

MHz

dB

dB

dB

−26

MHz

dB

dBm

5

5

7

dB

dB

dB

60

NF

IIP3

Differential

20 MHz RF BW, compensated

by programmable FIR filter

Due to digital filters

Input is a CW7 signal at 0 dB

attenuation setting

Maximum gain at

SnRx port, matching losses

de-embedded, gain control

limited to the first 20 steps

Maximum gain, IM3 1 MHz

offset from LO, gain control

limited to the first 20 steps

1

1

1

Rev. B | Page 6 of 57

dBm

dBm

dBm

�Data Sheet

Parameter

Input Second-Order Intercept

Point

AD9371

Symbol

IIP2

Min

700 MHz LO

2600 MHz LO

3500 MHz LO

Image Rejection

700 MHz LO

2600 MHz LO

3500 MHz LO

Input Impedance

Tx1 to SnRx Signal and Tx2 to

SnRx Signal Isolation

700 MHz LO

2600 MHz LO

3500 MHz LO

LO SYNTHESIZER

LO Frequency Step

Spot Phase Noise

700 MHz LO

10 kHz

100 kHz

1 MHz

2600 MHz LO

10 kHz

100 kHz

1 MHz

3500 MHz LO

10 kHz

100 kHz

1 MHz

5500 MHz LO

10 kHz

100 kHz

1 MHz

Integrated Phase Noise

Input Signal Power

Max

Unit

45

45

45

dBm

dBm

dBm

75

75

75

400

dB

dB

dB

Ω

60

60

60

dB

dB

dB

2.3

Hz

−80

dBc

−104

−107

−133

dBc

dBc

dBc

−93

−97

−123

dBc

dBc

dBc

−91

−97

−123

dBc

dBc

dBc

−98

−100

−110

dBc

dBc

dBc

Test Conditions/Comments

Maximum gain, IM2 1 MHz

offset from LO, gain control

limited to the first 20 steps

After online tone calibration

LO Spectral Purity

700 MHz LO

2600 MHz LO

3500 MHz LO

5500 MHz LO

EXTERNAL LO INPUT

Input Frequency

Typ

Differential

Applies to each SnRx input

1.5 GHz to 3 GHz, 76.8 MHz

phase frequency detector

(PFD) frequency

Excludes integer boundary

spurs 1 kHz to 100 MHz

Integrated from 1 kHz to

100 MHz

0.20

0.49

0.55

0.75

fEXTLO

600

0

3

Rev. B | Page 7 of 57

°rms

°rms

°rms

°rms

8000

MHz

6

dBm

Input frequency must be 2×

the desired LO frequency

50 Ω matching at the source

�AD9371

Parameter

REFERENCE CLOCK (DEV_CLK_IN

SIGNAL)

Frequency Range

Signal Level

AUXILIARY CONVERTERS

ADC

ADC Resolution

Input Voltage

Minimum

Maximum

DAC

DAC Resolution

Output Voltage

Minimum

Maximum

Drive Capability

DIGITAL SPECIFICATIONS (CMOS),

GPIO_x, RX1_ENABLE,

RX2_ENABLE, TX1_ENABLE, TX2

ENABLE, SYNCINBx+,

SYNCOUTB0+, GP_INTERRUPT,

SDIO, SDO, SCLK, CSB, RESET

Logic Inputs

Input Voltage

High Level

Low Level

Input Current

High Level

Low Level

Logic Outputs

Output Voltage

High Level

Data Sheet

Symbol

Min

Typ

10

0.3

Input Differential Voltage

Threshold

Receiver Differential Input

Impedance

Unit

320

2.0

MHz

V p-p

Test Conditions/Comments

AC-coupled, common-mode

voltage (VCM) = 618 mV; for

best spurious performance,

use a