FUNCTIONAL BLOCK DIAGRAM

APPLICATIONS

Low jitter, low phase noise clock distribution

Clock generation and translation for SONET, 10Ge, 10GFC,

Synchronous Ethernet, OTU2/3/4

Forward error correction (G.710)

Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs

High performance wireless transceivers

ATE and high performance instrumentation

Broadband infrastructures

GENERAL DESCRIPTION

The AD9520-31 provides a multioutput clock distribution

function with subpicosecond jitter performance, along with an

on-chip PLL and VCO. The on-chip VCO tunes from 1.72 GHz

to 2.25 GHz. An external 3.3 V/5 V VCO/VCXO of up to 2.4 GHz

can also be used.

1

LF

CP

OPTIONAL

REF1

REFIN

REFIN

CLK

REF2

STATUS

MONITOR

PLL

Low phase noise, phase-locked loop (PLL)

On-chip VCO tunes from 1.72 GHz to 2.25 GHz

Optional external 3.3 V/5 V VCO/VCXO to 2.4 GHz

1 differential or 2 single-ended reference inputs

Accepts CMOS, LVDS, or LVPECL references to 250 MHz

Accepts 16.62 MHz to 33.3 MHz crystal for reference input

Optional reference clock doubler

Reference monitoring capability

Automatic/manual reference holdover and reference

switchover modes, with revertive switching

Glitch-free switchover between references

Automatic recovery from holdover

Digital or analog lock detect, selectable

Optional zero delay operation

Twelve 1.6 GHz LVPECL outputs divided into 4 groups

Each group of 3 outputs shares a 1-to-32 divider with

phase delay

Additive output jitter as low as 225 fs rms

Channel-to-channel skew grouped outputs < 16 ps

Each LVPECL output can be configured as 2 CMOS outputs

(for fOUT ≤ 250 MHz)

Automatic synchronization of all outputs on power-up

Manual output synchronization available

SPI- and I²C-compatible serial control port

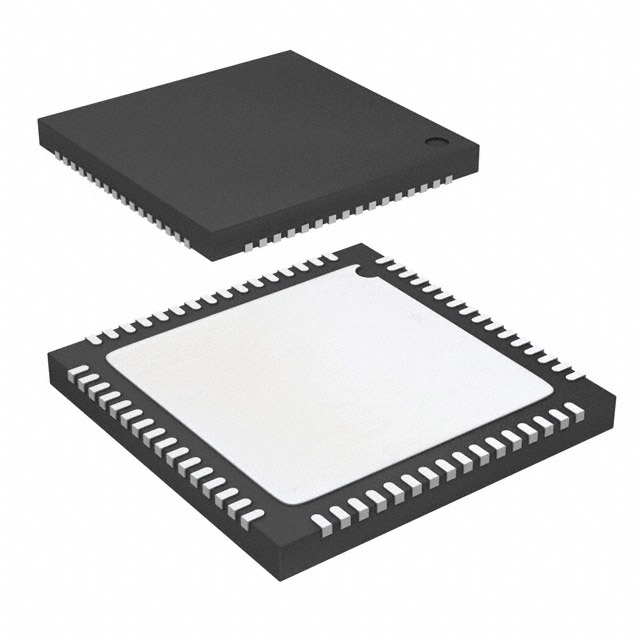

64-lead LFCSP

Nonvolatile EEPROM stores configuration settings

DIVIDER

AND MUXES

VCO

ZERO

DELAY

LVPECL/

CMOS

DIV/Φ

OUT0

OUT1

OUT2

DIV/Φ

OUT3

OUT4

OUT5

DIV/Φ

OUT6

OUT7

OUT8

DIV/Φ

OUT9

OUT10

OUT11

SPI/I2C CONTROL

PORT AND

DIGITAL LOGIC

EEPROM

AD9520

07216-001

FEATURES

SWITCHOVER

AND MONITOR

Data Sheet

12 LVPECL/24 CMOS Output Clock

Generator with Integrated 2 GHz VCO

AD9520-3

Figure 1.

The AD9520-3 serial interface supports both SPI and I²C ports.

An in-package EEPROM, which can be programmed through the

serial interface, can store user-defined register settings for

power-up and chip reset.

The features 12 LVPECL outputs in four groups. Any of the 1.6

GHz LVPECL outputs can be reconfigured as two 250 MHz

CMOS outputs. If an application requires LVDS drivers instead

of LVPECL drivers, refer to the AD9522-3.

Each group of three outputs has a divider that allows both the

divide ratio (from 1 to 32) and the phase offset or coarse time

delay to be set.

The is available in a 64-lead LFCSP and can be operated from a

single 3.3 V supply. The external VCO can have an operating

voltage of up to 5.5 V. A separate output driver power supply

can be from 2.375 V to 3.465 V.

The AD9520-3 is specified for operation over the standard

industrial range of −40°C to +85°C.

AD9520 is used throughout this data sheet to refer to all the members of the AD9520 family. However, when AD9520-3 is used, it refers to that specific member of the

AD9520 family.

Rev. B

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2008–2016 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

�AD9520-3

Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

Pin Configuration and Function Descriptions........................... 18

Applications ....................................................................................... 1

Typical Performance Characteristics ........................................... 21

General Description ......................................................................... 1

Terminology .................................................................................... 26

Functional Block Diagram .............................................................. 1

Detailed Block Diagram ................................................................ 27

Revision History ............................................................................... 3

Theory of Operation ...................................................................... 28

Specifications..................................................................................... 4

Operational Configurations ...................................................... 28

Power Supply Requirements ....................................................... 4

Zero Delay Operation ................................................................ 42

PLL Characteristics ...................................................................... 4

Clock Distribution ..................................................................... 43

Clock Inputs .................................................................................. 7

Reset Modes ................................................................................ 49

Clock Outputs ............................................................................... 7

Power-Down Modes .................................................................. 50

Timing Characteristics ................................................................ 8

Serial Control Port ......................................................................... 51

Clock Output Additive Phase Noise (Distribution Only; VCO

Divider Not Used) ...................................................................... 10

SPI/I²C Port Selection................................................................ 51

Clock Output Absolute Phase Noise (Internal VCO Used) .. 11

SPI Serial Port Operation .......................................................... 54

Clock Output Absolute Time Jitter (Clock Generation Using

Internal VCO) ............................................................................. 11

SPI Instruction Word (16 Bits) ................................................. 55

Clock Output Absolute Time Jitter (Clock Cleanup Using

Internal VCO) ............................................................................. 11

EEPROM Operations ..................................................................... 58

Clock Output Absolute Time Jitter (Clock Generation Using

External VCXO) ......................................................................... 12

Writing to the EEPROM ........................................................... 58

Reading from the EEPROM ..................................................... 58

Clock Output Additive Time Jitter (VCO Divider Not Used)

....................................................................................................... 12

Programming the EEPROM Buffer Segment ......................... 59

Thermal Performance .................................................................... 60

Clock Output Additive Time Jitter (VCO Divider Used) ..... 12

Register Map ................................................................................... 61

Serial Control Port—SPI Mode ................................................ 13

Register Map Descriptions ............................................................ 64

Serial Control Port—I²C Mode ................................................ 14

Applications Information .............................................................. 77

PD, EEPROM, RESET, and SYNC Pins .................................. 15

Frequency Planning Using the AD9520 .................................. 77

Serial Port Setup Pins—SP1, SP0 ............................................. 15

Using the AD9520 Outputs for ADC Clock Applications .... 77

LD, STATUS, and REFMON Pins ............................................ 15

CMOS Clock Distribution ........................................................ 78

Power Dissipation ....................................................................... 16

Outline Dimensions ....................................................................... 80

Absolute Maximum Ratings .......................................................... 17

Ordering Guide .......................................................................... 80

I²C Serial Port Operation .......................................................... 51

SPI MSB/LSB First Transfers .................................................... 55

Thermal Resistance .................................................................... 17

ESD Caution ................................................................................ 17

Rev. B | Page 2 of 80

�Data Sheet

AD9520-3

REVISION HISTORY

9/2016—Rev. A to Rev. B

Changed AD9520 to AD9520-3 .................................. Throughout

Change to PD Power-Down, Maximum Sleep Parameter,

Table 18 .............................................................................................16

Updated Outline Dimensions ........................................................80

8/13—Rev. 0 to Rev. A

Changes to Features Section, Applications Section, and

General Description Section ............................................................ 1

Changes to Table 2 ............................................................................ 4

Changes to Input Frequency Parameter; Change to Input

Sensitivity, Differential Parameter Test Conditions/Comments,

Table 3 ................................................................................................. 7

Change to Output Differential Voltage, VOD Parameter Test

Conditions/Comments; Added Source Current and Sink

Current Parameters, Table 4 ............................................................ 7

Change to Output Skew, LVPECL Outputs Parameter, Test

Conditions/Comments, Table 5 ...................................................... 8

Reordered Figure 2 to Figure 4 ........................................................ 9

Change to Reset Timing, Pulse Width Low Parameter, Table 15 ...15

Change to Maximum Power, Full Operation Parameter,

Internal VCO Value in Test Conditions/Comments, Table 18 .16

Change to Junction Temperature, Table 19; Reformatted

Table 19 .............................................................................................17

Change to Table 21 ..........................................................................18

Deleted Figure 13, Renumbered Sequentially .............................22

Reordered Figure 31 and Figure 32; Moved Figure 34 and

Figure 35 to PLL External Loop Filter Section, Page 35; Added

Figure 33, Renumbered Sequentially ............................................25

Change to Mode 0—Internal VCO and Clock Distribution

Section ..............................................................................................28

Change to Configuration of the PLL Section; Changes to

Charge Pump (CP) Section ............................................................34

Changes to On-Chip VCO Section and PLL External Loop

Filter Section; Added Figure 40; Moved Figure 41 and Figure 42

from Typical Performance Characteristics Section to PLL

External Loop Filter Section; Changes to PLL Reference

Inputs Section ..................................................................................35

Changes to Reference Switchover Section ...................................36

Change to Prescaler Section and A and B Counters Section;

Changes to Table 29 ........................................................................37

Changes to Current Source Digital Lock Detect (CSDLD)

Section ..............................................................................................38

Changes to Frequency Status Monitors Section and VCO

Calibration Section ......................................................................... 41

Added Table 31, Renumbered Sequentially; Change to

Internal Zero Delay Mode Section ............................................... 42

Change to External Zero Delay Mode Section ............................ 43

Change to Clock Frequency Division Section; Added Channel

Divider Maximum Frequency Section ......................................... 45

Reformatted Table 36 to Table 39.................................................. 46

Change to Phase Offset or Coarse Time Delay Section ............. 47

Change to LVPECL Output Drivers Section; Changes to CMOS

Output Drivers Section; Change to Power-On Reset Section ... 49

Changes to Soft Reset via the Serial Port Section and Soft

Reset to Settings in EEPROM When EEPROM Pin = 0b

via the Serial Port Section .............................................................. 50

Change to Pin Descriptions Section, SPI Mode Operation

Section, and Write Section ............................................................. 54

Changes to SPI Instruction Word (16 Bits) Section ................... 55

Changes to EEPROM Operations Section, Writing to the

EEPROM Section, and Reading from the EEPROM Section ... 58

Changes to Programming the EEPROM Buffer Segment

Section and Register Section Definition Group Section;

Added Operational Codes Section Heading ............................... 59

Changes to Table 50 ........................................................................ 61

Added Unused Bits to Register Map Descriptions Section;

Changes to Address 0x000, Bit 5, and Added Address 0x003,

Table 51; Changes to Address 0x000, Bit 5, and Added

Address 0x003, Table 52 ................................................................. 64

Changes to Address 0x017, Table 54 ............................................ 66

Changes to Address 0x018, Bit 4 and Bits[2:1], Table 54 ........... 67

Change to Address 0x1A, Bit 6, Table 54 ..................................... 68

Changes to Address 0x01B, Bits[4:0], Table 54 ........................... 69

Changes to Address 0x191, Bit 5, and Address 0x194, Bit 5,

Table 56 ............................................................................................. 72

Changes to Address 0x197, Bit 5, Table 56 .................................. 73

Changes to Address 0x19A, Bit 5, Table 56 ................................. 74

Changes to Table 60 ........................................................................ 75

Changes to Address 0xB02, Bit 0, and Address 0xB03, Bit 0,

Table 61 ............................................................................................. 76

Change to Frequency Planning Using the AD9520 Section ..... 77

Added LVPECL Y-Termination and Far-End Thevenin

Termination Headings; Changes to CMOS Clock Distribution

Section .............................................................................................. 78

9/08—Revision 0: Initial Version

Rev. B | Page 3 of 80

�AD9520-3

Data Sheet

SPECIFICATIONS

Typical is given for VS = VS_DRV = 3.3 V ± 5%; VS ≤ VCP ≤ 5.25 V; TA = 25°C; RSET = 4.12 kΩ; CPRSET = 5.1 kΩ, unless otherwise noted. Minimum

and maximum values are given over full VS and TA (−40°C to +85°C) variation.

POWER SUPPLY REQUIREMENTS

Table 1.

Parameter

POWER PINS

VS

VS_DRV

VCP

CURRENT SET RESISTORS

RSET Pin Resistor

CPRSET Pin Resistor

Min

Typ

Max

Unit

Test Conditions/Comments

3.135

2.375

VS

3.3

3.465

VS

5.25

V

V

V

3.3 V ± 5%

Nominally 2.5 V to 3.3 V ± 5%

Nominally 3.3 V to 5.0 V ± 5%

4.12

5.1

kΩ

kΩ

220

nF

Sets internal biasing currents; connect to ground

Sets internal CP current range, nominally 4.8 mA (CP_lsb = 600 µA); actual

current can be calculated by CP_lsb = 3.06/CPRSET; connect to ground

Bypass for internal LDO regulator; necessary for LDO stability; connect to ground

BYPASS PIN CAPACITOR

PLL CHARACTERISTICS

Table 2.

Parameter

VCO (ON CHIP)

Frequency Range

VCO Gain (KVCO)

Tuning Voltage (VT)

Frequency Pushing (Open-Loop)

Phase Noise at 1 kHz Offset

Phase Noise at 100 kHz Offset

Phase Noise at 1 MHz Offset

REFERENCE INPUTS

Differential Mode (REFIN, REFIN)

Input Frequency

Min

Typ

1720

Max

Unit

2250

MHz

MHz/V

V

MHz/V

dBc/Hz

dBc/Hz

dBc/Hz

47

0.5

VCP − 0.5

1

−55

−110

−129

0

Input Sensitivity

250

280

Self-Bias Voltage, REFIN

Self-Bias Voltage, REFIN

Input Resistance, REFIN

Input Resistance, REFIN

Dual Single-Ended Mode (REF1, REF2)

Input Frequency (AC-Coupled) with DC

Offset Off)

Input Frequency (AC-Coupled with

DC Offset On)

1.35

1.30

4.0

4.4

Input Frequency (DC-Coupled)

Input Sensitivity (AC-Coupled with

DC Offset Off)

Input Sensitivity (AC-Coupled with

DC Offset On)

Input Logic High, DC Offset Off

Input Logic Low, DC Offset Off

Input Current

Input Capacitance

Pulse Width High/Low

1.60

1.50

4.8

5.3

MHz

mV p-p

Test Conditions/Comments

See Figure 8

VT ≤ VS when using internal VCO

f = 2000 MHz

f = 2000 MHz

f = 2000 MHz

Differential mode (can accommodate single-ended

input by ac grounding undriven input)

Frequencies below about 1 MHz should be dc-coupled;

be careful to match VCM (self-bias voltage)

PLL figure of merit (FOM) increases with increasing slew

rate (see Figure 12); the input sensitivity is sufficient for

ac-coupled LVDS and LVPECL signals

Self-bias voltage of REFIN 1

Self-bias voltage of REFIN1

Self-biased1

Self-biased1

Two single-ended CMOS-compatible inputs

Slew rate must be >50 V/µs

1.75

1.60

5.9

6.4

V

V

kΩ

kΩ

250

MHz

250

MHz

0

0.55

250

3.28

MHz

V p-p

Slew rate must be >50 V/µs, and input amplitude

sensitivity specification must be met; see the input

sensitivity parameter

Slew rate > 50 V/µs; CMOS levels

VIH should not exceed VS

1.5

2.78

V p-p

VIH should not exceed VS

10

2.0

0.8

+100

−100

2

1.8

V

V

µA

pF

ns

Rev. B | Page 4 of 80

Each pin, REFIN (REF1)/REFIN (REF2)

The amount of time that a square wave is high/low;

determines the allowable input duty cycle

�Data Sheet

Parameter

Crystal Oscillator

Crystal Resonator Frequency Range

Maximum Crystal Motional Resistance

PHASE/FREQUENCY DETECTOR (PFD)

PFD Input Frequency

AD9520-3

Max

Unit

33.33

30

MHz

Ω

100

45

50

1.3

2.9

6.0

MHz

MHz

MHz

ns

ns

ns

ICP Sink/Source

High Value

4.8

mA

Low Value

0.60

mA

Reference Input Clock Doubler Frequency

Antibacklash Pulse Width

Min

Typ

16.62

0.004

CHARGE PUMP (CP)

Absolute Accuracy

CPRSET Range

ICP High Impedance Mode Leakage

Sink-and-Source Current Matching

ICP vs. VCP

ICP vs. Temperature

PRESCALER (PART OF N DIVIDER)

Prescaler Input Frequency

P = 1 FD

P = 2 FD

P = 3 FD

P = 2 DM (2/3)

P = 4 DM (4/5)

P = 8 DM (8/9)

P = 16 DM (16/17)

P = 32 DM (32/33)

Prescaler Output Frequency

PLL N DIVIDER DELAY

000

001

010

011

100

101

110

111

PLL R DIVIDER DELAY

000

001

010

011

100

101

110

111

2.5

1

1

%

kΩ

nA

%

1.5

2

%

%

2.7

10

300

600

900

200

1000

2400

3000

3000

300

Off

385

486

623

730

852

976

1101

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

Test Conditions/Comments

Antibacklash pulse width = 1.3 ns

Antibacklash pulse width = 2.9 ns

Register 0x017[1:0] = 01b

Register 0x017[1:0] = 00b; Register 0x017[1:0] = 11b

Register 0x017[1:0] = 10b

CPV is the CP pin voltage; VCP is the charge pump power

supply voltage (VCP pin)

Programmable

With CPRSET = 5.1 kΩ; higher ICP is possible by changing

CPRSET

With CPRSET = 5.1 kΩ; lower ICP is possible by changing

CPRSET

CPV = VCP/2

0.5 V < CPV < VCP − 0.5 V; CPV is the CP pin voltage;

VCP is the charge pump power supply voltage (VCP pin)

0.5 V < CPV < VCP − 0.5 V

CPV = VCP/2

A, B counter input frequency (prescaler input

frequency divided by P)

Register 0x019[2:0]; see Table 54

ps

ps

ps

ps

ps

ps

ps

Register 0x019[5:3]; see Table 54

Off

365

486

608

730

852

976

1101

ps

ps

ps

ps

ps

ps

ps

Rev. B | Page 5 of 80

�AD9520-3

Parameter

PHASE OFFSET IN ZERO DELAY

Phase Offset (REF-to-LVPECL Clock Output

Pins) in Internal Zero Delay Mode

Phase Offset (REF-to-LVPECL Clock Output

Pins) in Internal Zero Delay Mode

Phase Offset (REF-to-CLK Input Pins) in

External Zero Delay Mode

Phase Offset (REF-to-CLK Input Pins) in

External Zero Delay Mode

NOISE CHARACTERISTICS

In-Band Phase Noise of the Charge Pump/

Phase Frequency Detector 2

500 kHz PFD Frequency

1 MHz PFD Frequency

10 MHz PFD Frequency

50 MHz PFD Frequency

PLL Figure of Merit (FOM)

Data Sheet

Min

Typ

Max

Unit

560

1060

1310

ps

Test Conditions/Comments

REF refers to REFIN (REF1)/REFIN (REF2)

When N delay and R delay are bypassed

−320

+50

+240

ps

When N delay setting = 110b, and R delay is bypassed

140

630

870

ps

When N delay and R delay are bypassed

−460

−20

+200

ps

When N delay setting = 011b, and R delay is bypassed

The PLL in-band phase noise floor is estimated by

measuring the in-band phase noise at the output of the

VCO and subtracting 20 log(N) (where N is the value of

the N divider).

−165

−162

−152

−144

−222

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

Low Range (ABP 1.3 ns, 2.9 ns)

3.5

ns

High Range (ABP 1.3 ns, 2.9 ns)

7.5

ns

3.5

ns

Low Range (ABP 1.3 ns, 2.9 ns)

7

ns

High Range (ABP 1.3 ns, 2.9 ns)

15

ns

High Range (ABP 6.0 ns)

11

ns

PLL DIGITAL LOCK DETECT WINDOW 3

Lock Threshold (Coincidence of Edges)

High Range (ABP 6.0 ns)

Unlock Threshold (Hysteresis)3

Reference slew rate > 0.5 V/ns; FOM + 10 log(fPFD) is an

approximation of the PFD/CP in-band phase noise (in the

flat region) inside the PLL loop bandwidth; when

running closed-loop, the phase noise, as observed at the

VCO output, is increased by 20 log(N); PLL figure of merit

decreases with decreasing slew rate; see Figure 12

Signal available at the LD, STATUS, and REFMON pins

when selected by appropriate register settings; the lock

detect threshold varies linearly with the value of the

CPRSET resistor

Selected by Register 0x017[1:0] and Register 0x018[4]

(this is the threshold to go from unlock to lock)

Register 0x017[1:0] = 00b, 01b,11b;

Register 0x018[4] = 1b

Register 0x017[1:0] = 00b, 01b, 11b;

Register 0x018[4] = 0b

Register 0x017[1:0] = 10b; Register 0x018[4] = 0b

Selected by Register 0x017[1:0] and Register 0x018[4] (this

is the threshold to go from lock to unlock)

Register 0x017[1:0] = 00b, 01b, 11b;

Register 0x018[4] = 1b

Register 0x017[1:0] = 00b, 01b, 11b;

Register 0x018[4] = 0b

Register 0x017[1:0] = 10b; Register 0x018[4] = 0b

The REFIN and REFIN self-bias points are offset slightly to avoid chatter on an open input condition.

In-band means within the LBW of the PLL.

3

For reliable operation of the digital lock detect, the period of the PFD frequency must be greater than the unlock-after-lock time.

1

2

Rev. B | Page 6 of 80

�Data Sheet

AD9520-3

CLOCK INPUTS

Table 3.

Parameter

CLOCK INPUTS (CLK, CLK)

Input Frequency

Min

Max

Unit

01

01

2.4

2.0

GHz

GHz

01

1.6

GHz

Input Sensitivity, Differential

Typ

150

mV p-p

Input Level, Differential

Input Common-Mode Voltage, VCM

Input Common-Mode Range, VCMR

Input Sensitivity, Single-Ended

Input Resistance

Input Capacitance

1

1.3

1.3

3.9

1.57

150

4.7

2

2

V p-p

1.8

1.8

V

V

mV p-p

kΩ

pF

5.7

Test Conditions/Comments

Differential input

High frequency distribution (VCO divider)

Distribution only (VCO divider bypassed); this is the

frequency range supported by the channel divider for

all divide ratios except divide-by-17 and divide-by-3

Distribution only (VCO divider bypassed); this is the

frequency range supported by all channel divider ratios

Measured at 2.4 GHz; jitter performance is improved

with slew rates > 1 V/ns; the input sensitivity is

sufficient for ac-coupled LVDS and LVPECL signals

Larger voltage swings can turn on the protection

diodes and can degrade jitter performance

Self-biased; enables ac coupling

With 200 mV p-p signal applied; dc-coupled

CLK ac-coupled; CLK ac-bypassed to RF ground

Self-biased

Below about 1 MHz, the input should be dc-coupled. Care should be taken to match VCM.

CLOCK OUTPUTS

Table 4.

Parameter

LVPECL CLOCK OUTPUTS

OUT0, OUT1, OUT2, OUT3, OUT4,

OUT5, OUT6, OUT7, OUT8,

OUT9, OUT10, OUT11

Output Frequency, Maximum

Output High Voltage, VOH

Output Low Voltage, VOL

Output Differential Voltage, VOD

CMOS CLOCK OUTPUTS

OUT0A, OUT0B, OUT1A, OUT1B,

OUT2A, OUT2B, OUT3A, OUT3B,

OUT4A, OUT4B, OUT5A, OUT5B,

OUT6A, OUT6B, OUT7A, OUT7B,

OUT8A, OUT8B, OUT9A, OUT9B,

OUT10A, OUT10B, OUT11A,

OUT11B

Output Frequency

Output Voltage High, VOH

Output Voltage Low, VOL

Output Voltage High, VOH

Output Voltage Low, VOL

Output Voltage High, VOH

Output Voltage Low, VOL

Min

Typ

Max

2400

VS_DRV − 1.07

VS_DRV − 1.95

660

VS_DRV − 0.96

VS_DRV − 1.79

820

VS_DRV − 0.84

VS_DRV − 1.64

950

Unit

Test Conditions/Comments

Termination = 50 Ω to VS_DRV − 2 V

Differential (OUT, OUT)

MHz

Using direct to output (see Figure 20); higher

frequencies are possible, but the resulting amplitude

does not meet the VOD specification; the maximum

output frequency is limited by either the maximum VCO

frequency or the frequency at the CLK inputs,

depending on the AD9520-3 configuration

V

V

mV

VOH − VOL for each leg of a differential pair for default

amplitude setting with the driver not toggling; the

peak-to-peak amplitude measured using a differential

probe across the differential pair with the driver

toggling is roughly 2× these values (see Figure 20 for

variation over frequency)

Single-ended; termination = 10 pF

250

VS − 0.1

0.1

2.7

0.5

1.8

0.6

Rev. B | Page 7 of 80

MHz

V

V

V

V

V

V

See Figure 21

1 mA load, VS_DRV = 3.3 V/2.5 V

1 mA load, VS_DRV = 3.3 V/2.5 V

10 mA load VS_DRV = 3.3 V

10 mA load, VS_DRV = 3.3 V

10 mA load, VS_DRV = 2.5 V

10 mA load, VS_DRV = 2.5 V

�AD9520-3

Parameter

Source Current

Static

Dynamic

Sink Current

Static

Dynamic

Data Sheet

Min

Typ

Max

Unit

Test Conditions/Comments

Damage to the part can result if values are exceeded

20

16

mA

mA

8

16

mA

mA

Typ

Max

Unit

130

170

ps

130

170

ps

1050

970

1.0

1280

1180

ps

ps

ps/°C

5

16

ps

Termination = 50 Ω to VS_DRV – 2 V

VS_DRV = 3.3 V

5

5

20

45

ps

ps

VS_DRV = 2.5 V

VS_DRV = 3.3 V

5

60

190

ps

ps

VS_DRV = 2.5 V

VS_DRV = 3.3 V and 2.5 V

750

715

965

890

960

890

1280

1100

ps

ps

ps

ps

Termination = open

20% to 80%; CLOAD = 10 pF; VS_DRV = 3.3 V

80% to 20%; CLOAD = 10 pF; VS_DRV = 3.3 V

20% to 80%; CLOAD = 10 pF; VS_DRV = 2.5 V

80% to 20%; CLOAD = 10 pF; VS_DRV = 2.5 V

Clock distribution configuration

2.75

3.35

2

3.55

ns

ns

ps/°C

VS_DRV = 3.3 V

VS_DRV = 2.5 V

VS_DRV = 3.3 V and 2.5 V

7

85

ps

VS_DRV = 3.3 V

10

10

105

240

ps

ps

VS_DRV = 2.5 V

VS_DRV = 3.3 V

10

285

600

ps

ps

VS_DRV = 2.5 V

VS_DRV = 3.3 V

620

ps

VS_DRV = 2.5 V

All settings identical; different logic type

2.48

2.50

ns

ns

LVPECL to CMOS on same part

LVPECL to CMOS on same part

Damage to the part can result if values are exceeded

TIMING CHARACTERISTICS

Table 5.

Parameter

LVPECL OUTPUT RISE/FALL TIMES

Output Rise Time, tRP

Min

Output Fall Time, tFP

PROPAGATION DELAY, tPECL,

CLK-TO-LVPECL OUTPUT

For All Divide Values

850

800

Variation with Temperature

OUTPUT SKEW, LVPECL OUTPUTS 1

LVPECL Outputs Sharing the Same

Divider

LVPECL Outputs on Different

Dividers

All LVPECL Outputs Across

Multiple Parts

CMOS OUTPUT RISE/FALL TIMES

Output Rise Time, tRC

Output Fall Time, tFC

Output Rise Time, tRC

Output Fall Time, tFC

PROPAGATION DELAY, tCMOS, CLK-TOCMOS OUTPUT

For All Divide Values

2.1

Variation with Temperature

OUTPUT SKEW, CMOS OUTPUTS1

CMOS Outputs Sharing the Same

Divider

All CMOS Outputs on Different

Dividers

All CMOS Outputs Across Multiple

Parts

OUTPUT SKEW, LVPECL-TO-CMOS

OUTPUTS1

Outputs Sharing the Same Divider

Outputs on Different Dividers

1

1.18

1.20

1.76

1.78

Test Conditions/Comments

Termination = 50 Ω to VS_DRV − 2 V

20% to 80%, measured differentially (rise/fall times

are independent of VS and are valid for VS_DRV = 3.3 V

and 2.5 V)

80% to 20%, measured differentially (rise/fall times

are independent of VS and are valid for VS_DRV = 3.3 V

and 2.5 V)

High frequency clock distribution configuration

Clock distribution configuration

The output skew is the difference between any two similar delay paths while operating at the same voltage and temperature.

Rev. B | Page 8 of 80

�Data Sheet

AD9520-3

Timing Diagrams

DIFFERENTIAL

SINGLE-ENDED

80%

80%

LVPECL

CMOS

10pF LOAD

20%

tFP

tRC

Figure 2. LVPECL Timing, Differential

Figure 4. CMOS Timing, Single-Ended, 10 pF Load

tCLK

CLK

07216-060

tPECL

tCMOS

tFC

Figure 3. CLK/CLK to Clock Output Timing, DIV = 1

Rev. B | Page 9 of 80

07216-063

tRP

07216-061

20%

�AD9520-3

Data Sheet

CLOCK OUTPUT ADDITIVE PHASE NOISE (DISTRIBUTION ONLY; VCO DIVIDER NOT USED)

Table 6.

Parameter

CLK-TO-LVPECL ADDITIVE PHASE NOISE

CLK = 1 GHz, Output = 1 GHz

Divider = 1

10 Hz Offset

100 Hz Offset

1 kHz Offset

10 kHz Offset

100 kHz Offset

1 MHz Offset

10 MHz Offset

100 MHz Offset

CLK = 1 GHz, Output = 200 MHz

Divider = 5

10 Hz Offset

100 Hz Offset

1 kHz Offset

10 kHz Offset

100 kHz Offset

1 MHz Offset

>10 MHz Offset

CLK-TO-CMOS ADDITIVE PHASE NOISE

CLK = 1 GHz, Output = 250 MHz

Divider = 4

10 Hz Offset

100 Hz Offset

1 kHz Offset

10 kHz Offset

100 kHz Offset

1 MHz Offset

>10 MHz Offset

CLK = 1 GHz, Output = 50 MHz

Divider = 20

10 Hz Offset

100 Hz Offset

1 kHz Offset

10 kHz Offset

100 kHz Offset

1 MHz Offset

>10 MHz Offset

Min

Typ

−107

−117

−127

−135

−142

−145

−147

−150

Max

Unit

Test Conditions/Comments

Distribution section only; does not include PLL and VCO

Input slew rate > 1 V/ns

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

Input slew rate > 1 V/ns

−122

−132

−143

−150

−156

−157

−157

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

Distribution section only; does not include PLL and VCO

Input slew rate > 1 V/ns

−107

−119

−125

−134

−144

−148

−154

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

Input slew rate > 1 V/ns

−126

−133

−140

−148

−157

−160

−163

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

Rev. B | Page 10 of 80

�Data Sheet

AD9520-3

CLOCK OUTPUT ABSOLUTE PHASE NOISE (INTERNAL VCO USED)

Table 7.

Parameter

LVPECL ABSOLUTE PHASE NOISE

Min

VCO = 2.25 GHz; Output = 2.25 GHz

1 kHz Offset

10 kHz Offset

100 kHz Offset

1 MHz Offset

10 MHz Offset

40 MHz Offset

VCO = 2 GHz; Output = 2 GHz

1 kHz Offset

10 kHz Offset

100 kHz Offset

1 MHz Offset

10 MHz Offset

40 MHz Offset

VCO = 1.75 GHz; Output = 1.75 GHz

1 kHz Offset

10 kHz Offset

100 kHz Offset

1 MHz Offset

10 MHz Offset

40 MHz Offset

Typ

Max

Unit

−50

−82

−107

−126

−140

−146

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

−55

−85

−110

−129

−142

−147

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

−59

−89

−114

−132

−143

−147

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

Test Conditions/Comments

Internal VCO; direct-to-LVPECL output and

for loop bandwidths < 1 kHz

CLOCK OUTPUT ABSOLUTE TIME JITTER (CLOCK GENERATION USING INTERNAL VCO)

Table 8.

Parameter

LVPECL OUTPUT ABSOLUTE TIME JITTER

Min

VCO = 1.966 GHz; LVPECL = 245.76 MHz; PLL LBW = 55 kHz

Typ

Max

135

308

129

293

163

323

VCO = 1.966 GHz; LVPECL = 122.88 MHz; PLL LBW = 55 kHz

VCO = 1.966 GHz; LVPECL = 61.44 MHz; PLL LBW = 55 kHz

Unit

fs rms

fs rms

fs rms

fs rms

fs rms

fs rms

Test Conditions/Comments

Application example based on a typical

setup where the reference source is

clean, so a wider PLL loop bandwidth is

used; reference = 15.36 MHz; R divider = 1

Integration BW = 200 kHz to 10 MHz

Integration BW = 12 kHz to 20 MHz

Integration BW = 200 kHz to 10 MHz

Integration BW = 12 kHz to 20 MHz

Integration BW = 200 kHz to 10 MHz

Integration BW = 12 kHz to 20 MHz

CLOCK OUTPUT ABSOLUTE TIME JITTER (CLOCK CLEANUP USING INTERNAL VCO)

Table 9.

Parameter

LVPECL OUTPUT ABSOLUTE TIME JITTER

Min

VCO = 1.866 GHz; LVPECL = 155.52 MHz; PLL LBW = 1.9 kHz

VCO = 1.966 GHz; LVPECL = 122.88 MHz; PLL LBW = 2.2 kHz

Typ

377

386

Rev. B | Page 11 of 80

Max

Unit

fs rms

fs rms

Test Conditions/Comments

Application example based on a typical

setup where the reference source is jittery,

so a narrower PLL loop bandwidth is used;

reference = 19.44 MHz; R divider = 162

Integration BW = 12 kHz to 20 MHz

Integration BW = 12 kHz to 20 MHz

�AD9520-3

Data Sheet

CLOCK OUTPUT ABSOLUTE TIME JITTER (CLOCK GENERATION USING EXTERNAL VCXO)

Table 10.

Parameter

LVPECL OUTPUT ABSOLUTE TIME JITTER

Min

LVPECL = 245.76 MHz; PLL LBW = 125 Hz

Typ

Max

54

77

109

79

114

163

124

176

259

LVPECL = 122.88 MHz; PLL LBW = 125 Hz

LVPECL = 61.44 MHz; PLL LBW = 125 Hz

Unit

fs rms

fs rms

fs rms

fs rms

fs rms

fs rms

fs rms

fs rms

fs rms

Test Conditions/Comments

Application example based on a typical setup

using an external 245.76 MHz VCXO (Toyocom

TCO-2112); reference = 15.36 MHz; R divider = 1

Integration BW = 200 kHz to 5 MHz

Integration BW = 200 kHz to 10 MHz

Integration BW = 12 kHz to 20 MHz

Integration BW = 200 kHz to 5 MHz

Integration BW = 200 kHz to 10 MHz

Integration BW = 12 kHz to 20 MHz

Integration BW = 200 kHz to 5 MHz

Integration BW = 200 kHz to 10 MHz

Integration BW = 12 kHz to 20 MHz

CLOCK OUTPUT ADDITIVE TIME JITTER (VCO DIVIDER NOT USED)

Table 11.

Parameter

LVPECL OUTPUT ADDITIVE TIME JITTER

Min

CLK = 622.08 MHz

Any LVPECL Output = 622.08 MHz

Divide Ratio = 1

CLK = 622.08 MHz

Any LVPECL Output = 155.52 MHz

Divide Ratio = 4

CLK = 1000 MHz

Any LVPECL Output = 100 MHz

Divide Ratio = 10

CLK = 500 MHz

Any LVPECL Output = 100 MHz

Divide Ratio = 5

CMOS OUTPUT ADDITIVE TIME JITTER

CLK = 200 MHz

Any CMOS Output Pair = 100 MHz

Divide Ratio = 2

Typ

Max

46

fs rms

Test Conditions/Comments

Distribution section only; does not include PLL

and VCO; measured at rising edge of clock

signal

Integration bandwidth = 12 kHz to 20 MHz

64

fs rms

Integration bandwidth = 12 kHz to 20 MHz

223

fs rms

Calculated from SNR of ADC method

Broadband jitter

209

fs rms

Calculated from SNR of ADC method

Broadband jitter

325

Unit

fs rms

Distribution section only; does not include PLL

and VCO

Calculated from SNR of ADC method

Broadband jitter

CLOCK OUTPUT ADDITIVE TIME JITTER (VCO DIVIDER USED)

Table 12.

Parameter

LVPECL OUTPUT ADDITIVE TIME JITTER

Min

Typ

Max

Unit

CLK = 1.0 GHz; VCO DIV = 5; LVPECL = 100 MHz;

Channel Divider = 2; Duty-Cycle Correction = Off

CLK = 500 MHz; VCO DIV = 5; LVPECL = 100 MHz;

Bypass Channel Divider; Duty-Cycle Correction = On

CMOS OUTPUT ADDITIVE TIME JITTER

230

fs rms

215

fs rms

CLK = 200 MHz; VCO DIV = 2; CMOS = 100 MHz;

Bypass Channel Divider; Duty-Cycle Correction = Off

CLK = 1600 MHz; VCO DIV = 2; CMOS = 100 MHz;

Channel Divider = 8; Duty-Cycle Correction = Off

326

fs rms

362

fs rms

Rev. B | Page 12 of 80

Test Conditions/Comments

Distribution section only; does not include PLL

and VCO; uses rising edge of clock signal

Calculated from SNR of ADC method

(broadband jitter)

Calculated from SNR of ADC method

(broadband jitter)

Distribution section only; does not include PLL

and VCO; uses rising edge of clock signal

Calculated from SNR of ADC method

(broadband jitter)

Calculated from SNR of ADC method

(broadband jitter)

�Data Sheet

AD9520-3

SERIAL CONTROL PORT—SPI MODE

Table 13.

Parameter

CS (INPUT)

Input Logic 1 Voltage

Input Logic 0 Voltage

Input Logic 1 Current

Input Logic 0 Current

Min

Max

Unit

0.8

3

−110

V

V

µA

µA

2

pF

2.0

Input Capacitance

SCLK (INPUT IN SPI MODE)

Input Logic 1 Voltage

Input Logic 0 Voltage

Input Logic 1 Current

Input Logic 0 Current

Input Capacitance

SDIO (INPUT IN BIDIRECTIONAL MODE)

Input Logic 1 Voltage

Input Logic 0 Voltage

Input Logic 1 Current

Input Logic 0 Current

Input Capacitance

SDIO, SDO (OUTPUTS)

Output Logic 1 Voltage

Output Logic 0 Voltage

TIMING

Clock Rate (SCLK, 1/tSCLK)

Pulse Width High, tHIGH

Pulse Width Low, tLOW

SDIO to SCLK Setup, tDS

SCLK to SDIO Hold, tDH

SCLK to Valid SDIO and SDO, tDV

CS to SCLK Setup and Hold, tS, tC

CS Minimum Pulse Width High, tPWH

Typ

Test Conditions/Comments

CS has an internal 30 kΩ pull-up resistor

The minus sign indicates that current is flowing

out of the AD9520-3, which is due to the internal

pull-up resistor

SCLK has an internal 30 kΩ pull-down resistor in

SPI mode but not in I2C mode

2.0

0.8

110

1

2

2.0

0.8

1

1

2

2.7

0.4

25

16

16

4

0

11

2

3

Rev. B | Page 13 of 80

V

V

µA

µA

pF

V

V

µA

µA

pF

V

V

MHz

ns

ns

ns

ns

ns

ns

ns

�AD9520-3

Data Sheet

SERIAL CONTROL PORT—I²C MODE

Table 14.

Parameter

SDA, SCL (WHEN INPUTTING DATA)

Input Logic 1 Voltage

Input Logic 0 Voltage

Input Current with an Input Voltage Between

0.1 × VS and 0.9 × VS

Hysteresis of Schmitt Trigger Inputs

Pulse Width of Spikes That Must Be Suppressed by

the Input Filter, tSPIKE

SDA (WHEN OUTPUTTING DATA)

Output Logic 0 Voltage at 3 mA Sink Current

Output Fall Time from VIHMIN to VILMAX with a Bus

Capacitance from 10 pF to 400 pF

TIMING

Min

Typ

Unit

0.3 × VS

+10

V

V

µA

50

V

ns

0.4

250

V

ns

0.7 × VS

−10

0.015 × VS

20 + 0.1 Cb

Test Conditions/Comments

Cb = capacitance of one bus line in pF

Note that all I2C timing values are

referred to VIHMIN (0.3 × VS) and VILMAX

levels (0.7 × VS)

Clock Rate (SCL, fI2C)

Bus Free Time Between a Stop and Start Condition, tIDLE

Setup Time for a Repeated Start Condition, tSET; STR

Hold Time (Repeated) Start Condition, tHLD; STR

1.3

0.6

0.6

400

kHz

µs

µs

µs

Setup Time for Stop Condition, tSET; STP

Low Period of the SCL Clock, tLOW

High Period of the SCL Clock, tHIGH

SCL, SDA Rise Time, tRISE

SCL, SDA Fall Time, tFALL

Data Setup Time, tSET; DAT

0.6

1.3

0.6

20 + 0.1 Cb

20 + 0.1 Cb

120

µs

µs

µs

ns

ns

ns

Data Hold Time, tHLD; DAT

140

Capacitive Load for Each Bus Line, Cb

1

Max

300

300

880

ns

400

pF

After this period, the first clock pulse

is generated

This is a minor deviation from the

original I²C specification of 100 ns

minimum

This is a minor deviation from the

original I²C specification of 0 ns

minimum 1

According to the original I2C specification, an I2C master must also provide a minimum hold time of 300 ns for the SDA signal to bridge the undefined region of the SCL

falling edge.

Rev. B | Page 14 of 80

�Data Sheet

AD9520-3

PD, EEPROM, RESET, AND SYNC PINS

Table 15.

Parameter

INPUT CHARACTERISTICS

Logic 1 Voltage

Logic 0 Voltage

Logic 1 Current

Logic 0 Current

Capacitance

RESET TIMING

Pulse Width Low

RESET Inactive to Start of Register

Programming

SYNC TIMING

Pulse Width Low

Min

Typ

Max

Unit

0.8

1

−110

V

V

µA

µA

2

pF

2.0

Test Conditions/Comments

Each pin has a 30 kΩ internal pull-up resistor

The minus sign indicates that current is flowing out of

the AD9520-3, which is due to the internal pull-up resistor

500

100

ns

ns

1.3

ns

High speed clock is CLK input signal

Max

Unit

0.25 × VS

0.65 × VS

V

V

Test Conditions/Comments

These pins do not have internal pull-up/pull-down

resistors

VS is the voltage on the VS pin

These pins can be floated to obtain Logic Level ½; if

floating the pin, connect a capacitor to ground

SERIAL PORT SETUP PINS—SP1, SP0

Table 16.

Parameter

SP1, SP0

Min

Logic Level 0

Logic Level ½

0.4 × VS

Logic Level 1

0.8 × VS

Typ

V

LD, STATUS, AND REFMON PINS

Table 17.

Parameter

OUTPUT CHARACTERISTICS

Min

Output Voltage High, VOH

Output Voltage Low, VOL

MAXIMUM TOGGLE RATE

2.7

Max

Unit

0.4

100

V

V

MHz

3

pF

On-chip capacitance; used to calculate RC time constant

for analog lock detect readback; use a pull-up resistor

1.02

MHz

8

kHz

Frequency above which the monitor indicates the

presence of the reference

Frequency above which the monitor indicates the

presence of the reference

ANALOG LOCK DETECT

Capacitance

REF1, REF2, AND VCO FREQUENCY

STATUS MONITOR

Normal Range

Extended Range

LD PIN COMPARATOR

Trip Point

Hysteresis

Typ

1.6

260

V

mV

Rev. B | Page 15 of 80

Test Conditions/Comments

When selected as a digital output (CMOS); there are

other modes in which these pins are not CMOS digital

outputs; see Table 54, Register 0x017, Register 0x01A,

and Register 0x01B

Applies when mux is set to any divider or counter output

or PFD up/down pulse; also applies in analog lock detect

mode; usually debug mode only; beware that spurs can

couple to output when any pin is toggling

�AD9520-3

Data Sheet

POWER DISSIPATION

Table 18.

Parameter

POWER DISSIPATION, CHIP

Typ

Max

Unit

Power-On Default

PLL Locked; One LVPECL Output Enabled

1.32

0.55

1.5

0.64

W

W

PLL Locked; One CMOS Output Enabled

0.52

0.62

W

Distribution Only Mode; VCO Divider On;

One LVPECL Output Enabled

Distribution Only Mode; VCO Divider Off;

One LVPECL Output Enabled

Maximum Power, Full Operation

0.39

0.46

W

0.36

0.42

W

1.5

1.7

W

PD Power-Down

60

80

mW

PD Power-Down, Maximum Sleep

24

43

mW

4

4.8

mW

32

25

40

30

mW

mW

REF1, REF2 (Single-Ended) On/Off

15

20

mW

VCO On/Off

PLL Dividers and Phase Detector On/Off

LVPECL Channel

67

51

121

104

63

144

mW

mW

mW

LVPECL Driver

CMOS Channel

51

145

73

180

mW

mW

CMOS Driver On/Off

Channel Divider Enabled

11

40

24

57

mW

mW

Zero Delay Block On/Off

30

34

mW

VCP Supply

POWER DELTAS, INDIVIDUAL FUNCTIONS

VCO Divider On/Off

REFIN (Differential) Off

Min

Test Conditions/Comments

Does not include power dissipated in external resistors; all

LVPECL outputs terminated with 50 Ω to VCC − 2 V; all CMOS

outputs have 10 pF capacitive loading; VS_DRV = 3.3 V

No clock; no programming; default register values

fREF = 25 MHz; fOUT = 250 MHz; VCO = 2 GHz; VCO divider = 2;

one LVPECL output and output divider enabled; zero delay off;

ICP = 4.8 mA

fREF = 25 MHz; fOUT = 62.5 MHz; VCO = 2 GHz; VCO divider = 2;

one CMOS output and output divider enabled; zero delay off;

ICP = 4.8 mA

fCLK = 2.4 GHz; fOUT = 200 MHz; VCO divider = 2; one LVPECL

output and output divider enabled; zero delay off

fCLK = 2 GHz; fOUT = 200 MHz; VCO divider bypassed; one

LVPECL output and output divider enabled; zero delay off

PLL on; internal VCO = 2000 MHz; VCO divider = 2; all channel

dividers on; 12 LVPECL outputs at 125 MHz; zero delay on

PD pin pulled low; does not include power dissipated in

termination resistors

PD pin pulled low; PLL power-down, Register 0x010[1:0] = 01b;

power-down SYNC, Register 0x230[2] = 1b; power-down

distribution reference, Register 0x230[1] = 1b

PLL operating; typical closed-loop configuration

Power delta when a function is enabled/disabled

VCO divider not used

Delta between reference input off and differential reference

input mode

Delta between reference inputs off and one singled-ended

reference enabled; double this number if both REF1 and REF2

are powered up

Internal VCO disabled; CLK input selected

PLL off to PLL on, normal operation; no reference enabled

No LVPECL output on to one LVPECL output on; channel divider

is set to 1

Second LVPECL output turned on, same channel

No CMOS output on to one CMOS output on; channel divider

is set to 1; fOUT = 62.5 MHz and 10 pF of capacitive loading

Additional CMOS outputs within the same channel turned on

Delta between divider bypassed (divide-by-1) and divide-by-2

to divide-by-32

Rev. B | Page 16 of 80

�Data Sheet

AD9520-3

ABSOLUTE MAXIMUM RATINGS

Table 19.

Parameter

VS to GND

VCP, CP to GND

VS_DRV to GND

REFIN, REFIN to GND

RSET, LF, BYPASS to GND

CPRSET to GND

CLK, CLK to GND

CLK to CLK

SCLK/SCL, SDIO/SDA, SDO, CS to GND

OUT0, OUT0, OUT1, OUT1,

OUT2, OUT2, OUT3, OUT3,

OUT4, OUT4, OUT5, OUT5,

OUT6, OUT6, OUT7, OUT7,

OUT8, OUT8, OUT9, OUT9,

OUT10, OUT10, OUT11, OUT11 to GND

SYNC, RESET, PD to GND

REFMON, STATUS, LD to GND

SP0, SP1, EEPROM to GND

Junction Temperature 1

Storage Temperature Range

Lead Temperature (10 sec)

1

Rating

−0.3 V to +3.6 V

−0.3 V to +5.8 V

−0.3 V to +3.6 V

−0.3 V to VS + 0.3 V

−0.3 V to VS + 0.3 V

−0.3 V to VS + 0.3 V

−0.3 V to VS + 0.3 V

−1.2 V to +1.2 V

−0.3 V to VS + 0.3 V

−0.3 V to VS + 0.3 V

Stresses at or above those listed under Absolute Maximum

Ratings may cause permanent damage to the product. This is a

stress rating only; functional operation of the product at these

or any other conditions above those indicated in the operational

section of this specification is not implied. Operation beyond

the maximum operating conditions for extended periods may

affect product reliability.

THERMAL RESISTANCE

Thermal impedance measurements were taken on a JEDEC

JESD51-5 2S2P test board in still air in accordance with JEDEC

JESD51-2. See the Thermal Performance section for more

details.

Table 20.

Package Type

64-Lead LFCSP (CP-64-4)

−0.3 V to VS + 0.3 V

−0.3 V to VS + 0.3 V

−0.3 V to VS + 0.3 V

125°C

−65°C to +150°C

300°C

ESD CAUTION

See Table 20 for θJA.

Rev. B | Page 17 of 80

θJA

22

Unit

°C/W

�AD9520-3

Data Sheet

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

REFIN (REF1)

REFIN (REF2)

CPRSET

VS

VS

GND

RSET

VS

OUT0 (OUT0A)

OUT0 (OUT0B)

VS_DRV

OUT1 (OUT1A)

OUT1 (OUT1B)

OUT2 (OUT2A)

OUT2 (OUT2B)

VS

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

PIN 1

INDICATOR

AD9520

TOP VIEW

(Not to Scale)

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

OUT3 (OUT3A)

OUT3 (OUT3B)

VS_DRV

OUT4 (OUT4A)

OUT4 (OUT4B)

OUT5 (OUT5A)

OUT5 (OUT5B)

VS

VS

OUT8 (OUT8B)

OUT8 (OUT8A)

OUT7 (OUT7B)

OUT7 (OUT7A)

VS_DRV

OUT6 (OUT6B)

OUT6 (OUT6A)

NOTES

1. EXPOSED DIE PAD MUST BE CONNECTED TO GND.

07216-003

SDIO/SDA

SDO

GND

SP1

SP0

EEPROM

RESET

PD

OUT9 (OUT9A)

OUT9 (OUT9B)

VS_DRV

OUT10 (OUT10A)

OUT10 (OUT10B)

OUT11 (OUT11A)

OUT11 (OUT11B)

VS

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

VS

REFMON

LD

VCP

CP

STATUS

REF_SEL

SYNC

LF

BYPASS

VS

VS

CLK

CLK

CS

SCLK/SCL

Figure 5. Pin Configuration

Table 21. Pin Function Descriptions

Input/

Output

I

Pin

Type

Power

Mnemonic

VS

Description

3.3 V Power Pins.

O

O

I

3.3 V CMOS

3.3 V CMOS

Power

REFMON

LD

VCP

5

O

Loop filter

CP

6

7

O

I

3.3 V CMOS

3.3 V CMOS

STATUS

REF_SEL

8

I

3.3 V CMOS

SYNC

9

10

I

O

Loop filter

Loop filter

LF

BYPASS

13

I

CLK

14

I

Differential

clock input

Differential

clock input

Reference Monitor (Output). This pin has multiple selectable outputs.

Lock Detect (Output). This pin has multiple selectable outputs.

Power Supply for Charge Pump (CP); VS ≤ VCP ≤ 5.25 V. VCP must still be connected

to 3.3 V if the PLL is not used.

Charge Pump (Output). This pin connects to an external loop filter; it can be left

unconnected if the PLL is not used.

Programmable Status Output.

Reference Select. This pin selects REF1 (low) or REF2 (high) and has an internal 30 kΩ

pull-down resistor.

Manual Synchronization and Manual Holdover. This pin initiates a manual

synchronization and is used for manual holdover. Active low. This pin has an

internal 30 kΩ pull-up resistor.

Loop Filter (Input). This pin connects internally to the VCO control voltage node.

This pin is for bypassing the LDO to ground with a 220 nF capacitor. It can be left

unconnected if the PLL is not used.

Along with CLK, this pin is the differential input for the clock distribution section.

Pin No.

1, 11, 12,

32, 40, 41,

49, 57, 60,

61

2

3

4

CLK

Along with CLK, this pin is the differential input for the clock distribution section.

If a single-ended input is connected to the CLK pin, connect a 0.1 µF bypass capacitor

from this pin to ground.

Rev. B | Page 18 of 80

�Data Sheet

AD9520-3

Pin No.

15

Input/

Output

I

Pin

Type

3.3 V CMOS

Mnemonic

CS

16

I

3.3 V CMOS

SCLK/SCL

17

18

19, 59

20

I/O

O

I

I

SDIO/SDA

SDO

GND

SP1

21

I

22

I

3.3 V CMOS

3.3 V CMOS

GND

Three-level

logic

Three-level

logic

3.3 V CMOS

23

24

25

I

I

O

RESET

PD

OUT9 (OUT9A)

26

O

27, 35,

46, 54

28

I

3.3 V CMOS

3.3 V CMOS

LVPECL or

CMOS

LVPECL or

CMOS

Power

OUT10 (OUT10A)

29

O

30

O

31

O

33

O

34

O

36

O

37

O

38

O

39

O

42

O

43

O

44

O

45

O

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

O

SP0

EEPROM

OUT9 (OUT9B)

VS_DRV

OUT10 (OUT10B)

OUT11 (OUT11A)

OUT11 (OUT11B)

OUT6 (OUT6A)

OUT6 (OUT6B)

OUT7 (OUT7A)

OUT7 (OUT7B)

OUT8 (OUT8A)

OUT8 (OUT8B)

OUT5 (OUT5B)

OUT5 (OUT5A)

OUT4 (OUT4B)

OUT4 (OUT4A)

Description

Serial Control Port Chip Select; Active Low. This pin has an internal 30 kΩ

pull-up resistor.

Serial Control Port Clock Signal. This pin has an internal 30 kΩ pull-down resistor

in SPI mode but is high impedance in I²C mode.

Serial Control Port Bidirectional Serial Data In/Out.

Serial Control Port Unidirectional Serial Data Out.

Ground Pins.

Select SPI or I²C as the serial interface port and select the I²C slave address in I²C

mode. Three-level logic. This pin is internally biased for the open logic level.

Select SPI or I²C as the serial interface port and select the I²C slave address in I²C

mode. Three-level logic. This pin is internally biased for the open logic level.

Setting this pin high selects the register values stored in the internal EEPROM to be

loaded at reset and/or power-up. Setting this pin low causes the AD9520-3 to load

the hard-coded default register values at power-up/reset (unless Register

0xB02[1] is used. See the Soft Reset via the Serial Port section). This pin has an

internal 30 kΩ pull-down resistor. Note that, to guarantee proper loading of the

EEPROM during startup, a high-low-high pulse on the RESET pin should occur after

the power supply has stabilized.

Chip Reset, Active Low. This pin has an internal 30 kΩ pull-up resistor.

Chip Power Down, Active Low. This pin has an internal 30 kΩ pull-up resistor.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Output Driver Power Supply Pins. As a group, these pins can be set to either

2.5 V or 3.3 V. All four pins must be set to the same voltage.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output, or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Rev. B | Page 19 of 80

�AD9520-3

Pin No.

47

Input/

Output

O

48

O

50

O

51

O

52

O

53

O

55

O

56

O

58

O

62

O

63

I

64

I

EPAD

Data Sheet

Pin

Type

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

LVPECL or

CMOS

Current set

resistor

Current set

resistor

Reference

input

Reference

input

GND

Mnemonic

OUT3 (OUT3B)

OUT3 (OUT3A)

OUT2 (OUT2B)

OUT2 (OUT2A)

OUT1 (OUT1B)

OUT1 (OUT1A)

OUT0 (OUT0B)

OUT0 (OUT0A)

RSET

CPRSET

REFIN (REF2)

REFIN (REF1)

GND

Description

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Output. This pin can be configured as one side of a differential LVPECL

output or as a single-ended CMOS output.

Clock Distribution Current Set Resistor. Connect a 4.12 kΩ resistor from this pin

to GND.

Charge Pump Current Set Resistor. Connect a 5.1 kΩ resistor from this pin to GND.

This resistor can be omitted if the PLL is not used.

Along with REFIN, this is the differential input for the PLL reference. Alternatively,

this pin is a single-ended input for REF2.

Along with REFIN, this is the differential input for the PLL reference. Alternatively,

this pin is a single-ended input for REF1.

The exposed die pad must be connected to GND.

Rev. B | Page 20 of 80

�Data Sheet

AD9520-3

TYPICAL PERFORMANCE CHARACTERISTICS

350

5

3 CHANNELS—6 LVPECL

CURRENT FROM CP PIN (mA)

CURRENT (mA)

300

3 CHANNELS—3 LVPECL

250

2 CHANNELS—2 LVPECL

200

150

4

PUMP DOWN

PUMP UP

3

2

1

0

500

1000

1500

2000

2500

3000

FREQUENCY (MHz)

0

07216-108

100

0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

VOLTAGE ON CP PIN (V)

Figure 6. Total Current vs. Frequency, CLK-to-Output (PLL Off),

LVPECL Outputs Terminated 50 Ω to VS_DRV − 2 V

07216-111

1 CHANNEL—1 LVPECL

Figure 9. Charge Pump Characteristics at CPV = 3.3 V

240

5

3 CHANNELS—6 CMOS

CURRENT FROM CP PIN (mA)

220

CURRENT (mA)

200

180

3 CHANNELS—3 CMOS

160

140

2 CHANNELS—2 CMOS

120

4

PUMP DOWN

PUMP UP

3

2

1

1 CHANNEL—1 CMOS

50

100

150

200

250

FREQUENCY (MHz)

0

0

1.5

2.0

2.5

3.0

3.5

4.0

4.5

5.0

Figure 10. Charge Pump Characteristics at CPV = 5.0 V

–140

PFD PHASE NOISE REFERRED TO PFD INPUT

(dBc/Hz)

70

65

60

55

50

45

40

35

30

1.8

1.9

2.0

2.1

VCO FREQUENCY (GHz)

2.2

2.3

07216-010

KVCO (MHz/V)

1.0

VOLTAGE ON CP PIN (V)

Figure 7. Total Current vs. Frequency, CLK-to-Output (PLL Off),

CMOS Outputs with 10 pF Load

25

1.7

0.5

–145

–150

–155

–160

–165

–170

0.1

1

10

100

PFD FREQUENCY (MHz)

Figure 11. PFD Phase Noise Referred to PFD Input vs. PFD Frequency

Figure 8. KVCO vs. VCO Frequency

Rev. B | Page 21 of 80

07216-013

0

07216-109

80

07216-112

100

�AD9520-3

Data Sheet

–208

3.5

VS_DRV = 3.3V

3.0

VS_DRV = 3.135V

–212

VS_DRV = 2.5V

2.5

–214

VOH (V)

PLL FIGURE OF MERIT (dBc/Hz)

–210

–216

–218

VS_DRV = 2.35V

2.0

1.5

DIFFERENTIAL INPUT

1.0

–220

0.5

–222

0

0.2

0.4

0.6

0.8

1.0

1.2

1.4

INPUT SLEW RATE (V/ns)

0

10k

07216-114

–224

1k

100

RESISTIVE LOAD (Ω)

07216-118

SINGLE-ENDED INPUT

Figure 15. CMOS Output VOH (Static) vs. RLOAD (to Ground)

Figure 12. PLL Figure of Merit (FOM) vs. Slew Rate at REFIN/REFIN

0

1.2

–10

0.8

DIFFERENTIAL OUTPUT (V)

–20

POWER (dBm)

–30

–40

–50

–60

–70

–80

0.4

0

–0.4

–0.8

105

110

115

120

125

130

135

140

145

FREQUENCY (MHz)

–1.2

07216-116

–100

100

0

2

4

6

8

10

12

14

16

18

20

22

24

TIME (ns)

Figure 13. PFD/CP Spurs; 122.88 MHz; PFD = 15.36 MHz;

LBW = 127 kHz; ICP = 3.0 mA; fVCO = 1966.08 MHz

07216-014

–90

Figure 16. LVPECL Output (Differential) at 100 MHz

0

1.0

–10

DIFFERENTIAL SWING (V p-p)

–20

POWER (dBm)

–30

–40

–50

–60

–70

–80

0.6

0.2

–0.2

–0.6

122.58

122.78

122.98

123.18

123.38

FREQUENCY (MHz)

Figure 14. Output Spectrum, LVPECL; 122.88 MHz; PFD = 15.36 MHz;

LBW = 127 kHz; ICP = 3.0 mA; fVCO = 1966.08 MHz

Rev. B | Page 22 of 80

–1.0

0

0.5

1.0

TIME (ns)

Figure 17. LVPECL Differential Voltage Swing at 1600 MHz

1.5

07216-015

–100

122.38

07216-117

–90

�Data Sheet

AD9520-3

4.0

3.2

3.5

2.8

3.0

1.6

1.2

2.0

1.0

0.4

0.5

0

10

20

30

40

50

60

70

80

90

100

TIME (ns)

20pF

0

0

100

200

300

400

500

600

700

FREQUENCY (MHz)

Figure 21. CMOS Output Swing vs. Frequency and Capacitive Load

Figure 18. CMOS Output with 10 pF Load at 25 MHz

–40

2pF LOAD

3.2

10pF

1.5

0.8

0

–50

2.8

–60

PHASE NOISE (dBc/Hz)

10pF

LOAD

2.4

AMPLITUDE (V)

2.5

07216-124

AMPLITUDE (V)

2pF

2.0

07216-018

AMPLITUDE (V)

2.4

2.0

1.6

1.2

0.8

–70

–80

–90

–100

–110

–120

–130

0.4

1

2

3

4

5

6

7

8

9

10

TIME (ns)

–150

1k

07216-019

0

10k

100k

1M

10M

100M

FREQUENCY (Hz)

07216-023

–140

0

Figure 22. Internal VCO Phase Noise (Absolute), Direct-to-LVPECL at 1750 MHz

Figure 19. CMOS Output with 2 pF and 10 pF Load at 250 MHz

2.0

–40

–60

PHASE NOISE (dBc/Hz)

1.8

1.6

1.4

1.2

–70

–80

–90

–100

–110

–120

–130

0

0.5

1.0

1.5

2.0

2.5

3.0

FREQUENCY (GHz)

Figure 20. LVPECL Differential Voltage Swing vs. Frequency

–150

1k

10k

100k

1M

FREQUENCY (Hz)

10M

100M

07216-024

–140

1.0

07216-123

DIFFERENTIAL SWING (V p-p)

–50

Figure 23. Internal VCO Phase Noise (Absolute), Direct-to-LVPECL at 2000 MHz

Rev. B | Page 23 of 80

�AD9520-3

Data Sheet

–40

–100

–50

–110

–70

PHASE NOISE (dBc/Hz)

PHASE NOISE (dBc/Hz)

–60

–80

–90

–100

–110

–120

–130

–120

–130

–140

–150

10k

100k

1M

10M

100M

FREQUENCY (Hz)

–160

10

07216-025

–150

1k

–110

–120

PHASE NOISE (dBc/Hz)

–150

1k

10k

100k

1M

10M

100M

100M

–130

–140

–150

–170

10

100

1k

10k

100k

1M

10M

100M

FREQUENCY (Hz)

Figure 25. Additive (Residual) Phase Noise, CLK-to-LVPECL at

245.76 MHz, Divide-by-1

Figure 28. Additive (Residual) Phase Noise, CLK-to-CMOS at

50 MHz, Divide-by-20

–100

–110

–110

PHASE NOISE (dBc/Hz)

–100

–120

–130

–140

–120

–130

–140

–150

–150

100

1k

10k

100k

1M

10M

100M

FREQUENCY (Hz)

07216-129

PHASE NOISE (dBc/Hz)

10M

07216-131

100

FREQUENCY (Hz)

–160

10

1M

–160

07216-128

–160

10

100k

–160

10

100

1k

10k

100k

1M

10M

100M

FREQUENCY (Hz)

Figure 29. Additive (Residual) Phase Noise, CLK-to-CMOS at

250 MHz, Divide-by-4

Figure 26. Additive (Residual) Phase Noise, CLK-to-LVPECL at

200 MHz, Divide-by-5

Rev. B | Page 24 of 80

07216-132

PHASE NOISE (dBc/Hz)

–110

–140

10k

Figure 27. Additive (Residual) Phase Noise, CLK-to-LVPECL at

1600 MHz, Divide-by-1

–100

–130

1k

FREQUENCY (Hz)

Figure 24. Internal VCO Phase Noise (Absolute), Direct-to-LVPECL at 2250 MHz

–120

100

07216-130

–140

�Data Sheet

AD9520-3

–100

–80

INTEGRATED RMS JITTER (12kHz TO 20MHz): 377 fs

–90

–100

PHASE NOISE (dBc/Hz)

PHASE NOISE (dBc/Hz)

–110

–120

–130

–140

–110

–120

–130

–140

–150

10k

100k

1M

10M

100M

FREQUENCY (Hz)

–160

1k

07216-033

–160

1k

10k

100k

1M

10M

100M

FREQUENCY (Hz)

07216-034

–150

NOTES

1. THE LOOP FILTER USED TO GENERATE THIS PLOT IS SHOWN IN FIGURE 41.

NOTES

1. THE LOOP FILTER USED TO GENERATE THIS PLOT IS SHOWN IN FIGURE 42.

Figure 30. Phase Noise (Absolute) Clock Generation; Internal VCO at

1.966 GHz; PFD = 15.36 MHz; LBW = 40 kHz; LVPECL Output = 122.88 MHz

Figure 32. Phase Noise (Absolute) Clock Cleanup; Internal VCO at 1.866 GHz;

PFD = 120 kHz; LBW = 1.84 kHz; LVPECL Output = 155.52 MHz

1000

–140

–150

–160

1k

10k

100k

1M

FREQUENCY (Hz)

10M

100M

Figure 31. Phase Noise (Absolute), External VCXO (Toyocom TCO-2112)

at 245.76 MHz; PFD = 15.36 MHz; LBW = 250 Hz; LVPECL Output = 245.76 MHz

Rev. B | Page 25 of 80

OC-48 OBJECTIVE MASK

AD9520

100

fOBJ

10

1

NOTE: 375UI MAX AT 10Hz OFFSET IS THE

MAXIMUM JITTER THAT CAN BE

GENERATED BY THE TEST EQUIPMENT.

FAILURE POINT IS GREATER THAN 375UI.

0.1

0.01

0.1

1

10

100

JITTER FREQUENCY (kHz)

Figure 33. Telcordia GR-253 Jitter Tolerance Plot

1000

07216-134

INPUT JITTER AMPLITUDE (UI p-p)

–130

07216-135

PHASE NOISE (dBc/Hz)

–120

�AD9520-3

Data Sheet

TERMINOLOGY

Phase Jitter and Phase Noise

An ideal sine wave can be thought of as having a continuous

and even progression of phase with time from 0° to 360° for

each cycle. Actual signals, however, display a certain amount

of variation from ideal phase progression over time. This

phenomenon is called phase jitter. Although many causes can

contribute to phase jitter, one major cause is random noise,

which is characterized statistically as being Gaussian (normal)

in distribution.

This phase jitter leads to a spreading out of the energy of the

sine wave in the frequency domain, producing a continuous

power spectrum. This power spectrum is usually reported as a