FEATURES

FUNCTIONAL BLOCK DIAGRAM

Output frequency: PLL2_TO1

YES

YES

1PLL2_TO IS A CALCULATED TIMEOUT VALUE. SEE THE THEORY OF OPERATION, COMPONENT BLOCKS—INPUT PLL (PLL1) FOR ITS FORMULA.

Figure 44. AD9523 Device Initialization

Rev. D | Page 39 of 60

08439-145

END

�AD9523

Data Sheet

SOFTWARE

GENERATED

AD9523 SETUP

FILE

START

WRITE:

R0x000 TO R0x006

WRITE:

R0x010 TO R0x01D

WRITE:

R0x0F0 TO R0x0F9

WRITE:

R0x190 TO R0x1BB

WRITE:

R0x230 TO R0x233

WRITE:

R0xA00 TO R0xA16

END

08439-146

WRITE:

R0x234 = 0x01

Figure 45. Subprocess: Write Registers from Setup File

Rev. D | Page 40 of 60

�Data Sheet

AD9523

POWER DISSIPATION AND THERMAL CONSIDERATIONS

The AD9523 is a multifunctional, high speed device that targets

a wide variety of clock applications. The numerous innovative

features contained in the device each consume incremental power.

If all outputs are enabled in the maximum frequency and mode

that have the highest power, the safe thermal operating conditions

of the device may be exceeded. Careful analysis and consideration

of power dissipation and thermal management are critical

elements in the proper application of the AD9523 device.

The AD9523 device is specified to operate within the industrial

temperature range of –40°C to +85°C. This specification is

conditional, however, such that the absolute maximum junction

temperature is not exceeded (as specified in Table 17). At

high operating temperatures, extreme care must be taken when

operating the device to avoid exceeding the junction temperature

and potentially damaging the device.

A maximum junction temperature is listed in Table 1 with the

ambient operating range. The ambient range and maximum

junction temperature specifications ensure the performance of

the device, as guaranteed in the Specifications section.

Many variables contribute to the operating junction temperature

within the device, including

•

•

•

•

Selected driver mode of operation

Output clock speed

Supply voltage

Ambient temperature

The combination of these variables determines the junction

temperature within the AD9523 device for a given set of

operating conditions.

The AD9523 is specified for an ambient temperature (TA). To

ensure that TA is not exceeded, an airflow source can be used.

Use the following equation to determine the junction

temperature on the application PCB:

Clock speed directly and linearly influences the total power

dissipation of the device and, therefore, the junction temperature.

Two operating frequencies are listed under the incremental power

dissipation parameter in Table 3. Using linear interpretation is

a sufficient approximation for frequencies not listed in the table.

When calculating power dissipation for thermal consideration,

the amount of power dissipated in the 100 Ω resistor must be

removed. If using the data in Table 2, this power is already

removed. If using the current vs. frequency graphs provided in

the Typical Performance Characteristics section, the power into

the load must be subtracted, using the following equation:

Differential Output Voltage Swing 2

100 Ω

EVALUATION OF OPERATING CONDITIONS

The first step in evaluating the operating conditions is to

determine the maximum power consumption (PD) internal

to the AD9523. The maximum PD excludes power dissipated

in the load resistors of the drivers because such power is external

to the device. Use the power dissipation specifications listed in

Table 3 to calculate the total power dissipated for the desired

configuration. The base typical configuration parameter in

Table 3 lists a power of 428 mW, which includes one LVPECL

output at 122.88 MHz. If the frequency of operation is not listed

in Table 3, see the Typical Performance Characteristics section,

current vs. frequency and driver mode to calculate the power

dissipation; then add 20% for maximum current draw. Remove

the power dissipated in the load resistor to achieve the most

accurate power dissipation internal to the AD9523. See Table 30

for a summary of the incremental power dissipation from the base

power configuration for two different examples.

Table 30. Temperature Gradient Examples

TJ = TCASE + (ΨJT × PD)

where:

TJ is the junction temperature (°C).

TCASE is the case temperature (°C) measured by the user at the

top center of the package.

ΨJT is the value from Table 18.

PD is the power dissipation of the AD9523.

Values of θJA are provided for package comparison and PCB

design considerations. θJA can be used for a first-order

approximation of TJ by the equation

TJ = TA + (θJA × PD)

where TA is the ambient temperature (°C).

Values of θJC are provided for package comparison and PCB

design considerations when an external heat sink is required.

Values of ΨJB are provided for package comparison and PCB

design considerations.

CLOCK SPEED AND DRIVER MODE

Description

Example 1

Base Typical

Configuration

Output Driver

Output Driver

Total Power

Example 2

Base Typical

Configuration

Output Driver

Total Power

Mode

Frequency

(MHz)

Maximum

Power (mW)

428

6 × LVPECL

6 × LVDS

122.88

245.76

330

110

868

428

13 × LVPECL

983.04

2066

2500

The second step is to multiply the power dissipated by the thermal

impedance to determine the maximum power gradient. For this

example, a thermal impedance of θJA = 20.1°C/W was used.

Rev. D | Page 41 of 60

�AD9523

Data Sheet

Example 1

THERMALLY ENHANCED PACKAGE MOUNTING

GUIDELINES

(868 mW × 20.1°C/W) = 17.4°C

With an ambient temperature of 85°C, the junction temperature is

TJ = 85°C + 17.4°C = 102°C

See the AN-772 Application Note, A Design and Manufacturing

Guide for the Lead Frame Chip Scale Package (LFCSP), for more

information about mounting devices with an exposed paddle.

This junction temperature is below the maximum allowable.

Example 2

(2500 mW × 20.1°C/W) = 50.2°C

With an ambient temperature of 85°C, the junction temperature is

TJ = 85°C + 50°C = 135°C

This junction temperature exceeds the maximum allowable

range. To operate in the condition of Example 2, the ambient

temperature must be lowered to 65°C.

Rev. D | Page 42 of 60

�Data Sheet

AD9523

CONTROL REGISTERS

CONTROL REGISTER MAP

Register addresses that are not listed in Table 31 are not used, and writing to those registers has no effect. Registers that are marked as

reserved must never have their values changed. When writing to registers with bits that are marked reserved, the user must take care to

always write the default value for the reserved bits.

Table 31. Control Register Map

Addr

Register

(Hex)

Name

Serial Port Configuration

SPI mode

0x000

serial port

configuration

I2C mode

serial port

configuration

Readback

0x004

control

EEPROM

0x005

customer

0x006

version ID

Input PLL (PLL1)

PLL1 REFA

0x010

R divider

0x011

control

0x012

0x013

PLL1 REFB

R divider

control

0x014

PLL1 reference

test divider

PLL1 reserved

PLL1 feedback

N divider

control

0x015

0x016

0x017

0x018

PLL1 charge

pump control

0x019

(MSB)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Soft reset

Reserved

Reserved

Soft reset

Reserved

LSB first/

address

increment

Reserved

Soft reset

Reserved

Reserved

Soft reset

LSB first/

address

increment

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

SDO

active

(LSB)

Bit 0

Default

Value

(Hex)

SDO active

0x00

Reserved

0x00

Read back

active registers

0x00

EEPROM customer version ID[7:0] (LSB)

EEPROM customer version ID[15:8] (MSB)

10-bit REFA R divider[7:0] (LSB)

Reserved

10-bit REFB R divider[7:0] (LSB)

Reserved

Reserved

Reserved

Reserved

Reserved

0x00

0x00

10-bit REFA R divider[9:8]

(MSB)

10-bit REFB R divider[9:8]

(MSB)

REF_TEST divider

Reserved

Reserved

Reserved Reserved

10-bit PLL1 feedback divider[7:0] (LSB)

Reserved

PLL1

charge

pump

tristate

Reserved

Reserved

Reserved

0x01A

PLL1

input receiver

control

REF_TEST

input

receiver

enable

REFB

differential

receiver

enable

REFA

differential

receiver

enable

0x01B

REF_TEST,

REFA, REFB,

and ZD_IN

control

Reserved

Reserved

Zero delay

mode

0x01C

PLL1

miscellaneous

control

Enable

REFB R

divider independent

division

control

OSC_CTRL

control

voltage to

VCC/2

when ref

clock fails

Reserved

OSC_IN signal

feedback

for PLL1

Antibacklash

pulse width control

REFA

receiver

enable

Input

REFA, REFB

receiver

powerdown

control

enable

ZD_IN

differen.

receiver

mode

enable

ZD_IN

singleended

receiver

mode

enable

(CMOS

mode)

Reference selection mode

Rev. D | Page 43 of 60

0x00

0x00

0x00

Reserved

Reserved

10-bit PLL1 feedback divider[9:8]

(MSB)

PLL1 charge pump control

Enable SPI

control of

antibacklash

pulse width

REFB receiver

enable

0x00

0x00

0x00

0x00

0x00

0x0C

PLL1 charge pump mode

0x00

OSC_IN

single-ended

receiver

mode enable

(CMOS mode)

OSC_IN

differential

receiver mode

enable

0x00

REFB

single-ended

receiver

mode enable

(CMOS mode)

REFA

single-ended

receiver

mode enable

(CMOS mode)

0x00

Reserved

Reserved

0x00

�AD9523

Data Sheet

Addr

(Hex)

0x01D

Register

Name

PLL1 loop

filter zero

resistor control

(MSB)

Bit 7

Reserved

Bit 6

Reserved

Bit 5

Reserved

Bit 4

Reserved

Bit 3

Bit 2

0x01E

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Output PLL (PLL2)

PLL2 charge

0x0F0

pump control

PLL2

0x0F1

feedback

N divider

control

0x0F2

PLL2 control

0x0F3

VCO control

0x0F4

VCO divider

control

0x0F5

PLL2 loop

filter control

(9 bits)

0x0F6

0x0F9

Reserved

to

0x0FE

Clock Distribution

Channel 0

0x190

control

0x191

0x192

0x193

0x194

0x195

0x196

0x197

0x198

0x199

0x19A

0x19B

0x19C

0x19D

0x19E

Channel 1

control

Channel 2

control

Channel 3

control

Channel 4

control

Bit 1

PLL1 loop filter, RZERO

Reserved

(LSB)

Bit 0

Default

Value

(Hex)

0x00

Reserved

0x00

PLL2 charge pump control

A counter

0x00

B counter

PLL2 lock

detector

powerdown

Reserved

Reserved

Enable

frequency

doubler

Reserved

Reserved

Reserved

Reserved

Reserved

Pole 2 resistor (RPOLE2)

Enable SPI

control of

antibacklash

pulse width

Force release

of distribution

sync when

PLL2 is

unlocked

Reserved

Antibacklash

pulse width control

Treat

reference

as valid

Force

VCO to

midpoint

frequency

VCO

divider

powerdown

Zero resistor (RZERO)

0x04

PLL2 charge pump mode

Calibrate VCO

(not autoclearing)

0x00

Pole 1 capacitor (CPOLE1)

0x00

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Invert

divider

output

Ignore

sync

Powerdown

channel

Lower power

mode

Invert

divider

output

Invert

divider

output

Invert

divider

output

Invert

divider

output

Ignore

sync

Ignore

sync

Ignore

sync

Ignore

sync

Rev. D | Page 44 of 60

0x00

VCO divider

Reserved

10-bit channel divider[7:0] (LSB)

Divider phase[5:0]

Lower power

Powermode

down

channel

10-bit channel divider[7:0] (LSB)

Divider phase[5:0]

Lower power

Powermode

down

channel

10-bit channel divider[7:0] (LSB)

Divider phase[5:0]

PowerLower power

down

mode

channel

10-bit channel divider[7:0] (LSB)

Divider phase[5:0]

Lower power

Powermode

down

channel

10-bit channel divider[7:0] (LSB)

Divider phase[5:0]

Reserved

0x03

Bypass internal

RZERO resistor

Reserved

0x00

0x00

Driver mode

0x00

10-bit channel divider[9:8] (MSB)

Driver mode

0x1F

0x04

0x20

10-bit channel divider[9:8] (MSB)

Driver mode

0x1F

0x04

0x00

10-bit channel divider[9:8] (MSB)

Driver mode

0x1F

0x04

0x20

10-bit channel divider[9:8] (MSB)

Driver mode

0x1F

0x04

0x00

10-bit channel divider[9:8] (MSB)

0x1F

0x04

�Data Sheet

Addr

(Hex)

0x19F

0x1A0

0x1A1

0x1A2

0x1A3

0x1A4

0x1A5

0x1A6

0x1A7

0x1A8

0x1A9

0x1AA

0x1AB

0x1AC

0x1AD

0x1AE

0x1AF

0x1B0

0x1B1

0x1B2

0x1B3

0x1B4

0x1B5

0x1B6

0x1B7

0x1B8

0x1B9

0x1BA

0x1BB

Register

Name

Channel 5

control

Channel 6

control

Channel 7

control

Channel 8

control

Channel 9

control

Channel 10

control

Channel 11

control

Channel 12

control

Channel 13

control

AD9523

(MSB)

Bit 7

Invert

divider

output

Invert

divider

output

Invert

divider

output

Invert

divider

output

Invert

divider

output

Invert

divider

output

Invert

divider

output

Invert

divider

output

Invert

divider

output

Bit 6

Ignore

sync

Ignore

sync

Ignore

sync

Ignore

sync

Ignore

sync

Ignore

sync

Ignore

sync

Ignore

sync

Ignore

sync

PLL1 output

control

Reserved

Reserved

PLL1 output

channel

control

PLL1

output

driver

powerdown

Reserved

Bit 5

Powerdown

channel

Bit 4

Lower power

mode

Bit 3

Bit 2

Bit 1

Driver mode

(LSB)

Bit 0

10-bit channel divider[7:0] (LSB)

Divider phase[5:0]

10-bit channel divider[9:8] (MSB)

Lower power

PowerDriver mode

mode

down

channel

10-bit channel divider[7:0] (LSB)

Divider phase[5:0]

10-bit channel divider[9:8] (MSB)

Lower power

PowerDriver mode

mode

down

channel

10-bit channel divider[7:0] (LSB)

Divider phase[5:0]

10-bit channel divider[9:8] (MSB)

Lower power

PowerDriver mode

mode

down

channel

10-bit channel divider[7:0] (LSB)

Divider phase[5:0]

10-bit channel divider[9:8] (MSB)

Lower power

PowerDriver mode

mode

down

channel

10-bit channel divider[7:0] (LSB)

Divider phase[5:0]

10-bit channel divider[9:8] (MSB)

Lower power

PowerDriver mode

mode

down

channel

10-bit channel divider[7:0] (LSB)

Divider phase[5:0]

10-bit channel divider[9:8] (MSB)

Lower power

PowerDriver mode

mode

down

channel

10-bit channel divider[7:0] (LSB)

Divider phase[5:0]

10-bit channel divider[9:8] (MSB)

Lower power

PowerDriver mode

mode

down

channel

10-bit channel divider[7:0] (LSB)

Divider phase[5:0]

10-bit channel divider[9:8] (MSB)

Lower power

PowerDriver mode

mode

down

channel

10-bit channel divider[7:0] (LSB)

Divider phase[5:0]

10-bit channel divider[9:8] (MSB)

PLL1 output

Reserved

Out PLL1 output

CMOS driver

strength

Route VCXO

Route VCXO

Route

Route

Reserved

Reserved

clock to Ch 0

clock to Ch 1

VCXO

VCXO

divider input

divider input

clock to

clock to

Ch 2

Ch 3

divider

divider

input

input

Rev. D | Page 45 of 60

Default

Value

(Hex)

0x20

0x1F

0x04

0x00

0x1F

0x04

0x20

0x1F

0x04

0x00

0x1F

0x04

0x20

0x1F

0x04

0x00

0x1F

0x04

0x20

0x1F

0x04

0x00

0x1F

0x04

0x20

0x1F

0x04

0x00

0x80

�AD9523

Addr

Register

(Hex)

Name

Readback

0x22C

Readback 0

Data Sheet

(MSB)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

(LSB)

Bit 0

Status PLL1

feedback

clock

Reserved

Status

VCXO

Status

REF_TEST

Status

REFB

Status

REFA

Lock detect

PLL2

Lock detect

PLL1

Reserved

Reserved

Holdover

active

Reserved

VCO

calibration

in progress

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Selected

reference

(in auto

mode)

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

0x22D

Readback 1

Status PLL2

reference

clock

Reserved

0x22E

0x22F

Other

0x230

0x231

0x232

Readback 2

Readback 3

Reserved

Reserved

Reserved

Reserved

Status signals

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Enable

STATUS_

EEPROM on

STATUS0 pin

Status Monitor 0 control

Status Monitor 1 control

STATUS1 STATUS0

Reserved

pin

pin

divider

divider

enable

enable

Reserved

Reserved

Reserved

Reserved

Reserved

0x233

Power-down

control

Update all

registers

EEPROM Storage Sequence

Serial port

0xA00

configuration

0xA01

0xA02

Readback

0xA03

control and

EEPROM

0xA04

customer

0xA05

version ID

0x234

0xA06

0xA07

0xA08

0xA09

0xA0A

0xA0B

0xA0C

0xA0D

0xA0E

0xA0F

0xA10

0xA11

0xA12

Input PLL

(PLL1)

Output PLL

(PLL2)

Clock

distribution

Clock input

and REF

Other

0xA13

0xA14

0xA15

IO_UPDATE

0xA16

End of data

PLL1

powerdown

Reserved

EEPROM Buffer Segment

Default Setting: Size of transfer: one byte

EEPROM Buffer Segment

Default Setting: Starting address 0x0000

EEPROM Buffer Segment

Default Setting: Size of transfer: three bytes

EEPROM Buffer Segment

Default Setting: Starting address 0x0004

EEPROM Buffer Segment

Default Setting: Size of transfer: 15 bytes

EEPROM Buffer Segment

Default Setting: Starting address 0x0010

EEPROM Buffer Segment

Default Setting: Size of transfer: 15 bytes

EEPROM Buffer Segment

Default Setting: Starting address 0x00F0

EEPROM Buffer Segment

Default Setting: Size of transfer: 44 bytes

EEPROM Buffer Segment

Default Setting: Starting address 0x0190

EEPROM Buffer Segment

Default Setting: Size of transfer: two bytes

EEPROM Buffer Segment

Default Setting: Starting address 0x01E0

EEPROM Buffer Segment

Default Setting: Size of transfer: four bytes

EEPROM Buffer Segment

Default Setting: Starting address 0x0230

EEPROM Buffer Segment

Default Setting: Command: IO_UPDATE

EEPROM Buffer Segment

Default Setting: Command: End of data

Rev. D | Page 46 of 60

PLL2

power-down

Sync dividers

(manual

control)

0: sync signal

inactive

1: dividers

held in sync

(same as

SYNC pin low)

Distribution

power-down

IO_UPDATE

Default

Value

(Hex)

0x00

0x00

0x00

0x07

0x00

0x00

0x00

0x00

0x02

0x00

0x04

0x0E

0x00

0x10

0x0E

0x00

0xF0

0x2B

0x01

0x90

0x01

0x01

0xE0

0x03

0x02

0x30

0x80

0xFF

�Data Sheet

Addr

Register

(Hex)

Name

EEPROM Control

STATUS_

0xB00

EEPROM

(read only)

EEPROM error

0xB01

checking

readback

(read only)

EEPROM

0xB02

Control 1

EEPROM

0xB03

Control 2

AD9523

(MSB)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

SOFT_

EEPROM

Reserved

Rev. D | Page 47 of 60

(LSB)

Bit 0

STATUS_

EEPROM

(read only)

EEPROM

data error

(read only)

Enable

EEPROM write

REG2EEPROM

Default

Value

(Hex)

0x00

0x00

0x00

0x00

�AD9523

Data Sheet

CONTROL REGISTER MAP BIT DESCRIPTIONS

Serial Port Configuration (Address 0x000 to Address 0x006)

Table 32. SPI Mode Serial Port Configuration

Address

0x000

0x004

Bits

7

Bit Name

SDO active

6

LSB first/

address

increment

5

Soft reset

4

[3:0]

Reserved

Mirror[7:4]

0

Readback

active registers

Description

Selects unidirectional or bidirectional data transfer mode. This bit is ignored in I2C mode.

0: SDIO pin used for write and read; SDO is high impedance (default).

1: SDO used for read; SDIO used for write; unidirectional mode.

SPI MSB or LSB data orientation. This bit is ignored in I2C mode.

0: data-oriented MSB first; addressing decrements (default).

1: data-oriented LSB first; addressing increments.

Soft reset.

1 (self-clearing): soft reset; restores default values to internal registers.

Reserved.

Bits[3:0] should always mirror Bits[7:4] so that it does not matter whether the part is in MSB first or LSB

first mode (see Register 0x000[6]). Set bits as follows:

Bit 0 = Bit 7.

Bit 1 = Bit 6.

Bit 2 = Bit 5.

Bit 3 = Bit 4.

For buffered registers, serial port readback reads from actual (active) registers instead of from the

buffer.

0 (default): reads values currently applied to the internal logic of the device.

1: reads buffered values that take effect on the next assertion of the input/output update.

Table 33. I2C Mode Serial Port Configuration

Address

0x000

0x004

Bits

[7:6]

5

Bit Name

Reserved

Soft reset

4

[3:0]

Reserved

Mirror[7:4]

0

Read back

active registers

Description

Reserved.

Soft reset.

1 (self-clearing): soft reset; restores default values to internal registers.

Reserved.

Bits[3:0] should always mirror Bits[7:4]. Set bits as follows:

Bit 0 = Bit 7.

Bit 1 = Bit 6.

Bit 2 = Bit 5.

Bit 3 = Bit 4.

For buffered registers, serial port readback reads from actual (active) registers instead of from the

buffer.

0 (default): reads values currently applied to the internal logic of the device.

1: reads buffered values that take effect on the next assertion of the input/output update.

Table 34. EEPROM Customer Version ID

Address

0x005

Bits

[7:0]

0x006

[7:0]

Bit Name

EEPROM

customer

version ID (LSB)

EEPROM

customer

version ID (MSB)

Description

16-bit EEPROM ID, Bits[7:0]. This register, along with Register 0x006, allows the user to store a unique

ID to identify which version of the AD9523 register settings is stored in the EEPROM. It does not affect

AD9523 operation in any way (default: 0x00).

16-bit EEPROM ID, Bits[15:8]. This register, along with Register 0x005, allows the user to store a unique

ID to identify which version of the AD9523 register settings is stored in the EEPROM. It does not affect

AD9523 operation in any way (default: 0x00).

Rev. D | Page 48 of 60

�Data Sheet

AD9523

Input PLL (PLL1) (Address 0x010 to Address 0x01D)

Table 35. PLL1 REFA R Divider Control

Address

0x010

Bits

[7:0]

Bit Name

REFA R divider

0x011

[1:0]

REFA R divider

Description

10-bit REFA R divider, Bits[7:0] (LSB). Divide-by-1 to divide-by-1023.

00000000, 00000001: divide-by-1.

10-bit REFA R divider, Bits[9:8] (MSB).

Table 36. PLL1 REFB R Divider Control1

Address

0x012

Bits

[7:0]

Bit Name

REFB R divider

0x013

[1:0]

REFB R divider

1

Description

10-bit REFB R divider, Bits[7:0] (LSB). Divide-by-1 to divide-by-1023.

00000000, 00000001: divide-by-1.

10-bit REFB R divider, Bits[9:8] (MSB).

Requires Register 0x01C[7] = 1b for division that is independent of REFA division.

Table 37. PLL1 Reference Test Divider

Address

0x014

Bits

[7:6]

[5:0]

Bit Name

Reserved

REF_TEST divider

Description

Reserved

6-bit reference test divider. Divide-by-1 to divide-by-63.

000000, 000001: divide-by-1.

Table 38. PLL1 Reserved

Address

0x015

Bits

[7:0]

Bit Name

Reserved

Description

Reserved

Table 39. PLL1 Feedback N Divider Control

Address

0x016

Bits

[7:0]

Bit Name

PLL1 feedback N divider control

(N_PLL1)

0x017

[1:0]

PLL1 feedback N divider control

(N_PLL1)

Description

10-bit feedback divider, Bits[7:0] (LSB). Divide-by-1 to divide-by-1023.

00000000, 00000001: divide-by-1.

10-bit feedback divider, Bits[1:0] (MSB).

Table 40. PLL1 Charge Pump Control

Address

0x018

Bits

7

[6:0]

Bit Name

PLL1 charge pump tristate

PLL1 charge pump control

0x019

[7:5]

4

Reserved

Enable SPI control of antibacklash

pulse width

[3:2]

Antibacklash pulse width control

[1:0]

PLL1 charge pump mode

Description

Tristates the PLL1 charge pump.

These bits set the magnitude of the PLL1 charge pump current. Granularity is ~0.5 µA

with a full-scale magnitude of ~63.5 µA.

Reserved.

Setting this bit allows user control of the antibacklash pulse width setting in

Register 0x019[3:2].

0 (default): antibacklash period is forced to high.

1: antibacklash period defined by Register 0x019[3:2].

Controls the PFD antibacklash period. These bits default to the high setting unless

reprogrammed using Register 0x019[4] = 1b. The high setting decreases the

maximum allowable PLL1 PFD rate. See Table 7 for ranges.

00: minimum.

01: low.

10: high (initial state unless changed via Register 0x019[4] = 1b).

11: maximum.

Controls the mode of the PLL1 charge pump.

00 (default): tristate.

01: pump up.

10: pump down.

11: normal.

Rev. D | Page 49 of 60

�AD9523

Data Sheet

Table 41. PLL1 Input Receiver Control

Address

0x01A

Bits

7

Bit Name

REF_TEST input receiver enable

6

REFB differential receiver enable

5

REFA differential receiver enable

4

REFB receiver enable

3

REFA receiver enable

2

Input REFA and REFB receiver

power-down control enable

1

OSC_IN single-ended receiver

mode enable (CMOS mode)

0

OSC_IN differential receiver mode

enable

Description

1: enabled.

0: disabled (default).

1: differential receiver mode.

0: single-ended receiver mode (also depends on Register 0x01B[1]) (default).

1: differential receiver mode.

0: single-ended receiver mode (also depends on Register 0x01B[0]) (default).

REFB receiver power-down control mode only when Bit 2 = 1.

1: enable REFB receiver.

0: power down (default).

REFA receiver power-down control mode only when Bit 2 = 1.

1: enable REFA receiver.

0: power down (default).

Enables power-down control of the input receivers, REFA and REFB.

1: power-down control enabled.

0: both receivers enabled (default).

Selects which single-ended input pin is enabled when in single-ended receiver mode

(Register 0x01A[0] = 0).

1: negative receiver from oscillator input (OSC_IN pin) selected.

0: positive receiver from oscillator input (OSC_IN pin) selected (default).

1: differential receiver mode.

0: single-ended receiver mode (also depends on Bit 1) (default).

Table 42. REF_TEST, REFA, REFB, and ZD_IN Control

Address

0x01B

Bits

[7:6]

5

Bit Name

Reserved

Zero delay mode

4

OSC_IN signal feedback for PLL1

3

ZD_IN single-ended receiver

mode enable (CMOS mode)

2

ZD_IN differential receiver

mode enable

1

REFB single-ended receiver

mode enable (CMOS mode)

0

REFA single-ended receiver

mode enable (CMOS mode)

Description

0: reserved (default).

Selects the zero delay mode used (via the ZD_IN pin) when Register 0x01B[4] = 0.

Otherwise, this bit is ignored.

1: internal zero delay mode. The zero delay receiver is powered down. The internal

zero delay path from Distribution Divider Channel 0 is used.

0: external zero delay mode. The ZD_IN receiver is enabled.

Controls the input PLL feedback path, local feedback from the OSC_IN receiver or

zero delay mode.

1: OSC_IN receiver input used for the input PLL feedback (non-zero delay mode).

0: zero delay mode enabled (also depends on Register 0x01B[5] to select the zero

delay path.

Selects which single-ended input pin is enabled when in the single-ended receiver

mode (Register 0x01B[2] = 0).

1: ZD_IN pin enabled.

0: ZD_IN pin enabled.

1: differential receiver mode.

0: single-ended receiver mode (also depends on Register 0x01B[3]).

Selects which single-ended input pin is enabled when in single-ended receiver mode

(Register 0x01A[6] = 0).

1: REFB pin enabled.

0: REFB pin enabled.

Selects which single-ended input pin is enabled when in single-ended receiver mode

(Register 0x01A[5] = 0).

1: REFA pin enabled.

0: REFA pin enabled.

Rev. D | Page 50 of 60

�Data Sheet

AD9523

Table 43. PLL1 Miscellaneous Control

Address

0x01C

1

Bits

7

Bit Name

Enable REFB R divider

independent division control

6

OSC_CTRL control voltage to

VCC/2 when reference clock fails

5

[4:2]

Reserved

Reference selection mode

[1:0]

Reserved

Description

1: REFB R divider is controlled by Register 0x012 and Register 0x013.

0: REFB R divider is set to the same setting as the REFA R divider (Register 0x010

and Register 0x011). This requires that, for the loop to stay locked, the REFA and

REFB input frequencies must be the same.

High permits the OSC_CTRL control voltage to be forced to midsupply when the

feedback or input clocks fail. Low tristates the charge pump output.

1: OSC_CTRL control voltage goes to VCC/2.

0: OSC_CTRL control voltage tracks the tristated (high impedance) charge pump

(through the buffer).

Reserved.

Programs the REFA, REFB mode selection (default = 000).

REF_SEL

Pin

Bit 4

Bit 3

Bit 2

Description

X1

0

0

0

Nonrevertive: stay on REFB.

X1

0

0

1

Revert to REFA.

X1

0

1

0

Select REFA.

X1

0

1

1

Select REFB.

0

1

X1

X1

REF_SEL pin = 0 (low): REFA.

1

1

X1

X1

REF_SEL pin = 1 (high): REFB.

0: reserved (default).

X = don’t care.

Table 44. PLL1 Loop Filter Zero Resistor Control

Address

0x01D

Bits

[7:4]

[3:0]

Bit Name

Reserved

PLL1 loop filter, RZERO

Description

Reserved.

Programs the value of the zero resistor, RZERO.

Bit 3

Bit 2

Bit 1

Bit 0

RZERO Value (kΩ)

0

0

0

0

883

0

0

0

1

677

0

0

1

0

341

0

0

1

1

135

0

1

0

0

10

0

1

0

1

10

0

1

1

0

10

0

1

1

1

10

1

0

0

0

Use external resistor

Rev. D | Page 51 of 60

�AD9523

Data Sheet

Output PLL (PLL2) (Address 0x0F0 to Address 0x0F6)

Table 45. PLL2 Charge Pump Control

Address

0x0F0

Bits

[7:0]

Bit Name

PLL2 charge pump control

Description

These bits set the magnitude of the PLL2 charge pump current. Granularity is ~3.5 µA

with a full-scale magnitude of ~900 µA.

Table 46. PLL2 Feedback N Divider Control

Address

0x0F1

Bits

[7:6]

[5:0]

Bit Name

A counter

B counter

A Counter (Bits[7:6])

A = 0 or A = 1

A = 0 to A = 2

A = 0 to A = 2

A = 0 to A = 3

Description

A counter word.

B counter word.

Feedback Divider Constraints

B Counter (Bits[5:0])

B=4

B=5

B=6

B≥7

Allowed N Division (4 × B + A)

16, 17

20, 21, 22

24, 25, 26

28, 29 … continuous to 255

Table 47. PLL2 Control

Address

0x0F2

Bits

7

Bit Name

PLL2 lock detector power-down

6

5

Reserved

Enable frequency doubler

4

Enable SPI control of antibacklash

pulse width

[3:2]

Antibacklash pulse width control

[1:0]

PLL2 charge pump mode

Description

Controls power-down of the PLL2 lock detector.

1: lock detector powered down.

0: lock detector active.

Default = 0; value must remain 0.

Enables doubling of the PLL2 reference input frequency.

1: enabled.

0: disabled.

Setting this bit allows user control of the antibacklash pulse width setting in

Register 0x0F2[3:2].

0 (default): antibacklash period is forced to high.

1: antibacklash period defined by Register 0x0F[3:2] (recommended setting).

Controls the PFD antibacklash period. These bits default to the high setting unless

reprogrammed using Register 0x0F2[4] = 1b. The high setting decreases the

maximum allowable PLL2 PFD rate. See Table 12 for ranges.

00 minimum.

01: low.

10: high (initial state unless changed via Register 0x0F2[4] = 1b).

11: maximum.

Controls the mode of the PLL2 charge pump.

00: tristate.

01: pump up.

10: pump down.

11 (default): normal.

Rev. D | Page 52 of 60

�Data Sheet

AD9523

Table 48. VCO Control

Address

0x0F3

Bits

[7:5]

4

Bit Name

Reserved

Force release of distribution

sync when PLL2 is unlocked

3

Treat reference as valid

2

Force VCO to midpoint frequency

1

Calibrate VCO (not autoclearing)

0

Reserved

Description

Reserved.

0 (default): distribution is held in sync (static) until the output PLL locks for the first

time. Then it is automatically released from sync with all dividers synchronized.

1: overrides the PLL2 lock detector state; forces release of the distribution from sync.

0 (default): uses the PLL1 VCXO indicator to determine when the reference clock to

the PLL2 is valid.

1: treats the reference clock as valid even if PLL1 does not consider it to be valid.

Selects VCO control voltage functionality.

0 (default): normal VCO operation.

1: forces VCO control voltage to midscale.

1: initiates VCO calibration (this is not an autoclearing bit).

0: resets the VCO calibration.

Reserved.

Table 49. VCO Divider Control

Address

0x0F4

Bits

[7:4]

3

Bit Name

Reserved

VCO divider power-down

[2:0]

VCO divider

Description

Reserved.

1: powers down the divider.

0: normal operation.

Note that the VCO divider connects to all output channels.

Bit 2

Bit 1

Bit 0

Divider Value

0

0

0

Divide-by-4

0

0

1

Divide-by-5

0

1

0

Divide-by-6

0

1

1

Divide-by-7

1

0

0

Divide-by-8

1

0

1

Divide-by-9

1

1

0

Divide-by-10

1

1

1

Divide-by-11

Rev. D | Page 53 of 60

�AD9523

Data Sheet

Table 50. PLL2 Loop Filter Control

Address

0x0F5

0x0F6

Bits

[7:6]

Bit Name

Pole 2 resistor (RPOLE2)

[5:3]

Zero resistor (RZERO)

[2:0]

Pole 1 capacitor (CPOLE1)

[7:1]

0

Reserved

Bypass internal RZERO

resistor

Description

Bit 7

Bit 6

RPOLE2 (Ω)

0

0

900

0

1

450

1

0

300

1

1

225

Bit 5

Bit 4

Bit 3

RZERO (Ω)

0

0

0

3250

0

0

1

2750

0

1

0

2250

0

1

1

2100

1

0

0

3000

1

0

1

2500

1

1

0

2000

1

1

1

1850

Bit 2

Bit 1

Bit 0

CPOLE1 (pF)

0

0

0

0

0

0

1

8

0

1

0

16

0

1

1

24

1

0

0

24

1

0

1

32

1

1

0

40

1

1

1

48

Reserved.

Bypasses the internal RZERO resistor (RZERO = 0 Ω). Requires the use of a series external zero

resistor. This bit is the MSB of the loop filter control register (Address 0x0F5 and Address 0x0F6).

Rev. D | Page 54 of 60

�Data Sheet

AD9523

Clock Distribution (Register 0x190 to Register 0x1B9)

Table 51. Channel 0 to Channel 13 Control (This Same Map Applies to All 14 Channels)

Address

0x190

Bits

7

6

Bit Name

Invert divider output

Ignore sync

5

Power-down channel

4

Lower power mode

(differential modes only)

[3:0]

Driver mode

0x191

[7:0]

0x192

[7:2]

Channel divider,

Bits[7:0] (LSB)

Divider phase

[1:0]

Channel divider, Bits[9:8] (MSB)

Description

Inverts the polarity of the divider’s output clock.

0: obeys chip-level SYNC signal (default).

1: ignores chip-level SYNC signal.

1: powers down the entire channel.

0: normal operation.

Reduces power used in the differential output modes (LVDS/LVPECL/HSTL). This

reduction may result in power savings, but at the expense of performance. Note that

this bit does not affect output swing and current, just the internal driver power.

1: low strength/lower power.

0: normal operation.

Driver mode.

Bit 3 Bit 2 Bit 1 Bit 0 Driver Mode

0

0

0

0

Tristate output

0

0

0

1

LVPECL (8 mA)

0

0

1

0

LVDS (3.5 mA)

0

0

1

1

LVDS (7 mA)

0

1

0

0

HSTL-0 (16 mA)

0

1

0

1

HSTL-1 (8 mA)

0

1

1

0

CMOS (both outputs in phase)

+ Pin: true phase relative to divider output

− Pin: true phase relative to divider output

0

1

1

1

CMOS (opposite phases on outputs)

+ Pin: true phase relative to divider output

− Pin: complement phase relative to divider output

1

0

0

0

CMOS

+ Pin: true phase relative to divider output

− Pin: high-Z

1

0

0

1

CMOS

+ Pin: high-Z

− Pin: true phase relative to divider output

1

0

1

0

CMOS

+ Pin: high-Z

− Pin: high-Z

1

0

1

1

CMOS (both outputs in phase)

+ Pin: complement phase relative to divider output

− Pin: complement phase relative to divider output

1

1

0

0

CMOS (both outputs out of phase)

+ Pin: complement phase relative to divider output

− Pin: true phase relative to divider output

1

1

0

1

CMOS

+ Pin: complement phase relative to divider output

− Pin: high-Z

1

1

1

0

CMOS

+ Pin: high-Z

− Pin: complement phase relative to divider output

1

1

1

1

Tristate output

Division = Channel Divider Bits[9:0] + 1. For example, [9:0] = 0 is divided by 1, [9:0] = 1

is divided by 2 … [9:0] = 1023 is divided by 1024. 10-bit channel divider, Bits[7:0] (LSB).

Divider initial phase after a sync is asserted relative to the divider input clock (from the

VCO divider output). LSB = ½ of a period of the divider input clock.

Phase = 0: no phase offset.

Phase = 1: ½ period offset, …

Phase = 63: 31 period offset.

10-bit channel divider, Bits[9:8] (MSB).

Rev. D | Page 55 of 60

�AD9523

Data Sheet

Table 52. PLL1 Output Control (PLL1_OUT, Pin 72)

Address

0x1BA

Bits

[7:5]

4

Bit Name

Reserved

PLL1 output CMOS driver

strength

[3:0]

PLL1 output divider

Description

Reserved

CMOS driver strength

1: weak

0: strong

0000: divide-by-1

0001: divide-by-2 (default)

0010: divide-by-4

0100: divide-by-8

1000: divide-by-16

No other inputs permitted

Table 53. PLL1 Output Channel Control

Address

0x1BB

Bits

7

[6:4]

3

Bit Name

PLL1 output driver power-down

Reserved

Route VCXO clock to

Channel 3 divider input

2

Route VCXO clock to

Channel 2 divider input

1

Route VCXO clock to

Channel 1 divider input

0

Route VCXO clock to

Channel 0 divider input

Description

PLL1 output driver power-down

Reserved

1: channel uses VCXO clock. Routes VCXO clock to divider input.

0: channel uses VCO divider output clock

1: channel uses VCXO clock. Routes VCXO clock to divider input.

0: channel uses VCO divider output clock

1: channel uses VCXO clock. Routes VCXO clock to divider input.

0: channel uses VCO divider output clock

1: channel uses VCXO clock. Routes VCXO clock to divider input.

0: channel uses VCO divider output clock

Readback (Address 0x22C to Address 0x22D)

Table 54. Readback Registers (Readback 0 and Readback 1)

Address

0x22C

0x22D

Bits

7

Bit Name

Status PLL2 reference clock

6

Status PLL1 feedback clock

5

Status VCXO

4

Status REF_TEST

3

Status REFB

2

Status REFA

1

Lock detect PLL2

0

Lock detect PLL1

[7:4]

3

Reserved

Holdover active

2

Selected reference

(in auto mode)

1

0

Reserved

VCO calibration in progress

Description

1: OK

0: off/clocks are missing

1: OK

0: off/clocks are missing

1: OK

0: off/clocks are missing

1: OK

0: off/clocks are missing

1: OK

0: off/clocks are missing

1: OK

0: off/clocks are missing

1: locked

0: unlocked

1: locked

0: unlocked

Reserved

1: holdover is active (both references are missing)

0: normal operation

Selected reference (applies only when the device automatically selects the reference;

for example, not in manual control mode)

1: REFB

0: REFA

Reserved

1: VCO calibration in progress

0: VCO calibration not in progress

Rev. D | Page 56 of 60

�Data Sheet

AD9523

Other (Address 0x230 to Address 0x234)

Table 55. Status Signals

Address

0x230

0x231

Bits

[7:6]

[5:0]

Bit Name

Reserved

Status Monitor 0 control

Description

Reserved

Bit 5

Bit 4

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Bit 3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

Bit 2

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

Bit 1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

Bit 0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Muxout

GND

PLL1 and PLL2 locked

PLL1 locked

PLL2 locked

Both references are missing (REFA and REFB)

Both references are missing and PLL2 is locked

REFB selected (applies only to auto select mode)

REFA is OK

REFB is OK

REF_TEST is OK

VCXO is OK

PLL1 feedback is OK

PLL2 reference clock is OK

Reserved

REFA and REFB are OK

All clocks are OK (except REF_TEST)

PLL1 feedback is divide-by-2

PLL1 PFD down divide-by-2

PLL1 REF divide-by-2

PLL1 PFD up divide-by-2

GND

GND

GND

GND

All bit combinations after 010111 are reserved

[7:6]

[5:0]

Reserved

Status Monitor 1 control

Reserved

Bit 5

Bit 4

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Bit 3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

Bit 2

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

Bit 1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

Bit 0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Muxout

GND

PLL1 and PLL2 locked

PLL1 locked

PLL2 locked

Both references are missing (REFA and REFB)

Both references are missing and PLL2 is locked

REFB selected (applies only to auto select mode)

REFA is OK

REFB is OK

REF_TEST is OK

VCXO is OK

PLL1 feedback is OK

PLL2 reference clock is OK

Reserved

REFA and REFB are OK

All clocks are OK (except REF_TEST)

GND

GND

GND

GND

PLL2 feedback is divide-by-2

PLL2 PFD down divide-by-2

PLL2 REF divide-by-2

PLL2 PFD up divide-by-2

All bit combinations after 010111 are reserved

Rev. D | Page 57 of 60

�AD9523

Address

0x232

Bits

[7:5]

4

3

Data Sheet

Bit Name

Reserved

Enable STATUS_EEPROM

on STATUS0 pin

STATUS1 pin divider

enable

2

STATUS0 pin divider

enable

1

0

Reserved

Sync dividers

(manual control)

Description

Reserved.

Enables the EEPROM status on the STATUS0 pin.

1: enable status.

Enables a divide-by-4 on the STATUS1 pin, allowing dynamic signals to be viewed at a lower

frequency (such as the PFD input clocks). Not to be used with dc states on the status pins,

which occur when the settings of Register 0x231[5:0] are in the range of 000000 to 001111.

1: enabled.

0: disabled.

Enables a divide-by-4 on the STATUS0 pin, allowing dynamic signals to be viewed at a lower

frequency (such as the PFD input clocks). Not to be used with dc states on the status pins,

which occur when the settings of Register 0x230[5:0] are in the range of 000000 to 001111.

1: enable.

0: disable.

Reserved.

Set bit to put dividers in sync; clear bit to release. Functions like SYNC pin low.

1: sync.

0: normal.

Table 56. Power-Down Control

Address

0x233

Bits

[7:3]

2

Bit Name

Reserved

PLL1 power-down

1

PLL2 power-down

0

Distribution powerdown

Description

Reserved.

1: power-down (default).

0: normal operation.

1: power-down (default).

0: normal operation.

Powers down the distribution.

1: power-down (default).

0: normal operation.

Table 57. Update All Registers

Address

0x234

Bits

[7:1]

0

Bit Name

Reserved

IO_UPDATE

Description

Reserved.

This bit must be set to 1 to transfer the contents of the buffer registers into the active registers,

which happens on the next SCLK rising edge. This bit is self-clearing; that is, it does not have

to be set back to 0.

1 (self-clearing): update all active registers to the contents of the buffer registers.

EEPROM Buffer (Address 0xA00 to Address 0xA16)

Table 58. EEPROM Buffer Segment

Address

0xA00

to

0xA16

Bits

[7:0]

Bit Name

EEPROM Buffer

Segment Register 1 to

EEPROM Buffer

Segment Register 23

Description

The EEPROM buffer segment section stores the starting address and number of bytes that are

to be stored and read back to and from the EEPROM. Because the register space is noncontiguous,

the EEPROM controller needs to know the starting address and number of bytes in the register

space to store and retrieve from the EEPROM. In addition, there are special instructions for the

EEPROM controller: operational codes (that is, IO_UPDATE and end-of-data) that are also stored in

the EEPROM buffer segment. The on-chip default setting of the EEPROM buffer segment

registers is designed such that all registers are transferred to/from the EEPROM, and an IO_UPDATE

is issued after the transfer (see the Programming the EEPROM Buffer Segment section).

Rev. D | Page 58 of 60

�Data Sheet

AD9523

EEPROM Control (Address 0xB00 to Address 0xB03)

Table 59. STATUS_EEPROM

Address

0xB00

Bits

[7:1]

0

Bit Name

Reserved

STATUS_EEPROM

(read only)

Description

Reserved.

This read-only bit indicates the status of the data transferred between the EEPROM and the

buffer register bank during the writing and reading of the EEPROM. This signal is also

available at the STATUS0 pin when Register 0x232[4] is set.

0: data transfer is complete.

1: data transfer is not complete.

Table 60. EEPROM Error Checking Readback

Address

0xB01

Bits

[7:1]

0

Bit Name

Reserved

EEPROM data error

(read only)

Description

Reserved.

This read-only bit indicates an error during the data transfer between the EEPROM and the buffer.

0: no error; data is correct.

1: incorrect data detected.

Table 61. EEPROM Control 1

Address

0xB02

Bits

[7:2]

1

Bit Name

Reserved

SOFT_EEPROM

0

Enable EEPROM write

Description

Reserved.

When the EEPROM_SEL pin is tied low, setting the SOFT_EEPROM bit resets the AD9523 using

the settings saved in EEPROM.

1: soft reset with EEPROM settings (self-clearing).

Enables the user to write to the EEPROM.

0: EEPROM write protection is enabled. User cannot write to EEPROM (default).

1: EEPROM write protection is disabled. User can write to EEPROM.

Table 62. EEPROM Control 2

Address

0xB03

Bits

[7:1]

0

Bit Name

Reserved

REG2EEPROM

Description

Reserved.

Transfers data from the buffer register to the EEPROM (self-clearing).

1: setting this bit initiates the data transfer from the buffer register to the EEPROM (writing

process); it is reset by the I²C master after the data transfer is done.

Rev. D | Page 59 of 60

�AD9523

Data Sheet

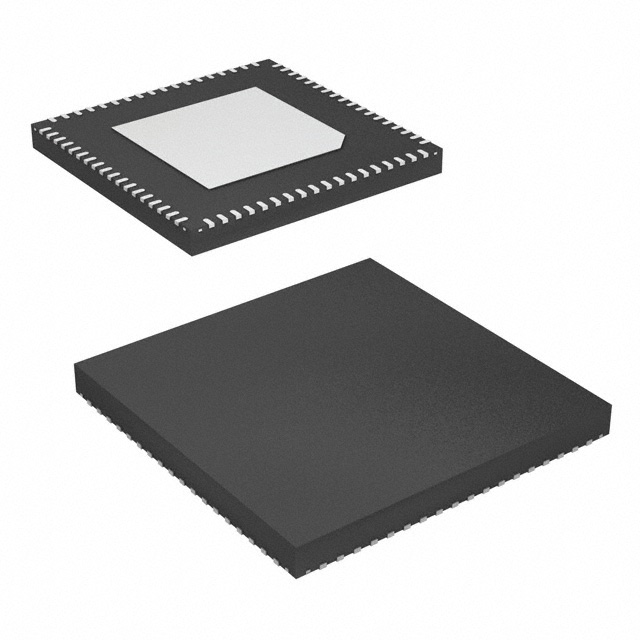

OUTLINE DIMENSIONS

10.10

10.00 SQ

9.90

0.60

0.42

0.24

0.60

0.42

0.24

0.30

0.23

0.18

55

54

72

1

PIN 1

INDICATOR

PIN 1

INDICATOR

9.85

9.75 SQ

9.65

0.50

BSC

0.50

0.40

0.30

18

37

BOTTOM VIEW

0.80 MAX

0.65 TYP

0.05 MAX

0.02 NOM

COPLANARITY

0.08

0.20 REF

SEATING

PLANE

0.25 MIN

8.50 REF

FOR PROPER CONNECTION OF

THE EXPOSED PAD, REFER TO

THE PIN CONFIGURATION AND

FUNCTION DESCRIPTIONS

SECTION OF THIS DATA SHEET.

COMPLIANT TO JEDEC STANDARDS MO-220-VNND-4

06-25-2012-C

12° MAX

19

36

TOP VIEW

1.00

0.85

0.80

5.45

5.30 SQ

5.15

EXPOSED

PAD

Figure 46. 72-Lead Lead Frame Chip Scale Package [LFCSP_VQ]

10 mm × 10 mm Body, Very Thin Quad

(CP-72-6)

Dimensions shown in millimeters

ORDERING GUIDE

Model1

AD9523BCPZ

AD9523BCPZ-REEL7

AD9523/PCBZ

1

Temperature Range

−40°C to +85°C

−40°C to +85°C

Package Description

72-Lead Lead Frame Chip Scale Package [LFCSP_VQ]

72-Lead Lead Frame Chip Scale Package [LFCSP_VQ]

Evaluation Board

Z = RoHS Compliant Part.

I2C refers to a communications protocol originally developed by Philips Semiconductors (now NXP Semiconductors).

©2010–2015 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D08439-0-9/15(D)

Rev. D | Page 60 of 60

Package Option

CP-72-6

CP-72-6

�