PIN CONNECTION DIAGRAMS

Input overvoltage protection, 32 V above and below the

supply rails

No phase reversal for input voltage up to ±32 V beyond the

power supply

Rail-to-rail input and output swing

Low power: 60 µA per amplifier typical

Unity-gain bandwidth

800 kHz typical at VSY = ±15 V

550 kHz typical at VSY = ±5 V

465 kHz typical at VSY = ±1.5 V

Single-supply operation: 3 V to 30 V

Low offset voltage: 300 µV maximum

Large signal voltage gain: 120 dB typical

Unity gain stable

Qualified for automotive applications

APPLICATIONS

OUTA 1

8

V+

–INA 2

ADA4096-2

7

OUTB

+INA 3

TOP VIEW

(Not to Scale)

6

–INB

5

+INB

V– 4

09241-001

FEATURES

Figure 1. 8-Lead, MSOP (RM-8), ADA4096-2

OUTA 1

8 V+

–INA 2

ADA4096-2

7 OUTB

+INA 3

TOP VIEW

(Not to Scale)

6 –INB

5 +INB

V– 4

NOTES

1. CONNECT THE EXPOSED PAD

TO V–.

09241-002

Data Sheet

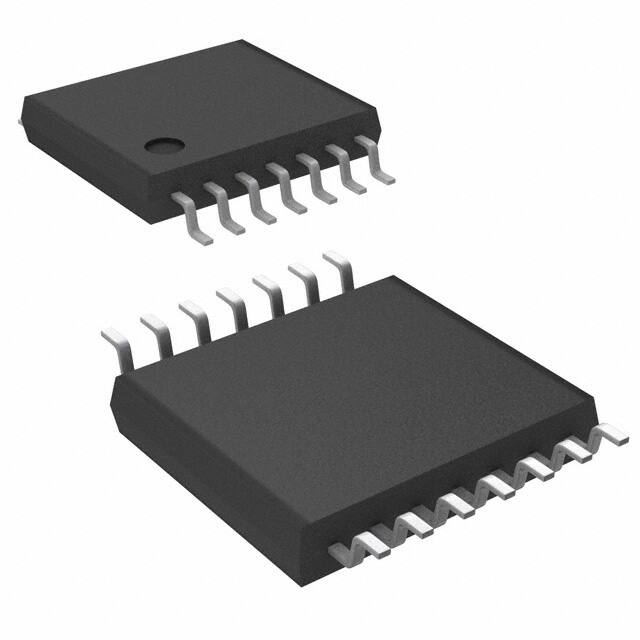

30 V, Micropower, Overvoltage Protection,

Rail-to-Rail Input/Output Amplifiers

ADA4096-2/ADA4096-4

Figure 2. 8-Lead LFCSP (CP-8-10), ADA4096-2

Note: For the ADA4096-4, see the Pin Configurations and

Function Descriptions section.

Battery monitoring

Sensor conditioners

Portable power supply controls

Portable instrumentation

GENERAL DESCRIPTION

T

The ADA4096-2 and ADA4096-4 have overvoltage protection

inputs and diodes that allow the voltage input to extend 32 V

above and below the supply rails, making this device ideal for

robust industrial applications. The ADA4096-2 and ADA4096-4

feature a unique input stage that allows the input voltage to

exceed either supply safely without any phase reversal or latchup; this is called overvoltage protection, or OVP.

The dual ADA4096-2 is available in 8-lead LFCSP (2 mm ×

2 mm) and 8-lead MSOP packages. The ADA4096-2 is available

in 16-lead LFCSP (3 mm × 3 mm) and 14-lead TSSOP

packages. The ADA4096-2W is qualified for automotive

applications and is available in an 8-lead MSOP package.

Rev. G

1

CH1 10.0V

CH2 10.0V

M2.00ms

T 34.20%

A CH1

–3.6V

09241-146

The ADA4096-2 dual and ADA4096-4 quad operational

amplifiers feature micropower operation and rail-to-rail input

and output ranges. The extremely low power requirements and

guaranteed operation from 3 V to 30 V make these amplifiers

perfectly suited to monitor battery usage and to control battery

charging. Their dynamic performance, including 27 nV/√Hz

voltage noise density, recommends them for battery-powered

audio applications. Capacitive loads to 200 pF are handled

without oscillation.

Figure 3. No Phase Reversal

The ADA4096-2 family is specified over the extended industrial

temperature range of (−40°C to +125°C) and is part of the

growing selection of 30 V, low power op amps from Analog

Devices, Inc. (see Table 1).

Table 1. Low Power, 30 V Operational Amplifiers

Op Amp

Dual

Quad

Rail-to-Rail I/O

ADA4091-2

ADA4091-4

PJFET

AD8682

AD8684

Low Noise

AD8622

AD8624

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2011–2017 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

�ADA4096-2/ADA4096-4

Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

±1.5 V Characteristics ............................................................... 10

Applications ....................................................................................... 1

±5 V Characteristics................................................................... 13

Pin Connection Diagrams ............................................................... 1

±15 V Characteristics ................................................................ 16

General Description ......................................................................... 1

Comparative Voltage and Variable Voltage Graphs ............... 19

Revision History ............................................................................... 3

Theory of Operation ...................................................................... 20

Specifications..................................................................................... 4

Input Stage ................................................................................... 20

Electrical Specifications, VSY = ±1.5 V....................................... 4

Phase Inversion ........................................................................... 20

Electrical Specifications, VSY = ±5 V .......................................... 5

Input Overvoltage Protection ................................................... 21

Electrical Specifications, VSY = ±15 V........................................ 6

Comparator Operation .............................................................. 21

Absolute Maximum Ratings ............................................................ 7

Outline Dimensions ....................................................................... 22

Thermal Resistance ...................................................................... 7

Ordering Guide .......................................................................... 24

ESD Caution .................................................................................. 7

Automotive Products ................................................................. 24

Pin Configurations and Function Descriptions ........................... 8

Typical Performance Characteristics ........................................... 10

Rev. G | Page 2 of 25

�Data Sheet

ADA4096-2/ADA4096-4

REVISION HISTORY

9/2017—Rev. F to Rev. G

Changed ADA409x to ADA4096-2 ............................ Throughout

Changed CP-16-27 to CP-16-22 .................................. Throughout

Changes to Figure 12 and Figure 13 .............................................10

Changes to Figure 26 ......................................................................13

Changes to Figure 39 ......................................................................16

Updated Outline Dimensions ........................................................22

Changes to Ordering Guide ...........................................................24

12/2014—Rev. E to Rev. F

Changes to EPAD Note, Figure 2 .................................................... 1

Changes to EPAD Note, Figure 5 and Table 7 ............................... 7

Changes to EPAD Note, Figure 7 and Table 8 ............................... 8

3/2014—Rev. D to Rev. E

Changes to Figure 10 and Figure 12 ............................................... 9

Changes to Figure 23 and Figure 25 .............................................12

Changes to Figure 36 and Figure 38 .............................................15

5/2013—Rev. C to Rev. D

Changes to Pin Connection Diagrams Section ............................. 1

Changes to Pin Configurations and Function Descriptions

Section ................................................................................................ 7

Added Figure 10, Renumbered Sequentially ................................. 9

Added Figure 23 ..............................................................................12

Added Figure 36 ..............................................................................15

8/2012—Rev. B to Rev. C

Changes to Table 8 ............................................................................ 8

8/2012—Rev. A to Rev. B

Added ADA4096-4 ............................................................ Universal

Changes to Features Section ............................................................ 1

Added Figure 3 .................................................................................. 1

Changes to Pin Connection Diagrams Section ............................. 1

Changes to Input Bias Current, Common-Mode Rejection

Ratio, Large Signal Voltage Gain, and Supply Current per

Amplifier Parameters, and −3 dB Closed-Loop Bandwidth

Symbol, Table 2 .................................................................................. 3

Changes to Input Bias Current, Common-Mode Rejection

Ratio, Large Signal Voltage Gain, and Parameters, and −3 dB

Closed-Loop Bandwidth Symbol, Table 3 ..................................... 4

Changes to Input Bias Current, Common-Mode Rejection

Ratio, Large Signal Voltage Gain, Output Voltage High, and

Output Voltage Low Parameters, and −3 dB Closed-Loop

Bandwidth Symbol, Table 4 ............................................................. 5

Changes to Table 6 ............................................................................ 7

Added Pin Configurations and Function Descriptions

Section ................................................................................................ 8

Added Figure 4 and Figure 5, Renumbered Sequentially ............ 8

Added Table 7, Renumbered Sequentially ..................................... 8

Added Figure 6, Figure 7, and Table 8 ............................................ 9

Updated Outline Dimensions........................................................ 18

Changes to Ordering Guide ........................................................... 20

3/2012—Rev. 0 to Rev. A

Changed −3 dB Closed-Loop Bandwidth from 97 kHz to

970 kHz, Table 2 ................................................................................ 3

Changed −3 dB Closed-Loop Bandwidth from 114 kHz to

1140 kHz, Table 3 .............................................................................. 4

Changed to −3 dB Closed-Loop Bandwidth from 152 kHz to

1520 kHz, Table 4 .............................................................................. 5

Updated Outline Dimensions........................................................ 18

7/2011—Revision 0: Initial Version

Rev. G | Page 3 of 25

�ADA4096-2/ADA4096-4

Data Sheet

SPECIFICATIONS

ELECTRICAL SPECIFICATIONS, VSY = ±1.5 V

VSY = ±1.5 V, VCM = VSY/2, TA = 25°C, unless otherwise noted.

Table 2.

Parameter

INPUT CHARACTERISTICS

Offset Voltage

Offset Voltage Drift

Input Bias Current

Symbol

Test Conditions/Comments

Min

VOS

∆VOS/∆T

IB

0°C ≤ TA ≤ +125°C

−40°C ≤ TA ≤ +125°C

−40°C ≤ TA ≤ +125°C

Typ

Max

Unit

35

300

450

900

µV

µV

µV

µV/°C

nA

nA

nA

nA

V

dB

dB

dB

dB

dB

dB

1

±10

−40°C ≤ TA ≤ +125°C

Input Offset Current

IOS

±0.1

−40°C ≤ TA ≤ +125°C

Input Voltage Range

Common-Mode Rejection Ratio

CMRR

Large Signal Voltage Gain

AVO

MATCHING CHARACTERISTICS

Offset Voltage

OUTPUT CHARACTERISTICS

Output Voltage High

Output Voltage Low

Short-Circuit Limit

Closed-Loop Impedance

POWER SUPPLY

Power Supply Rejection Ratio

Supply Current per Amplifier

DYNAMIC PERFORMANCE

Slew Rate

Gain Bandwidth Product

Unity-Gain Crossover

Phase Margin

−3 dB Closed-Loop Bandwidth

NOISE PERFORMANCE

Voltage Noise

Voltage Noise Density

Current Noise Density

VCM = 0 V to ±1.5 V

−40°C ≤ TA ≤ +125°C

RL = 10 kΩ, VO = −1.4 V to +1.4 V

−40°C ≤ TA ≤ +125°C

RL = 2 kΩ, VO = −1.3 V to +1.3 V

−40°C ≤ TA ≤ +125°C

−1.5

61

58

91

84

86

77

TA = 25°C

VOH

VOL

ISC

ZOUT

PSRR

ISY

SR

GBP

UGC

ΦM

f−3 dB

en p-p

en

in

1.48

1.45

1.45

1.40

VSY = 3 V to 36 V

−40°C ≤ TA ≤ +125°C

VO = VSY/2

−40°C ≤ TA ≤ +125°C

100

90

RL = 100 kΩ, CL = 30 pF

VIN = 5 mV p-p, RL = 10 kΩ, AV = 100

VIN = 5 mV p-p, RL = 10 kΩ, AV = 1

77

94

92

100

RL = 10 kΩ to GND

−40°C ≤ TA ≤ +125°C

RL = 2 kΩ to GND

−40°C to +125°C

RL = 10 kΩ to GND

−40°C ≤ TA ≤ +125°C

RL = 2 kΩ to GND

−40°C ≤ TA ≤ +125°C

Source/sink

f = 100 kHz, AV = 1

±25

±30

±1.5

±3

+1.5

300

1.49

1.46

−1.49

−1.48

−1.48

−1.45

−1.47

−1.40

±10

102

40

50

80

µV

V

V

V

V

V

V

V

V

mA

Ω

dB

dB

µA

µA

AV = 1, VIN = 5 mV p-p

0.25

501

465

51

970

V/µs

kHz

kHz

Degrees

kHz

0.1 Hz to 10 Hz

f = 1 kHz

f = 1 kHz

0.7

27

0.2

µV p-p

nV/√Hz

pA/√Hz

Rev. G | Page 4 of 25

�Data Sheet

ADA4096-2/ADA4096-4

ELECTRICAL SPECIFICATIONS, VSY = ±5 V

VSY = ±5 V, VCM = VSY/2, TA = 25°C, unless otherwise noted.

Table 3.

Parameter

INPUT CHARACTERISTICS

Offset Voltage

Symbol

Test Conditions/Comments

Min

VOS

Typ

Max

Unit

35

300

500

µV

µV

µV/°C

nA

nA

nA

nA

V

dB

dB

dB

dB

dB

dB

dB

dB

−40°C ≤ TA ≤ +125°C

Offset Voltage Drift

Input Bias Current

∆VOS/∆T

IB

1

±10

−40°C ≤ TA ≤ +125°C

Input Offset Current

IOS

±1.5

−40°C ≤ TA ≤ +125°C

Input Voltage Range

Common-Mode Rejection Ratio

Large Signal Voltage Gain

MATCHING CHARACTERISTICS

Offset Voltage

OUTPUT CHARACTERISTICS

Output Voltage High

Output Voltage Low

Short-Circuit Limit

Closed-Loop Impedance

POWER SUPPLY

Power Supply Rejection Ratio

Supply Current per Amplifier

DYNAMIC PERFORMANCE

Slew Rate

Gain Bandwidth Product

Unity-Gain Crossover

Phase Margin

−3 dB Closed-Loop Bandwidth

NOISE PERFORMANCE

Voltage Noise

Voltage Noise Density

Current Noise Density

CMRR

AVO

VCM = −5 V to +5 V

−40°C ≤ TA ≤ +125°C

VCM = −3 V to +3 V

−40°C ≤ TA ≤ +125°C

RL = 10 kΩ, VO = ±4.8 V

−40°C ≤ TA ≤ +125°C

RL = 2 kΩ, VO = ±4.7 V

−40°C ≤ TA ≤ +125°C

−5

72

68

91

85

102

99

93

88

TA = 25°C

VOH

VOL

ISC

ZOUT

PSRR

ISY

4.96

4.95

4.80

4.70

VSY = 3 V to 36 V

−40°C ≤ TA ≤ +125°C

VO = VSY/2

−40°C ≤ TA ≤ +125°C

100

90

SR

GBP

UGC

ΦM

f−3 dB

RL = 100 kΩ, CL = 30 pF

VIN = 5 mV p-p, RL = 10 kΩ, AV = 100

VIN = 5 mV p-p, RL = 10 kΩ, AV = 1

en p-p

en

in

86

103

111

103

100

RL = 10 kΩ to GND

−40°C ≤ TA ≤ +125°C

RL = 2 kΩ to GND

−40°C ≤ TA ≤ +125°C

RL = 10 kΩ to GND

−40°C ≤ TA ≤ +125°C

RL = 2 kΩ to GND

−40°C ≤ TA ≤ +125°C

Source/sink

f = 100 kHz, AV = 1

±25

±30

±2

±3

+5

300

4.97

4.90

−4.98

−4.90

−4.97

−4.95

−4.80

−4.75

±10

71

47

55

75

µV

V

V

V

V

V

V

V

V

mA

Ω

dB

dB

µA

µA

AV = 1, VIN = 5 mV p-p

0.3

595

550

52

1140

V/µs

kHz

kHz

Degrees

kHz

0.1 Hz to 10 Hz

f = 1 kHz

f = 1 kHz

0.7

27

0.2

µV p-p

nV/√Hz

pA/√Hz

Rev. G | Page 5 of 25

�ADA4096-2/ADA4096-4

Data Sheet

ELECTRICAL SPECIFICATIONS, VSY = ±15 V

VSY = ±15 V, VCM = VSY/2, VO = 0.0 V, TA = 25°C, unless otherwise noted.

Table 4.

Parameter

INPUT CHARACTERISTICS

Offset Voltage

Symbol

Offset Voltage Drift

Input Bias Current

∆VOS/∆T

IB

Test Conditions/Comments

Min

VOS

Typ

Max

Unit

35

300

500

µV

µV

µV/°C

nA

nA

nA

nA

V

dB

dB

dB

dB

dB

dB

dB

dB

−40°C ≤ TA ≤ +125°C

1

±3

−40°C ≤ TA ≤ +125°C

Input Offset Current

IOS

±0.1

−40°C ≤ TA ≤ +125°C

Input Voltage Range

Common-Mode Rejection Ratio

Large Signal Voltage Gain

Input Capacitance

Differential Mode

Common Mode

MATCHING CHARACTERISTICS

Offset Voltage

OUTPUT CHARACTERISTICS

Output Voltage High

Output Voltage Low

Short-Circuit Limit

Closed-Loop Impedance

POWER SUPPLY

Power Supply Rejection Ratio

Supply Current per Amplifier

DYNAMIC PERFORMANCE

Slew Rate

Settling Time

Gain Bandwidth Product

Unity-Gain Crossover

Phase Margin

−3 dB Closed-Loop Bandwidth

Channel Separation

NOISE PERFORMANCE

Voltage Noise

Voltage Noise Density

Current Noise Density

CMRR

AVO

VCM = −15 V to +15 V

−40°C ≤ TA ≤ +125°C

VCM = −13 V to +13 V

−40°C ≤ TA ≤ +125°C

RL = 10 kΩ, VO = ±14.7 V

−40°C ≤ TA ≤ +125°C

RL = 2 kΩ, VO = ±11 V

−40°C ≤ TA ≤ +125°C

−15

81

75

95

89

109

105

99

90

CDM

CCM

VOL

ISC

ZOUT

PSRR

ISY

95

107

120

112

2.5

7

TA = 25°C

VOH

±25

±30

±1.5

±3

+15

100

RL = 10 kΩ to GND

−40°C ≤ TA ≤ +125°C

RL = 2 kΩ to GND

−40°C ≤ TA ≤ +125°C

RL = 10 kΩ to GND

−40°C ≤ TA ≤ +125°C

RL = 2 kΩ to GND

−40°C ≤ TA ≤ +125°C

Source/sink

f = 100 kHz, AV = 1

14.92

14.90

14.0

11.0

VSY = 3 V to 36 V

−40°C ≤ TA ≤ +125°C

VO = VSY/2

−40°C ≤ TA ≤ +125°C

100

90

SR

tS

GBP

UGC

ΦM

f−3 dB

CS

RL = 100 kΩ, CL = 30 pF

To 0.1%, 10 V step

VIN = 5 mV p-p, RL = 10 kΩ, AV = 100

VIN = 5 mV p-p, RL = 10 kΩ, AV = 1

en p-p

en

in

pF

pF

300

14.94

14.3

−14.96

−14.75

−14.80

−14.75

−14.60

−14.0

±10

40

60

75

100

µV

V

V

V

V

V

V

V

V

mA

Ω

dB

dB

µA

µA

AV = 1, VIN = 5 mV p-p

f = 1 kHz

0.4

23.4

786

800

60

1520

100

V/µ

µs

kHz

kHz

Degrees

kHz

dB

0.1 Hz to 10 Hz

f = 1 kHz

f = 1 kHz

0.7

27

0.2

µV p-p

nV/√Hz

pA/√Hz

Rev. G | Page 6 of 25

�Data Sheet

ADA4096-2/ADA4096-4

ABSOLUTE MAXIMUM RATINGS

THERMAL RESISTANCE

Table 5.

Parameter

Supply Voltage

Input Voltage

Operating Condition

Overvoltage Condition1

Differential Input Voltage2

Input Current

Output Short-Circuit Duration to

GND

Storage Temperature Range

Operating Temperature Range

Junction Temperature Range

Lead Temperature (Soldering,

60 seconds)

1

2

θJA is specified for the device soldered on a 4-layer JEDEC

standard printed circuit board (PCB) with zero airflow. The

exposed pad is soldered to the application board.

Rating

36 V

−V ≤ VIN ≤ +V

(−V) − 32 V ≤ VIN ≤ (+V) + 32 V

±VSY

±5 mA

Indefinite

−65°C to +150°C

−40°C to +125°C

−65°C to +150°C

300°C

Table 6. Thermal Resistance

Package Type

8-Lead MSOP (RM-8)

8-Lead LFCSP (CP-8-10)

14-Lead TSSOP (RU-14)

16-Lead LFCSP (CP-16-22)

ESD CAUTION

Performance not guaranteed during overvoltage conditions.

Limit the input current to ±5 mA.

Stresses at or above those listed under Absolute Maximum

Ratings may cause permanent damage to the product. This is a

stress rating only; functional operation of the product at these

or any other conditions above those indicated in the operational

section of this specification is not implied. Operation beyond

the maximum operating conditions for extended periods may

affect product reliability.

Rev. G | Page 7 of 25

θJA

142

76

112

75

θJC

45

43

35

12

Unit

°C/W

°C/W

°C/W

°C/W

�ADA4096-2/ADA4096-4

Data Sheet

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

7

OUTB

+INA 3

TOP VIEW

(Not to Scale)

6

–INB

5

+INB

V– 4

OUTA 1

8 V+

–INA 2

ADA4096-2

7 OUTB

+INA 3

TOP VIEW

(Not to Scale)

6 –INB

V– 4

5 +INB

NOTES

1. CONNECT THE EXPOSED PAD

TO V–.

09241-202

V+

ADA4096-2

09241-201

8

–INA 2

OUTA 1

Figure 5. 8-Lead LFCSP (CP-8-10), ADA4096-2

Figure 4. 8-Lead, MSOP (RM-8), ADA4096-2

Table 7. Pin Function Descriptions, ADA4096-2

Pin No. 1

8-Lead MSOP 8-Lead LFCSP

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

N/A

EP 2

1

2

Mnemonic

OUTA

−INA

+INA

V−

+INB

−INB

OUTB

V+

EPAD

Description

Output Channel A.

Negative Input Channel A.

Positive Input Channel A.

Negative Supply Voltage.

Positive Input Channel B.

Negative Input Channel B.

Output Channel B.

Positive Supply Voltage.

Exposed Pad.2 For the ADA4096-2 (8-lead LFCSP only), connect the exposed pad to V−.

N/A means not applicable.

The exposed pad is not shown in the pin configuration diagram.

Rev. G | Page 8 of 25

�+INA

3

ADA4096-4

12

+IND

V+

4

TOP VIEW

(Not to Scale)

11

V–

+INB

5

10

+INC

–INB

6

9

–INC

OUTB

7

8

OUTC

13 NIC

–INA 1

+INA 2

12 –IND

ADA4096-4

TOP

VIEW

V+ 3

11 +IND

10 V–

9

+INB 4

+INC

NOTES

1. NIC = NOT INTERNALLY CONNECTED.

2. CONNECT THE EXPOSED PAD TO V–.

09241-103

–IND

–INC 8

OUTD

OUTC 7

14

13

–INB 5

2

OUTB 6

–INA

09241-101

OUTA 1

14 OUTD

16 NIC

ADA4096-2/ADA4096-4

15 OUTA

Data Sheet

Figure 7. 16-Lead LFCSP (CP-16-22), ADA4096-4

Figure 6. 14-Lead TSSOP (RU-14), ADA4096-4

Table 8. Pin Function Descriptions, ADA4096-4

Pin No.1

14-Lead TSSOP

16-Lead LFCSP

1

15

2

1

3

2

4

3

5

4

6

5

7

6

8

7

9

8

10

9

11

10

12

11

13

12

14

14

N/A

13

N/A

16

N/A

EP2

1

2

Mnemonic

OUTA

−INA

+INA

V+

+INB

−INB

OUTB

OUTC

−INC

+INC

V−

+IND

−IND

OUTD

NIC

NIC

EPAD

Description

Output Channel A.

Negative Input Channel A.

Positive Input Channel A.

Positive Supply Voltage.

Positive Input Channel B.

Negative Input Channel B.

Output Channel B.

Output Channel C.

Negative Input Channel C.

Positive Input Channel C.

Negative Supply Voltage.

Positive Input Channel D.

Negative Input Channel D.

Output Channel D.

No Internal Connection.

No Internal Connection.

Exposed Pad.2 For the ADA4096-4 (16-lead LFCSP only), connect the exposed pad to V−.

N/A means not applicable.

The exposed pad is not shown in the pin configuration diagram.

Rev. G | Page 9 of 25

�ADA4096-2/ADA4096-4

Data Sheet

TYPICAL PERFORMANCE CHARACTERISTICS

TA = 25°C, unless otherwise noted. All typical performance characteristics shown are for the ADA4096-2 only.

±1.5 V CHARACTERISTICS

30

180

160

20

140

10

120

TA = +25°C

100

80

TA = +85°C

–10

TA = 0°C

60

–20

40

–30

0

–0.5

1.5

1.0

0.5

VCM (V)

Figure 8. Input Offset Voltage (VOS) Distribution

Figure 11. Input Bias Current (IB) vs. VCM for Various Temperatures

25

10k

20

15

10

5

1.0

1.5

2.0

2.5

SOURCING

TCVOS (µV/°C)

SINKING

10

1

0.001

0.01

0.1

1

10

LOAD CURRENT (mA)

Figure 9. Offset Voltage Drift (TCVOS) Distribution

Figure 12. Output Voltage to Supply Rail vs. Load Current

800

100

80

400

60

200

40

GAIN (dB)

600

0

225

ADA4096-2

VSY = ±1.5V

TA = 25°C

180

135

90

PHASE

20

45

GAIN

–200

0

–400

–20

–45

–40

–90

VSY = ±1.5V

10 CHANNELS

–800

–1.5 –1.3 –1.0 –0.8 –0.5 –0.3

09241-210

–600

0

0.3

0.5

0.8

1.0

1.3

1.5

–60

100

VCM (V)

0

1k

10k

100k

1M

–135

10M

FREQUENCY (Hz)

Figure 10. Input Offset Voltage (VOS) vs. Common-Mode Voltage (VCM)

Rev. G | Page 10 of 25

Figure 13. Open-Loop Gain and Phase vs. Frequency

PHASE (Degrees)

0.5

100

09241-007

0

1k

09241-004

0

–2.5 –2.0 –1.5 –1.0 –0.5

ADA4096-2

VSY = ±1.5V

TA = 25°C

09241-006

OUTPUT VOLTAGE TO SUPPLY RAIL (mV)

ADA4096-2

VSY = ±1.5V

TA = –40°C TO +125°C

NUMBER OF AMPLIFIERS

TA = –40°C

–1.0

09241-005

VOS (µV)

–40

–1.5

09241-003

200

MORE

175

150

125

75

100

50

0

25

–25

–50

–75

–100

–125

–150

–200

0

–175

20

VOS (µV)

TA = +125°C

0

IB (nA)

NUMBER OF AMPLIFIERS

ADA4096-2

VSY = ±1.5V

ADA4096-2

VSY = ±1.5V

TA = 25°C

�Data Sheet

ADA4096-2/ADA4096-4

50

120

ADA4096-2

VSY = ±1.5V

TA = 25°C

G = +100

40

ADA4096-2

VSY = ±1.5V

TA = 25°C

100

G = +10

80

20

PSRR+

10

PSRR (dB)

CLOSED-LOOP GAIN (dB)

30

G = +1

0

–10

–20

60

PSRR–

40

20

–30

0

100

1k

10k

100k

1M

10M

FREQUENCY (Hz)

–20

10

09241-008

–50

10

100

10k

100k

1M

10M

FREQUENCY (Hz)

Figure 14. Closed-Loop Gain vs. Frequency

Figure 16. PSRR vs. Frequency

10k

1k

1k

09241-052

–40

2.0

ADA4096-2

VSY = ±1.5V

TA = 25°C

ADA4096-2

VSY = ±1.5V

TA = 25°C

RL = 10kΩ

CL = 100pF

G = +1

1.5

1.0

0.5

VOUT (V)

G = +100

10

G = +10

0

–0.5

1

–1.0

G = +1

0.1

0.01

10

100

1k

10k

100k

1M

FREQUENCY (Hz)

10M

Figure 15. Output Impedance (ZOUT) vs. Frequency

–2.0

0

20

40

60

80

100

TIME (µs)

Figure 17. Large Signal Transient Response

Rev. G | Page 11 of 25

120

09241-010

–1.5

09241-009

ZOUT (Ω)

100

�ADA4096-2/ADA4096-4

Data Sheet

0.08

0.2

ADA4096-2

VSY = ±1.5V

TA = 25°C

RL = 10kΩ

CL = 100pF

G = +1

0.06

0.04

–0.2

–0.4

–0.02

–0.6

–0.8

–0.04

–1.0

–0.06

–1.2

–0.08

–1.4

–0.10

0

5

10

15

20

25

30

TIME (µs)

Figure 18. Small Signal Transient Response

ADA4096-2

VSY = ±1.5V

TA = 25°C

RF = 10kΩ

RS = 100Ω

1.2

1.0

0.8

0.6

0.4

0

20

40

60

80

TIME (µs)

100

09241-055

0.2

0

0

20

40

60

80

TIME (µs)

Figure 20. Negative Overload Recovery

1.6

1.4

–1.6

Figure 19. Positive Overload Recovery

Rev. G | Page 12 of 25

100

09241-056

VOUT (V)

0

09241-011

VOUT (V)

0.02

VOUT (V)

ADA4096-2

VSY = ±1.5V

TA = 25°C

RF = 10kΩ

RS = 100Ω

0

�Data Sheet

ADA4096-2/ADA4096-4

±5 V CHARACTERISTICS

30

250

ADA4096-2

VSY = ±5V

TA = 25°C

20

ADA4096-2

VSY = ±5V

10

TA = +125°C

0

150

IB (nA)

NUMBER OF AMPLIFIERS

200

TA = +85°C

–10

100

–20

TA = +25°C

–30

50

TA = 0°C

–40

–2

–1

0

1

2

3

4

5

Figure 24. Input Bias Current (IB) vs. VCM for Various Temperatures

10k

OUTPUT VOLTAGE TO SUPPLY RAIL (mV)

ADA4096-2

V = ±5V

35 T SY= –40°C TO +125°C

A

30

25

20

15

10

5

1.0

1.5

2.0

2.5

SOURCING

TCVOS (µV/°C)

SINKING

10

1

0.001

0.01

0.1

1

10

100

LOAD CURRENT (mA)

Figure 22. Offset Voltage Drift (TCVOS) Distribution

Figure 25. Output Voltage to Supply Rail vs. Load Current

800

100

VSY = ±5V

10 CHANNELS

600

225

ADA4096-2

VSY = ±5V

TA = 25°C

80

60

200

40

GAIN (dB)

400

0

180

135

90

PHASE

45

20

GAIN

0

–400

–20

–45

–600

–40

–90

–800

–5

09241-223

–200

–4

–3

–2

–1

0

1

2

3

4

5

–60

100

VCM (V)

0

1k

10k

100k

1M

–135

10M

FREQUENCY (Hz)

Figure 23. Input Offset Voltage (VOS) vs. Common-Mode Voltage (VCM)

Rev. G | Page 13 of 25

Figure 26. Open-Loop Gain and Phase vs. Frequency

PHASE (Degrees)

0.5

100

09241-020

0

1k

09241-016

0

–2.5 –2.0 –1.5 –1.0 –0.5

ADA4096-2

VSY = ±5V

TA = 25°C

09241-023

40

NUMBER OF AMPLIFIERS

–3

VCM (V)

Figure 21. Input Offset Voltage (VOS) Distribution

VOS (µV)

–4

09241-050

–50

–5

09241-015

200

VOS (µV)

MORE

175

150

125

75

100

50

0

25

–25

–50

–75

–100

–125

–150

–200

–175

TA = –40°C

0

�ADA4096-2/ADA4096-4

Data Sheet

50

140

ADA4096-2

VSY = ±5V

TA = 25°C

G = +100

40

ADA4096-2

VSY = ±5V

TA = 25°C

120

100

G = +10

20

10

PSRR (dB)

CLOSED-LOOP GAIN (dB)

30

G = +1

0

–10

80

PSRR+

60

PSRR–

40

–20

20

–30

100

1k

10k

100k

1M

10M

FREQUENCY (Hz)

–20

10

09241-024

–50

10

100

100k

1M

10M

Figure 29. PSRR vs. Frequency

10k

6

ADA4096-2

VSY = ±5V

TA = 25°C

ADA4096-2

VSY = ±5V

TA = 25°C

RL = 10kΩ

CL = 100pF

G = +1

4

100

2

VOUT (V)

G = +100

10

0

G = +10

1

–2

G = +1

0.1

100

1k

10k

100k

1M

FREQUENCY (Hz)

10M

Figure 28. Output Impedance (ZOUT) vs. Frequency.

–6

0

50

100

150

200

250

300

350

TIME (µs)

Figure 30. Large Signal Transient Response

Rev. G | Page 14 of 25

400

09241-017

0.01

10

–4

09241-021

ZOUT (Ω)

10k

FREQUENCY (Hz)

Figure 27. Closed-Loop Gain vs. Frequency

1k

1k

09241-053

0

–40

�Data Sheet

ADA4096-2/ADA4096-4

0.08

1

ADA4096-2

VSY = ±5V

TA = 25°C

RL = 10kΩ

CL = 100pF

G = +1

0.06

0.04

0

–1

VOUT (V)

0.02

VOUT (V)

ADA4096-2

VSY = ±5V

TA = 25°C

RF = 10kΩ

RS = 100Ω

0

–0.02

–2

–3

–0.04

–0.06

–4

0

5

10

15

20

25

30

TIME (µs)

Figure 31. Small Signal Transient Response

ADA4096-2

VSY = ±5V

TA = 25°C

RF = 10kΩ

RS = 100Ω

3

2

1

0

20

40

60

80

TIME (µs)

100

09241-057

VOUT (V)

4

0

0

20

40

60

80

TIME (µs)

Figure 33. Negative Overload Recovery

6

5

–5

Figure 32. Positive Overload Recovery

Rev. G | Page 15 of 25

100

09241-058

–0.10

09241-018

–0.08

�ADA4096-2/ADA4096-4

Data Sheet

±15 V CHARACTERISTICS

40

250

ADA4096-2

30 VSY = ±15V

ADA4096-2

VSY = ±15V

TA = 25°C

20

TA = +125°C

10

TA = +85°C

0

150

IB (nA)

–10

100

–20

TA = +25°C

TA = 0°C

–30

50

–40

0

5

10

15

09241-051

–5

Figure 37. Input Bias Current (IB) vs. VCM for Various Temperatures

10k

OUTPUT VOLTAGE TO SUPPLY RAIL (mV)

ADA4096-2

VSY = ±15V

30 TA = –40°C TO +125°C

25

20

15

10

5

0.5

1.0

1.5

2.0

2.5

100

SOURCING

TCVOS (µV/°C)

SINKING

10

1

0.001

0.01

0.1

1

10

100

LOAD CURRENT (mA)

Figure 35. Offset Voltage Drift (TCVOS) Distribution

Figure 38. Output Voltage to Supply Rail vs. Load Current

800

225

100

VSY = ±15V

10 CHANNELS

600

ADA4096-2

VSY = ±15V

TA = 25°C

80

60

200

40

GAIN (dB)

400

0

180

135

90

PHASE

45

20

GAIN

0

–400

–20

–45

–600

–40

–90

–800

–15

09241-236

–200

–12

–9

–6

–3

0

3

6

9

12

15

–60

100

VCM (V)

0

1k

10k

100k

1M

–135

10M

FREQUENCY (Hz)

Figure 36. Input Offset Voltage (VOS) vs. Common-Mode Voltage (VCM)

Rev. G | Page 16 of 25

Figure 39. Open-Loop Gain and Phase vs. Frequency

PHASE (Degrees)

0

1k

09241-028

0

–2.5 –2.0 –1.5 –1.0 –0.5

ADA4096-2

VSY = ±15V

TA = 25°C

09241-034

35

NUMBER OF AMPLIFIERS

–10

VCM (V)

Figure 34. Input Offset Voltage (VOS) Distribution

VOS (µV)

TA = –40°C

–60

–15

09241-027

200

VOS (µV)

MORE

175

150

125

75

100

50

0

25

–25

–50

–75

–100

–125

–150

–200

–175

–50

0

09241-030

NUMBER OF AMPLIFIERS

200

�Data Sheet

ADA4096-2/ADA4096-4

50

120

ADA4096-2

VSY = ±15V

TA = 25°C

G = +100

ADA4096-2

VSY = ±15V

TA = 25°C

100

30

80

G = +10

PSRR+

20

PSRR (dB)

10

G = +1

0

60

PSRR–

40

–10

20

–20

100

1k

10k

100k

1M

10M

FREQUENCY (Hz)

–20

10

09241-036

–40

10

100

10M

ADA4096-2

VSY = ±15V

TA = 25°C

RL = 10kΩ

CL = 100pF

G = +1

10

VOUT (V)

5

G = +100

G = +10

0

–5

G = +1

0.1

0.01

10

–10

100

1k

10k

100k

1M

FREQUENCY (Hz)

10M

09241-035

ZOUT (Ω)

1M

15

ADA4096-2

VSY = ±15V

TA = 25°C

100

1

100k

Figure 42. PSRR vs. Frequency

10k

10

10k

FREQUENCY (Hz)

Figure 40. Closed-Loop Gain vs. Frequency

1k

1k

09241-054

0

–30

–15

0

50

100

150

200

250

300

350

TIME (µs)

Figure 43. Large Signal Transient Response

Figure 41. Output Impedance (ZOUT) vs. Frequency

Rev. G | Page 17 of 25

400

09241-031

CLOSED-LOOP GAIN (dB)

40

�ADA4096-2/ADA4096-4

Data Sheet

0.08

0

ADA4096-2

VSY = ±15V

TA = 25°C

RL = 10kΩ

CL = 100pF

G = +1

0.06

0.04

ADA4096-2

VSY = ±15V

TA = 25°C

RF = 10kΩ

RS = 100Ω

–2

–4

0.02

VOUT (V)

VOUT (V)

–6

0

–0.02

–8

–10

–0.04

–12

–0.06

0

5

10

15

20

25

30

TIME (µs)

09241-032

–0.10

Figure 44. Small Signal Transient Response

ADA4096-2

VSY = ±15V

TA = 25°C

RF = 10kΩ

RS = 100Ω

12

8

6

4

2

0

20

40

60

80

TIME (µs)

100

09241-059

VOUT (V)

10

0

0

20

40

60

80

TIME (µs)

Figure 46. Negative Overload Recovery

16

14

–16

Figure 45. Positive Overload Recovery

Rev. G | Page 18 of 25

100

09241-060

–14

–0.08

�Data Sheet

ADA4096-2/ADA4096-4

COMPARATIVE VOLTAGE AND VARIABLE VOLTAGE GRAPHS

70

0.4

SUPPLY CURRENT PER AMPLIFIER (µA)

ADA4096-2

VSY = ±15V

TA = 25°C

0.3

NOISE (µV)

0.2

0.1

0

–0.1

–0.2

–0.4

–10

–8

–6

–4

–2

0

2

4

6

8

10

TIME (s)

40

30

20

10

4

8

12

16

20

24

28

32

36

SUPPLY VOLTAGE (V)

Figure 50. Supply Current per Amplifier vs. Supply Voltage

–80

100

ADA4096-2

VSY = ±15V

TA = 25°C

ADA4096-2

VSY = ±15V

TA = 25°C

–100

en (nV/ Hz)

CHANNEL SEPARATION (dB)

50

0

Figure 47. Input Voltage Noise, 0.1 Hz to 10 Hz Bandwidth

–90

60

0

09241-039

–0.3

ADA4096-2

TA = 25°C

RL = ∞

09241-043

0.5

–110

10kΩ

–120

1kΩ

2kΩ

–130

100

1k

10k

50k

FREQUENCY (Hz)

10

0.1

09241-040

–140

20

10

100

1k

FREQUENCY (Hz)

Figure 48. Channel Separation vs. Frequency

Figure 51. Voltage Noise Density (eN) vs. Frequency

50

120

ADA4096-2

TA = 25°C

110

40

100

90

OVERSHOOT (%)

VSY = ±15V

80

VSY = ±1.5V

70

VSY = ±5V

60

ADA4096-2

VSY = ±15V

TA = 25°C

RL = 2kΩ

G = +1

VIN = 100mV p-p

30

20

OS–

50

10

40

20

100

1k

10k

100k

FREQUENCY (Hz)

1M

10M

Figure 49. CMRR vs. Frequency

0

0.01

0.1

CLOAD (nF)

Figure 52. Overshoot vs. Load Capacitance (CLOAD)

Rev. G | Page 19 of 25

1

09241-100

OS+

30

09241-041

CMRR (dB)

1

09241-044

VIN =

10V p-p

�ADA4096-2/ADA4096-4

Data Sheet

THEORY OF OPERATION

INPUT STAGE

VCC

R2

I1

R7

R5

I3

D6

Q5

D3

Q3

Q6

D10

Q11

D9

C2

Q4

Q18

OUT

Q13

D4

Q20

Q12

Q7

Q8

C1

Q9

Q14

Q10

D8

Q17

×1

+IN

OVP

–IN

OVP

Q1

Q19

Q2

R6

D2

I2

R3

Q15

R4

D7

Q16

D11

D1

VEE

09241-045

R1

Figure 53. Simplified Schematic, ADA4096-2

Figure 53 shows a simplified schematic of the ADA4096-2. The

input stage comprises two differential pairs (Q1 to Q4 and Q5

to Q8) operating in parallel. When the input common-mode

voltage approaches VCC − 1.5 V, Q1 to Q4 shut down as I1

reaches its minimum voltage compliance. Conversely, when the

input common-mode voltage approaches VEE + 1.5 V, Q5 to Q8

shut down as I2 reaches its minimum voltage compliance. This

topology allows for maximum input dynamic range because the

amplifier can function with its inputs at 200 mV outside the rail

(at room temperature).

Although phase inversion persists for only as long as the inputs

are saturated, it can be detrimental to applications where the

amplifier is part of a closed-loop system. The ADA4096-2 family

is free from phase inversion over the entire common-mode

voltage range, as well as the overvoltage protected range that is

stated in the Absolute Maximum Ratings section, Table 5.

Figure 54 shows the ADA4096-2 in a unity-gain configuration

with the input signal at ±40 V and the amplifier supplies at

±10 V.

As with any rail-to-rail input amplifier, VOS mismatch between

the two input pairs determines the CMRR of the amplifier. If

the input common-mode voltage range is kept within 1.5 V of

each rail, transitions between the input pairs are avoided, thus

improving the CMRR by approximately 10 dB (see Table 3 and

Table 4).

T

1

Some single-supply amplifiers exhibit phase inversion when

the input signal extends beyond the common-mode voltage

range of the amplifier. When the input devices become

saturated, the inverting and noninverting inputs exchange

functions, causing the output to move in the opposing

direction.

CH1 10.0V

CH2 10.0V

M2.00ms

T 34.20%

A CH1

Figure 54. No Phase Reversal

Rev. G | Page 20 of 25

–3.6V

09241-046

PHASE INVERSION

�Data Sheet

ADA4096-2/ADA4096-4

INPUT OVERVOLTAGE PROTECTION

The ADA4096-2 family inputs are protected from input voltage

excursions up to 32 V outside each rail. This feature is of

particular importance in applications with power supply

sequencing issues that could cause the signal source to be active

before the power supplies.

4

3

2

1

0

COMPARATOR OPERATION

Although op amps are quite different from comparators,

occasionally an unused section of a dual or a quad op amp may

be pressed into service as a comparator; however, this is not

recommended for any rail-to-rail output op amps. For rail-torail output op amps, the output stage is generally a ratioed

current mirror with bipolar or metal-oxide semiconductor

field-effect (MOSFET) transistors. With the device operating in

open loop, the second stage increases the current drive to the

ratioed mirror to close the loop, but it cannot, which results in

an increase in supply current. With the op amp configured as a

comparator, the supply current can be significantly higher (see

Figure 56).

–1

500

–2

–4

–5

–7

–48 –40 –32 –24 –16 –8

0

8

16

24

32

VIN (V)

40

48

09241-047

LOW RDSON SERIES FET

5kΩ SERIES RESISTOR

–6

Figure 55. Input Current Limiting Capability

Figure 55 was generated with the ADA4096-2 in a buffer

configuration with the supplies connected to GND (or ±15 V)

and the positive input swept until it exceeds the supplies by

32 V. In general, input current is limited to 1 mA during

positive overvoltage conditions and 200 µA during negative

undervoltage conditions. For example, at an overvoltage of 20 V,

the ADA4096-2 input current is limited to 1 mA, providing a

current-limit equivalent to a series 20 kΩ resistor. Figure 55 also

shows that the current limiting circuitry is active whether the

amplifier is powered or not.

Rev. G | Page 21 of 25

400

VOUT = HIGH

300

VOUT = LOW

200

100

BUFFER

0

0

4

8

12

16

20

24

28

SUPPLY VOLTAGE (V)

Figure 56. Comparator Supply Current

32

36

09241-048

–3

SUPPLY CURRENT PER AMPLIFIER (µA)

INPUT BIAS CURRENT (mA)

5

VCC = +15V

6

VEE = 0V

7

VEE = –15V

Figure 55 shows the input current limiting capability of the

ADA4096-2 (green curves) compared to using a 5 kΩ series

resistor (red curves).

Note that Figure 55 represents input protection under abnormal

conditions only. The correct amplifier operation input voltage

range (IVR) is specified in Table 2 to Table 4.

�ADA4096-2/ADA4096-4

Data Sheet

OUTLINE DIMENSIONS

3.20

3.00

2.80

8

3.20

3.00

2.80

1

5.15

4.90

4.65

5

4

PIN 1

IDENTIFIER

0.65 BSC

0.95

0.85

0.75

15° MAX

1.10 MAX

0.40

0.25

6°

0°

0.80

0.55

0.40

0.23

0.09

10-07-2009-B

0.15

0.05

COPLANARITY

0.10

COMPLIANT TO JEDEC STANDARDS MO-187-AA

Figure 57. 8-Lead Mini Small Outline Package [MSOP]

(RM-8)

Dimensions shown in millimeters

DETAIL A

(JEDEC 95)

1.70

1.60

1.50

2.10

2.00 SQ

1.90

0.50 BSC

0.15 REF

8

5

0.425

0.350

0.275

PKG-003580

SEATING

PLANE

SIDE VIEW

0.30

0.25

0.20

4

1

BOTTOM VIEW

TOP VIEW

0.60

0.55

0.50

1.10

1.00

0.90

EXPOSED

PAD

0.05 MAX

0.02 NOM

0.20 REF

FOR PROPER CONNECTION OF

THE EXPOSED PAD, REFER TO

THE PIN CONFIGURATION AND

FUNCTION DESCRIPTIONS

SECTION OF THIS DATA SHEET

Figure 58. 8-Lead Lead Frame Chip Scale Package [LFCSP]

2 mm × 2 mm Body and 0.55 mm Package Height

(CP-8-10)

Dimensions shown in millimeters

Rev. G | Page 22 of 25

PIN 1

INDIC ATOR AREA OPTIONS

(SEE DETAIL A)

02-08-2017-C

PIN 1 INDEX

AREA

�Data Sheet

ADA4096-2/ADA4096-4

5.10

5.00

4.90

14

8

4.50

4.40

4.30

6.40

BSC

1

7

PIN 1

0.65 BSC

1.20

MAX

0.15

0.05

COPLANARITY

0.10

0.30

0.19

0.20

0.09

0.75

0.60

0.45

8°

0°

SEATING

PLANE

061908-A

1.05

1.00

0.80

COMPLIANT TO JEDEC STANDARDS MO-153-AB-1

Figure 59. 14-Lead Thin Shrink Small Outline Package [TSSOP]

(RU-14)

Dimensions shown in millimeters

DETAIL A

(JEDEC 95)

0.30

0.23

0.18

0.50

BSC

13

PIN 1

INDICATOR AREA OPTIONS

16

(SEE DETAIL A)

12

1

1.75

1.60 SQ

1.45

EXPOSED

PAD

9

TOP VIEW

0.80

0.75

0.70

PKG-005138

SEATING

PLANE

TOP VIEW

0.50

0.40

0.30

4

8

5

BOTTOM VIEW

0.05 MAX

0.02 NOM

COPLANARITY

0.08

0.20 REF

FOR PROPER CONNECTION OF

THE EXPOSED PAD, REFER TO

THE PIN CONFIGURATION AND

FUNCTION DESCRIPTIONS

SECTION OF THIS DATA SHEET.

COMPLIANT TO JEDEC STANDARDS MO-220-WEED-6.

Figure 60. 16-Lead Lead Frame Chip Scale Package [LFCSP]

3 mm × 3 mm Body and 0.75 mm Package Height

(CP-16-22)

Dimensions shown in millimeters

Rev. G | Page 23 of 25

0.20 MIN

02-23-2017-E

PIN 1

INDICATOR

3.10

3.00 SQ

2.90

�ADA4096-2/ADA4096-4

Data Sheet

ORDERING GUIDE

Model 1, 2

ADA4096-2ARMZ

ADA4096-2ARMZ-R7

ADA4096-2ARMZ-RL

ADA4096-2ACPZ-R7

ADA4096-2ACPZ-RL

ADA4096-2WARMZ-R7

ADA4096-2WARMZ-RL

ADA4096-4ARUZ

ADA4096-4ARUZ-R7

ADA4096-4ARUZ-RL

ADA4096-4ACPZ-R7

ADA4096-4ACPZ-RL

1

2

Temperature Range

−40°C to +125°C

−40°C to +125°C

−40°C to +125°C

−40°C to +125°C

−40°C to +125°C

−40°C to +125°C

−40°C to +125°C

−40°C to +125°C

−40°C to +125°C

−40°C to +125°C

−40°C to +125°C

−40°C to +125°C

Package Description

8-Lead Mini Small Outline Package [MSOP]

8-Lead Mini Small Outline Package [MSOP]

8-Lead Mini Small Outline Package [MSOP]

8-Lead Lead Frame Chip Scale Package [LFCSP_UD]

8-Lead Lead Frame Chip Scale Package [LFCSP_UD]

8-Lead Mini Small Outline Package [MSOP]

8-Lead Mini Small Outline Package [MSOP]

14-Lead Thin Shrink Small Outline Package [TSSOP]

14-Lead Thin Shrink Small Outline Package [TSSOP]

14-Lead Thin Shrink Small Outline Package [TSSOP]

16-Lead Lead Frame Chip Scale Package [LFCSP_WQ]

16-Lead Lead Frame Chip Scale Package [LFCSP_WQ]

Package Option

RM-8

RM-8

RM-8

CP-8-10

CP-8-10

RM-8

RM-8

RU-14

RU-14

RU-14

CP-16-22

CP-16-22

Branding

A2T

A2T

A2T

A4

A4

A2T

A2T

A30

A30

Z = RoHS Compliant Part.

W = Qualified for Automotive Applications.

AUTOMOTIVE PRODUCTS

The ADA4096-2W models are available with controlled manufacturing to support the quality and reliability requirements of automotive

applications. Note that these automotive models may have specifications that differ from the commercial models; therefore, designers

should review the Specifications section of this data sheet carefully. Only the automotive grade products shown are available for use in

automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to

obtain the specific Automotive Reliability reports for these models.

Rev. G | Page 24 of 25

�Data Sheet

ADA4096-2/ADA4096-4

NOTES

©2011–2017 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D09241-0-9/17(G)

Rev. G | Page 25 of 25

�