4.25 Gbps 40 × 40

数字交叉开关

ADN4605

产品特性

功能框图

DVCC

IP[39:0]

VTTIA,

VTTIB

IN[39:0]

VCC

Rx

40 × 40

SWITCH

MATRIX

EQ

Tx

OP[39:0]

PREEMPHASIS

VTTOA,

VTTOB

ON[39:0]

EQUALIZATION

SETTINGS

CONNECTION

MAP 1

CONNECTION

MAP 0

RESET

SER/PAR

I2C/SPI

(UPDATE)

CS

SCL/SCK/

WE

SDI/RE

OUTPUT

LEVEL

SETTINGS

PREEMPHASIS

LEVEL

SETTINGS

DATA[0]/

SDA/SDO

DATA[1]

(UPDATE)

DATA[7:2]

PARALLEL/SERIA L CONTROL

LOGIC INTERFACE

ADDR[7:0]

ADN4605

VEE

09796-001

每端口的NRZ数据速率:DC至4.25 Gbps

可调节接收均衡

3 dB、6 dB或12 dB增强

4.25 Gbps时可补偿40英寸以上的FR4

可调节发射预加重/去加重

可编程增强和输出级

4.25 Gbps时可补偿40英寸以上的FR4

低功耗

每通道105 mW(2.5 V,400 mV p-p差分输出电平摆幅)

40 x 40、全差分、非阻塞式阵列

含双映射的双级连接编程

低抖动:典型值 1 kΩ)。

Rev. A | Page 38 of 56

�ADN4605

寄存器映射

请注意,在“寄存器映射”中,当“描述”栏中提供的设置针对第一个bit时,这些设置适用于具有相同功能的所

有bits。

表19. 寄存器映射

寄存器名称

软件复位

Bits

0

Bit名称

复位

描述

软件复位

XPT更新

0

XPT更新

更新交叉点开关内核

0x02

默认值

0x00

只写

0x0

只写

0x00

XPT映射表

选择

0

映射表选择

0x03

0x04

0x05

0x06

0x07

0x08

0x09

0x0A

0x0B

0x0C

0x0D

0x0E

0x0F

0x10

0x11

0x12

0x13

0x14

0x15

0x16

0x17

0x18

0x19

0x1A

0x1B

0x1C

0x1D

0x1E

0x1F

0x20

0x21

0x22

0x23

0x24

0x25

0x26

0x27

0x28

0x29

0x2A

0x2B

只写

0x00

0x01

0x02

0x03

0x04

0x05

0x06

0x07

0x08

0x09

0x0A

0x0B

0x0C

0x0D

0x0E

0x0F

0x10

0x11

0x12

0x13

0x14

0x15

0x16

0x17

0x18

0x19

0x1A

0x1B

0x1C

0x1D

0x1E

0x1F

0x20

0x21

0x22

0x23

0x24

0x25

0x26

0x27

XPT广播

XPT映射0控制0

XPT映射0控制1

XPT映射0控制2

XPT映射0控制3

XPT映射0控制4

XPT映射0控制5

XPT映射0控制6

XPT映射0控制7

XPT映射0控制8

XPT映射0控制9

XPT映射0控制10

XPT映射0控制11

XPT映射0控制12

XPT映射0控制13

XPT映射0控制14

XPT映射0控制15

XPT映射0控制16

XPT映射0控制17

XPT映射0控制18

XPT映射0控制19

XPT映射0控制20

XPT映射0控制21

XPT映射0控制22

XPT映射0控制23

XPT映射0控制24

XPT映射0控制25

XPT映射0控制26

XPT映射0控制27

XPT映射0控制28

XPT映射0控制29

XPT映射0控制30

XPT映射0控制31

XPT映射0控制32

XPT映射0控制33

XPT映射0控制34

XPT映射0控制35

XPT映射0控制36

XPT映射0控制37

XPT映射0控制38

XPT映射0控制39

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

XPT BCAST [5:0]

OUT 0 [5:0]

OUT 1 [5:0]

OUT 2 [5:0]

OUT 3 [5:0]

OUT 4 [5:0]

OUT 5 [5:0]

OUT 6 [5:0]

OUT 7 [5:0]

OUT 8 [5:0]

OUT 9 [5:0]

OUT 10 [5:0]

OUT 11 [5:0]

OUT 12 [5:0]

OUT 13 [5:0]

OUT 14 [5:0]

OUT 15 [5:0]

OUT 16 [5:0]

OUT 17 [5:0]

OUT 18 [5:0]

OUT 19 [5:0]

OUT 20 [5:0]

OUT 21 [5:0]

OUT 22 [5:0]

OUT 23 [5:0]

OUT 24 [5:0]

OUT 25 [5:0]

OUT 26 [5:0]

OUT 27 [5:0]

OUT 28 [5:0]

OUT 29 [5:0]

OUT 30 [5:0]

OUT 31 [5:0]

OUT 32 [5:0]

OUT 33 [5:0]

OUT 34 [5:0]

OUT 35 [5:0]

OUT 36 [5:0]

OUT 37[5:0]

OUT 38 [5:0]

OUT 39 [5:0]

0:选取映射0

1:选取映射1

所有输出连接分配

输出0连接分配

输出1连接分配

输出2连接分配

输出3连接分配

输出4连接分配

输出5连接分配

输出6连接分配

输出7连接分配

输出8连接分配

输出9连接分配

输出10连接分配

输出11连接分配

输出12连接分配

输出13连接分配

输出14连接分配

输出15连接分配

输出16连接分配

输出17连接分配

输出18连接分配

输出19连接分配

输出20连接分配

输出21连接分配

输出22连接分配

输出23连接分配

输出24连接分配

输出25连接分配

输出26连接分配

输出27连接分配

输出28连接分配

输出29连接分配

输出30连接分配

输出31连接分配

输出32连接分配

输出33连接分配

输出34连接分配

输出35连接分配

输出36连接分配

输出37连接分配

输出38连接分配

输出39连接分配

地址:通道

0x00

0x01

Rev. A | Page 39 of 56

�ADN4605

地址:通道

0x2C

0x2D

0x2E

0x2F

0x30

0x31

0x32

0x33

0x34

0x35

0x36

0x37

0x38

0x39

0x3A

0x3B

0x3C

0x3D

0x3E

0x3F

0x40

0x41

0x42

0x43

0x44

0x45

0x46

0x47

0x48

0x49

0x4A

0x4B

0x4C

0x4D

0x4E

0x4F

0x50

0x51

0x52

0x53

0x54

0x55

0x56

0x57

0x58

0x59

0x5A

0x5B

0x5C

0x5D

0x5E

0x5F

0x60

默认值

0x27

0x26

0x25

0x24

0x23

0x22

0x21

0x20

0x1F

0x1E

0x1D

0x1C

0x1B

0x1A

0x19

0x18

0x17

0x16

0x15

0x14

0x13

0x12

0x11

0x10

0x0F

0x0E

0x0D

0x0C

0x0B

0x0A

0x09

0x08

0x07

0x06

0x05

0x04

0x03

0x02

0x01

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

寄存器名称

XPT映射1控制0

XPT映射1控制1

XPT映射1控制2

XPT映射1控制3

XPT映射1控制4

XPT映射1控制5

XPT映射1控制6

XPT映射1控制7

XPT映射1控制8

XPT映射1控制9

XPT映射1控制10

XPT映射1控制11

XPT映射1控制12

XPT映射1控制13

XPT映射1控制14

XPT映射1控制15

XPT映射1控制16

XPT映射1控制17

XPT映射1控制18

XPT映射1控制19

XPT映射1控制20

XPT映射1控制21

XPT映射1控制22

XPT映射1控制23

XPT映射1控制24

XPT映射1控制25

XPT映射1控制26

XPT映射1控制27

XPT映射1控制28

XPT映射1控制29

XPT映射1控制30

XPT映射1控制31

XPT映射1控制32

XPT映射1控制33

XPT映射1控制34

XPT映射1控制35

XPT映射1控制36

XPT映射1控制37

XPT映射1控制38

XPT映射1控制39

XPT状态0

XPT状态1

XPT状态2

XPT状态3

XPT状态4

XPT状态5

XPT状态6

XPT状态7

XPT状态8

XPT状态9

XPT状态10

XPT状态11

XPT状态12

Bits

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

Bit名称

OUT 0 [5:0]

OUT 1 [5:0]

OUT 2 [5:0]

OUT 3 [5:0]

OUT 4 [5:0]

OUT 5 [5:0]

OUT 6 [5:0]

OUT 7 [5:0]

OUT 8 [5:0]

OUT 9 [5:0]

OUT 10 [5:0]

OUT 11 [5:0]

OUT 12 [5:0]

OUT 13 [5:0]

OUT 14 [5:0]

OUT 15 [5:0]

OUT 16 [5:0]

OUT 17 [5:0]

OUT 18 [5:0]

OUT 19 [5:0]

OUT 20 [5:0]

OUT 21 [5:0]

OUT 22 [5:0]

OUT 23 [5:0]

OUT 24 [5:0]

OUT 25 [5:0]

OUT 26 [5:0]

OUT 27 [5:0]

OUT 28 [5:0]

OUT 29 [5:0]

OUT 30 [5:0]

OUT 31 [5:0]

OUT 32 [5:0]

OUT 33 [5:0]

OUT 34 [5:0]

OUT 35 [5:0]

OUT 36 [5:0]

OUT 37[5:0]

OUT 38 [5:0]

OUT 39 [5:0]

OUT 0 [5:0]

OUT 1 [5:0]

OUT 2 [5:0]

OUT 3 [5:0]

OUT 4 [5:0]

OUT 5 [5:0]

OUT 6 [5:0]

OUT 7 [5:0]

OUT 8 [5:0]

OUT 9 [5:0]

OUT 10 [5:0]

OUT 11 [5:0]

OUT 12 [5:0]

Rev. A | Page 40 of 56

描述

输出0连接分配

输出1连接分配

输出2连接分配

输出3连接分配

输出4连接分配

输出5连接分配

输出6连接分配

输出7连接分配

输出8连接分配

输出9连接分配

输出10连接分配

输出11连接分配

输出12连接分配

输出13连接分配

输出14连接分配

输出15连接分配

输出16连接分配

输出17连接分配

输出18连接分配

输出19连接分配

输出20连接分配

输出21连接分配

输出22连接分配

输出23连接分配

输出24连接分配

输出25连接分配

输出26连接分配

输出27连接分配

输出28连接分配

输出29连接分配

输出30连接分配

输出31连接分配

输出32连接分配

输出33连接分配

输出34连接分配

输出35连接分配

输出36连接分配

输出37连接分配

输出38连接分配

输出39连接分配

输出0连接状态

输出1连接状态

输出2连接状态

输出3连接状态

输出4连接状态

输出5连接状态

输出6连接状态

输出7连接状态

输出8连接状态

输出9连接状态

输出10连接状态

输出11连接状态

输出12连接状态

�ADN4605

地址:通道

0x61

0x62

0x63

0x64

0x65

0x66

0x67

0x68

0x69

0x6A

0x6B

0x6C

0x6D

0x6E

0x6F

0x70

0x71

0x72

0x73

0x74

0x75

0x76

0x77

0x78

0x79

0x7A

0x7B

0x7D

0x80:输出0

0x81:输出1

0x82:输出2

0x83:输出3

0x84:输出4

0x85:输出5

0x86:输出6

0x87:输出7

0x88:输出8

0x89:输出9

0x8A:输出10

0x8B:输出11

0x8C:输出12

0x8D:输出13

0x8E:输出14

0x8F:输出15

0x90:输出16

0x91:输出17

0x92:输出18

0x93:输出19

0x94:输出20

0x95:输出21

0x96:输出22

0x97:输出23

0x98:输出24

默认值

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

寄存器名称

XPT状态13

XPT状态14

XPT状态15

XPT状态16

XPT状态17

XPT状态18

XPT状态19

XPT状态20

XPT状态21

XPT状态22

XPT状态23

XPT状态24

XPT状态25

XPT状态26

XPT状态27

XPT状态28

XPT状态29

XPT状态30

XPT状态31

XPT状态32

XPT状态33

XPT状态34

XPT状态35

XPT状态36

XPT状态37

XPT状态38

XPT状态39

XPT裕量

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Bits

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

5:0

0

7

6:4

Bit名称

OUT 13 [5:0]

OUT 14 [5:0]

OUT 15 [5:0]

OUT 16 [5:0]

OUT 17 [5:0]

OUT 18 [5:0]

OUT 19 [5:0]

OUT 20 [5:0]

OUT 21 [5:0]

OUT 22 [5:0]

OUT 23 [5:0]

OUT 24 [5:0]

OUT 25 [5:0]

OUT 26 [5:0]

OUT 27 [5:0]

OUT 28 [5:0]

OUT 29 [5:0]

OUT 30 [5:0]

OUT 31 [5:0]

OUT 32 [5:0]

OUT 33 [5:0]

OUT 34 [5:0]

OUT 35 [5:0]

OUT 36 [5:0]

OUT 37[5:0]

OUT 38 [5:0]

OUT 39 [5:0]

XPT_HDROOM

保留

OLEV [2:0]

描述

输出13连接状态

输出14连接状态

输出15连接状态

输出16连接状态

输出17连接状态

输出18连接状态

输出19连接状态

输出20连接状态

输出21连接状态

输出22连接状态

输出23连接状态

输出24连接状态

输出25连接状态

输出26连接状态

输出27连接状态

输出28连接状态

输出29连接状态

输出30连接状态

输出31连接状态

输出32连接状态

输出33连接状态

输出34连接状态

输出35连接状态

输出36连接状态

输出37连接状态

输出38连接状态

输出39连接状态

0 = 禁用,1 = 使能(VCC > 2.7 V时需要)

0(保留位)

000: 0 mA

001: 4 mA

010: 8 mA

011: 12 mA

100:16 mA(默认)

101: 20 mA

110: 24 mA

111:(保留位)

3

Overdrive

1:过驱(使OLEV和PE电流增加25%)

0:无过驱(默认)

2:0

PE [2:0]

000:0 mA(默认)

001: 2 mA

010: 3 mA

011: 4 mA

100: 5 mA

101: 6 mA

110: 7 mA

111: 8 mA

Rev. A | Page 41 of 56

�ADN4605

地址:通道

0x99:输出25

0x9A:输出26

0x9B:输出27

0x9C:输出28

0x9D:输出29

0x9E:输出30

0x9F:输出31

0xA0:输出32

0xA1:输出33

0xA2:输出34 4

0xA3:输出35

0xA4:输出36

0xA5:输出37

0xA6:输出38

0xA7:输出39

0xA8:Tx广播

0xA9

默认值

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x40

0x0

寄存器名称

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx通道控制

Tx符号控制

0xAA

0x0

Tx符号控制

0xAB

0x0

Tx符号控制

0xAC

0x0

Tx符号控制

Bits

Bit名称

描述

7

TXSIGN [7]

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

TXSIGN [6]

TXSIGN [5]

TXSIGN [4]

TXSIGN [3]

TXSIGN [2]

TXSIGN [1]

TXSIGN [0]

TXSIGN [15]

TXSIGN [14]

TXSIGN [13]

TXSIGN [12]

TXSIGN [11]

TXSIGN [10]

TXSIGN [9]

TXSIGN [8]

TXSIGN [23]

TXSIGN [22]

TXSIGN [21]

TXSIGN [20]

TXSIGN [19]

TXSIGN [18]

TXSIGN [17]

TXSIGN [16]

TXSIGN [31]

TXSIGN [30]

TXSIGN [29]

TXSIGN [28]

TXSIGN [27]

TXSIGN [26]

TXSIGN [25]

TXSIGN [24]

信号路径极性反转输出7

0 = 不反转

1 = 反转

信号路径极性反转输出6

信号路径极性反转输出5

信号路径极性反转输出4

信号路径极性反转输出3

信号路径极性反转输出2

信号路径极性反转输出1

信号路径极性反转输出0

信号路径极性反转输出15

信号路径极性反转输出14

信号路径极性反转输出13

信号路径极性反转输出12

信号路径极性反转输出11

信号路径极性反转输出10

信号路径极性反转输出9

信号路径极性反转输出8

信号路径极性反转输出23

信号路径极性反转输出22

信号路径极性反转输出21

信号路径极性反转输出20

信号路径极性反转输出19

信号路径极性反转输出18

信号路径极性反转输出17

信号路径极性反转输出16

信号路径极性反转输出31

信号路径极性反转输出30

信号路径极性反转输出29

信号路径极性反转输出28

信号路径极性反转输出27

信号路径极性反转输出26

信号路径极性反转输出25

信号路径极性反转输出24

Rev. A | Page 42 of 56

�ADN4605

Tx驱动控制

Bits

7

6

5

4

3

2

1

0

7:6

Bit名称

TXSIGN [39]

TXSIGN [38]

TXSIGN [37]

TXSIGN [36]

TXSIGN [35]

TXSIGN [34]

TXSIGN [33]

TXSIGN [32]

TXEN [3]

Tx驱动控制

5:4

3:2

1:0

7:6

TXEN [2]

TXEN [1]

TXEN [0]

TXEN [7]

Tx驱动控制

5:4

3:2

1:0

7:6

TXEN [6]

TXEN [5]

TXEN [4]

TXEN [11]

Tx驱动控制

5:4

3:2

1:0

7:6

TXEN [10]

TXEN [9]

TXEN [8]

TXEN [15]

Tx驱动控制

5:4

3:2

1:0

7:6

TXEN [14]

TXEN [13]

TXEN [12]

TXEN [19]

5:4

3:2

1:0

TXEN [18]

TXEN [17]

TXEN [16]

地址:通道

0xAD

默认值

0x0

寄存器名称

Tx符号控制

0xB0

0x0

0xB1

0xB2

0xB3

0xB4

0x0

0x0

0x0

0x0

Rev. A | Page 43 of 56

描述

信号路径极性反转输出39

信号路径极性反转输出38

信号路径极性反转输出37

信号路径极性反转输出36

信号路径极性反转输出35

信号路径极性反转输出34

信号路径极性反转输出33

信号路径极性反转输出32

Tx使能状态输出3

11 = 使能

10 = 待机

01 = 静噪

00 = 禁用

Tx使能状态输出2

Tx使能状态输出1

Tx使能状态输出0

Tx使能状态输出7

11 = 使能

10 = 待机

01 = 静噪

00 = 禁用

Tx使能状态输出6

Tx使能状态输出5

Tx使能状态输出4

Tx使能状态输出11

11 = 使能

10 = 待机

01 = 静噪

00 = 禁用

Tx使能状态输出10

Tx使能状态输出9

Tx使能状态输出8

Tx使能状态输出15

11 = 使能

10 = 待机

01 = 静噪

00 = 禁用

Tx使能状态输出14

Tx使能状态输出13

Tx使能状态输出12

Tx使能状态输出19

11 = 使能

10 = 待机

01 = 静噪

00 = 禁用

Tx使能状态输出18

Tx使能状态输出17

Tx使能状态输出16

�ADN4605

地址:通道

0xB5

0xB6

0xB7

0xB8

0xB9

默认值

0x0

0x0

0x0

0x0

0x0

寄存器名称

Tx驱动控制

Bits

7:6

Bit名称

TXEN [23]

Tx驱动控制

5:4

3:2

1:0

7:6

TXEN [22]

TXEN [21]

TXEN [20]

TXEN [27]

Tx驱动控制

5:4

3:2

1:0

7:6

TXEN [26]

TXEN [25]

TXEN [24]

TXEN [31]

Tx驱动控制

5:4

3:2

1:0

7:6

TXEN [30]

TXEN [29]

TXEN [28]

TXEN [35]

Tx驱动控制

5:4

3:2

1:0

7:6

TXEN [34]

TXEN [33]

TXEN [32]

TXEN [39]

TXEN [38]

TXEN [37]

TXEN [36]

TXENBC [39]

TX_HDROOM

0xBA

Write Only

Tx驱动控制

5:4

3:2

1:0

7:6

0xBB

0x0

Tx裕量

0

Rev. A | Page 44 of 56

描述

Tx使能状态输出23

11 = 使能

10 = 待机

01 = 静噪

00 = 禁用

Tx使能状态输出22

Tx使能状态输出21

Tx使能状态输出20

Tx使能状态输出27

11 = 使能

10 = 待机

01 = 静噪

00 = 禁用

Tx使能状态输出26

Tx使能状态输出25

Tx使能状态输出24

Tx使能状态输出31

11 = 使能

10 = 待机

01 = 静噪

00 = 禁用

Tx使能状态输出30

Tx使能状态输出29

Tx使能状态输出28

Tx使能状态输出35

11 = 使能

10 = 待机

01 = 静噪

00 = 禁用

Tx使能状态输出34

Tx使能状态输出33

Tx使能状态输出32

Tx使能状态输出39

11 = 使能

10 = 待机

01 = 静噪

00 = 禁用

Tx使能状态输出38

Tx使能状态输出37

Tx使能状态输出36

Tx使能状态广播

11 = 使能

10 = 待机

01 = 静噪

00 = 禁用

0 = 禁用,1 = 使能(VCC > 2.7 V时需要)

�ADN4605

地址:通道

0xBC

0xBD

0xC0

0xC1

0xC2

0xC3

默认值

0x0

0x0

0x0

0x0

0x0

0x0

寄存器名称

Tx端接控制

Bits

4

Bit名称

TXA_TERM [19:16]

Tx端接控制

3

2

1

0

4

TXA_TERM [15:12]

TXA_TERM [11:8]

TXA_TERM [7:4]

TXA_TERM [3:0]

TXB_TERM [39:36]

3

2

1

0

TXB_TERM [35:32]

TXB_TERM [31:28]

TXB_TERM [27:24]

TXB_TERM [23:20]

Rx EQ控制

7:6

RXEQIN [3]

Rx EQ控制

5:4

3:2

1:0

7:6

RXEQIN [2]

RXEQIN [1]

RXEQIN [0]

RXEQIN [7]

Rx EQ控制

5:4

3:2

1:0

7:6

RXEQIN [6]

RXEQIN [5]

RXEQIN [4]

RXEQIN [11]

Rx EQ控制

5:4

3:2

1:0

7:6

RXEQIN [10]

RXEQIN [9]

RXEQIN [8]

RXEQIN [15]

5:4

3:2

1:0

RXEQIN [14]

RXEQIN [13]

RXEQIN [12]

Rev. A | Page 45 of 56

描述

输出[19:16](B侧)端接控制

0:端接使能

1:端接禁用

输出[15:12](B侧)端接控制

输出[11:8](B侧)端接控制

输出[7:4](B侧)端接控制

输出[3:0](B侧)端接控制

输出[39:36](B侧)端接控制

0:端接使能

1:端接禁用

输出[35:32](B侧)端接控制

输出[31:28](B侧)端接控制

输出[27:24](B侧)端接控制

输出[23:20](B侧)端接控制

输入3的均衡器增强控制

11 = 12 dB

10 = 6 dB

01 = 3 dB

00 = 禁用

输入2的均衡器增强控制

输入1的均衡器增强控制

输入0的均衡器增强控制

输入7的均衡器增强控制

11 = 12 dB

10 = 6 dB

01 = 3 dB

00 = 禁用

输入6的均衡器增强控制

输入5的均衡器增强控制

输入4的均衡器增强控制

输入11的均衡器增强控制

11 = 12 dB

10 = 6 dB

01 = 3 dB

00 = 禁用

输入10的均衡器增强控制

输入9的均衡器增强控制

输入8的均衡器增强控制

输入15的均衡器增强控制

11 = 12 dB

10 = 6 dB

01 = 3 dB

00 = 禁用

输入14的均衡器增强控制

输入13的均衡器增强控制

输入12的均衡器增强控制

�ADN4605

地址:通道

0xC4

0xC5

默认值

0x0

0x0

寄存器名称

Rx EQ控制

Bits

7:6

Bit名称

RXEQIN [19]

Rx EQ控制

5:4

3:2

1:0

7:6

RXEQIN [18]

RXEQIN [17]

RXEQIN [16]

RXEQIN [23]

Rx EQ控制

5:4

3:2

1:0

7:6

RXEQIN [22]

RXEQIN [21]

RXEQIN [20]

RXEQIN [27]

Rx EQ控制

5:4

3:2

1:0

7:6

RXEQIN [26]

RXEQIN [25]

RXEQIN [24]

RXEQIN [31]

Rx EQ控制

5:4

3:2

1:0

7:6

RXEQIN [30]

RXEQIN [29]

RXEQIN [28]

RXEQIN [35]

Rx EQ控制

5:4

3:2

1:0

7:6

RXEQIN [34]

RXEQIN [33]

RXEQIN [32]

RXEQIN [39]

Rx EQ控制

5:4

3:2

1:0

1:0

RXEQIN [38]

RXEQIN [37]

RXEQIN [36]

RXEQIN BC

输入 19 的均衡器增强控制

0xC6

0xC7

0xC8

0xC9

0xCA

0x0

0x0

0x0

0x0

0x0

Rev. A | Page 46 of 56

描述

输入19的均衡器增强控制

11 = 12 dB

10 = 6 dB

01 = 3 dB

00 = 禁用

输入18的均衡器增强控制

输入17的均衡器增强控制

输入16的均衡器增强控制

输入23的均衡器增强控制

11 = 12 dB

10 = 6 dB

01 = 3 dB

00 = 禁用

输入22的均衡器增强控制

输入21的均衡器增强控制

输入20的均衡器增强控制

输入27的均衡器增强控制

11 = 12 dB

10 = 6 dB

01 = 3 dB

00 = 禁用

输入26的均衡器增强控制

输入25的均衡器增强控制

输入24的均衡器增强控制

输入31的均衡器增强控制

11 = 12 dB

10 = 6 dB

01 = 3 dB

00 = 禁用

输入30的均衡器增强控制

输入29的均衡器增强控制

输入28的均衡器增强控制

输入35的均衡器增强控制

11 = 12 dB

10 = 6 dB

01 = 3 dB

00 = 禁用

输入34的均衡器增强控制

输入33的均衡器增强控制

输入32的均衡器增强控制

输入39的均衡器增强控制

11 = 12 dB

10 = 6 dB

01 = 3 dB

00 = 禁用

输入38的均衡器增强控制

输入37的均衡器增强控制

输入36的均衡器增强控制

所有输入的均衡器增强控制

11 = 12 dB

10 = 6 dB

01 = 3 dB

00 = 禁用

�ADN4605

地址:通道

0xCB

默认值

0x0

寄存器名称

Rx符号控制

0xCC

0x0

Rx符号控制

0xCD

0x0

Rx符号控制

0xCE

0x0

Rx符号控制

0xCF

0x0

Rx符号控制

0xD0

0x0

Rx端接控制

Bits

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

4

3

2

1

0

Bit名称

RXSIGN [7]

RXSIGN [6]

RXSIGN [5]

RXSIGN [4]

RXSIGN [3]

RXSIGN [2]

RXSIGN [1]

RXSIGN [0]

RXSIGN [15]

RXSIGN [14]

RXSIGN [13]

RXSIGN [12]

RXSIGN [11]

RXSIGN [10]

RXSIGN [9]

RXSIGN [8]

RXSIGN [23]

RXSIGN [22]

RXSIGN [21]

RXSIGN [20]

RXSIGN [19]

RXSIGN [18]

RXSIGN [17]

RXSIGN [16]

RXSIGN [31]

RXSIGN [30]

RXSIGN [29]

RXSIGN [28]

RXSIGN [27]

RXSIGN [26]

RXSIGN [25]

RXSIGN [24]

RXSIGN [39]

RXSIGN [38]

RXSIGN [37]

RXSIGN [36]

RXSIGN [35]

RXSIGN [34]

RXSIGN [33]

RXSIGN [32]

RXA_TERM [19:16]

描述

信号路径极性反转输入7

信号路径极性反转输入6

信号路径极性反转输入5

信号路径极性反转输入4

信号路径极性反转输入3

信号路径极性反转输入2

信号路径极性反转输入1

信号路径极性反转输入0

信号路径极性反转输入15

信号路径极性反转输入14

信号路径极性反转输入13

信号路径极性反转输入12

信号路径极性反转输入11

信号路径极性反转输入10

信号路径极性反转输入9

信号路径极性反转输入8

信号路径极性反转输入23

信号路径极性反转输入22

信号路径极性反转输入21

信号路径极性反转输入20

信号路径极性反转输入19

信号路径极性反转输入18

信号路径极性反转输入17

信号路径极性反转输入16

信号路径极性反转输入31

信号路径极性反转输入30

信号路径极性反转输入29

信号路径极性反转输入28

信号路径极性反转输入27

信号路径极性反转输入26

信号路径极性反转输入25

信号路径极性反转输入24

信号路径极性反转输入39

信号路径极性反转输入38

信号路径极性反转输入37

信号路径极性反转输入36

信号路径极性反转输入35

信号路径极性反转输入34

信号路径极性反转输入33

信号路径极性反转输入32

输入[19:16](A侧)端接控制

0:端接控制使能

1:端接控制禁用

RXA_TERM [15:12] 输入[15:12](A侧)端接控制

RXA_TERM [11:8] 输入[11:8](A侧)端接控制

RXA_TERM [7:4]

输入[7:4](A侧)端接控制

RXA_TERM [3:0]

输入[3:0](A侧)端接控制

Rev. A | Page 47 of 56

�ADN4605

地址:通道

0xD1

默认值

0x0

寄存器名称

Rx端接控制

Bits

4

Bit名称

RXB_TERM [39:36]

3

2

1

0

RXB_TERM [35:32]

RXB_TERM [31:28]

RXB_TERM [27:24]

RXB_TERM [23:20]

Rev. A | Page 48 of 56

描述

输入[39:36](B侧)端接控制

0:端接使能

1:端接禁用

输入[35:32](B侧)端接控制

输入[31:28](B侧)端接控制

输入[27:24](B侧)端接控制

输入[23:20](B侧)端接控制

�ADN4605

应用信息

ADN4605是一款与协议无关的异步数字开关,因此适合包

ADN4605来构建一个完整的40 × 40矩阵开关。10 × 10和

括网络路由和数字视频切换在内的各种应用。ADN4605支

20 × 20等较小的阵列分别需要一个和两个ADN4605器件。

持HDMI®、DVI®、DisplayPort以及SD、HD和3G-SDI数字

应采用合适的高速PCB设计技术,以保持高数据速率信号

视频的数据速率和信号电平。ADN4605可用于构建矩阵开

的信号完整性。必须尽可能降低这类应用中的通道间歪斜

关。图50给出了一个40 × 40矩阵开关框图。由于HDMI、

和串扰。

DVI和 DisplayPort为 四 通 道 协 议 , 因 此 可 使 用 四 个

SOURCE 1

IN 0

OUT 0

IN 1

OUT 1

DISPLAY 1

ADN4605

DISPLAY 2

SOURCE 2

IN 39

OUT 39

IN 0

OUT 0

IN 1

OUT 1

ADN4605

IN 39

OUT 39

IN 0

OUT 0

IN 1

OUT 1

ADN4605

SOURCE 39

IN 39

OUT 39

IN 0

OUT 0

IN 1

OUT 1

DISPLAY 39

SOURCE 40

DISPLAY 40

IN 39

OUT 39

图50. ADN4605数字视频(DVI、HDMI、DisplayPort)矩阵开关框图

Rev. A | Page 49 of 56

09796-052

ADN4605

�ADN4605

O/E

IN 1

O/E

IN 2

OUT 1

CDR

E/O

OUT 2

CDR

E/O

CDR

E/O

ADN4605

O/E

IN 39

OUT 39

09796-053

40 × 40

CROSSPOINT

SWITCH

图51. ADN4605网络交换机应用框图

8 LANE UPLINK PATH

Z0

Z0

EQ

PE

Z0

Z0

8 LANE DOWNLINK PATH

Z0

ASIC 2

Z0

PE

EQ

Z0

Z0

LOSSY CHANNEL

LOSSY CHANNEL

图52. 多通道信号调理应用框图

Rev. A | Page 50 of 56

07934-053

ASIC 1

�ADN4605

电源时序控制

输出顺从电压

理想情况下,所有电源都应同时上电至合适电平(电源要

在低电压应用中,用户必须注意差分和共模信号电平。输

求由表1中的电源限值和表6中列出的绝对最大额定值来设

出电压摆幅、预加重设置、电源电压(VCC和VTTOx)以及输

置)。如果ADN4605的电源是分别上电的,则电源上电序

出耦合(交流或直流)的选择会影响峰值和建立单端电压摆

列如下:DV CC 首先上电,接着是V CC ,最后是端接电源

幅以及在输出端接电阻上测得的共模偏移。这些选择还会

(VTTIA、VTTIB、VTTOA和VTTOB)。

影响输出电流,进而会影响功耗。

关断序列恰好相反,即端接电源首先关断。端接电源包含

表20显示了输出共模电压变化与(ΔVOCM = VCC − VOCM)与输

连至VCC电源域的ESD保护二极管。为避免这些元件中出

出电平和预加重设置的关系。单端输出电平是在VTTOx电源

现持续高电流条件,VTTIx和VTTOx电源应在VCC之后上电并

电压等于3.3 V和2.5 V条件下计算得出的,旨在展示一些降

应在VCC之前关断。

低电源电压时面对的实际挑战。VL最小值(最小VL)不得低

如果系统电源在关断状态下具有高阻抗,那么只有注意到

于表1中指定的绝对最低电平。

以下限制,就无需遵守电源时序控制:

由于表1中指定的绝对最低输出电压是相对于VCC而言的,

• 从VTTIx或VTTOx到VCC的峰值电流小于200 mA

因此需要降低VCC,以便在需要较低输出端接电压时使输

出电平保持在指定限值范围内。当输出摆幅小于或等于

• 从VTTIx或VTTOx到VCC的持续电流小于100 mA

400 mV(单端)时,VTTOx电压可低至1.8 V。

功耗

ADN4605的功耗取决于电源电压、I/O耦合类型和器件配

置。输入端接电阻会产生功耗,具体功耗取决于差分输入

摆幅和共模电压。交流耦合时,共模电压等于端接电源电

压(VTTIx或VTTOx)。从输入端接电源汲取的电流实际上为零

在图53给出的应用中,ADN4605用作直流耦合电平转换

器,用于将3.3 V CML驱动器与具有1.8 V I/O的ASIC进行接

口。与VCC串联的二极管可降低VCC处的电压,从而改善输

出顺从电压。

时,端接电阻上仍然会因为差分信号摆幅而产生功耗和热

TX/XPT 裕量

量。内核电源电流和输出端接电流很大程度上取决于器件

Tx裕量和XPT裕量寄存器用于在内核电源电压(VCC)大于

配置,如使能的通道数量、输出电平设置以及输出预加重

2.7 V时改善ADN4605的输出顺从电压范围。使能XPT裕量

设置。

和Tx裕量寄存器后,发射器的输出顺从电压会额外增加

在环境温度较高的条件下工作时,应避免超过器件的最大

300 mV。当内核电源电压(VCC)小于或等于2.7 V时,不应使

能裕量电路。

结温。通过以下方式可以限制总功耗:

置1时,XPT裕量寄存器(地址0x7D)和Tx裕量寄存器(地址

• 降低输出摆幅

• 降低预加重电平

0xBB)针对所有发射器输出使能。值为0时,禁用裕量产生

• 将电源电压降至表1中定义的允许范围内

电路。注意,这两个寄存器(XPT裕量和Tx裕量)必须同时

• 禁用不使用的通道

置1,裕量电路才会正常工作。

或者,可通过以下方式减少热阻:

• 添加外部散热器

• 增加空气流通

有关合适的散热模板布局和制造工艺建议,请参阅“印刷

电路板(PCB)布局布线指南”部分。

Rev. A | Page 51 of 56

�ADN4605

示例:VCC = 3.3 V,VTTOx = 2.5 V

当PE设置为9.5 dB时,交流耦合发射器的单端摆幅为2.2 V

在典型应用中,用户可以选择200 mV单端(400 mVp-p差分)

至1.6 V,直流耦合发射器的输出摆幅则为2.5 V至1.9 V。交

的默认输出电平,并可能需要0 dB和9.5 dB两种预加重设

流耦合发射器的最小单端输出电压(VL-PE)要比VL的最小值

置选项。

1.9 V大300 mV,这违反了器件的规格要求。

禁用预加重时,直流耦合发射器会在端接电阻上产生

通过使能TX_HDROOM和XPT_HDROOM bit,可将VL最小

100 mV共模偏移电压,直流耦合发射器则会导致两倍的共

值减少约300 mV,使其达到1.6 V。此发射器配置现在符合

模偏移电压。直流耦合时,单端输出电压摆幅为2.5 V至

输出电压范围规格。

2.3 V;交流耦合时,摆幅则为2.4 V至2.2 V。这两种情况下,

这些电平均大于VL的最小值,即1.9 V (VL = VCC − 1.4 V)。

Rev. A | Page 52 of 56

�ADN4605

3.3V

3.3V

1.8V

VTTIx

VCC

VTTOx

1.8V

ASIC

3.3V

Z0

Z0

Rx

CML

CML

Z0

09796-055

ADN4605

Z0

VEE

图53. 直流耦合电平转换器应用电路

表20. 输出电压范围和输出共模偏移与输出电平和PE设置的关系

Tx通道控制

寄存器设置

单端输出电平和

PE增强

VSW-DC 1

(mV)

100

100

100

150

150

200

200

200

250

250

300

300

300

350

350

400

400

400

450

450

500

500

550

600

1

VSW-PE1

(mV)

100

300

500

250

450

200

400

600

350

550

300

500

700

450

650

400

600

800

550

750

500

700

650

600

PE增强

百分比(%)

0.00

200.00

400.00

66.67

200.00

0.00

100.00

200.00

40.00

200.00

0.00

66.67

133.33

28.57

85.71

0.00

50.00

100.00

22.22

66.67

0.00

40.00

18.18

0.00

PE

(dB)

0.00

9.54

13.98

4.44

9.54

0.00

6.02

9.54

2.92

6.85

0.00

4.44

7.36

2.18

5.38

0.00

3.52

6.02

1.74

4.44

0.00

2.92

1.45

0.00

OLEV [2:0]

0x01

0x02

0x03

0x02

0x03

0x02

0x03

0x04

0x03

0x04

0x03

0x04

0x05

0x04

0x05

0x04

0x05

0x06

0x05

0x06

0x05

0x06

0x06

0x06

PE [2:0]

0x00

0x03

0x07

0x01

0x05

0x00

0x03

0x07

0x01

0x05

0x00

0x03

0x07

0x01

0x05

0x00

0x03

0x07

0x01

0x05

0x00

0x03

0x01

0x00

交流耦合输出

VCC = VTTO =

VCC = VTTO =

2.5 V

3.3 V

输出

电流

ITTO1

(mA)

4

12

20

10

18

8

16

24

14

22

12

20

28

18

26

16

24

32

22

30

20

28

26

24

∆VOCM1

(mV)

100

300

500

250

450

200

400

600

350

550

300

500

700

450

650

400

600

800

550

750

500

700

650

600

VH-PE1

(V)

3.25

3.15

3.05

3.175

3.075

3.2

3.1

3

3.125

3.025

3.15

3.05

2.95

3.075

2.975

3.1

3.0

2.9

3.025

2.925

3.05

2.95

2.975

3.0

符号定义如表15所示。

Rev. A | Page 53 of 56

VL-PE1

(V)

3.15

2.85

2.55

2.925

2.625

3.0

2.7

2.4

2.775

2.475

2.85

2.55

2.25

2.625

2.325

2.7

2.4

2.1

2.475

2.175

2.55

2.25

2.325

2.4

VH-PE1

(V)

2.45

2.35

2.25

2.375

2.275

2.40

2.30

2.20

2.325

2.225

2.35

2.25

2.15

2.275

2.175

2.3

2.2

2.1

2.225

2.125

2.25

2.15

2.175

2.2

VL-PE1

(V)

2.35

2.05

1.75

2.125

1.825

2.20

1.90

1.60

1.975

1.675

2.05

1.75

1.45

1.825

1.525

1.9

1.6

1.3

1.675

1.375

1.75

1.45

1.525

1.6

直流耦合输出

∆VOCM1

(mV)

50

150

250

125

225

100

200

300

175

275

150

250

350

225

325

200

300

400

275

375

250

350

325

300

VCC = VTTO =

3.3 V

VCC = VTTO =

2.5 V

VH-PE1

(V)

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

VH-PE1

(V)

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

VL-PE1

(V)

3.2

3.0

2.8

3.15

2.85

3.1

2.9

2.7

2.95

2.75

3.0

2.8

2.6

2.85

2.65

2.9

2.7

2.5

2.75

2.55

2.8

2.6

2.65

2.7

VL-PE1

(V)

2.4

2.2

2.0

2.25

2.05

2.3

2.1

1.9

2.15

1.95

2.2

2.0

1.8

2.05

1.85

2.1

1.9

1.7

1.95

1.75

2.0

1.8

1.85

1.9

�ADN4605

W

印刷电路板(PCB)布局布线指南

高速差分输入和输出应通过100 Ω受控阻抗差分传输线路进

行布线。传输线路(微带线或带状线)应当以实心低阻抗参

考层为参考。图54所示为一个PCB截面示例。走线宽度

(W)、差分摆幅(S)、高出参考层的高度(H)以及PCB材料的

S

W

SOLDERMASK

SIGNAL (MICROSTRIP)

H

PCB DIELECTRIC

REFERENCE PLANE

介电常数决定特征阻抗。相邻通道的间距应大于3倍走线

PCB DIELECTRIC

宽度,以便将串扰降至最低。

SIGNAL (STRIPLINE)

PCB DIELECTRIC

REFERENCE PLANE

W

图54. PCB截面示例

Rev. A | Page 54 of 56

S

W

09796-100

PCB DIELECTRIC

�ADN4605

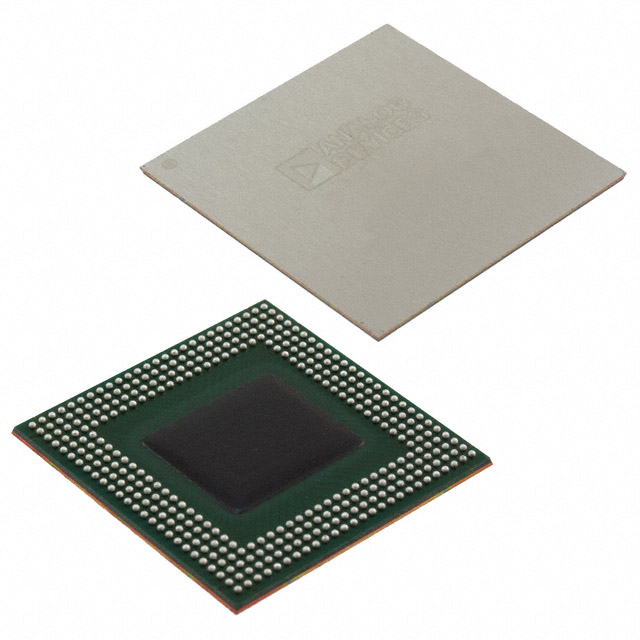

外形尺寸

A1 CORNER

INDEX AREA

35.10

35.00 SQ

34.90

26

25

24

23

22

9

5

3

21 19 17 15 13 11

1

7

6

20 18 16 14 12 10 8

2

4

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

AF

BALL A1

INDICATOR

31.85

31.75 SQ

31.65

TOP VIEW

BOTTOM

VIEW

1.27

BSC

DETAIL A

1.00

0.80

0.60

DETAIL A

1.70 MAX

0.70

0.60

0.50

0.20 MIN

COPLANARITY

0.35

SEATING

PLANE

COMPLIANT TO JEDEC STANDARDS MO-192-BAL-2

022206-A

0.25 MIN

(4 )

0.90

0.75

0.60

BALL DIAMETER

图55. 352球栅阵列、散热增强型封装[BGA_ED]

(BP-352)

图示尺寸单位:mm

订购指南

型号1

ADN4605ABPZ

ADN4605-EVALZ

1

温度范围

−40℃至+85℃

封装描述

352球栅阵列、散热增强型封装[BGA_ED]

评估板

Z = 符合RoHS标准的器件。

Rev. A | Page 55 of 56

封装选项

BP-352

�ADN4605

注释

I2C指最初由Philips Semiconductors(现为NXP Semiconductors)开发的一种通信协议。

HDMI、HDMI商标和High-Definition Multimedia Interface是HDMI Licensing LLC公司在美国及其他国家的商标或注册商标。

©2011 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D09796sc-0-11/11(A)

Rev. A | Page 56 of 56

�

很抱歉,暂时无法提供与“ADN4605ABPZ”相匹配的价格&库存,您可以联系我们找货

免费人工找货