2 A/3 A, 20 V, 700 kHz, Nonsynchronous Step-Down Regulators ADP2302/ADP2303

FEATURES

Wide input voltage range: 3.0 V to 20 V Maximum load current 2 A for ADP2302 3 A for ADP2303 ±1.5% output accuracy over temperature Output voltage down to 0.8 V 700 kHz switching frequency Current-mode control architecture Automatic PFM/PWM mode Precision enable pin with hysteresis Integrated high-side MOSFET Integrated bootstrap diode Internal compensation and soft start Power-good output Undervoltage lockout (UVLO) Overcurrent protection (OCP) Thermal shutdown (TSD) 8-lead SOIC package with exposed paddle

VIN VIN BST

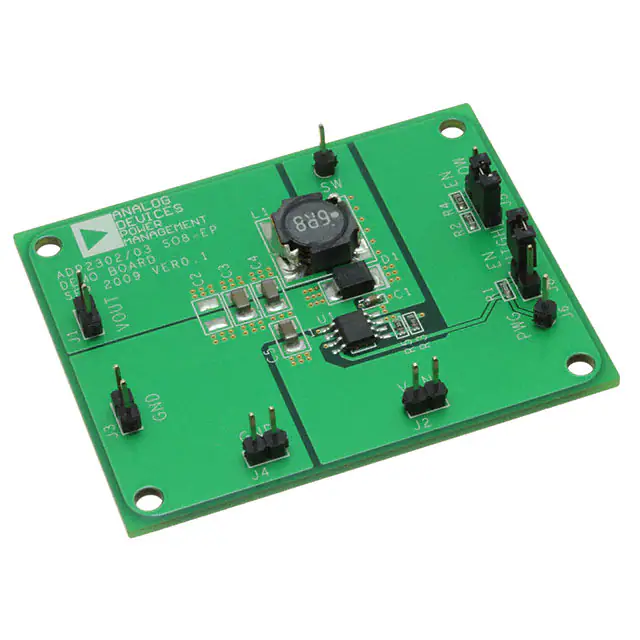

TYPICAL APPLICATIONS CIRCUIT

ADP2302/ ADP2303

PGOOD SW

VOUT

ON OFF EN GND FB

08833-001

Figure 1. Typical Application Circuit

100

90

EFFICIENCY (%)

80

70

APPLICATIONS

Intermediate power rail conversion DC-to-DC point of load applications Communications and networking Industrial and instrumentation Healthcare and medical Consumer

60

50

VOUT = 3.3V INDUCTOR: VLF10040T -4R7N5R4 DIODE: SSB43L VOUT = 5.0V

40

OUTPUT CURRENT (A)

Figure 2. ADP2303 Efficiency vs. Output Current at VIN = 12 V

GENERAL DESCRIPTION

The ADP2302/ADP2303 are fixed frequency, current-mode control, step-down, dc-to-dc regulators with an integrated power MOSFET. The ADP2302/ADP2303 can run from an input voltage of 3.0 V to 20 V, which makes them suitable for a wide range of applications. The output voltage of the ADP2302/ ADP2303 can be down to 0.8 V for the adjustable version, while the fixed output version is available in preset output voltage options of 5.0 V, 3.3 V, and 2.5 V. The 700 kHz operating frequency allows small inductor and ceramic capacitors to be used, providing a compact solution. Current mode control provides fast and stable line and load transient performance. The ADP2302/ADP2303 have integrated soft start circuitry to prevent a large inrush current at power-up. The power-good signal can be used to sequence devices that have an enable input. The precision enable threshold voltage allows the part to be easily sequenced from other input/output supplies. Other key features include undervoltage lockout (UVLO), overvoltage protection (OVP), thermal shutdown (TSD), and overcurrent protection (OCP). The ADP2302/ADP2303 devices are available in the 8-lead, SOIC package with exposed paddle and are rated for the −40oC to +125oC junction temperature range.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com Fax: 781.461.3113 ©2010 Analog Devices, Inc. All rights reserved.

08833-002

0

0.5

1.0

1.5

2.0

2.5

3.0

�ADP2302/ADP2303 TABLE OF CONTENTS

Features .............................................................................................. 1 Applications....................................................................................... 1 Typical Applications Circuit............................................................ 1 General Description ......................................................................... 1 Revision History ............................................................................... 2 Specifications..................................................................................... 3 Absolute Maximum Ratings............................................................ 4 Thermal Resistance ...................................................................... 4 ESD Caution.................................................................................. 4 Pin Configuration and Function Descriptions............................. 5 Typical Performance Characteristics ............................................. 6 Functional Block Diagram ............................................................ 13 Theory of Operation ...................................................................... 14 Basic Operation .......................................................................... 14 PWM Mode................................................................................. 14 Power Saving Mode.................................................................... 14 Bootstrap Circuitry .................................................................... 14 Precision Enable ......................................................................... 14 Integrated Soft Start ................................................................... 14 Current Limit .............................................................................. 14 Short-Circuit Protection............................................................ 14 Undervoltage Lockout (UVLO) ............................................... 15 Thermal Shutdown (TSD)......................................................... 15 Overvoltage Protection (OVP)................................................. 15 Power Good ................................................................................ 15 Control Loop............................................................................... 15 Applications Information .............................................................. 16 Programming Output Voltage .................................................. 16 Voltage Conversion Limitations............................................... 16 Low Input Voltage Considerations .......................................... 17 Programming the Precision Enable ......................................... 17 Inductor ....................................................................................... 17 Catch Diode ................................................................................ 18 Input Capacitor........................................................................... 19 Output Capacitor........................................................................ 19 Thermal Consideration ............................................................. 19 Design Example .............................................................................. 20 Catch Diode Selection ............................................................... 20 Inductor Selection ...................................................................... 20 Output Capacitor Selection....................................................... 20 Resistive Voltage Divider Selection.......................................... 20 Circuit Board Layout Recommendations ................................... 22 Typical Application Circuits ......................................................... 23 Outline Dimensions ....................................................................... 26 Ordering Guide .......................................................................... 26

REVISION HISTORY

7/10—Revision 0: Initial Version

Rev. 0 | Page 2 of 28

�ADP2302/ADP2303 SPECIFICATIONS

VIN = 3.3 V, TJ = −40°C to +125°C for minimum/maximum specifications, and TA = 25°C for typical specifications, unless otherwise noted. Table 1.

Parameters VIN Voltage Range Supply Current Shutdown Current Undervoltage Lockout Threshold FB Regulation Voltage Symbol VIN IVIN ISHDN UVLO Test Conditions Min 3.0 No switching, VIN = 12 V VEN = 0 V, VIN = 12 V VIN rising VIN falling ADP230xARDZ (adjustable) ADP230xARDZ-2.5 ADP230xARDZ-3.3 ADP230xARDZ-5.0 ADP230xARDZ (adjustable) VBST − VSW = 5 V, ISW = 200 mA ADP2302, VBST − VSW = 5 V ADP2303, VBST − VSW = 5 V VEN = VSW = 0 V, VIN = 12 V 720 24 2.7 2.4 0.8 2.5 3.3 5.0 0.01 120 3.5 5.5 0.1 126 210 700 2048 1.2 100 1.2 5.0 87.5 2.5 32 150 0.1 150 15 Typ Max 20 950 45 2.9 Unit V μA μA V V V V V V μA mΩ A A μA ns ns kHz Clock cycles V mV μA V % % Clock cycles mV μA °C °C

2.2 0.788 2.463 3.25 4.925

VFB

Bias Current SW On Resistance 1 Peak Current Limit Leakage Current Minimum On Time Minimum Off Time OSCILLATOR FREQUENCY SOFT START TIME EN Input Threshold Input Hysteresis Pull-Down Current BOOTSTRAP VOLTAGE PGOOD PGOOD Rising Threshold PGOOD Hysteresis PGOOD Deglitch Time 2 PGOOD Output Low Voltage PGOOD Leakage Current THERMAL SHUTDOWN Threshold Hysteresis

1 2

IFB

0.812 2.538 3.35 5.075 0.1 160 4.4 6.4 5 170 280 805

80 2.7 4.6

fSW

595

VEN

1.12

1.28

VBOOT

VIN = 12 V

4.7 82.5

5.3 92.5

VPGOOD = 5 V Rising temperature

300 1

Pin-to-Pin measurements. Guaranteed by design.

Rev. 0 | Page 3 of 28

�ADP2302/ADP2303 ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter VIN, EN, PGOOD SW BST to SW FB, NC Operating Junction Temperature Range Storage Temperature Range Soldering Conditions MAX Rating −0.3 V to +24 V −1.0 V to +24 V −0.6 V to +6 V −0.3 V to +6 V −40°C to +125°C −65°C to +150°C JEDEC J-STD-020

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages. Table 3. Thermal Resistance1

Package Type 8-Lead SOIC_N_EP

1

θJA 58.5

Unit °C/W

θJA is measured using natural convection on JEDEC 4-layer board.

ESD CAUTION

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Absolute maximum ratings apply individually only, not in combination. Unless otherwise specified, all voltages are referenced to GND.

Rev. 0 | Page 4 of 28

�ADP2302/ADP2303 PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

BST 1 VIN 2 EN 3

ADP2302 ADP2303

8 7 6 5

SW GND NC FB

TOP VIEW PGOOD 4 (Not to Scale)

Figure 3. Pin Configuration (Top View)

Table 4. Pin Function Descriptions

Pin No. 1 2 3 4 5 6 7 8 9 (EPAD) Mnemonic BST VIN EN PGOOD FB NC GND SW Exposed Pad Description Bootstrap Supply for the High-Side MOSFET Driver. A 0.1 μF capacitor is connected between SW and BST to provide a floating driver voltage for the power switch. Power Input. Connect to the input power source with a ceramic bypass capacitor to GND directly from this pin. Output Enable. Pull this pin high to enable the output. Pull this pin low to disable the output. This pin can also be used as a programmable UVLO input. This pin has an internal 1.2 μA pull-down current to GND. Power-Good Open-Drain Output. Feedback Voltage Sense Input. For the adjustable version, connect this pin to a resistive divider from VOUT. For the fixed output version, connect this pin to VOUT directly. Used for internal testing. Connect to GND or leave this pin floating to ensure proper operation. Ground. Connect this pin to the ground plane. Switch Node Output. Connect an inductor to VOUT and a catch diode to GND from this pin. The exposed pad should be soldered to an external ground plane underneath the IC for thermal dissipation.

Rev. 0 | Page 5 of 28

08833-003

NOTES 1. NC = NO CONNECT. 2. THE EXPOSED PAD SHOULD BE SOLDERED TO AN EXTERNAL GROUND PLANE UNDERNEATH THE IC FOR THERMAL DISSIPATION.

�ADP2302/ADP2303 TYPICAL PERFORMANCE CHARACTERISTICS

VIN = 3.3 V, TA = 25°C, unless otherwise noted.

100

100

90

90

EFFICIENCY (%)

EFFICIENCY (%)

80

80

70

70 VOUT = 1.5V VOUT = 1.8V VOUT = 2.5V VOUT = 3.3V VOUT = 5.0V INDUCTOR: VLF10040T-4R7N5R4 DIODE: SSB43L

0 0.5 1.0 1.5 2.0 2.5 3.0

08833-007

60

VOUT = 2.5V VOUT = 3.3V VOUT = 5.0V

60

50

INDUCTOR: VLF10040T-6R8N4R5 DIODE: SSB43L 0 0.5 1.0 1.5 2.0 2.5 3.0

08833-004

50

40

40

OUTPUT CURRENT (A)

OUTPUT CURRENT (A)

Figure 4. ADP2303 Efficiency, VIN = 18 V

100

100

Figure 7. ADP2303 Efficiency, VIN = 12 V

90

90

EFFICIENCY (%)

EFFICIENCY (%)

80

80

70 VOUT = 1.2V VOUT = 1.5V VOUT = 1.8V VOUT = 2.5V INDUCTOR: VLF10040T-2R2N7R1 DIODE: SSB43L 0 0.5 1.0 1.5 2.0 2.5 3.0

08833-005

70 VOUT = 2.5V VOUT = 3.3V VOUT = 5.0V

60

60

50

50

INDUCTOR: VLF10040T-6R8N4R5 DIODE: SSB43L 0 0.5 1.0 OUTPUT CURRENT (A) 1.5 2.0

08833-008

40 OUTPUT CURRENT (A)

40

Figure 5. ADP2303 Efficiency, VIN = 5 V

100

Figure 8. ADP2302 Efficiency, VIN = 18 V

100

90

90

EFFICIENCY (%)

70

EFFICIENCY (%)

80

80

70 VOUT = 1.2V VOUT = 1.5V VOUT = 1.8V VOUT = 2.5V

60

VOUT = 1.5V VOUT = 1.8V VOUT = 2.5V VOUT = 3.3V VOUT = 5.0V INDUCTOR: VLF10040T-6R8N4R5 DIODE: SSB43L 0 0.5 1.0 OUTPUT CURRENT (A) 1.5 2.0

08833-006

60

50

50 INDUCTOR: VLF10040T-3R3N6R2 DIODE: SSB43L 0 0.5 1.0 OUTPUT CURRENT (A) 1.5 2.0

08833-009

40

40

Figure 6. ADP2302 Efficiency, VIN = 12 V

Figure 9. ADP2302 Efficiency, VIN = 5 V

Rev. 0 | Page 6 of 28

�ADP2302/ADP2303

0.20 0.15 0.10 0.05 0 –0.05 –0.10 –0.15

08833-010

0.20 0.15 0.10 0.05 0 –0.05 –0.10 –0.15

08833-013

–0.20 5 8 11 VIN (V) 14 17 20

LOAD REGULATION (%)

LINE REGULATION (%)

–0.20 0 0.5 1.0 OUTPUT CURRENT (A) 1.5 2.0

Figure 10. ADP2302 Line Regulation, VOUT = 3.3 V, IOUT = 2 A

0.20 0.15 0.10 0.05 0 –0.05 –0.10 –0.15

08833-011

Figure 13. ADP2302 Load Regulation, VOUT = 3.3V, VIN = 12 V

0.20 0.15 0.10 0.05 0 –0.05 –0.10 –0.15

08833-014

–0.20 5 8 11 VIN (V) 14 17 20

LOAD REGULATION (%)

LINE REGULATION (%)

–0.20

0

0.5

1.0

1.5

2.0

2.5

3.0

OUTPUT CURRENT (A)

Figure 11. ADP2303 Line Regulation, VOUT = 3.3 V , IOUT = 3 A

Figure 14. ADP2303 Load Regulation, VOUT = 3.3 V, VIN = 12 V

50 45

SHUTDOWN CURRENT (μA)

QUIESCENT CURRENT (μA)

900 850 800 750 700 650 600 550 500 TJ = –40°C TJ = +25°C TJ = +125°C

40 35 30 25 20 15 10 5 0

TJ = –40°C TJ = +25°C TJ = +125°C

08833-012

2

4

6

8

10

12

14

16

18

20

2

4

6

8

VIN (V)

10 12 VIN (V)

14

16

18

20

Figure 12. Shutdown Current vs. VIN

Figure 15. Quiescent Current vs. VIN

Rev. 0 | Page 7 of 28

08833-015

�ADP2302/ADP2303

810 790 770

812 810 808

FEEDBACK VOLTAGE (mV)

08833-016

750 FREQUENCY (kHz) 730 710 690 670 650 630 610 590 –40

–20 0 20 40 60 80 100 120

806 804 802 800 798 796 794 792 790 –20 0 20 40 60 80 100 120

08833-019 08833-021

788 –40

TEMPERATURE (°C)

TEMPERATURE (°C)

Figure 16. Frequency vs. Temperature

4.4 4.2

Figure 19. 0.8 V Feedback Voltage vs. Temperature

6.4 6.2

PEAK CURRENT LIMIT (A)

PEAK CURRENT LIMIT (A)

4.0 3.8 3.6 3.4 3.2 3.0 2.8 2.6 –40

6.0 5.8 5.6 5.4 5.2 5.0 4.8

–20

0

20

40

60

80

100

120

08833-017

–20

0

20

40

60

80

100

120

TEMPERATURE (°C)

TEMPERATURE (°C)

Figure 17. ADP2302 Current-Limit Threshold vs. Temperature, VBST − VSW = 5 V

2.9 2.8

Figure 20. ADP2303 Current-Limit Threshold vs. Temperature, VBST − VSW = 5 V

1.30

1.25

ENABLE THRESHOLD (V)

UVLO THRESHOLD (V)

2.7 RISING 2.6 2.5 2.4 FALLING 2.3 2.2 –40

RISING

1.20

1.15

FALLING

1.10

1.05

–20

0

20

40

60

80

100

120

08833-018

1.00 –40

–20

0

20

40

60

80

100

120

TEMPERATURE (°C)

TEMPERATURE (°C)

Figure 18. UVLO Threshold vs. Temperature

Figure 21. Enable Threshold vs. Temperature

Rev. 0 | Page 8 of 28

08833-020

4.6 –40

�ADP2302/ADP2303

270 265 260 255

150 145 140

MINIMUM OFF TIME (ns)

MINIMUM ON TIME (ns)

08833-022

250 245 240 235 230 225 220 215 210 205 –40

–20 0 20 40 60 80 100 120

135 130 125 120 115 110 105

08833-025

100 –40

–20

0

20

40

60

80

100

120

TEMPERATURE (°C)

TEMPERATURE (°C)

Figure 22. Minimum Off Time vs. Temperature

Figure 25. Minimum On Time vs. Temperature

180 170 160

VOUT (AC)

1

MOSFET RESISTOR (mΩ)

150 140 130 120 110 100 90 80 70

08833-023

IL

SW

4

VGS = 3V VGS = 4V VGS = 5V

2

–20

0

20

40

60

80

100

120

CH1 5.00mV

B

W

TEMPERATURE (°C)

CH2 5.00V M1.00µs CH4 2.00A Ω T 30.00%

A CH2

7.50V

Figure 23. MOSFET RDSON vs. Temperature (Pin-to-Pin Measurement)

Figure 26. Continuous Conduction Mode (CCM), VOUT = 3.3 V, VIN = 12 V

VOUT (AC)

1

VOUT (AC)

IL

4

1

4

IL

SW

SW

2

2

08833-024

CH1 5.00mV

B W

CH2 5.00V M1.00µs CH4 2.00A Ω T 30.00%

A CH2

7.50V

CH1 50.00mV

B

W

CH2 5.00V CH4 2.00A Ω

M200µs A CH2 T 30.00%

7.50V

Figure 24. Discontinuous Conduction Mode (DCM), VOUT = 3.3 V, VIN = 12 V

Figure 27. Power Saving Mode, VOUT = 3.3 V, VIN = 12 V

Rev. 0 | Page 9 of 28

08833-027

08833-026

60 –40

�ADP2302/ADP2303

VOUT

VOUT

1

IL

1

IL

4

4

EN SW

3

EN SW

3

2

2

08833-028

CH1 2.00V BW CH3 10.0V BW

CH2 10.0V M1.00ms CH4 2.00A Ω T 20.20%

A CH3

6.20V

CH1 2.00V BW CH3 10.0V BW

CH2 10.0V M1.00ms CH4 2.00A Ω T 20.20%

A CH3

3.60V

Figure 28. Soft Start Without Load, VOUT = 3.3 V, VIN = 12 V

Figure 31. Soft Start with Full Load, VOUT = 3.3 V, VIN = 12 V

VOUT (AC)

1

1

VOUT (AC)

IO

IO

4

4

08833-029

CH1 500mV

B W

CH4 2.00A Ω

M200µs T 20.00%

A CH4

1.20A

CH1 200mV

B W

CH4 2.00A Ω

M200µs T 20.00%

A CH4

1.88A

Figure 29. ADP2303 Load Transient, 0.5 A to 3.0 A, VOUT = 5.0 V, VIN = 12 V, L = 4.7 μH, COUT = 47 μF

Figure 32. ADP2303 Load Transient, 0.5 A to 3.0 A, VOUT = 3.3 V, VIN = 12 V, L = 4.7 μH, COUT = 2 × 47 μF

VOUT (AC)

1 1

VOUT (AC)

IO

IO

4

4

08833-030

08833-032

08833-031

CH1 200mV

B

W

CH4 1.00A Ω

M200µs T 20.00%

A CH4

1.20A

CH1 200mV

B

W

CH4 1.00A Ω

M200µs T 20.00%

A CH4

1.20A

Figure 30. ADP2302 Load Transient, 0.5 A to 2.0 A, VOUT = 5.0 V, VIN = 12 V, L = 6.8 μH, COUT = 2 × 22 μF

Figure 33. ADP2302 Load Transient, 0.5 A to 2.0 A, VOUT = 3.3 V, VIN = 12 V, L = 6.8 μH, COUT = 2 × 22 μF

Rev. 0 | Page 10 of 28

08833-033

�ADP2302/ADP2303

VOUT

VOUT

1 1

IL

IL

4

SW

4

SW

2

08833-034

2

CH1 1.00mV

B W

CH2 10.0V M40.0µs CH4 5.00A Ω T 30.00%

A CH1

1.26V

CH1 1.00V

B

W

CH2 10.0V M400µs CH4 5.00A Ω T 30.00%

A CH1

1.26V

Figure 34. Output Short, VOUT = 3.3 V, VIN = 12 V, L = 4.7 μH, COUT = 2 × 47 μF

Figure 37. Output Short Recovery, VOUT = 3.3 V, VIN = 12 V, L = 4.7 μH, COUT = 2 × 47 μF

VOUT

1

VOUT VIN

VIN

1

SW

SW

3

3

2

2

08833-035

08833-037

CH1 20.0mV BW CH2 10.0V BW CH3 5.00V BW

M1.00ms A CH3 T 23.40%

11.0V

CH1 20.0mV BW CH2 10.0V BW M1.00ms CH3 5.00V BW T 23.40%

A CH3

11.0V

Figure 35. ADP2303 Line Transient, 7 V to 15 V, VOUT = 3.3 V, IOUT = 3 A, L = 4.7 μH, COUT = 2 × 47 μF

80 64 48 32

MAGNITUDE (dB)

Figure 38. ADP2302 Line Transient, 7 V to 15 V, VOUT = 3.3 V, IOUT = 2 A, L = 6.8 μH, COUT = 2 × 22 μF

80 64 48 32 180 144 108 72 36 0 –36 –72 –108 CROSS FREQUENCY = 42kHz PHASE MARGIN = 56° 1k 10k 100k FREQUENCY (Hz) 1M –144

08833-039

180 144 108 72

MAGNITUDE (dB)

16 0 –16 –32 –48 –64 –80 1k

CROSS FREQUENCY = 36kHz PHASE MARGIN = 60°

36 0 –36 –72 –108 –144

PHASE (Degrees)

16 0 –16 –32 –48 –64

08833-036

–180 10k 100k FREQUENCY (Hz) 1M

–80

–180

Figure 36. ADP2302 Bode Plot, VOUT = 2.5 V, VIN = 12 V, L = 4.7 μH, COUT =3 × 22 μF

Figure 39. ADP2302 Bode Plot, VOUT = 3.3 V, VIN = 12 V, L = 6.8 μH, COUT = 2 × 22 μF

Rev. 0 | Page 11 of 28

PHASE (Degrees)

08833-038

�ADP2302/ADP2303

80 64 48 32 180 144 108

80 64 48

MAGNITUDE (B/A) (dB)

180 144 108

PHASE (B–A) (Degeres) PHASE (B–A) (Degeres)

08833-143 08833-142

72 36 0 –36 –72 –108 CROSS FREQUENCY = 32kHz PHASE MARGIN = 59° 1k 10k 100k FREQUENCY (Hz) 1M –144

08833-040

32 16 0 –16 –32 –48 –64 –80 1k

CROSS FREQUENCY = 26kHz PHASE MARGIN = 65°

72 36 0 –36 –72 –108 –144 –180 10k 100k FREQUENCY (Hz) 1M

MAGNITUDE (dB)

16 0 –16 –32 –48 –64 –80

–180

Figure 40. ADP2302 Bode Plot, VOUT = 5 V, VIN = 12 V, L = 6.8 μH, COUT = 2 × 22 μF

80 64 48 32 180 144 108

PHASE (Degrees)

Figure 42. ADP2303 Bode Plot, VOUT = 2.5 V, VIN = 12 V, L = 3.3 μH, COUT = 2 × 47 μF

80 64 48 MAGNITUDE (B/A) (dB) 32 16 0 –16 –32 –48 –64

08833-041

180 144 108 72 36 0 –36 –72 –108 CROSS FREQUENCY = 28kHz PHASE MARGIN = 65° 1k 10k 100k FREQUENCY (Hz) 1M –144 –180

72 36 0 –36 –72 –108 CROSS FREQUENCY = 19kHz PHASE MARGIN = 59° 1k 10k 100k FREQUENCY (Hz) 1M –144 –180

MAGNITUDE (dB)

16 0 –16 –32 –48 –64 –80

PHASE (Degrees)

–80

Figure 41. ADP2303 Bode Plot, VOUT = 3.3 V, VIN = 12 V, L = 4.7 μH, COUT = 2 × 47 μF

Figure 43. ADP2303 Bode Plot, VOUT = 5 V, VIN = 12 V, L = 4.7 μH, COUT = 47 μF

Rev. 0 | Page 12 of 28

�ADP2302/ADP2303 FUNCTIONAL BLOCK DIAGRAM

VIN VIN

2

THERMAL SHUTDOWN

SHUTDOWN LOGIC

UVLO SHUTDOWN IC

1.20V ON OFF EN 3 1.2µA OVP 0.880V CURRENT LIMIT THRESHOLD OCP CURRENT SENSE AMPLIFIER BOOT REGULATOR R S PGOOD 4 VBIAS = 1.1V RAMP GENERATOR CLK GENERATOR

8 1

BST

Q VOUT

SW

0.680V

FREQUENCY FOLDBACK (⅛ fSW, ¼ fSW, ½ fSW, fSW) NC 6

gm

5

0.8V VOLTAGE REFERENCE

FB

ADP2302/ADP2303

7

GND

Figure 44. Functional Block Diagram

Rev. 0 | Page 13 of 28

08833-042

�ADP2302/ADP2303 THEORY OF OPERATION

The ADP2302/ADP2303 are nonsynchronous, step-down, dc-to-dc regulators, each with an integrated high-side power MOSFET. The high switching frequency and 8-lead SOIC package provide a small, step-down, dc-to-dc regulator solution. The ADP2302/ADP2303 can operate with an input voltage from 3.0 V to 20 V while regulating an output voltage down to 0.8 V. The ADP2302 can provide 2 A maximum continuous output current, and the ADP2303 can provide 3 A maximum continuous output current. Because the output voltage occasionally dips below regulation and then recovers, the output voltage ripple in the power saving mode is larger than the ripple in the PWM mode of operation.

BOOTSTRAP CIRCUITRY

The ADP2302/ADP2303 each have an integrated boot regulator, which requires that a 0.1 μF ceramic capacitor (X5R or X7R) be placed between the BST and SW pins to provide the gate drive voltage for the high-side MOSFET. There is at least a 1.2 V difference between the BST and SW pins to turn on the high-side MOSFET. This voltage should not exceed 5.5 V in case the BST pin is supplied with the external voltage source through a diode. The ADP2302/ADP2303 generate a typical 5.0 V bootstrap voltage for the gate drive circuit by differentially sensing and regulating the voltage between the BST and SW pins. There is a diode integrated on the chip that blocks the reverse voltage between the VIN and BST pins when the MOSFET switch is turned on.

BASIC OPERATION

The ADP2302/ADP2303 use the fixed-frequency, peak currentmode PWM control architecture from medium to high loads, but shift to a pulse-skip mode control scheme at light loads to reduce the switching power losses and improve efficiency. When these devices operate in fixed-frequency PWM mode, output regulation is achieved by controlling the duty cycle of the integrated MOSFET. While the devices are operating in pulse-skip mode at light loads, the output voltage is controlled in a hysteretic manner with higher output ripple. In this mode of operation, the regulator periodically stops switching for a few cycles, thus keeping the conversion losses minimal to improve efficiency.

PRECISION ENABLE

The ADP2302/ADP2303 provide a precision enable circuit that has 1.2 V reference threshold with 100 mV hysteresis. When the voltage at the EN pin is greater than 1.2 V (typical), the part is enabled. If the EN voltage falls below 1.1 V (typical), the chip is disabled. The precision enable threshold voltage allows the ADP2302/ADP2303 to be easily sequenced from other input/ output supplies. It also can be used as a programmable UVLO input by using a resistive divider. An internal 1.2 μA pull-down current prevents errors if the EN pin is left floating.

PWM MODE

In PWM mode, the ADP2302/ADP2303 operate at a fixed frequency, set by an internal oscillator. At the start of each oscillator cycle, the MOSFET switch is turned on, providing a positive voltage across the inductor. The inductor current increases until the current-sense signal crosses the peak inductor current threshold that turns off the MOSFET switch; this threshold is set by the error amplifier output. During the MOSFET off time, the inductor current declines through the external diode until the next oscillator clock pulse comes and a new cycle starts.

INTEGRATED SOFT START

The ADP2302/ADP2303 have an internal digital soft start circuitry to limit the output voltage rise time and reduce the inrush current at power up. The soft start time is fixed at 2048 clock cycles.

CURRENT LIMIT

The ADP2302/ADP2303 include current-limit protection circuitry to limit the amount of positive current flowing through the highside MOSFET switch. The positive current limit on the power switch limits the amount of current that can flow from the input to the output.

POWER SAVING MODE

To achieve higher efficiency, the ADP2302/ADP2303 smoothly transition to the pulse-skip mode when the output load decreases below the pulse-skip current threshold. When the output voltage dips below the regulation, the ADP2302/ADP2303 enter PWM mode for a few oscillator cycles until the voltage increases to regulation range. During the idle time between bursts, the MOSFET switch is turned off, and the output capacitor supplies all the output current. Because the pulse-skip mode comparator monitors the internal compensation node, which represents the peak inductor current information, the average pulse-skip load current threshold depends on the input voltage (VIN), the output voltage (VOUT), the inductor, and the output capacitor.

SHORT-CIRCUIT PROTECTION

The ADP2302/ADP2303 include frequency foldback to prevent output current runaway when there is a hard short on the output. The switching frequency is reduced when the voltage at the FB pin drops below a certain value, which allows more time for the inductor current to decline, but increases the ripple current while regulating the peak current. This results in a reduction in average output current and prevents output current runaway. The correlation between the switching frequency and the FB pin voltage is shown in Table 5.

Rev. 0 | Page 14 of 28

�ADP2302/ADP2303

Table 5. Correlation Between fSW and VFB

FB Pin Voltage VFB ≥ 0.6 V 0.4 V < VFB < 0.6 V 0.2 V < VFB ≤ 0.4 V VFB ≤ 0.2 V Switching Frequency fSW 1/2 fSW 1/4 fSW 1/8 fSW

OVERVOLTAGE PROTECTION (OVP)

The ADP2302/ADP2303 provide an overvoltage protection feature to protect the system against an output short to a higher voltage supply. If the feedback voltage is above 0.880 V, the internal high-side MOSFET is turned off, until the voltage at FB decreases to 0.850 V. At that time, the ADP2302/ADP2303 resume normal operation.

When a hard short (VFB ≤ 0.2 V) is removed, a soft start cycle is initiated to regulate the output back to its level during normal operation, which helps to limit the inrush current and prevent possible overshoot on the output voltage.

POWER GOOD

The PGOOD pin is an active high, open-drain output and requires a resistor to pull it up to a voltage (