Ultralow Noise, High Accuracy

Voltage References

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

FEATURES

PIN CONFIGURATIONS

Maximum temperature coefficient (TCVOUT):

0.8 ppm/°C (D grade 0°C to 70°C)

1 ppm/°C (C grade 0°C to 70°C)

2 ppm/°C (B grade −40°C to +125°C)

4 ppm/°C (A grade −40°C to +125°C)

Output noise (0.1 Hz to 10 Hz):

1 μV p-p at VOUT of 2.048 V typical

Initial output voltage error:

B, C, D grade: ±0.02% (maximum)

Input voltage range: 3 V to 15 V

Operating temperature:

A grade and B grade: −40°C to +125°C

C grade and D grade: 0°C to +70°C

Output current: +10 mA source/−10 mA sink

Low quiescent current: 950 μA (maximum)

Low dropout voltage: 300 mV at 2 mA (VOUT ≥ 3 V)

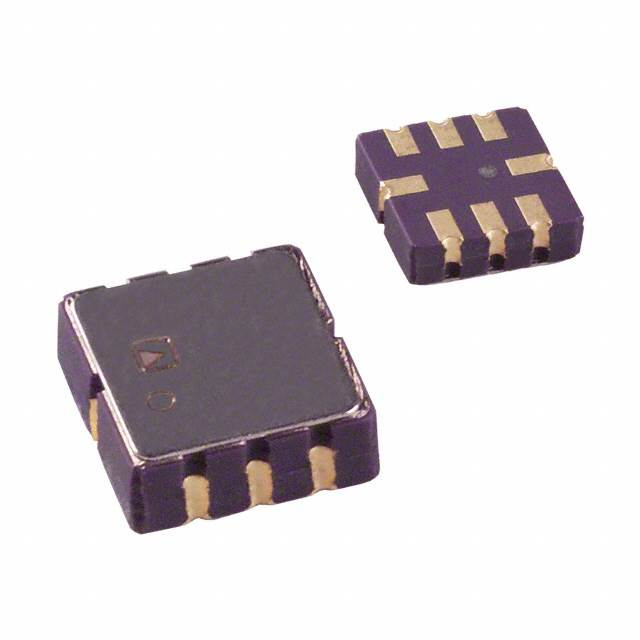

8-lead SOIC and LCC package

AEC-Q100 qualified for automotive applications

Long-term drift: 8 ppm typical at 4500 hours

ADR4520/ADR4525/

ADR4530/ADR4533/

ADR4540/ADR4550

8

DNC

VIN 2

7

NIC

NOTES

1. NIC = NOT INTERNALLY CONNECTED.

THIS PIN IS NOT CONNECTED INTERNALLY.

2. DNC = DO NOT CONNECT. DO NOT CONNECT TO THIS PIN.

Figure 1. 8-Lead SOIC Pin Configuration

ADR4520/ADR4525/

ADR4530/ADR4533/

ADR4540/ADR4550

DNC

8

DNC

1

7

VOUTFORCE

VIN

2

6

VOUTSENSE

GNDFORCE

3

5

NIC

4

GNDSENSE

NOTES

1. NIC = NOT INTERNALLY CONNECTED.

THIS PIN IS NOT CONNECTED INTERNALLY.

2. DNC = DO NOT CONNECT. DO NOT CONNECT TO THIS PIN.

Precision data acquisition systems

High resolution data converters

High precision measurement devices

Industrial instrumentation

Medical devices

Automotive battery monitoring

10203-001

6 VOUT

NIC 3

TOP VIEW

GND 4 (Not to Scale) 5 NIC

APPLICATIONS

Figure 2. 8-Lead LCC Pin Configuration

GENERAL DESCRIPTION

The ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/

ADR4550 devices are high precision, low power, low noise

voltage references featuring ±0.02% B, C, and D grade

maximum initial error, excellent temperature stability, and low

output noise.

This family of voltage references uses an innovative core topology

to achieve high accuracy while offering industry-leading

temperature stability and noise performance. The low, thermally

induced output voltage hysteresis and low long-term output

voltage drift of the devices also improve system accuracy over

time and temperature variations.

A maximum operating current of 950 μA and a maximum low

dropout voltage of 300 mV allow the devices to function very

well in portable equipment.

The ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/

ADR4550 series of references are each provided in an 8-lead

SOIC and are available in a wide range of output voltages, all of

which are specified over the extended industrial temperature

range of −40°C to +125°C.

Rev. D

NIC 1

10203-057

Data Sheet

The ADR4525, ADR4540, and ADR4550 are also available in D,

which are in 8 lead LCC package, and C grade with a temperature

range of 0°C to 70°C. The ADR4525W, available in an 8-lead

SOIC package, is qualified for automotive applications.

Table 1. Selection Guide

Model

ADR4520

ADR4525

ADR4525W

ADR4530

ADR4533

ADR4540

ADR4550

Output Voltage (V)

2.048

2.5

2.5

3.0

3.3

4.096

5.0

Grade

A, B

A, B, C, D

B

A, B

A, B

A, B, C, D

A, B, C, D

Table 2. Voltage Reference Choices from Analog Devices, Inc.

VOUT (V)

2.048

Micropower

ADR3420

LT6656

2.5

ADR3425

LT1461

LT6656

ADR3450

LT1461

LT6656

5.0

Low Power

ADR360

LTC6652

LT6654

ADR361

LTC6652

LT6654

ADR365

LTC6652

LT6654

Ultralow Noise

ADR440

LTC6655

ADR441

LTC6655

ADR445

LTC6655

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice.

No license is granted by implication or otherwise under any patent or patent rights of Analog

Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2012–2021 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

ADR4530 ..................................................................................... 19

Applications ...................................................................................... 1

ADR4533 ..................................................................................... 22

General Description ......................................................................... 1

ADR4540 ..................................................................................... 25

Pin Configurations ........................................................................... 1

ADR4550 ..................................................................................... 29

Revision History ............................................................................... 2

Terminology.................................................................................... 33

Specifications .................................................................................... 4

Applications Information ............................................................. 34

ADR4520 Electrical Characteristics........................................... 4

Basic Voltage Reference Connection ...................................... 34

ADR4525 Electrical Characteristics........................................... 5

Input and Output Capacitors ................................................... 34

ADR4530 Electrical Characteristics........................................... 6

Location of Reference in System .............................................. 34

ADR4533 Electrical Characteristics........................................... 7

Power Dissipation ...................................................................... 34

ADR4540 Electrical Characteristics........................................... 8

Sample Applications .................................................................. 34

ADR4550 Electrical Characteristics........................................... 9

Long-Term Drift ........................................................................ 35

Absolute Maximum Ratings ......................................................... 10

Thermal Hysteresis .................................................................... 36

Thermal Resistance .................................................................... 10

Humidity Sensitivity .................................................................. 37

ESD Caution................................................................................ 10

Power Cycle Hysteresis ............................................................. 38

Pin Configurations and Function Descriptions ......................... 11

Outline Dimensions ....................................................................... 39

Typical Performance Characteristics ........................................... 12

Ordering Guide .......................................................................... 39

ADR4520 ..................................................................................... 12

Automotive Products ................................................................ 40

ADR4525 ..................................................................................... 15

REVISION HISTORY

1/2021—Rev. C to Rev. D

Added 8-Lead LCC Package ........................................ Throughout

Changes to Features Section, General Description Section, and

Table 1 .......................................................................................................... 1

Added Figure 2; Renumbered Sequentially.......................................... 1

Changes to Table 4 ........................................................................... 5

Changes to Table 7 ........................................................................... 8

Changes to Table 8 ........................................................................... 9

Changes to Table 9 and Table 10 ................................................. 10

Added Figure 4 and Table 11; Renumbered Sequentially ........ 11

Changes to Typical Performance Characteristics Section ........ 12

Changes to Figure 110 and Figure 11 .......................................... 35

Added Figure 112 ........................................................................... 35

Changes to Figure 113 to Figure 116 ........................................... 36

Added Figure 117 ........................................................................... 36

Added Figure 118 ........................................................................... 37

Changes to Figure 120 and Figure 121 ........................................ 37

Changes to Figure 122 ................................................................... 38

Added Figure 124 ........................................................................... 38

Changes to Ordering Guide .......................................................... 38

3/2020—Rev. B to Rev. C

Added ADR4540 C Grade and ADR4550 C Grade . Throughout

Changes to Table 4 ............................................................................5

Changes to Table 7 ............................................................................8

Changes to Table 8 ............................................................................9

Deleted Figure 32, Renumbered Sequentially ............................ 18

Changes to Figure 39 ..................................................................... 19

Changes to Figure 52 ..................................................................... 22

Added Figure 69, Renumbered Sequentially .............................. 26

Changes to Figure 79 ..................................................................... 28

Added Figure 83 ............................................................................. 29

Updated Ordering Guide .............................................................. 41

12/2018—Rev. A to Rev. B

Changes to Features Section, Table 1, and Table 2 ......................1

Changes to Table 3 ............................................................................4

Changes to Table 4 ............................................................................5

Changes to Table 5 ............................................................................6

Changes to Table 6 ............................................................................7

Changes to Table 7 ............................................................................8

Changes to Table 8 ............................................................................9

Rev. D | Page 2 of 40

�Data Sheet

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

Added Electrostatic Discharge (ESD) Human Body Model

(HBM) Parameter and Moisture Sensitivity Level Rating

Parameter, Table 9 ..........................................................................10

Changes to Thermal Resistance Section and Table 10 ..............10

Deleted Figure 4; Renumbered Sequentially ...............................12

Changes to Figure 15 ......................................................................14

Deleted Figure 17 ............................................................................14

Changes to Figure 16 Caption .......................................................15

Added Figure 17; Renumbered Sequentially ...............................15

Deleted Figure 19 ............................................................................15

Changes to Figure 29 ......................................................................17

Deleted Figure 32 ............................................................................17

Deleted Figure 34 ............................................................................18

Changes to Figure 43 ......................................................................20

Deleted Figure 48 ............................................................................20

Deleted Figure 50 ............................................................................21

Changes to Figure 56 ......................................................................23

Deleted Figure 63 ............................................................................23

Deleted Figure 65 ............................................................................24

Changes to Figure 69 ......................................................................26

Deleted Figure 78 ............................................................................26

Deleted Figure 80 ............................................................................27

Changes to Figure 82 ......................................................................29

Deleted Figure 93 ............................................................................29

Changes to Terminology Section.................................................. 30

Deleted Theory of Operation Section and Long-Term Drift

Section .............................................................................................. 31

Moved Power Dissipation Section................................................ 31

Added Long-Term Drift (LTD)Section, Figure 86, and

Figure 87 ........................................................................................... 32

Added Thermal Hysteresis Section, Figure 88, Figure 89,

Figure 90, and Figure 91 ................................................................ 33

Added Humidity Sensitivity Section, Figure 92, Figure 93, and

Figure 94 ........................................................................................... 34

Added Power Cycle Hysteresis Section and Figure 95 .............. 35

Changes to Ordering Guide .......................................................... 36

10/2017—Rev. 0 to Rev. A

Changed TP Pin to DNC Pin and NC Pin to

NIC Pin........................................................................... Throughout

Changes to Features Section, Figure 1, and General Description

Section ................................................................................................ 1

Changes to Figure 2 and Table 11 ................................................ 10

Changes to Ordering Guide .......................................................... 32

Added Automotive Products Section .......................................... 33

4/2012—Revision 0: Initial Version

Rev. D | Page 3 of 40

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

Data Sheet

SPECIFICATIONS

ADR4520 ELECTRICAL CHARACTERISTICS

Unless otherwise noted, supply voltage (VIN) = 3 V to 15 V, IL = 0 mA, TA = 25°C.

Table 3.

Parameter

OUTPUT VOLTAGE

INITIAL OUTPUT VOLTAGE ERROR

B Grade

Symbol

VOUT

VOUT_ERR

Test Conditions/Comments

Min

Typ

2.048

Max

Unit

V

±0.02

410

±0.04

820

%

μV

%

μV

%

2

4

4

8

10

80

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/V

ppm/mA

120

950

1

1

ppm/mA

μA

V

V

dB

−8

10

1.0

35.8

mA

mA

μV p-p

nV/√Hz

−13

−97

−8

−17

ppm

ppm

ppm

ppm

19

25

51

90

ppm

ppm

ppm

µs

A Grade

SOLDER HEAT RESISTANCE SHIFT

TEMPERATURE COEFFICIENT

B Grade

±0.02

TCVOUT

A Grade

LINE REGULATION

LOAD REGULATION

ΔVOUT/ΔVIN

ΔVOUT/ΔIL

QUIESCENT CURRENT

DROPOUT VOLTAGE

IQ

VDO

RIPPLE REJECTION RATIO

OUTPUT CURRENT CAPACITY

Sinking

Sourcing

OUTPUT VOLTAGE NOISE

OUTPUT VOLTAGE NOISE DENSITY

OUTPUT VOLTAGE HYSTERESIS

RRR

IL

LONG-TERM DRIFT

TURN-ON SETTLING TIME

eNp-p

eN

ΔVOUT_HYS

ΔVOUT_LTD

tR

See Terminology section

−40°C ≤ TA ≤ +125°C (box method)

−40°C ≤ TA ≤ +125°C (bowtie method)

−40°C ≤ TA ≤ +125°C (box method)

−40°C ≤ TA ≤ +125°C (bowtie method)

−40°C ≤ TA ≤ +125°C

IL = 0 mA to +10 mA source, −40°C ≤ TA ≤

+125°C

IL = 0 mA to −10 mA sink, −40°C ≤ TA ≤ +125°C

−40°C ≤ TA ≤ +125°C, no load

−40°C ≤ TA ≤ +125°C, no load

−40°C ≤ TA ≤ +125°C, IL = 2 mA

Input frequency (fIN) = 1 kHz

1

30

100

700

90

0.1 Hz to 10.0 Hz

1 kHz

TA = temperature cycled from

+25°C to +125°C to−40°C to +25°C (full cycle)

25°C to 125°C to 25°C (half cycle)

25°C to 70°C to 0°C to 25°C (full cycle)

25°C to 70°C to 25°C (half cycle)

TA = 25°C

250 hours (early life drift)

1000 hours

4500 hours

Output capacitor (COUT) = 1 µF, input capacitor

(CIN) = 0.1 µF, load resistance (RLOAD) = 1 kΩ

LOAD CAPACITANCE

1

Rev. D | Page 4 of 40

100

µF

�Data Sheet

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

ADR4525 ELECTRICAL CHARACTERISTICS

Unless otherwise noted, VIN = 3 V to 15 V, IL = 0 mA, TA = 25°C.

Table 4.

Parameter

OUTPUT VOLTAGE

INITIAL OUTPUT VOLTAGE ERROR

B, C, D Grade

Symbol

VOUT

VOUT_ERR

Test Conditions/Comments

Min

Typ

2.500

A Grade

SOLDER HEAT RESISTANCE SHIFT

A, B, C, D Grade

TEMPERATURE COEFFICIENT

D Grade

B Grade

A Grade

ΔVOUT/ΔVIN

ΔVOUT/ΔIL

D Grade

QUIESCENT CURRENT

DROPOUT VOLTAGE

IQ

VDO

RIPPLE REJECTION RATIO

OUTPUT CURRENT CAPACITY

Sinking

Sourcing

OUTPUT VOLTAGE NOISE

OUTPUT VOLTAGE NOISE

DENSITY

OUTPUT VOLTAGE HYSTERESIS

A, B, C Grade

RRR

IL

±0.02

500

±0.04

1

%

μV

%

mV

ΔVOUT_HYS

TA = temperature cycled from

+25°C to +125°C to−40°C to +25°C (full cycle)

25°C to 125°C to 25°C (half cycle)

25°C to 70°C to 0°C to 25°C (full cycle)

25°C to 70°C to 25°C (half cycle)

25°C to 70°C to 0°C to 25°C (full cycle)

25°C to 70°C to 25°C (half cycle)

TA = 25°C

250 hours (early life drift)

1000 hours

4500 hours

250 hours (early life drift)

1000 hours

4500 hours

COUT = 1 µF, CIN = 0.1 µF, RLOAD = 1 kΩ

ΔVOUT_LTD

tR

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/V

80

120

45

9

950

500

500

ppm/mA

ppm/mA

ppm/mA

ppm/mA

μA

mV

mV

dB

−10

10

1.25

41.3

mA

mA

μV p-p

nV/√Hz

−13

−97

−8

−17

1

5

ppm

ppm

ppm

ppm

ppm

ppm

19

25

51

3

5

8

125

ppm

ppm

ppm

ppm

ppm

ppm

µs

µF

30

60

35

4

700

90

1

Rev. D | Page 5 of 40

%

0.8

1.6

1

2

2

4

4

8

10

1

IL = 0 mA to +10 mA source, −40°C ≤ TA ≤ +125°C

IL = 0 mA to −10 mA sink, −40°C ≤ TA ≤ +125°C

IL = 0 mA to +10 mA source, 0°C ≤ TA ≤ +70°C

IL = 0 mA to −10 mA sink, 0°C ≤ TA ≤ +70°C

−40°C ≤ TA ≤ +125°C, no load

−40°C ≤ TA ≤ +125°C, no load

−40°C ≤ TA ≤ +125°C, IL = 2 mA

fIN = 1 kHz

0.1 Hz to 10.0 Hz

1 kHz

D Grade

TURN-ON SETTLING TIME

LOAD CAPACITANCE

See Terminology section

0°C ≤ TA ≤ 70°C (box method)

0°C ≤ TA ≤ 70°C (bowtie method)

0°C ≤ TA ≤ 70°C (box method)

0°C ≤ TA ≤ 70°C (bowtie method)

−40°C ≤ TA ≤ +125°C (box method)

−40°C ≤ TA ≤ +125°C (bowtie method)

−40°C ≤ TA ≤ +125°C (box method)

−40°C ≤ TA ≤ +125°C (bowtie method)

−40°C ≤ TA ≤ +125°C

eNp-p

eN

D Grade

LONG-TERM DRIFT

A, B, C Grade

Unit

V

±0.02

TCVOUT

C Grade

LINE REGULATION

LOAD REGULATION

A, B, C Grade

Max

100

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

Data Sheet

ADR4530 ELECTRICAL CHARACTERISTICS

Unless otherwise noted, VIN = 3.1 V to 15 V, IL = 0 mA, TA = 25°C.

Table 5.

Parameter

OUTPUT VOLTAGE

INITIAL OUTPUT VOLTAGE ERROR

B Grade

Symbol

VOUT

VOUT_ERR

Test Conditions/Comments

Min

Typ

3.000

Max

Unit

V

±0.02

600

±0.04

1.2

%

μV

%

mV

%

2

4

4

8

10

80

120

950

100

300

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/V

ppm/mA

ppm/mA

μA

mV

mV

dB

−10

10

1.6

60

mA

mA

μV p-p

nV/√Hz

−13

−97

−8

−17

ppm

ppm

ppm

ppm

19

25

51

130

ppm

ppm

ppm

µs

µF

A Grade

SOLDER HEAT RESISTANCE SHIFT

TEMPERATURE COEFFICIENT

B Grade

±0.02

TCVOUT

A Grade

LINE REGULATION

LOAD REGULATION

ΔVOUT/ΔVIN

ΔVOUT/ΔIL

QUIESCENT CURRENT

DROPOUT VOLTAGE

IQ

VDO

RIPPLE REJECTION RATIO

OUTPUT CURRENT CAPACITY

Sinking

Sourcing

OUTPUT VOLTAGE NOISE

OUTPUT VOLTAGE NOISE DENSITY

OUTPUT VOLTAGE HYSTERESIS

RRR

IL

LONG-TERM DRIFT

TURN-ON SETTLING TIME

LOAD CAPACITANCE

eNp-p

eN

ΔVOUT_HYS

ΔVOUT_LTD

tR

See Terminology section

−40°C ≤ TA ≤ +125°C (box method)

−40°C ≤ TA ≤ +125°C (bowtie method)

−40°C ≤ TA ≤ +125°C (box method)

−40°C ≤ TA ≤ +125°C (bowtie method)

−40°C ≤ TA ≤ +125°C

IL = 0 mA to +10 mA source, −40°C ≤ TA ≤ +125°C

IL = 0 mA to −10 mA sink, −40°C ≤ TA ≤ +125°C

−40°C ≤ TA ≤ +125°C, no load

−40°C ≤ TA ≤ +125°C, no load

−40°C ≤ TA ≤ +125°C, IL = 2 mA

fIN = 1 kHz

1

30

60

700

90

0.1 Hz to 10.0 Hz

1 kHz

TA = temperature cycled from

+25°C to +125°C to−40°C to +25°C (full cycle)

25°C to 125°C to 25°C (half cycle)

25°C to 70°C to 0°C to 25°C (full cycle)

25°C to 70°C to 25°C (half cycle)

TA = 25°C

250 hours (early life drift)

1000 hours

4500 hours

COUT = 0.1 µF, CIN = 0.1 µF, RLOAD = 1 kΩ

0.1

Rev. D | Page 6 of 40

100

�Data Sheet

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

ADR4533 ELECTRICAL CHARACTERISTICS

Unless otherwise noted, VIN = 3.4 V to 15 V, IL = 0 mA, TA = 25°C.

Table 6.

Parameter

OUTPUT VOLTAGE

INITIAL OUTPUT VOLTAGE ERROR

B Grade

Symbol

VOUT

VOUT_ERR

Test Conditions/Comments

Min

Typ

3.300

Max

Unit

V

±0.02

660

±0.04

1.32

%

µV

%

mV

%

2

4

4

8

10

80

120

950

100

300

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/V

ppm/mA

ppm/mA

μA

mV

mV

dB

−10

10

2.1

64.2

mA

mA

μV p-p

nV/√Hz

−13

−97

−8

−17

ppm

ppm

ppm

ppm

19

25

51

135

ppm

ppm

ppm

µs

µF

A Grade

SOLDER HEAT RESISTANCE SHIFT

TEMPERATURE COEFFICIENT

B Grade

±0.02

TCVOUT

A Grade

LINE REGULATION

LOAD REGULATION

ΔVOUT/ΔVIN

ΔVOUT/ΔIL

QUIESCENT CURRENT

DROPOUT VOLTAGE

IQ

VDO

RIPPLE REJECTION RATIO

OUTPUT CURRENT CAPACITY

Sinking

Sourcing

OUTPUT VOLTAGE NOISE

OUTPUT VOLTAGE NOISE DENSITY

OUTPUT VOLTAGE HYSTERESIS

RRR

IL

LONG-TERM DRIFT

TURN-ON SETTLING TIME

LOAD CAPACITANCE

eNp-p

eN

ΔVOUT_HYS

ΔVOUT_LTD

tR

See Terminology section

−40°C ≤ TA ≤ +125°C (box method)

−40°C ≤ TA ≤ +125°C (bowtie method)

−40°C ≤ TA ≤ +125°C (box method)

−40°C ≤ TA ≤ +125°C (bowtie method)

−40°C ≤ TA ≤ +125°C

IL = 0 mA to +10 mA source, −40°C ≤ TA ≤ +125°C

IL = 0 mA to −10 mA sink, −40°C ≤ TA ≤ +125°C

−40°C ≤ TA ≤ +125°C, no load

−40°C ≤ TA ≤ +125°C, no load

−40°C ≤ TA ≤ +125°C, IL = 2 mA

fIN =1 kHz

1

30

60

700

90

0.1 Hz to 10.0 Hz

1 kHz

TA = temperature cycled from

+25°C to +125°C to−40°C to +25°C (full cycle)

25°C to 125°C to 25°C (half cycle)

25°C to 70°C to 0°C to 25°C (full cycle)

25°C to 70°C to 25°C (half cycle)

TA = 25°C

250 hours (early life drift)

1000 hours

4500 hours

COUT = 0.1 µF, CIN = 0.1 µF, RLOAD = 1 kΩ

0.1

Rev. D | Page 7 of 40

100

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

Data Sheet

ADR4540 ELECTRICAL CHARACTERISTICS

Unless otherwise noted, VIN = 4.2 V to 15 V, IL = 0 mA, TA = 25°C.

Table 7.

Parameter

OUTPUT VOLTAGE

INITIAL OUTPUT VOLTAGE ERROR

B, C, D Grade

Symbol

VOUT

VOUT_ERR

Test Conditions/Comments

Min

Typ

4.096

A Grade

SOLDER HEAT RESISTANCE SHIFT

A, B, C, D Grade

TEMPERATURE COEFFICIENT

D Grade

B Grade

A Grade

ΔVOUT/ΔVIN

ΔVOUT/ΔIL

D Grade

QUIESCENT CURRENT

DROPOUT VOLTAGE

IQ

VDO

RIPPLE REJECTION RATIO

OUTPUT CURRENT CAPACITY

Sinking

Sourcing

OUTPUT VOLTAGE NOISE

OUTPUT VOLTAGE NOISE DENSITY

OUTPUT VOLTAGE HYSTERESIS

A, B, C Grade

RRR

IL

eNp-p

eN

ΔVOUT_HYS

D Grade

LONG-TERM DRIFT

A, B, C Grade

ΔVOUT_LTD

D Grade

TURN-ON SETTLING TIME

LOAD CAPACITANCE

Unit

V

±0.02

820

±0.04

1.64

%

μV

%

mV

±0.02

TCVOUT

C Grade

LINE REGULATION

LOAD REGULATION

A, B, C Grade

Max

tR

See Terminology section

0°C ≤ TA ≤ +70°C (box method)

0°C ≤ TA ≤ +70°C (bowtie method)

0°C ≤ TA ≤ +70°C (box method)

0°C ≤ TA ≤ +70°C (bowtie method)

−40°C ≤ TA ≤ +125°C (box method)

−40°C ≤ TA ≤ +125°C (bowtie method)

−40°C ≤ TA ≤ +125°C (box method)

−40°C ≤ TA ≤ +125°C (bowtie method)

−40°C ≤ TA ≤ +125°C

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/V

80

120

25

9

950

100

300

ppm/mA

ppm/mA

ppm/mA

ppm/mA

μA

mV

mV

dB

−10

10

2.7

83.5

mA

mA

μV p-p

nV/√Hz

−13

−97

−8

−17

1

5

ppm

ppm

ppm

ppm

ppm

ppm

19

25

51

3

5

8

155

ppm

ppm

ppm

ppm

ppm

ppm

µs

µF

25

50

15

5

700

90

0.1 Hz to 10.0 Hz

1 kHz

TA = temperature cycled from

+25°C to +125°C to−40°C to +25°C (full cycle)

25°C to 125°C to 25°C (half cycle)

25°C to 70°C to 0°C to 25°C (full cycle)

25°C to 70°C to 25°C (half cycle)

25°C to 70°C to 0°C to 25°C (full cycle)

25°C to 70°C to 25°C (half cycle)

TA = 25°C

250 hours (early life drift)

1000 hours

4500 hours

250 hours (early life drift)

1000 hours

4500 hours

COUT = 0.1 µF, CIN = 0.1 µF, RLOAD = 1 kΩ

0.1

Rev. D | Page 8 of 40

0.8

1.6

1

2

2

4

4

8

10

1

IL = 0 mA to +10 mA source, −40°C ≤ TA ≤ +125°C

IL = 0 mA to −10 mA sink, −40°C ≤ TA ≤ +125°C

IL = 0 mA to +10 mA source, 0°C ≤ TA ≤ +70°C

IL = 0 mA to −10 mA sink, 0°C ≤ TA ≤ +70°C

−40°C ≤ TA ≤ +125°C, no load

−40°C ≤ TA ≤ +125°C, no load

−40°C ≤ TA ≤ +125°C, IL = 2 mA

fIN = 1 kHz

%

100

�Data Sheet

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

ADR4550 ELECTRICAL CHARACTERISTICS

Unless otherwise noted, VIN = 5.1 V to 15 V, IL = 0 mA, TA = 25°C.

Table 8.

Parameter

OUTPUT VOLTAGE

INITIAL OUTPUT VOLTAGE ERROR

B, C, D Grade

Symbol

VOUT

VOUT_ERR

Test Conditions/Comments

Min

Typ

5.000

A Grade

SOLDER HEAT RESISTANCE SHIFT

A, B, C, D Grade

TEMPERATURE COEFFICIENT

D Grade

TCVOUT

B Grade

A Grade

ΔVOUT/ΔVIN

ΔVOUT/ΔIL

D Grade

QUIESCENT CURRENT

DROPOUT VOLTAGE

IQ

VDO

RIPPLE REJECTION RATIO

OUTPUT CURRENT CAPACITY

Sinking

Sourcing

OUTPUT VOLTAGE NOISE

OUTPUT VOLTAGE NOISE

DENSITY

OUTPUT VOLTAGE HYSTERESIS

A, B, C Grade

RRR

IL

±0.02

1

±0.04

2

%

mV

%

mV

ΔVOUT_HYS

TA = temperature cycled from

+25°C to +125°C to−40°C to +25°C (full cycle)

25°C to 125°C to 25°C (half cycle)

25°C to 70°C to 0°C to 25°C (full cycle)

25°C to 70°C to 25°C (half cycle)

25°C to 70°C to 0°C to 25°C (full cycle)

25°C to 70°C to 25°C (half cycle)

TA = 25°C

250 hours (early life drift)

1000 hours

4500 hours

250 hours (early life drift)

1000 hours

4500 hours

COUT = 0.1 µF, CIN = 0.1 µF, RLOAD = 1 kΩ

ΔVOUT_LTD

tR

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/°C

ppm/V

80

120

12

9

950

100

300

ppm/mA

ppm/mA

ppm/mA

ppm/mA

μA

mV

mV

dB

−10

10

2.8

95.3

mA

mA

μV p-p

nV/√Hz

−13

−97

−8

−17

1

5

ppm

ppm

ppm

ppm

ppm

ppm

19

25

51

3

5

8

160

ppm

ppm

ppm

ppm

ppm

ppm

µs

µF

25

35

6

4

700

90

0.1

Rev. D | Page 9 of 40

%

0.8

1.6

1

2

2

4

4

8

10

1

IL = 0 mA to +10 mA source, −40°C ≤ TA ≤ +125°C

IL = 0 mA to −10 mA sink, −40°C ≤ TA ≤ +125°C

IL = 0 mA to +10 mA source, 0°C ≤ TA ≤ +70°C

IL = 0 mA to −10 mA sink, 0°C ≤ TA ≤ +70°C

−40°C ≤ TA ≤ +125°C, no load

−40°C ≤ TA ≤ +125°C, no load

−40°C ≤ TA ≤ +125°C, IL = 2 mA

fIN = 1 kHz

0.1 Hz to 10.0 Hz

1 kHz

D Grade

TURN-ON SETTLING TIME

LOAD CAPACITANCE

See Terminology section

0°C ≤ TA ≤ +70°C (box method)

0°C ≤ TA ≤ +70°C (bowtie method)

0°C ≤ TA ≤ +70°C (box method)

0°C ≤ TA ≤ +70°C (bowtie method)

−40°C ≤ TA ≤ +125°C (box method)

−40°C ≤ TA ≤ +125°C (bowtie method)

−40°C ≤ TA ≤ +125°C (box method)

−40°C ≤ TA ≤ +125°C (bowtie method)

−40°C ≤ TA ≤ +125°C

eNp-p

eN

D Grade

LONG-TERM DRIFT

A, B, C Grade

Unit

V

±0.02

C Grade

LINE REGULATION

LOAD REGULATION

A, B, C Grade

Max

100

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

Data Sheet

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

THERMAL RESISTANCE

Table 9.

Thermal performance is directly linked to printed circuit board

(PCB) design and operating environment. Close attention to

PCB thermal design is required.

Parameter

Supply Voltage

Operating Temperature Range

ADR4525, ADR4540, ADR4550

C and D Grade Only

Storage Temperature Range

Junction Temperature Range

Electrostatic Discharge (ESD) Human

Body Model (HBM)

Moisture Sensitivity Level Rating

Rating

16 V

−40°C to +125°C

0°C to 70°C

Table 10. Thermal Resistance

Package Type

8-Lead SOIC2

1-Layer JEDEC Board

2-Layer JEDEC Board

8- Lead LCC

−65°C to +150°C

−65°C to +150°C

6 kV

MSL-1

θJC1

Unit

N/A3

120

120

63

N/A3

N/A3

°C/W

°C/W

°C/W

For the θJC test, 100 μm thermal interface material (TIM) is used. TIM is

assumed to have 3.6 W/mK.

2

Thermal impedance simulated values are based on a JEDEC thermal test

board. See JEDEC JESD51.

3

N/A means not applicable.

1

Stresses at or above those listed under Absolute Maximum

Ratings may cause permanent damage to the product. This is a

stress rating only; functional operation of the product at these

or any other conditions above those indicated in the

operational section of this specification is not implied.

Operation beyond the maximum operating conditions for

extended periods may affect product reliability.

θJA

ESD CAUTION

Rev. D | Page 10 of 40

�Data Sheet

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

ADR4520/ADR4525/

ADR4530/ADR4533/

ADR4540/ADR4550

NIC 1

8

DNC

VIN 2

7

NIC

NIC 3

NOTES

1. NIC = NOT INTERNALLY CONNECTED.

THIS PIN IS NOT CONNECTED INTERNALLY.

2. DNC = DO NOT CONNECT. DO NOT CONNECT TO THIS PIN.

10203-002

6 VOUT

TOP VIEW

GND 4 (Not to Scale) 5 NIC

Figure 3. 8-Lead SOIC Pin Configuration

Table 11. 8-Lead SOIC Pin Function Descriptions

Pin No.

1

2

3

4

5

6

7

8

Mnemonic

NIC

VIN

NIC

GND

NIC

VOUT

NIC

DNC

Description

Not Internally Connected. This pin is not connected internally.

Input Voltage Connection.

Not Internally Connected. This pin is not connected internally.

Ground.

Not Internally Connected. This pin is not connected internally.

Output Voltage.

Not Internally Connected. This pin is not connected internally.

Do Not Connect. Do not connect to this pin.

ADR4520/ADR4525/

ADR4530/ADR4533/

ADR4540/ADR4550

DNC

8

DNC

1

7

VOUTFORCE

VIN

2

6

VOUTSENSE

GNDFORCE

3

5

NIC

4

10203-058

GNDSENSE

NOTES

1. NIC = NOT INTERNALLY CONNECTED.

THIS PIN IS NOT CONNECTED INTERNALLY.

2. DNC = DO NOT CONNECT. DO NOT CONNECT TO THIS PIN.

Figure 4. 8-Lead LCC Pin Configuration

Table 12. 8-Lead LCC Pin Function Descriptions

Pin No.

1

2

3

4

5

6

7

8

Mnemonic

NIC

VIN

GNDFORCE

GNDSENSE

NIC

VOUTSENSE

VOUTFORCE

DNC

Description

Not Internally Connected. This pin is not connected internally.

Input Voltage Connection.

Ground connection

Ground sensing connection. Connect directly to the ground connection of the load device

Not Internally Connected. This pin is not connected internally.

Reference Voltage Output.

Reference Voltage Output sensing connection. Connect directly to the voltage input of the load device

Do Not Connect. Do not connect to this pin.

Rev. D | Page 11 of 40

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

Data Sheet

TYPICAL PERFORMANCE CHARACTERISTICS

TA = 25°C, unless otherwise noted.

ADR4520

2.0485

35

ADR4520

ADR4520

2.0484

30

LOAD REGULATION (ppm/mA)

2.0483

2.0481

2.0480

2.0479

2.0478

2.0477

25

20

15

10

–30

–10

10

30

50

70

90

110

0

–60

10203-101

2.0475

–50

130

TEMPERATURE (°C)

–40

–20

0

20

40

60

80

100

120

140

TEMPERATURE (°C)

Figure 5. ADR4520 B Grade Output Voltage vs. Temperature

10203-107

5

2.0476

Figure 8. ADR4520 Load Regulation vs. Temperature (Sourcing)

100

ADR4520

ADR4520

90

LOAD REGULATION (ppm/mA)

VIN (5V/DIV)

1

VOUT (1V/DIV)

CH2 1.00V

M40.0µs

A CH1

9.10V

70

60

50

40

30

20

0

–60

–40

–20

0

20

40

60

80

100

120

140

TEMPERATURE (°C)

Figure 6. ADR4520 Output Voltage Start-Up Response

1.6

10203-108

CH1 5.00V

80

10

10203-104

CIN = 0.1µF

COUT = 0.1µF

RL = 1kΩ

2

Figure 9. ADR4520 Load Regulation vs. Temperature (Sinking)

1.4

ADR4520

ADR4520

1.3

1.4

+125°C

1.2

LINE REGULATION (ppm/V)

1.2

+25°C

1.0

–40°C

0.8

0.6

0.4

1.1

1.0

0.9

0.8

0.7

0.6

0.2

–10

–8

–6

–4

–2

0

2

4

6

8

ILOAD (mA)

10

0.4

–60

–40

–20

0

20

40

60

80

100

120

TEMPERATURE (°C)

Figure 7. ADR4520 Dropout Voltage vs. Load Current

Figure 10. ADR4520 Line Regulation vs. Temperature

Rev. D | Page 12 of 40

140

10203-109

0.5

0

10203-106

DROPOUT VOLTAGE (V)

VOUT (V)

2.0482

�Data Sheet

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

1000

1k

ADR4520

ADR4520

+125°C

ISY (µA)

+25°C

–40°C

400

0

0

1

2

3

4

5

6

7

8

9

10 11 12 13 14 15 16

VIN (V)

10

1

0.01

10203-110

200

100

10

100

1k

10k

100k

Figure 13. ADR4520 Output Noise Spectral Density

0

ADR4520

–10 CLOAD = 1µF

ADR4520

RIPPLE REJECTION RATIO (dB)

100

80

60

40

20

–20

–30

–40

–50

–60

–70

–80

–90

–100

0.4

0.7

1.0

1.3

1.6

1.9

2.2

2.5

OUTPUT VOLTAGE NOISE DISTRIBUTION (µV p-p)

2.8

–120

10

100

1k

10k

100k

1M

10M

100M

FREQUENCY (Hz)

Figure 12. ADR4520 Output Voltage Noise

(Maximum Amplitude from 0.1 Hz to 10 Hz)

Figure 14. ADR4520 Ripple Rejection Ratio vs. Frequency

Rev. D | Page 13 of 40

10203-113

–110

0

10203-111

OCCURRENCE

1

FREQUENCY (Hz)

Figure 11. ADR4520 Supply Current (ISY) vs. Supply Voltage

120

0.1

10203-112

600

NOISE DENSITY (nV rms/ Hz)

800

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

Data Sheet

80

ADR4520

T

70

NUMBER OF UNITS

60

INPUT

2

W

M40.0µs

T 12.0%

A CH1

7.02V

0

–0.06

RL = 100kΩ

CL = 10µF

RL = 100kΩ

CL = 1µF

10

0

10

100

1k

10k

100k

FREQUENCY (Hz)

1M

10203-115

OUTPUT IMPEDANCE (Ω)

RL = 1kΩ

CL = 1µF

30

20

0

0.02

0.04

0.06

Figure 17. ADR4520 Solder Heat Resistance Shift (3 × Reflow)

50

RL = 1kΩ

CL = 10µF

–0.02

SOLDER HEAT SHIFT (%)

ADR4520

40

–0.04

Figure 16. ADR4520 Output Impedance vs. Frequency

Rev. D | Page 14 of 40

10203-716

B

10203-114

CH2 1.00mV

Figure 15. ADR4520 Line Transient Response

60

30

10

CIN = 0.1µF

COUT = 1µF

CH1 1.00V

40

20

OUTPUT AC

1

50

�Data Sheet

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

ADR4525

2.5005

ADR4525

ADR4525

2.5004

VIN (5V/DIV)

2.5003

VOUT (V)

2.5002

2.5001

2.5000

1

VOUT (1V/DIV)

2.4999

2.4998

2.4997

2

–30

–10

10

30

50

70

90

110

130

TEMPERATURE (°C)

CH1 5.00V

M40.0µs

A CH1

9.10V

Figure 21. ADR4525 Output Voltage Start-Up Response

Figure 18. ADR4525 B Grade Output Voltage vs. Temperature

2.49980

1.4

ADR4525

1.2

DROPOUT VOLTAGE (V)

2.49975

OUTPUT VOLTAGE (V)

CH2 1.00V

10203-204

2.4995

–50

10203-201

2.4996

2.49970

2.49965

2.49960

+125°C

+25°C

1.0

0.8

–40°C

0.6

0.4

2.49955

0

10

20

30

40

50

60

70

TEMPERATURE (°C)

0

–15

–10

–5

0

5

10

15

ILOAD (mA)

10203-206

2.49950

10203-817

0.2

Figure 22. ADR4525 Dropout Voltage vs. Load Current

Figure 19. ADR4525 C Grade Output Voltage vs. Temperature

2.50010

35

ADR4525

LOAD REGULATION (ppm/mA)

30

2.50000

2.49995

2.49990

2.49985

2.49980

2.49975

25

20

15

10

2.49970

0

10

20

30

40

50

60

TEMPERATURE (°C)

70

0

–60

–40

–20

0

20

40

60

80

100

120

140

TEMPERATURE (°C)

Figure 20. ADR4525 D Grade Output Voltage vs. Temperature

Figure 23. ADR4525 Load Regulation vs. Temperature (Sourcing)

Rev. D | Page 15 of 40

10203-207

5

10203-926

D GRADE OUTPUT VOLTAGE (V)

2.50005

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

Data Sheet

160

100

ADR4525

ADR4525

140

80

120

70

OCCURRENCE

LOAD REGULATION (ppm/mA)

90

60

50

40

30

100

80

60

40

20

20

0

–40

–20

0

20

40

60

80

100

120

140

TEMPERATURE (°C)

0.6

10203-208

0

–60

1.2

1.5

1.8

2.1

2.4

2.7

3.0

Figure 27. ADR4525 Output Voltage Noise

(Maximum Amplitude from 0.1 Hz to 10 Hz)

Figure 24. ADR4525 Load Regulation vs. Temperature (Sinking)

1.4

0.9

OUTPUT VOLTAGE NOISE DISTRIBUTION (µV p-p)

10203-211

10

1k

ADR4525

ADR4525

1.3

NOISE DENSITY (nV rms/ Hz)

LINE REGULATION (ppm/V)

1.2

1.1

1.0

0.9

0.8

0.7

0.6

100

10

–40

–20

0

20

40

60

80

100

120

140

TEMPERATURE (°C)

1

0.01

10203-209

0.4

–60

100

1k

10k

100k

0

ADR4525

–10

RIPPLE REJECTION RATIO (dB)

800

700

600

+25°C –40°C

500

400

300

200

100

–20

–30

–40

–50

–60

–70

–80

–90

–100

0

1

2

3

4

5

6

7

8

9

10 11 12 13 14 15 16

VIN (V)

–120

10

100

1k

10k

100k

1M

10M

100M

FREQUENCY (Hz)

Figure 29. ADR4525 Ripple Rejection Ratio vs. Frequency

Figure 26. ADR4525 Supply Current vs. Supply Voltage

Rev. D | Page 16 of 40

10203-213

–110

0

10203-210

ISY (µA)

10

Figure 28. ADR4525 Output Noise Spectral Density

ADR4525

+125°C

1

FREQUENCY (Hz)

Figure 25. ADR4525 Line Regulation vs. Temperature

900

0.1

10203-212

0.5

�Data Sheet

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

80

ADR4525

T

70

NUMBER OF UNITS

60

INPUT

2

OUTPUT AC

1

50

40

30

20

CH2 1.00mV

B

W

M200µs

T 10.0%

A CH1

4.08V

0

–0.06

10203-214

–0.04

0

–0.02

Figure 30. ADR4525 Line Transient Response

VIN = 4V PART 2

5mA

IOUT

0mA

IOUT

0mA

–5mA

VOUT

100mV/DIV

10203-920

VOUT

100mV/DIV

200µs/DIV

200µs/DIV

Figure 34. ADR4525 A, B C Grade Load Transient Response (Sourcing)

Figure 31. ADR4525 A, B C Grade Load Transient Response (Sinking)

40

ADR4525

VIN = 4V

SINKING

35

LOAD REGULATION (ppm/mA)

70

RL = 1kΩ

CL = 1µF

60

50

RL = 1kΩ

CL = 10µF

40

RL = 100kΩ

CL = 1µF

30

RL = 100kΩ

CL = 10µF

20

30

25

20

15

10

0

10

100

1k

10k

100k

FREQUENCY (Hz)

Figure 32. ADR4525 Output Impedance vs. Frequency

1M

0

0

10

20

30

40

TEMPERATURE (°C)

50

60

70

10203-923

5

10

10203-215

OUTPUT IMPEDANCE (Ω)

0.06

Figure 33. ADR4525 Solder Heat Resistance Shift (3 × Reflow)

VIN = 4V PART 1

80

0.04

0.02

SOLDER HEAT SHIFT (%)

10203-919

CH1 1.00V

10203-731

10

CIN = 0.1µF

COUT = 1µF

Figure 35. ADR4525 D Grade Load Regulation vs. Temperature (Sinking)

Rev. D | Page 17 of 40

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

Data Sheet

VIN = 4V PART 1

VIN = 4V PART 1

5mA

IOUT

0mA

IOUT

0mA

–5mA

VOUT

100mV/DIV

200µs/DIV

Figure 36. ADR4525 D Grade Load Transient Response (Sinking)

Figure 38. ADR4525 D Grade Load Transient Response (Sourcing)

40

VIN = 4V

SOURCING

LOAD REGULATION (ppm/mA)

35

30

25

20

15

10

0

10

20

30

40

TEMPERATURE (°C)

50

60

70

10203-918

5

0

200µs/DIV

Figure 37. ADR4525 D Grade Load Regulation vs. Temperature (Sourcing)

Rev. D | Page 18 of 40

10203-916

10203-917

VOUT

100mV/DIV

�Data Sheet

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

ADR4530

3.0005

35

ADR4530

ADR4530

3.0004

30

LOAD REGULATION (ppm/mA)

3.0003

VOUT (V)

3.0002

3.0001

3.0000

2.9999

2.9998

2.9997

25

20

15

10

5

–30

–10

10

30

50

70

90

110

0

–60

10203-301

2.9995

–50

130

TEMPERATURE (°C)

–40

–20

0

20

40

60

80

100

120

140

TEMPERATURE (°C)

Figure 39. ADR4530 B Grade Output Voltage vs. Temperature

10203-307

2.9996

Figure 42. ADR4530 Load Regulation vs. Temperature (Sourcing)

100

ADR4530

ADR4530

VIN (5V/DIV)

LOAD REGULATION (ppm/mA)

90

1

2

VOUT (1V/DIV)

CH2 1.00V

M40.0µs

A CH1

3.10V

60

50

40

30

20

0

–60

–40

–20

0

20

40

60

80

100

120

140

TEMPERATURE (°C)

Figure 40. ADR4530 Output Voltage Start-Up Response

1.4

10203-308

CH1 5.00V

70

10

10203-304

CIN = 0.1µF

COUT = 0.1µF

RL = 1kΩ

80

Figure 43. ADR4530 Load Regulation vs. Temperature (Sinking)

1.4

ADR4530

ADR4530

1.3

1.2

+125°C

LINE REGULATION (ppm/V)

+25°C

0.8

–40°C

0.6

0.4

1.1

1.0

0.9

0.8

0.7

0.6

0.2

–10

–5

0

5

10

ILOAD (mA)

15

0.4

–60

–40

–20

0

20

40

60

80

100

120

TEMPERATURE (°C)

Figure 44. ADR4530 Line Regulation vs. Temperature

Figure 41. ADR4530 Dropout Voltage vs. Load Current

Rev. D | Page 19 of 40

140

10203-309

0.5

0

–15

10203-306

DROPOUT VOLTAGE (V)

1.2

1.0

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

900

1k

ADR4530

–40°C

Data Sheet

ADR4530

NOISE DENSITY (nV rms/ Hz)

800

700

+125°C

ISY (µA)

600

+25°C

500

400

300

200

100

10

1

2

3

4

5

6

7

8

9

10

11

12

VIN (V)

13

1

0.01

1

10

100

1k

10k

100k

FREQUENCY (Hz)

Figure 45. ADR4530 Supply Current vs. Supply Voltage

Figure 47. ADR4530 Output Noise Spectral Density

100

0

ADR4530

ADR4530

–10

RIPPLE REJECTION RATIO (dB)

90

80

70

60

50

40

30

20

–20

–30

–40

–50

–60

–70

–80

–90

–100

10203-311

OUTPUT VOLTAGE NOISE DISTRIBUTION (µV p-p)

2.9

2.7

2.5

2.3

2.1

1.9

–120

1.7

0

1.5

–110

1.3

10

1.1

OCCURRENCE

0.1

1

10

100

1k

10k

100k

1M

10M

100M

FREQUENCY (Hz)

Figure 46. ADR4530 Output Voltage Noise

(Maximum Amplitude from 0.1 Hz to 10 Hz)

Figure 48. ADR4530 Ripple Rejection Ratio vs. Frequency

Rev. D | Page 20 of 40

10203-313

0

10203-310

0

10203-312

100

�Data Sheet

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

80

ADR4530

T

70

NUMBER OF UNITS

60

INPUT

2

OUTPUT AC

M200µs

T 10.0%

A CH1

7.02V

0

–0.06

40

RL = 1kΩ

CL = 1µF

RL = 100kΩ

CL = 1µF

10

0

1

10

100

1k

10k

100k

1M

FREQUENCY (Hz)

10M

10203-315

OUTPUT IMPEDANCE (Ω)

50

RL = 100kΩ

CL = 10µF

0

0.02

0.04

0.06

Figure 51. ADR4530 Solder Heat Resistance Shift (3 × Reflow)

ADR4530

20

–0.02

SOLDER HEAT SHIFT (%)

Figure 49. ADR4530 Line Transient Response

RL = 1kΩ

CL = 10µF

–0.04

Figure 50. ADR4530 Output Impedance vs. Frequency

Rev. D | Page 21 of 40

10203-747

W

10203-314

B

CH2 1.00mV

30

30

10

1

60

40

20

CIN = 0.1µF

COUT = 1µF

CH1 1.00V

50

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

Data Sheet

ADR4533

3.3010

35

ADR4533

ADR4533

3.3008

30

LOAD REGULATION (ppm/mA)

3.3006

VOUT (V)

3.3004

3.3002

3.3000

3.2998

3.2996

3.2994

25

20

15

10

5

–30

–10

10

30

50

70

90

110

0

–60

10203-401

3.2990

–50

130

TEMPERATURE (°C)

–40

–20

0

20

40

60

80

100

120

140

TEMPERATURE (°C)

Figure 52. ADR4533 B Grade Output Voltage vs. Temperature

10203-407

3.2992

Figure 55. ADR4533 Load Regulation vs. Temperature (Sourcing)

100

ADR4533

ADR4533

90

LOAD REGULATION (ppm/mA)

1

2

VOUT (1V/DIV)

CH1 5.00V

CH2 1.00V

M40.0µs

A CH1

3.10V

70

60

50

40

30

20

10

10203-404

CIN = 0.1µF

COUT = 0.1µF

RL = 1kΩ

80

0

–60

–40

–20

0

20

40

60

80

100

120

140

TEMPERATURE (°C)

Figure 53. ADR4533 Output Voltage Start-Up Response

1.0

Figure 56. ADR4533 Load Regulation vs. Temperature (Sinking)

1.2

ADR4533

ADR4533

1.1

+125°C

0.8

LINE REGULATION (ppm/V)

1.0

+25°C

0.6

–40°C

0.4

0.2

0.9

0.8

0.7

0.6

0.5

0.4

–10

–5

0

5

10

ILOAD (mA)

15

Figure 54. ADR4533 Dropout Voltage vs. Load Current

0.2

–60

–40

–20

0

20

40

60

80

100

120

TEMPERATURE (°C)

Figure 57. ADR4533 Line Regulation vs. Temperature

Rev. D | Page 22 of 40

140

10203-409

0.3

0

–15

10203-406

DROPOUT VOLTAGE (V)

10203-408

VIN (5V/DIV)

�Data Sheet

900

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

1k

ADR4533

ADR4533

+125°C

NOISE DENSITY (nV rms/ Hz)

800

700

+25°C

ISY (µA)

600

–40°C

500

400

300

200

100

10

0

1

2

3

4

5

6

7

8

9 10 11 12 13 14 15 16

VIN (V)

1

0.01

10203-410

0

1

10

100

1k

10k

100k

FREQUENCY (Hz)

Figure 58. ADR4533 Supply Current vs. Supply Voltage

Figure 60. ADR4533 Output Noise Spectral Density

60

0

ADR4533

ADR4533

–10

–20

RIPPLE REJECTION RATIO (dB)

50

40

30

20

–30

–40

–50

–60

–70

–80

–90

–100

–110

10

–130

10

100

1k

10k

100k

1M

10M

100M

FREQUENCY (kHz)

Figure 61. ADR4533 Ripple Rejection Ratio vs. Frequency

Figure 59. ADR4533 Output Voltage Noise

(Maximum Amplitude from 0.1 Hz to 10 Hz)

Rev. D | Page 23 of 40

10203-413

10203-411

OUTPUT VOLTAGE NOISE DISTRIBUTION (µV p-p)

3.4

3.2

3.0

2.8

2.6

2.4

2.2

2.0

1.8

0

1.6

–120

BIN

OCCURRENCE

0.1

10203-412

100

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

Data Sheet

80

ADR4533

T

70

NUMBER OF UNITS

60

INPUT

2

OUTPUT AC

M200µs

T 12.0%

A CH1

7.02V

0

–0.06

40

RL = 1kΩ

CL = 1µF

RL = 100kΩ

CL = 1µF

10

0

1

10

100

1k

10k

100k

1M

FREQUENCY (Hz)

10M

10203-415

OUTPUT IMPEDANCE (Ω)

50

RL = 100kΩ

CL = 10µF

0

0.02

0.04

0.06

Figure 64. ADR4533 Solder Heat Resistance Shift (3 × Reflow)

ADR4533

20

–0.02

SOLDER HEAT SHIFT (%)

Figure 62. ADR4533 Line Transient Response

RL = 1kΩ

CL = 10µF

–0.04

Figure 63. ADR4533 Output Impedance vs. Frequency

Rev. D | Page 24 of 40

10203-762

W

10203-414

B

CH2 1.00mV

30

30

10

1

60

40

20

CIN = 0.1µF

COUT = 1µF

CH1 1.00V

50

�Data Sheet

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

ADR4540

4.0970

ADR4540

ADR4540

VIN (5V/DIV)

4.0965

VOUT (V)

1

4.0960

2

4.0955

VOUT (1V/DIV)

–30

–10

10

30

50

70

90

110

130

TEMPERATURE (°C)

CH1 5.00V

Figure 65. ADR4540 B Grade Output Voltage vs. Temperature

CH2 1.00V

M40.0µs

A CH1

10203-504

4.0950

–50

10203-501

CIN = 0.1µF

COUT = 0.1µF

RL = 1kΩ

3.10V

Figure 68. ADR4540 Output Voltage Start-Up Response

0.8

VSY = 7V

ADR4540

4.09555

0.7

DROPOUT VOLTAGE (V)

4.09550

4.09545

4.09540

+25°C

0.5

0.3

0.2

4.09535

20

30

40

50

60

70

TEMPERATURE (°C)

0

–15

–5

0

5

10

15

ILOAD (mA)

Figure 69. ADR4540 Dropout Voltage vs. Load Current

Figure 66. ADR4540 C Grade Output Voltage vs. Temperature

35

4.09610

ADR4540

4.09605

30

LOAD REGULATION (ppm/mA)

4.09600

4.09595

4.09590

4.09585

4.09580

4.09575

4.09570

25

20

15

10

5

0

10

20

30

40

50

60

70

TEMPERATURE (°C)

Figure 67. ADR4540 D Grade Output Voltage vs. Temperature

10203-924

4.09565

4.09560

–10

10203-506

10

10203-901

0.1

0

VOUT REFERENCE (V)

–40°C

0.4

0

–60

–40

–20

0

20

40

60

80

100

120

140

TEMPERATURE (°C)

Figure 70. ADR4540 Load Regulation vs. Temperature (Sourcing)

Rev. D | Page 25 of 40

10203-507

OUTPUT VOLTAGE (V)

+125°C

0.6

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

Data Sheet

70

100

ADR4540

ADR4540

90

80

50

70

OCCURRENCE

LOAD REGULATION (ppm/mA)

60

60

50

40

30

40

30

20

20

10

OUTPUT VOLTAGE NOISE DISTRIBUTION (µV p-p)

Figure 71. ADR4540 Load Regulation vs. Temperature (Sinking)

1.0

10203-511

TEMPERATURE (°C)

0

3.9

140

3.7

120

3.5

100

3.3

80

3.1

60

2.9

40

2.7

20

2.5

0

2.3

–20

2.1

–40

10203-508

0

–60

BIN

10

Figure 74. ADR4540 Output Voltage Noise

(Maximum Amplitude from 0.1 Hz to 10 Hz)

1k

ADR4540

ADR4540

0.9

NOISE DENSITY (nV rms/ Hz)

LINE REGULATION (ppm/V)

0.8

0.7

0.6

0.5

0.4

0.3

0.2

100

10

–40

–20

0

20

40

60

80

100

120

140

TEMPERATURE (°C)

1

0.01

10203-509

0

–60

ADR4540

+125°C

700

+25°C

500

400

300

200

100

0

1

2

3

4

5

6

7

8

9

10 11 12 13 14 15 16

VIN (V)

10203-510

ISY (µA)

–40°C

0

10

100

1k

10k

Figure 75. ADR4540 Output Noise Spectral Density

800

600

1

FREQUENCY (Hz)

Figure 72. ADR4540 Line Regulation vs. Temperature

900

0.1

Figure 73. ADR4540 Supply Current vs. Supply Voltage

Rev. D | Page 26 of 40

100k

10203-512

0.1

�Data Sheet

0

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

60

ADR4540

ADR4540

–20

50

–30

OUTPUT IMPEDANCE (Ω)

RIPPLE REJECTION RATIO (dB)

–10

–40

–50

–60

–70

–80

–90

RL = 100kΩ

CL = 1µF

40

RL = 100kΩ

CL = 10µF

30

RL = 1kΩ

CL = 10µF

20

RL = 1kΩ

CL = 1µF

10

–100

0

1k

10k

100k

1M

10M

100M

FREQUENCY (Hz)

1

10203-513

100

10

100

1k

10k

100k

1M

10M

FREQUENCY (Hz)

Figure 76. ADR4540 Ripple Rejection Ratio vs. Frequency

10203-515

–110

–120

10

Figure 79. ADR4540 Output Impedance vs. Frequency

80

ADR4540

T

70

NUMBER OF UNITS

60

INPUT

2

OUTPUT AC

50

40

30

20

CH2 1.00mV

B

W

M200µs

T 12.0%

A CH1

7.02V

0

–0.06

–0.04

–0.02

0

0.02

0.04

0.06

SOLDER HEAT SHIFT (%)

Figure 77. ADR4540 Line Transient Response

Figure 80. ADR4540 Solder Heat Resistance Shift (3 × Reflow)

VIN = 5.6V PART 1

VIN = 5.6V PART 3

5mA

IOUT

0mA

IOUT

0mA

–5mA

VOUT

100mV/DIV

200µs/DIV

10203-914

VOUT

100mV/DIV

Figure 78. ADR4540 A, B, C Grade Load Transient Response (Sinking)

200µs/DIV

10203-913

CH1 1.00V

10203-514

1

10203-777

10

CIN = 0.1µF

COUT = 1µF

Figure 81. ADR4540 A, B, C Grade Load Transient Response (Sourcing)

Rev. D | Page 27 of 40

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

6.0

15

VIN = 5.6V

5.5

SOURCING

VIN = 5.6V

14

SOURCING

13

5.0

LOAD REGULATION (ppm/mA)

4.5

4.0

3.5

3.0

2.5

2.0

1.5

1.0

12

11

10

9

8

7

6

5

4

3

0

0

10

20

30

40

50

60

70

TEMPERATURE (°C)

10203-912

1

0

Figure 82. ADR4540 D Grade Load Regulation vs. Temperature (Sinking)

0

10

20

30

40

50

60

70

TEMPERATURE (°C)

10203-911

2

0.5

Figure 84. ADR4540 D Grade Load Regulation vs. Temperature (Sourcing)

VIN = 5.6V PART 1

VIN = 4V PART 1

5mA

IOUT

0mA

IOUT

0mA

–5mA

VOUT

100mV/DIV

200µs/DIV

10203-917

VOUT

100mV/DIV

Figure 83. ADR4540 D Grade Load Transient Response (Sinking)

200µs/DIV

Figure 85. ADR4540 D Grade Load Transient Response (Sourcing)

Rev. D | Page 28 of 40

10203-909

LOAD REGULATION (ppm/mA)

Data Sheet

�Data Sheet

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

ADR4550

5.0010

ADR4550

ADR4550

VIN (5V/DIV)

5.0005

VOUT (V)

VOUT (1V/DIV)

5.0000

1

4.9995

–30

–10

10

30

50

70

90

110

130

TEMPERATURE (°C)

CH1 5.00V

Figure 86. ADR4550 B Grade Output Voltage vs. Temperature

CH2 1.00V

M40.0µs

A CH1

9.10V

10203-604

4.9990

–50

10203-601

2

Figure 89. ADR4550 Output Voltage Start-Up Response

0.7

ADR4550

VSY = 7V

4.99920

+125°C

0.6

DROPOUT VOLTAGE (V)

OUTPUT VOLTAGE (V)

+25°C

4.99915

4.99910

4.99905

0.5

0.4

–40°C

0.3

0.2

0.1

10

20

30

40

50

60

70

TEMPERATURE (°C)

0

–15

10203-902

0

–5

–10

0

5

15

10

ILOAD (mA)

10203-606

4.99900

Figure 90. ADR4550 Dropout Voltage vs. Load Current

Figure 87. ADR4550 C Grade Output Voltage vs. Temperature

4.09680

35

ADR4550

4.09675

30

LOAD REGULATION (ppm/mA)

4.09565

4.09560

4.99955

4.99950

4.99945

4.99940

20

15

10

0

10

20

30

40

50

60

70

TEMPERATURE (°C)

0

–60

–40

–20

0

20

40

60

80

100

120

140

TEMPERATURE (°C)

Figure 88. ADR4550 D Grade Output Voltage vs. Temperature

Figure 91. ADR4550 Load Regulation vs. Temperature (Sourcing)

Rev. D | Page 29 of 40

10203-607

4.99930

25

5

4.99935

10203-924

VOUT REFERENCE (V)

4.09670

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

Data Sheet

9

100

ADR4550

ADR4550

8

80

7

70

OCCURRENCE

60

50

40

6

5

4

3

30

2

20

1

10

–40

–20

0

20

40

60

80

100

120

140

TEMPERATURE (°C)

0

10203-608

0

–60

2.1

2.3

2.5

2.7

2.9

3.1

3.3

3.5

3.7

OUTPUT VOLTAGE NOISE DISTRIBUTION (µV p-p)

Figure 92. ADR4550 Load Regulation vs. Temperature (Sinking)

1.0

1.9

10203-611

LOAD REGULATION (ppm/mA)

90

Figure 95. ADR4550 Output Voltage Noise

(Maximum Amplitude from 0.1 Hz to 10 Hz)

1k

ADR4550

ADR4550

0.9

NOISE DENSITY (nV rms/ Hz)

LINE REGULATION (ppm/V)

0.8

0.7

0.6

0.5

0.4

0.3

0.2

100

10

0

50

100

150

TEMPERATURE (°C)

ADR4550

+125°C

800

700

+25°C

–40°C

500

400

300

200

100

0

0

1

2

3

4

5

6

7

8

9

10 11 12 13 14 15 16

VIN (V)

10203-610

ISY (µA)

600

0.1

1

10

100

1k

10k

FREQUENCY (Hz)

Figure 96. ADR4550 Output Noise Spectral Density

Figure 93. ADR4550 Line Regulation vs. Temperature

900

1

0.01

Figure 94. ADR4550 Supply Current vs. Supply Voltage

Rev. D | Page 30 of 40

100k

10203-612

0

–50

10203-609

0.1

�Data Sheet

140

ADR4550

RL = 100kΩ

CL = 0.1µF

ADR4550

120

OUTPUT IMPEDANCE (Ω)

–20

–40

–60

–80

–100

RL = 100kΩ

CL = 1µF

100

80

RL = 1kΩ

CL = 0.1µF

60

40

RL = 1kΩ

CL = 1µF

–120

10

100

1k

10k

100k

1M

10M

100M

FREQUENCY (Hz)

0

10

100

1k

10k

1M

100k

FREQUENCY (Hz)

10203-615

20

10203-613

RIPPLE REJECTION RATIO (dB)

0

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

Figure 100. ADR4550 Output Impedance vs. Frequency

Figure 97. ADR4550 Ripple Rejection Ratio vs. Frequency

80

ADR4550

T

70

NUMBER OF UNITS

60

INPUT

2

50

40

30

20

OUTPUT AC

CH2 1.00mV

B

W

M200µs

T 12.0%

A CH1

7.02V

0

–0.06

–0.04

–0.02

0

0.02

0.04

0.06

SOLDER HEAT SHIFT (%)

Figure 101. ADR4550 Solder Heat Resistance Shift (3 × Reflow)

Figure 98. ADR4550 Line Transient Response

VIN = 6.5V PART 3

VIN = 6.5V PART 3

5mA

IOUT

0mA

IOUT

0mA

–5mA

VOUT

100mV/DIV

200µs/DIV

10203-908

VOUT

100mV/DIV

Figure 99. ADR4550 A, B, C Grade Load Transient Response (Sinking)

200µs/DIV

10203-907

CH1 1.00V

10203-614

1

10203-792

10

CIN = 0.1µF

COUT = 1µF

Figure 102. ADR4550 A, B, C Grade Load Transient Response (Sourcing)

Rev. D | Page 31 of 40

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

4.0

5.0

VIN = 6.5V

VIN = 6.5V

SINKING

4.5

LOAD REGULATION (ppm/mA)

3.5

3.0

2.5

2.0

1.5

1.0

0.5

SOURCING

4.0

3.5

3.0

2.5

2.0

1.5

1.0

0

10

20

30

40

50

60

70

TEMPERATURE (°C)

0

10203-906

0

0

10

20

30

40

50

60

70

TEMPERATURE (°C)

10203-905

0.5

Figure 105. ADR4550 D Grade Load Regulation (Sourcing)

Figure 103. ADR4550 D Grade Load Regulation (Sinking)

VIN = 6.5V PART 2

VIN = 6.5V PART 1

5mA

IOUT

0mA

IOUT

0mA

–5mA

VOUT

100mV/DIV

200µs/DIV

Figure 104. ADR4550 D Grade Load Transient Response (Sinking)

10203-904

VOUT

100mV/DIV

200µs/DIV

Figure 106. ADR4550 D Grade Load Transient Response (Sourcing)

Rev. D | Page 32 of 40

10203-903

LOAD REGULATION (ppm/mA)

Data Sheet

�Data Sheet

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

TERMINOLOGY

Dropout Voltage (VDO)

Dropout voltage, sometimes referred to as supply voltage headroom or supply output voltage differential, is defined as the

minimum voltage differential between the input and output such

that the output voltage is maintained to within 0.1% accuracy.

VDO = (VIN − VOUT)min|IL = constant

Because the dropout voltage depends on the current passing

through the device, it is always specified for a given load current.

In series mode devices, the dropout voltage typically increases

proportionally to the load current (see Figure 7, Figure 22,

Figure 41, Figure 54, Figure 69, and Figure 90).

Line Regulation

Line regulation refers to the change in output voltage in response

to a given change in input voltage and is expressed in percent

per volt, ppm per volt, or μV per volt change in input voltage.

This parameter accounts for the effects of self heating.

Load Regulation

Load regulation refers to the change in output voltage in response

to a given change in load current and is expressed in μV per mA,

ppm per mA, or ohms of dc output resistance. This parameter

accounts for the effects of self heating.

Solder Heat Resistance (SHR) Shift

SHR shift refers to the permanent shift in output voltage that is

induced by exposure to reflow soldering and is expressed as a

percentage of the output voltage. This shift is caused by changes

in the stress exhibited on the die by the package materials when

these materials are exposed to high temperatures. This effect is

more pronounced in lead-free soldering processes due to higher

reflow temperatures. SHR is calculated after three solder reflow

cycles to simulate the worst case conditions when assembling a

two-sided PCB with surface mount components with one additional rework cycle. The reflow cycles use the JEDEC standard

reflow temperature profile.

Temperature Coefficient (TCVOUT)

The temperature coefficient relates the change in the output

voltage to the change in the ambient temperature of the device, as

normalized by the output voltage at 25°C. The TCVOUT for the

ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

A grade and B grade is fully tested over three temperatures:

−40°C, +25°C, and +125°C. The TCVOUT for the C grade and D

grade is fully tested over three temperatures: 0°C, +25°C, and

+70°C. This parameter is specified using two methods. The box

method is the most common method and accounts for the

temperature coefficient over the full temperature range,

whereas the bowtie method calculates the worst case slope from

+25°C and is therefore more useful for systems which are

calibrated at +25°C.

Box Method

The box method is represented by the following equation:

TCVOUT =

max{VOUT (T1 , T2 , T3 )} − min{VOUT (T1 , T2 , T3 )}

VOUT (T2 ) × (T3 − T1 )

× 10 6

where:

TCVOUT is expressed in ppm/°C.

VOUT(TX) is the output voltage at Temperature TX.

T1 = −40°C.

T2 = +25°C.

T3 = +125°C.

This box method ensures that TCVOUT accurately portrays the

maximum difference between any of the three temperatures at

which the output voltage of the device is measured.

Bowtie Method

The bowtie method is represented by the following equation:

TCVOUT = |max{TCVOUT1, TCVOUT2}|

where:

TCVOUT 1 =

max{VOUT (T1 , T2 )} − min{VOUT (T1 , T2 )}

× 10 6

VOUT (T2 ) × (T2 − T1 )

TCVOUT 2 =

max{VOUT (T2 , T3 )} − min{VOUT (T2 , T3 )}

× 10 6

VOUT (T2 ) × (T3 − T2 )

TCVOUT is expressed in ppm/°C.

VOUT(TX) is the output voltage at Temperature TX.

T1 = 0°C.

T2 = +25°C.

T3 = +70°C.

Thermally Induced Output Voltage Hysteresis (ΔVOUT_HYS)

Thermally induced output voltage hysteresis represents the

change in the output voltage after the device is exposed to a

specified temperature cycle. This is expressed as a difference in

ppm from the nominal output.

∆

=

VOUT _ HYS

VOUT1_25°C − VOUT2_25°C

× 106[ppm]

VOUT_25°C

where:

VOUT1_25°C is the output voltage at 25°C.

VOUT2_25°C is the output voltage after temperature cycling.

Long-Term Stability (ΔVOUT_LTD)

Long-term stability refers to the shift in the output voltage versus

time. This is expressed as a difference in ppm from the nominal

output.

∆VOUT _ LTD =

VOUT (t 1 ) − VOUT (t 0 )

VOUT (t 0 )

× 10 6 [ppm]

where:

VOUT(t0) is the VOUT at the starting time of the measurement.

VOUT(t1) is the VOUT at the end time of the measurement.

Rev. D | Page 33 of 40

�ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550

Data Sheet

APPLICATIONS INFORMATION

BASIC VOLTAGE REFERENCE CONNECTION

POWER DISSIPATION

The circuit shown in Figure 107 shows the basic configuration

for the ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/

ADR4550 family of voltage references.

The ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/

ADR4550 voltage references are capable of sourcing and sinking