DS1743/DS1743P

Y2K-Compliant, Nonvolatile Timekeeping

RAMs

www.maxim-ic.com

FEATURES

PIN CONFIGURATIONS

Integrated NV SRAM, Real-Time Clock,

Crystal, Power-Fail Control Circuit, and

Lithium Energy Source

Clock Registers are Accessed Identically to

the Static RAM. These Registers Reside in

the Eight Top RAM Locations.

Century Byte Register

Totally Nonvolatile with Over 10 Years of

Operation in the Absence of Power

BCD-Coded Century, Year, Month, Date,

Day, Hours, Minutes, and Seconds with

Automatic Leap Year Compensation Valid

through 2099

Low-Battery-Voltage Level Indicator Flag

Power-Fail Write Protection Allows for ±10%

VCC Power-Supply Tolerance

Lithium Energy Source is Electrically

Disconnected to Retain Freshness Until

Power is Applied for the First Time

DIP Module Only

Standard JEDEC Bytewide 8k x 8 Static

RAM Pinout

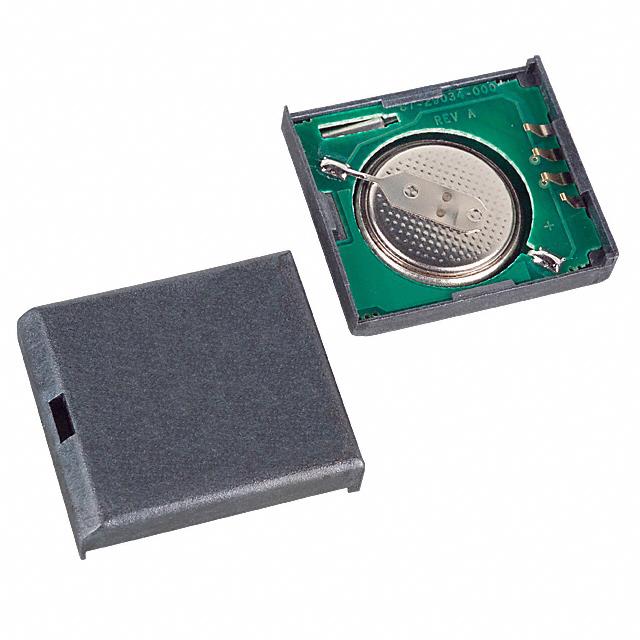

PowerCap Module Board Only

Surface-Mountable Package for Direct

Connection to PowerCap Containing

Battery and Crystal

Replaceable Battery (PowerCap)

Power-On Reset Output

Pin-for-Pin Compatible with Other Densities

of DS174XP Timekeeping RAM

Underwriters Laboratories (UL) Recognized

to Prevent Charging of the Internal Lithium

Battery

TOP VIEW

N.C.

A12

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

DQ1

DQ2

GND

1

28

2 DS1743 27

3

26

4

25

5

24

6

23

7

22

8

21

9

20

10

19

11

18

12

17

13

16

14

15

VCC

WE

CE2

A8

A9

A11

OE

A10

CE

DQ7

DQ6

DQ5

DQ4

DQ3

28-Pin Encapsulated Package

(28 PIN 740)

N.C.

N.C.

N.C.

RST

VCC

WE

OE

CE

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

DS1743P

X1

GND

VBAT

X2

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

N.C.

N.C.

N.C.

N.C.

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

34-Pin PowerCap Module Board

(Uses DS9034PCX PowerCap)

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device

may be simultaneously available through various sales channels. For information about device errata, click here: www.maxim-ic.com/errata.

1 of 16

REV: 090407

�DS1743/DS1743P Y2K-Compliant, Nonvolatile Timekeeping RAMs

PIN DESCRIPTION

PIN

PDIP

PowerCap

1, 2, 3,

1

31–34

2

30

3

25

4

24

5

23

6

22

7

21

8

20

9

19

10

18

11

16

12

15

13

14

14

17

15

13

16

12

17

11

18

10

19

9

NAME

FUNCTION

N.C.

No Connection

A12

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

DQ1

DQ2

GND

DQ3

DQ4

DQ5

DQ6

DQ7

PIN

PDIP

PowerCap

Address Input

Data Input/

Output

NAME

20

8

CE

21

28

A10

22

7

OE

23

24

25

26

29

27

26

—

A11

A9

A8

CE2

27

6

WE

28

5

VCC

—

4

RST

Ground

Data Input/

Output

2 of 16

—

X1, X2

—

VBAT

FUNCTION

Chip Enable,

Active Low

Address Input

Output Enable,

Active Low

Address Input

Chip Enable 2

Write Enable,

Active Low

Power-Supply

Input

Power-On Reset

Output, Active

Low

Crystal

Connection

Battery

Connection

�DS1743/DS1743P Y2K-Compliant, Nonvolatile Timekeeping RAMs

ORDERING INFORMATION

PART

TEMP RANGE

PIN-PACKAGE

DS1743-85

DS1743-100

DS1743-100 IND

DS1743P-85

DS1743P-100

DS1743P-100IND

DS1743W-120

DS1743W-120 IND

DS1743W-150

DS1743W-150 IND

DS1743WP-120

DS1743WP-120 IND

DS1743-85+

DS1743-100+

DS1743-100 IND+

DS1743P-85+

DS1743P-100+

DS1743P-100IND+

DS1743W-120+

DS1743W-120 IND+

DS1743W-150+

DS1743W-150 IND+

DS1743WP-120+

DS1743WP-120 IND+

DS9034PCX

DS9034I-PCX

DS9034PCX+

DS9034I-PCX+

0°C to +70°C

0°C to +70°C

-40°C to +85°C

0°C to +70°C

0°C to +70°C

-40°C to +85°C

0°C to +70°C

-40°C to +85°C

0°C to +70°C

-40°C to +85°C

0°C to +70°C

-40°C to +85°C

0°C to +70°C

0°C to +70°C

-40°C to +85°C

0°C to +70°C

0°C to +70°C

-40°C to +85°C

0°C to +70°C

-40°C to +85°C

0°C to +70°C

-40°C to +85°C

0°C to +70°C

-40°C to +85°C

0°C to +70°C

-40°C to +85°C

0°C to +70°C

-40°C to +85°C

28 EDIP Module

28 EDIP Module

28 EDIP Module

34 PowerCap*

34 PowerCap*

34 PowerCap*

28 EDIP Module

28 EDIP Module

28 EDIP Module

28 EDIP Module

34 PowerCap*

34 PowerCap*

28 EDIP Module

28 EDIP Module

28 EDIP Module

34 PowerCap*

34 PowerCap*

34 PowerCap*

28 EDIP Module

28 EDIP Module

28 EDIP Module

28 EDIP Module

34 PowerCap*

34 PowerCap*

PowerCap

PowerCap IND

PowerCap

PowerCap IND

VOLTAGE

(V)

5

5

5

5

5

5

3.3

3.3

3.3

3.3

3.3

3.3

5

5

5

5

5

5

3.3

3.3

3.3

3.3

3.3

3.3

—

—

—

—

TOP MARK**

DS1743-85

DS1743-100

DS1743-100-IND

DS1743P-85

DS1743P-100

DS1743P-100 IND

DS1743W-120

DS1743W-120 IND

DS1743W-150

DS1743W-150 IND

DS1743WP-120

DS1743WP-120 IND

DS1743-85

DS1743-100

DS1743-100-IND

DS1743P-85

DS1743P-100

DS1743P-100 IND

DS1743W-120

DS1743W-120 IND

DS1743W-150

DS1743W-150 IND

DS1743WP-120

DS1743WP-120 IND

DS9034PC

DS9034PCI

DS9034PC

DS9034PCI

+Denotes a lead(Pb)-free/RoHS-compliant package.

*DS9034PCX required (must be ordered separately).

**A ‘+’ indicates lead(Pb)-free. The top mark will include a ‘+’ symbol on lead(Pb)-free devices.

DESCRIPTION

The DS1743 is a full-function, year-2000-compliant (Y2KC), real-time clock/calendar (RTC) and 8k x 8

nonvolatile static RAM. User access to all registers within the DS1743 is accomplished with a bytewide

interface as shown in Figure 1. The RTC information and control bits reside in the eight uppermost RAM

locations. The RTC registers contain century, year, month, date, day, hours, minutes, and seconds data in

24-hour binary-coded decimal (BCD) format. Corrections for the day of the month and leap year are made

automatically. The RTC clock registers are double buffered to avoid access of incorrect data that can occur

during clock update cycles. The double-buffered system also prevents time loss as the timekeeping

countdown continues unabated by access to time register data. The DS1743 also contains its own powerfail circuitry, which deselects the device when the VCC supply is in an out-of-tolerance condition. When

VCC is above VPF, the device is fully accessible. When VCC is below VPF, the internal CE signal is forced

high, preventing any access. When VCC rises above VPF, access remains inhibited for TREC, allowing time

for the system to stabilize. These features prevent loss of data from unpredictable system operation brought

on by low VCC as errant access and update cycles are avoided.

3 of 16

�DS1743/DS1743P Y2K-Compliant, Nonvolatile Timekeeping RAMs

PACKAGES

The DS1743 is available in two packages: the 28-pin DIP and the 34-pin PowerCap module. The 28-pin

DIP-style module integrates the crystal, lithium energy source, and silicon all in one package. The 34-pin

PowerCap Module Board is designed with contacts for connection to a separate PowerCap (DS9034PCX)

that contains the crystal and battery. This design allows the PowerCap to be mounted on top of the

DS1743P after the completion of the surface-mount process. Mounting the PowerCap after the surfacemount process prevents damage to the crystal and battery due to the high temperatures required for solder

reflow. The PowerCap is keyed to prevent reverse insertion. The PowerCap Module Board and PowerCap

are ordered separately and shipped in separate containers. The part number for the PowerCap is

DS9034PCX.

TIME AND DATE OPERATION

The time and date information is obtained by reading the appropriate register bytes. Table 2 shows the

RTC registers. The time and date are set or initialized by writing the appropriate register bytes. The

contents of the time and date registers are in the BCD format. The day-of-week register increments at

midnight. Values that correspond to the day of week are user-defined, but must be sequential (i.e., if 1

equals Sunday, then 2 equals Monday and so on). Illogical time and date entries result in undefined

operation.

CLOCK OPERATIONS-READING THE CLOCK

While the double-buffered register structure reduces the chance of reading incorrect data, internal updates

to the DS1743 clock registers should be halted before clock data is read to prevent reading of data in

transition. However, halting the internal clock register updating process does not affect clock accuracy.

Updating is halted when a 1 is written into the read bit, bit 6 of the century register (see Table 2). As long

as a 1 remains in that position, updating is halted. After a halt is issued, the registers reflect the count that

is day, date, and time that was current at the moment the halt command was issued. However, the internal

clock registers of the double-buffered system continue to update so that the clock accuracy is not affected

by the access of data. All the DS1743 registers are updated simultaneously after the internal clock register

updating process has been re-enabled. Updating is within a second after the read bit is written to 0.

The READ bit must be a zero for a minimum of 500s to ensure the external registers are updated.

4 of 16

�DS1743/DS1743P Y2K-Compliant, Nonvolatile Timekeeping RAMs

Figure 1. Block Diagram

Dallas

Semiconductor

DS1743

Table 1. Truth Table

CE

VCC

VIH

X

VCC > VPF

VIL

VIL

VIL

VSO < VCC < VPF

X

VCC