ADuCM320i/ADuCM322/ADuCM322i Reference Manual

UG-868

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

ADuCM320i/ADuCM322/ADuCM322i Reference Manual

SCOPE

This manual provides a detailed description of the ADuCM320i/ADuCM322/ADuCM322i functionality and features.

FUNCTIONAL BLOCK DIAGRAMS

BUF_VREF2V5

2.5V BAND GAP

XTALO XTALI ECLKIN

1.8V LDO

CLOCK SYSTEM

32.768kHz

16MHz OSC

80MHz PLL

AIN0

AIN5

14-BIT

SAR ADC

MUX

AIN6

DGNDx

AVDDx

AGNDx

IOVDDx

IOGNDx

AIN15

INTERNAL

CHANNELS:

TEMPERATURE,

AVDD, IOVDD

MEMORY

2 × 128kB FLASH

32kB SRAM

COMPARATOR

VDAC0

VDAC

VDAC7

VDAC

IDAC0

IDAC

IDAC3

IDAC

ARM

CORTEX-M3

PROCESSOR

DMA

NVIC

ADuCM320i

GPIO PORTS

UART

2 × SPI

2 × I2C

EXT IRQs

MDIO

PLA

GENERALPURPOSE

I/O PORTS

3 × GENERALPURPOSE TIMER

WATCHDOG TIMER

WAKE-UP TIMER

PWM

PWM0 TO

PWM6

RESET SYSTEM

SERIAL WIRE

SWDIO

PVDDx

PGND

13437-001

SWCLK

RESET

Figure 1. ADuCM320i Functional Block Diagram

BUF_VREF2V5

XTALO XTALI ECLKIN

2.5V BAND GAP

1.8V LDO

CLOCK SYSTEM

32.768kHz

16MHz OSC

80MHz PLL

AIN0

AIN5

AIN6

MUX

SAR ADC

DGNDx

AVDDx

AGNDx

IOVDDx

IOGNDx

AIN15

ARM

CORTEX-M3

PROCESSOR

INTERNAL

CHANNELS:

TEMPERATURE,

AVDD, IOVDD

MEMORY

2 × 128kB FLASH

32kB SRAM

COMPARATOR

VDAC0

GENERALPURPOSE

I/O PORTS

3 × GENERALPURPOSE TIMER

WATCHDOG TIMER

WAKE-UP TIMER

PWM

PWM0 TO

PWM6

VDAC

DMA

NVIC

VDAC7

GPIO PORTS

UART

2 × SPI

2 × I2C

EXT IRQs

MDIO

PLA

VDAC

ADuCM322/

ADuCM322i

RESET SYSTEM

SERIAL WIRE

SWDIO

PVDDx

PGND

RESET

Figure 2. ADuCM322/ADuCM322i Functional Block Diagram

PLEASE SEE THE LAST PAGE FOR AN IMPORTANT

WARNING AND LEGAL TERMS AND CONDITIONS.

Rev. D | Page 1 of 195

13437-102

SWCLK

�UG-868

ADuCM320i/ADuCM322/ADuCM322i Reference Manual

TABLE OF CONTENTS

Scope .................................................................................................. 1

Register Summary: ADC Circuit ............................................. 27

Functional Block Diagrams............................................................. 1

Register Details: ADC Circuit .................................................. 28

Revision History ............................................................................... 5

Register Summary: Additional Registers ................................ 31

Using the ADuCM320i/ADuCM322/ADuCM322i Reference

Manual ............................................................................................... 6

Register Details: Additional Registers ..................................... 32

Analog Comparator ....................................................................... 33

Number Notations ....................................................................... 6

Analog Comparator Features ................................................... 33

Register Access Conventions ...................................................... 6

Analog Comparator Overview ................................................. 33

Introduction to the ADuCM320i/ADuCM322/ADuCM322i ... 7

Analog Comparator Operation ................................................ 33

Main Features of the ADuCM320i/ADuCM322/ADuCM322i

......................................................................................................... 8

Register Summary: Analog Comparator ................................ 33

Memory Organization ................................................................. 8

Clocking Architecture.................................................................... 10

Clocking Architecture Features ............................................... 10

Clocking Architecture Block Diagram .................................... 10

Clocking Architecture Overview.............................................. 11

Register Summary: Clock Architecture................................... 11

Clocking Architecture Operation ............................................ 11

Register Details: Clock Architecture ....................................... 11

Power Management Unit .............................................................. 15

Power Management Unit Features .......................................... 15

Power Management Unit Overview ........................................ 15

Power Management Unit Operation ....................................... 15

Code Examples ........................................................................... 16

Register Summary: Power Management Unit ....................... 17

Register Details: Power Management Unit ............................ 17

ARM Cortex-M3 Processor .......................................................... 18

ARM Cortex-M3 Processor Features ...................................... 18

ARM Cortex-M3 Processor Overview .................................... 18

ARM Cortex-M3 Processor Operation ................................... 18

ARM Cortex-M3 Processor Related Documents .................. 19

ADC Circuit .................................................................................... 20

ADC Circuit Features ................................................................ 20

ADC Circuit Block Diagram..................................................... 20

ADC Circuit Overview .............................................................. 21

ADC Circuit Operation ............................................................. 21

ADC Transfer Function ............................................................ 22

ADC Typical Setup Sequence ................................................... 23

ADC Input Buffer....................................................................... 23

ADC Internal Channels ............................................................. 24

ADC Support Circuits ............................................................... 25

Register Details: Analog Comparator ..................................... 33

IDACs (ADuCM320i Only).......................................................... 34

IDAC Features ............................................................................ 34

IDAC Block Diagram ................................................................ 34

IDAC Overview .......................................................................... 34

Register Summary: IDAC ......................................................... 36

Register Details: IDAC .............................................................. 36

VDACs ............................................................................................. 40

VDAC Features .......................................................................... 40

VDAC Block Diagram ............................................................... 40

VDAC Overview ........................................................................ 40

VDAC Operation ....................................................................... 40

Register Summary: VDAC ........................................................ 42

Register Details: VDAC ............................................................. 42

System Exceptions and Peripheral Interrupts ............................ 48

Cortex-M3 and Fault Management ......................................... 48

External Interrupt Configuration ............................................ 51

Register Summary: External Interrupts .................................. 51

Register Details: External Interrupts ....................................... 51

Low Voltage Analog Die Interrupt Configuration................ 54

Register Summary: Low Voltage Die Interrupts.................... 54

Register Details: Low Voltage Die Interrupts ........................ 55

Reset ................................................................................................. 56

Reset Features ............................................................................. 56

Reset Operation .......................................................................... 56

Register Summary: Reset........................................................... 57

Register Details: Reset................................................................ 57

Direct Memory Access (DMA) Controller ................................. 58

DMA Features ............................................................................ 58

DMA Overview .......................................................................... 58

DMA Operation ......................................................................... 58

Rev. D | Page 2 of 195

�ADuCM320i/ADuCM322/ADuCM322i Reference Manual

UG-868

DMA Interrupts ..........................................................................59

SPI Transfer Initiation .............................................................123

DMA Priority ..............................................................................59

SPI Interrupts ............................................................................125

Channel Control Data Structure...............................................59

SPI Wire-OR’ed Mode (WOM)..............................................126

Control Data Configuration ......................................................60

SPI CSERR Condition ..............................................................126

DMA Transfer Types (CHNL_CFG[2:0]) ...............................61

SPI DMA ....................................................................................126

Address Calculation....................................................................63

SPI and Power-Down Modes ..................................................127

Aborting DMA Transfers ..........................................................63

Register Summary: SPI0...........................................................128

Register Summary: DMA ...........................................................64

Register Details: SPI0 ...............................................................128

Register Details: DMA................................................................64

Register Summary: SPI1...........................................................132

Flash Controller ...............................................................................70

Register Details: SPI1 ...............................................................132

Flash Controller Features...........................................................70

UART Serial Interface ..................................................................136

Flash Controller Overview.........................................................70

UART Features..........................................................................136

Flash Controller Operation .......................................................70

UART Overview........................................................................136

Flash Memory Operation...........................................................72

UART Operation ......................................................................136

Register Summary: Flash Controller ........................................79

Register Summary: UART .......................................................140

Register Details: Flash Controller .............................................80

Register Details: UART ............................................................140

Silicon Identification ......................................................................88

Programmable Logic Array (PLA) .............................................145

Silicon Identification Memory Mapped Registers .................88

PLA Features .............................................................................145

Digital Die ID Register ...............................................................88

PLA Overview ...........................................................................145

Low Voltage Die ID Register .....................................................88

PLA Operation ..........................................................................146

Digital Inputs/Outputs ...................................................................89

Register Summary: PLA ...........................................................149

Digital Inputs/Outputs Features ...............................................89

Register Details: PLA ................................................................149

Digital Inputs/Outputs Block Diagram ...................................89

General-Purpose Timers ..............................................................153

Digital Inputs/Outputs Overview .............................................89

General-Purpose Timers Features ..........................................153

Digital Inputs/Outputs Operation............................................89

General-Purpose Timers Block Diagram ..............................153

Digital Port Multiplex ................................................................92

General-Purpose Timers Overview ........................................153

Register Summary: Digital Input/Output................................94

General-Purpose Timer Operations ......................................154

Register Details: Digital Input/Output ....................................95

Register Summary: General-Purpose Timer 0......................156

I C Serial Interface ..........................................................................99

Register Details: General-Purpose Timer 0 ..........................156

I2C Features ..................................................................................99

Register Summary: General-Purpose Timer 1......................158

I2C Overview ................................................................................99

Register Details: General-Purpose Timer 1 ..........................158

I2C Operation...............................................................................99

Register Summary: General-Purpose Timer 2......................160

I2C Operating Modes ............................................................... 101

Register Details: General-Purpose Timer 2 ..........................160

Register Summary: I2C0 .......................................................... 104

Watchdog Timer ...........................................................................163

Register Details: I2C0 ............................................................... 104

Watchdog Timer Features .......................................................163

Register Summary: I C1 .......................................................... 113

Watchdog Timer Block Diagram ...........................................163

Register Details: I C1 ............................................................... 113

Watchdog Timer Overview .....................................................163

Serial Peripheral Interfaces ......................................................... 122

Watchdog Timer Operation....................................................163

SPI Features .............................................................................. 122

Register Summary: Watchdog Timer ....................................164

SPI Overview ............................................................................ 122

Register Details: Watchdog Timer .........................................164

SPI Operation ........................................................................... 122

Wake-Up Timer ............................................................................166

2

2

2

Rev. D | Page 3 of 195

�UG-868

ADuCM320i/ADuCM322/ADuCM322i Reference Manual

Wake-Up Timer Features ....................................................... 166

Management Data Input/Output (MDIO) ............................... 181

Wake-Up Timer Block Diagram ............................................ 166

MDIO Features ......................................................................... 181

Wake-Up Timer Overview ..................................................... 166

MDIO Overview ....................................................................... 181

Wake-Up Timer Operation .................................................... 166

MDIO Operation ..................................................................... 181

Register Summary: Wake-Up Timer ..................................... 169

Register Summary: MDIO Interface (MDIO) ..................... 183

Register Details: Wake-Up Timer .......................................... 169

Register Details: MDIO ........................................................... 183

Pulse Width Modulator (PWM) ................................................ 173

Downloader ................................................................................... 186

PWM Features .......................................................................... 173

I2C Downloader (ADuCM320i/ADuCM322i Only)........... 186

PWM Overview ........................................................................ 173

MDIO Downloader (ADuCM322 Only) .............................. 186

PWM Operation ....................................................................... 173

Hardware Design Considerations .............................................. 191

PWM Interrupt Generation.................................................... 176

Typical System Configuration ................................................ 191

Register Summary: PWM........................................................ 177

Serial Wire Debug Interface ................................................... 195

Register Details: PWM ............................................................ 177

Rev. D | Page 4 of 195

�ADuCM320i/ADuCM322/ADuCM322i Reference Manual

UG-868

REVISION HISTORY

3/2020—Rev. C to Rev. D

Changes to Table 117 and Table 118 ............................................88

5/2018—Rev. B to Rev. C

Changes to ADC Voltage Reference Selection Section and

Figure 9 .............................................................................................26

Changes to Table 14 ........................................................................29

Changes to Table 22 ........................................................................32

Changes to VDAC Operation Section .........................................41

Added Figure 14; Renumbered Sequentially ...............................41

Changes to Table 66 ........................................................................57

Changes to Table 183....................................................................129

Changes to Table 191....................................................................133

Changes to Watchdog Timer Operation Section .....................162

Changes to MDIO Downloader Section (ADuCM322 Only)

Section.............................................................................................186

1/2017—Rev. A to Rev. B

Changes to Clocking Architecture Operation Section ..............10

Changes to ADC Circuit Features Section ..................................19

Changes to ADC Circuit Overview Section ................................20

Changes to Single-Ended Mode Section and Differential

Section...............................................................................................21

Changes to ADC Voltage Reference Selection Section..............25

Changes to Table 22 ........................................................................31

Added IDAC Thermal Shutdown Section ...................................35

Changes to Writing to the Flash Section .....................................71

Changes to Table 120......................................................................90

Changes to Table 183....................................................................127

2/2016—Rev. 0 to Rev. A

Changed ADuCM320i to

ADuCM320i/ADuCM322/ADuCM322i ................... Throughout

Changed CS to CS0/CS1 .............................................. Throughout

Added Figure 2; Renumbered Sequentially ................................... 1

Changes to Advanced Interrupt Handling Section ....................17

Changes to Table 11 ........................................................................26

Changes to Table 14 ........................................................................28

Changes to Table 20 ........................................................................31

Deleted Note 1, Table 64; Renumbered Sequentially ................ 53

Changes to Table 83........................................................................ 63

Changes to Protection, Integrity Section ..................................... 67

Added Error Checking and Correcting (ECC) Error Handling

Section, ECC Error During Reading Section, and ECC Error

During Execution of Sign Command Section ............................ 71

Changes to Table 94........................................................................ 75

Changes to Table 95........................................................................ 76

Added ECC Enable/Disable, Error Response Register Section

and Table 111 .................................................................................. 81

Added Flash 0 Error Address Register Section, Table 112,

Flash 1 ECC Error Address Register Section, and Table 113 ... 82

Changes to Figure 18 and Figure 19 ............................................. 86

Changes to Table 120 ..................................................................... 88

Changes to Table 145 ...................................................................105

Changes to Table 167 ...................................................................114

Changes to Table 183 ...................................................................125

Changes to Table 191 ...................................................................129

Changes to Table 205 ...................................................................140

Changes to Table 211 ...................................................................145

Added MDIO Interrupt Power Up Register Write Sequence

Section ............................................................................................178

Added I2C Downloader (ADuCM320i/ADuCM322i Only)

Section, MDIO Downloader (ADuCM322 Only) Section, and

Figure 39 .........................................................................................181

Added Flash Block Partitioning Section, Program Image

Section, Debug Mode Section, and Choosing the Active Block

Section ............................................................................................182

Added Trial Run Mode Section, Normal Mode Section, Typical

Sequence Section, and Table 301 ................................................ 183

Added Table 302 ...........................................................................184

Added to Figure 40 .......................................................................185

Changes to Typical System Configurations Section ................ 186

Changes to Figure 41 ....................................................................187

Added Figure 42 ............................................................................188

Added Figure 43 ............................................................................189

8/2015—Revision 0: Initial Version

Rev. D | Page 5 of 195

�UG-868

ADuCM320i/ADuCM322/ADuCM322i Reference Manual

USING THE ADUCM320i/ADUCM322/ADUCM322i REFERENCE MANUAL

NUMBER NOTATIONS

Table 1. Number Notations

Notation

Bit N

V[x:y]

0xNN

0bNN

NN

Description

Bits are numbered in little endian format, that is, the least significant bit of a number is referred to as Bit 0.

Bit field representation covering Bit x to Bit y of a value or a field (V).

Hexadecimal (Base 16) numbers are preceded by the prefix 0x.

Binary (Base 2) numbers are preceded by the prefix 0b.

Decimal (Base 10) numbers are represented using no additional prefixes or suffixes.

REGISTER ACCESS CONVENTIONS

Table 2. Register Access Conventions

Mode

RW

RC

R

W

Description

Memory location has read and write access.

Memory location is cleared after reading it.

Memory location is read access only. A read always returns 0, unless otherwise specified.

Memory location is write access only.

Memory mapped register (MMR) bits that are not documented are reserved. When writing to MMRs with reserved bits, the reserved bits

must be written with the value in the reset column of the relevant MMR description unless otherwise noted.

Rev. D | Page 6 of 195

�ADuCM320i/ADuCM322/ADuCM322i Reference Manual

UG-868

INTRODUCTION TO THE ADUCM320i/ADUCM322/ADUCM322i

The ADuCM320i/ADuCM322/ADuCM322i are fully integrated, single-package devices that incorporate high performance analog

peripherals together with digital peripherals controlled by an 80 MHz ARM® Cortex™-M3 processor and integral flash for code and data.

The analog-to-digital converter (ADC) on the 14-bit ADuCM320i and the 12-bit ADuCM322/ADuCM322i provide 1 MSPS data acquisition

on up to 16 input pins that can be programmed for single-ended or differential operation. Additionally, chip temperature and supply

voltages can be measured. The ADC input voltage is 0 V to VREF. A sequencer is provided that allows a user selected set of ADC channels

to be measured in sequence without software involvement during the sequence. The sequence can optionally repeat automatically at a

user-selectable rate.

Up to eight voltage digital-to-analog converters (VDACs) are provided with output ranges programmable to one of two voltage ranges.

The DAC outputs have an enhanced feature of being able to retain their output voltage during a watchdog or software reset sequence.

For the ADuCM320i only, four current output DAC (IDAC) sources are provided. The output currents are programmable with a range

from 0 mA to 150 mA. A low drift, band gap reference and a voltage comparator complete the analog input peripheral set.

The microcontroller core is a low power ARM Cortex-M3 processor, a 32-bit RISC machine that offers up to 100 MIPS peak performance.

Also integrated on chip are two 128 kB Flash/EE memory and 32 kB of SRAM. The flash comprises two separate 128 kB blocks supporting

execution from one flash block and simultaneous writing/erasing of the other flash block.

The ADuCM320i/ADuCM322/ADuCM322i operate from an on-chip oscillator or a 16 MHz external crystal and a phase-locked loop

(PLL) at 80 MHz. This clock can optionally be divided down to reduce current consumption. Additional low power modes can be set via

software. In the normal operating mode, the ADuCM320i/ADuCM322/ADuCM322i digital core consumes approximately 300 µA/MHz.

The ADuCM320i/ADuCM322/ADuCM322i integrate a range of on-chip peripherals that can be configured via software control as

required in the application. These peripherals include one universal asynchronous transmitter (UART), two I2Cs, two serial peripheral

interface (SPI) serial input/output communication controllers, general-purpose input/output (GPIO) pins, 32-element programmable

logic array (PLA), three general-purpose timers, one wake-up timer (WUT), and one system watchdog timer (WDT). In addition, 16-bit

pulse-width modulators (PWMs) with seven output signals are provided.

The ADuCM320i/ADuCM322/ADuCM322i include a management data input/output (MDIO) interface capable of operating up to

4 MHz. The capability to simultaneously execute from one flash block and write or erase the other flash block makes the ADuCM320i/

ADuCM322/ADuCM322i ideal for 40 G/100 G optical applications. User programming is eased by receiving interrupts after physical

address (PHYADR), device address (DEVADD), and end of frame and by having PHYADR and DEVADD hardware comparators.

GPIO pins on the device power up in input mode. In output mode, the software can choose between open-drain mode and push-pull

mode. The outputs can drive at least 4 mA. The pull-ups can be enabled and disabled in the software. In GPIO mode, the inputs can

always be enabled to monitor the pins. The GPIO pins can also be programmed to handle digital or analog peripheral signals, in which

case, the pin characteristics are matched to the specific requirement.

A large support ecosystem is available for the ARM Cortex-M3 processor to ease product development of the ADuCM320i/ADuCM322/

ADuCM322i. Access is via the ARM serial wire debug port. On-chip factory firmware supports in-circuit serial download via I2C

(ADuCM320i/ADuCM322i) or MDIO (ADuCM322). These features are incorporated in a low cost, QuickStart™ development system

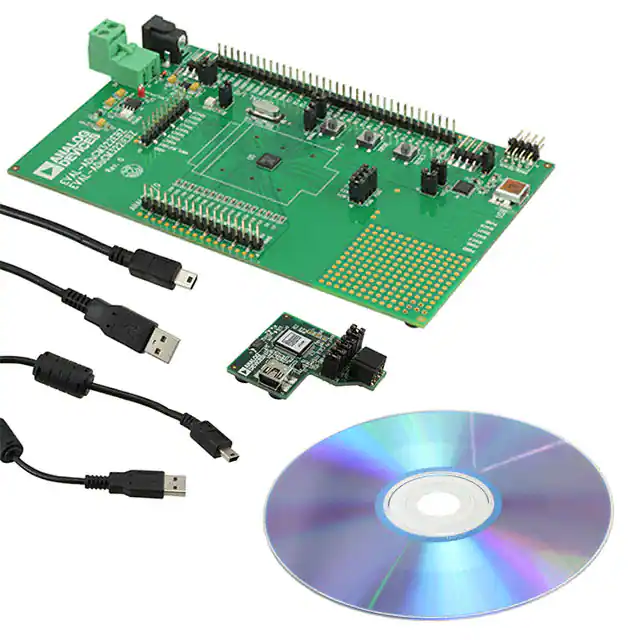

supporting this precision analog microcontroller family.

Rev. D | Page 7 of 195

�UG-868

ADuCM320i/ADuCM322/ADuCM322i Reference Manual

MAIN FEATURES OF THE ADUCM320i/ADUCM322/ADUCM322i

ADC

•

•

Multichannel, 14-bit (ADuCM320i)/12-bit (ADuCM322/ADuCM322i), 1 MSPS successive approximation register (SAR) ADC

Low drift, on-chip voltage reference

DACs

•

•

•

Eight voltage output DACs: VDACs are 12-bit monotonic

Four current output DACs: IDACs are 12-bit monotonic (ADuCM320i only)

Low drift, on-chip 2.5 V voltage reference source: two buffered reference outputs

Communication

•

•

•

•

•

UART: industry standard, 16450 UART peripheral and support for direct memory access (DMA)

Two I2Cs: 2-byte transmit (Tx) and receive (Rx) FIFOs for the master and slave, and support for DMA

Two SPIs: master or slave mode with separate 4-byte Rx and Tx FIFOs, and Rx and Tx DMA channels

16-bit PWM with seven output channels

Multiple GPIO pins

Processing

•

•

•

•

•

ARM Cortex-M3 processor, operating from an internal 80 MHz system clock

Two 128 kB Flash/EE memory, 32 kB SRAM

In-circuit programming and debug via serial wire

In-circuit programming via I2C downloader (ADuCM320i/ADuCM322i only)

In-circuit programming via MDIO downloader (ADuCM322 only)

On-Chip Peripherals

•

•

•

•

Three general-purpose timers

Wake-up timer

Watchdog timer

32-element PLA

Package and Temperature Range

•

6 mm × 6 mm, 96-ball BGA package, −40°C to +85°C (ADuCM320i only) and −40°C to +105°C (ADuCM322/ADuCM322i only)

Tools

•

•

Low cost development system

Third-party compiler and emulator tool support

Applications

•

•

•

•

Optical networking: 10 G, 40 G, and 100 G modules

Industrial control and automation systems

Smart sensors, precision instrumentation

Base station systems

MEMORY ORGANIZATION

The ADuCM320i/ADuCM322/ADuCM322i memory organization is described in this section.

Features

•

•

•

•

Cortex-M3 memory system features include predefined memory map, support for bit band operation for atomic operations, and

unaligned data access.

ADuCM320i/ADuCM322/ADuCM322i on-chip peripherals are accessed via memory mapped registers, situated in the bit band

region.

User memory sizes options: 32 kB SRAM and two 128 kB Flash/EE memory.

On-chip kernel for manufacturer data and in-circuit download.

Rev. D | Page 8 of 195

�ADuCM320i/ADuCM322/ADuCM322i Reference Manual

UG-868

0xFFFF FFFF

VENDOR SPECIFIC

0xE010 0000

0xE00F FFFF

PRIVATE

PERIPHERAL

BUS—EXTERNAL

0xE004 0000

0xE003 FFFF

PRIVATE

PERIPHERAL

BUS—INTERNAL

0xE000 0000

0xE000 EF00

ADuCM320i/ADuCM322/ADuCM322i

MMRs

0xE000 E000

0xDFFF FFFF

EXTERNAL DEVICE

1GB

(NOT AVAILABLE IN

ADuCM320i)

0xA000 0000

0x9FFF FFFF

EXTERNAL RAM

1GB

(NOT AVAILABLE IN

ADuCM320i)

0x6000 0000

0x5FFF FFFF

PERIPHERAL

0.5GB

0x4000 0000

0x400A FFFF

ADuCM320i/ADuCM322/ADuCM322i

MMRs

0x4000 0000

0x3FFF FFFF

SRAM 0.5GB

0x2000 0000

0x2000 7FFF

ADuCM320i/ADuCM322/ADuCM322i

32kB SRAM

0x2000 0000

0x1FFF FFFF

CODE 0.5GB

0x0004 0FFF

0x0000 0000

ADuCM320i/ADuCM322/ADuCM322i

KERNEL SPACE

0x0004 0000

0x0000 0000

Figure 3. Cortex-M3 Memory Map Diagram

Rev. D | Page 9 of 195

13437-002

0x0003 FFFF

ADuCM320i/ADuCM322/ADuCM322i

256kB FLASH/EE MEMORY

�UG-868

ADuCM320i/ADuCM322/ADuCM322i Reference Manual

CLOCKING ARCHITECTURE

CLOCKING ARCHITECTURE FEATURES

The ADuCM320i/ADuCM322/ADuCM322i integrates two on-chip oscillators and circuitry for an external crystal and external clock source:

•

•

•

•

LFOSC is a 32 kHz low power internal oscillator that is used in low power modes.

HFOSC is a 16 MHz internal oscillator that is used in active mode, which is the default input to the PLL.

HFXTAL is a 16 MHz external crystal oscillator.

External clock input (ECLKIN) via GPIO pin.

CLOCKING ARCHITECTURE BLOCK DIAGRAM

÷4

0

HFXTAL

16MHz OSC

ACLK

(TO LOW VOLTAGE DIE,

ADC)

80MHz SPLL

1

CLKCON5[3]

CLKCON0[11]

I2C0

CLKCON5[4]

CDPCLK

(CLKCON1[10:8])

I2C1

CLKCON5[5]

01

UART

PCLK

UCLK

CLKCON5[6]

HFOSC

16MHz OSC

00

ECLKIN

P1.0

11

CDD2DCLK

(CLKCON1[11])

D2D

CLKCON5[0]

SPI0

CLKCON5[1]

CLKCON0[1:0]

SPI1

CDHCLK

(CLKCON1[2:0])

HCLK

CORE

WATCHDOG

TIMER

LFOSC

(INTERNAL)

PWM

FLASH

PCLK

01

11

00

WAKE-UP

TIMER

T4CON[9:10]

PCLK

HCLK

00

01

11

10

TIMER0CLK

T0CON[5:6]

PCLK

HCLK

00

01

11

10

TIMER1CLK

T1CON[5:6]

00

01

11

10

TIMER2CLK

13437-003

PCLK

HCLK

T2CON[5:6]

Figure 4. Clocking Architecture Block Diagram

Rev. D | Page 10 of 195

�ADuCM320i/ADuCM322/ADuCM322i Reference Manual

UG-868

CLOCKING ARCHITECTURE OVERVIEW

The system clock, UCLK, can be selected from a 16 MHz oscillator or from an 80 MHz PLL output (default). An external clock on P1.0

can also be used for test purposes.

Internally, the system clock is divided into separate clocks:

•

•

•

•

UCLK system clock

HCLK for the flash, SRAM, and DMA

PCLK for most peripherals

ACLK for the analog section of the chip; this is based on UCLK/4 and goes to the low voltage analog die

All ADC performance details are based on a 20 MHz ACLK. Performance at other clock speeds is not guaranteed.

REGISTER SUMMARY: CLOCK ARCHITECTURE

Table 3. Clocking Register Summary

Address

0x40028000

0x40028004

0x40028014

0x40028018

Name

CLKCON0

CLKCON1

CLKCON5

CLKSTAT0

Description

Miscellaneous clock settings register

Clock dividers register

User clock gating control register

Clocking status

Reset

0x0041

0x0200

0x0040

0x0000

Access

RW

RW

RW

RW

CLOCKING ARCHITECTURE OPERATION

At power-up, the processor executes at 80 MHz, sourced from the 80 MHz PLL output. The clock source for the 80 MHz PLL is the

internal 16 MHz oscillator by default. User code can select the clock source for the system clock and can divide the clock by a factor of 1

to 128, where the clock divider bits are controlled by CLKCON1[2:0]. Slower code execution and reduced power consumption result.

Note that P1.0 must be configured as a clock input before the clock source is switched in the clock control register.

When changing from one clock source to a different clock source, the user code must ensure that both clock sources are kept active for a

minimum of five clock cycles to ensure that the clock switching is fully completed without any glitches.

If the clock source for the 80 MHz SPLL needs to be changed from the internal 16 MHz oscillator to the external HFXTAL, use the

following procedure:

1.

2.

3.

4.

5.

6.

Check that HFXTAL is stable by reading CLKSTAT0[14:12].

Change the system clock to the internal 16 MHz oscillator using CLKCON0[1:0].

Wait 5 × 16 MHz clock cycles.

Switch the input to the SPLL using CLKCON0[11].

Wait until the SPLL has locked by monitoring CLKSTAT0[2:0].

Change the system clock back to the SPLL clock.

REGISTER DETAILS: CLOCK ARCHITECTURE

Miscellaneous Clock Settings Register

Address: 0x40028000, Reset: 0x0041, Name: CLKCON0

Table 4. Bit Descriptions for CLKCON0

Bit(s)

15

Bit Name

HFXTALIE

14

13

RESERVED

SPLLIE

12

11

RESERVED

PLLMUX

Description

High frequency crystal interrupt enable.

0: an interrupt to the core does not generate on a HFXTALOK or HFXTALNOK.

1: an interrupt to the core generates on a HFXTALOK or HFXTALNOK.

Reserved.

SPLL interrupt enable.

0: SPLL interrupt does not generate.

1: SPLL interrupt generates.

Reserved.

PLL source selection.

0: internal oscillator is selected (HFOSC).

1: external oscillator is selected (HFXTAL).

Rev. D | Page 11 of 195

Reset

0x0

Access

RW

0x0

0x0

RW

RW

0x0

0x0

R

RW

�UG-868

ADuCM320i/ADuCM322/ADuCM322i Reference Manual

Bit(s)

[10:8]

[7:4]

Bit Name

RESERVED

CLKOUT

[3:2]

[1:0]

RESERVED

CLKMUX

Description

Reserved.

GPIO clock out selection.

0000: UCLK.

0001: LFOSC (32 kHz).

0010: HFOSC(16 MHz).

0100: core clock.

0101: PCLK.

1011: General-Purpose Timer 0 clock.

1100: wake-up timer clock.

1110: HFXTAL.

All other combinations are reserved.

Reserved.

Clock selection.

00: high frequency internal oscillator (HFOSC).

01: SPLL is selected (80 MHz).

10: reserved.

11: external GPIO port is selected (ECLKIN).

Reset

0x0

0x4

Access

RW

RW

0x0

0x1

R

RW

Reset

0x0

0x0

Access

R

R

0x2

RW

0x0

0x0

R

RW

Clock Dividers Register

Address: 0x40028004, Reset: 0x0200, Name: CLKCON1

Table 5. Bit Descriptions for CLKCON1

Bit(s)

[15:12]

11

Bit Name

RESERVED

CDD2DCLK

[10:8]

CDPCLK

[7:3]

[2:0]

RESERVED

CDHCLK

Description

Reserved.

D2DCLK divide bits.

0: D2D_CLK frequency is HCLK frequency.

1: D2D_CLK frequency is half of HCLK frequency.

PCLK divide bits. PCLK divide bits.

000: Reserved.

001: Reserved.

010: DIV4. Divide by 4 (PCLK is quarter the frequency of root clock, 20 MHz). All ADC

specifications based on this setting. Using any other setting may affect ADC

performance.

011: DIV8. Divide by 8.

100: DIV16. Divide by 16.

101: DIV32. Divide by 32.

110: DIV64. Divide by 64.

111: DIV128. Divide by 128.

Reserved. Always returns 0 when read.

HCLK divide bits.

000: DIV1. Divide by 1 (HCLK is equal to root clock).

001: DIV2. Divide by 2 (HCLK is half the frequency of root clock).

010: DIV4. Divide by 4 (HCLK is quarter the frequency of root clock).

011: DIV8. Divide by 8.

100: DIV16. Divide by 16.

101: DIV32. Divide by 32.

110: DIV64. Divide by 64.

111: DIV128. Divide by 128.

Rev. D | Page 12 of 195

�ADuCM320i/ADuCM322/ADuCM322i Reference Manual

UG-868

User Clock Gating Control Register

Address: 0x40028014, Reset: 0x0040, Name: CLKCON5

The user clock gating control register (CLKCON5) controls the gates of the peripheral UCLKs.

Table 6. Bit Descriptions for CLKCON5

Bit(s)

[15:7]

6

5

Bit Name

RESERVED

RESERVED

UCLKUARTOFF

4

UCLKI2C1OFF

3

UCLKI2C0OFF

2

1

RESERVED

UCLKSPI1OFF

0

UCLKSPI0OFF

Description

Reserved. Always returns 0 when read.

Always set to 1. Do not write 0 to this bit.

UART clock user control. This bit disables the UCLK_UART clock. It controls the gate on

UCLK_UART in Power Mode 0 and Power Mode 1. In Power Mode 2 and Power Mode

3, the UCLK_UART is always off, and this bit has no effect.

0: clock on.

1: clock off.

I2C1 clock user control. This bit disables the PCLK_I2C1 clock. It controls the gate on

PCLK_I2C1 in Power Mode 0 and Power Mode 1. In Power Mode 2 and Power Mode 3,

the I2C1 PCLK is always off, and this bit has no effect.

0: clock on.

1: clock off.

I2C0 clock user control. This bit disables the PCLK_I2C0 clock. It controls the gate on

PCLK_I2C0 in Power Mode 0 and Power Mode 1. In Power Mode 2 and Power Mode 3,

the PCLK_I2C0 is always off, and this bit has no effect.

0: clock on.

1: clock off.

Reserved.

SPI1 clock user control. This bit disables the UCLK_SPI1 clock. It controls the gate on

UCLK_SPI1 in Power Mode 0 and Power Mode 1. In Power Mode 2 and Power Mode 3,

the UCLK_SPI1 is always off, and this bit has no effect.

0: clock on.

1: clock off.

SPI0 clock user control. This bit disables the UCLK_SPI0 clock. It controls the gate on

UCLK_SPI0 in Power Mode 0 and Power Mode 1. In Power Mode 2 and Power Mode 3,

the UCLK_SPI0 is always off, and this bit has no effect.

0: clock on.

1: clock off.

Rev. D | Page 13 of 195

Reset

0x0

0x1

0x0

Access

R

RW

RW

0x0

RW

0x0

RW

0x0

0x0

R

RW

0x0

RW

�UG-868

ADuCM320i/ADuCM322/ADuCM322i Reference Manual

Clocking Status Register

Address: 0x40028018, Reset: 0x0000, Name: CLKSTAT0

The clock status register monitors PLL and oscillator status.

Table 7. Bit Descriptions for CLKSTAT0

Bit(s)

15

14

Bit Name

RESERVED

HFXTALNOK

13

HFXTALOK

12

HFXTALSTATUS

[11:3]

2

RESERVED

SPLLUNLOCK

1

SPLLLOCK

0

SPLLSTATUS

Description

Reserved. Always returns 0 when read.

HF crystal not stable. This bit is sticky. It is used to interrupt the core when

interrupts are enabled. Write a 1 to this location to clear it.

0: HF crystal stable signal is not deasserted.

1: HF crystal stable signal is deasserted.

HF crystal stable. This bit is sticky. It is used to interrupt the core when interrupts are

enabled. Write a 1 to this location to clear it.

0: HF crystal stable signal is not asserted.

1: HF crystal stable signal is asserted.

HF crystal status.

0: HF crystal is not stable or not enabled.

1: HF crystal is stable.

Reserved.

System PLL unlock. This bit is sticky. SPLLUNLOCK is set when the PLL loses its lock.

SPLLUNLOCK is used as the interrupt source to signal the core that a lock was lost.

Writing a 1 to this bit clears it. SPLLUNLOCK does not set again unless the system

PLL gains a lock and subsequently loses it again.

0: no loss of PLL lock is detected.

1: a PLL loss of lock is detected.

System PLL lock. This bit is sticky. SPLLLOCK is set when the PLL locks. SPLLLOCK is

used as the interrupt source to signal the core that a lock was detected. Writing a 1

to this bit clears it. SPLLLOCK does not set again unless the system PLL loses lock

and subsequently locks again.

0: no PLL lock event is detected.

1: a PLL lock event is detected.

System PLL status. Indicates the current status of the PLL. Initially, the system PLL is

unlocked. After a stabilization period, the PLL locks and is ready for use as the

system clock source. This is a read only bit. A write has no effect.

0: the PLL is not locked or properly configured. The PLL is not ready for use as the

system clock source.

1: the PLL is locked and is ready for use as the system clock source.

Rev. D | Page 14 of 195

Reset

0x0

0x0

Access

R

RW

0x0

RW

0x0

R

0x0

0x0

R

RW

0x0

RW

0x0

R

�ADuCM320i/ADuCM322/ADuCM322i Reference Manual

UG-868

POWER MANAGEMENT UNIT

POWER MANAGEMENT UNIT FEATURES

The power management unit (PMU) controls the different power modes of the ADuCM320i/ADuCM322/ADuCM322i.

Four power modes are available:

•

•

•

•

Active

CORE_SLEEP

SYS_SLEEP

Hibernate

POWER MANAGEMENT UNIT OVERVIEW

The Cortex-M3 sleep modes are linked to the PMU modes and are described in this section. The PMU is in the always-on section. Each

mode gives a power reduction benefit with a corresponding reduction in functionality.

POWER MANAGEMENT UNIT OPERATION

The debug tools can prevent the Cortex-M3 from fully entering its power saving modes by setting bits in the debug logic. Only a power-on reset

resets the debug logic. Therefore, the device must be power cycled after using serial wire debug with application code containing the wait

for interrupt (WFI) instruction.

Power Mode: Active Mode, Mode 0

The system is fully active. Memories and all user enabled peripherals are clocked, and the Cortex-M3 processor executes instructions.

Note that the Cortex-M3 processor manages its internal clocks and can be in a partial clock gated state. This clock gating affects only the

internal Cortex-M3 processing core. Automatic clock gating is used on all blocks. User code can use a WFI command to put the Cortex-M3

processor into sleep mode; it is independent of the power mode settings of the PMU.

When the ADuCM320i/ADuCM322/ADuCM322i wakes up from any of the low power modes, the devices return to Mode 0.

Power Mode: CORE_SLEEP Mode, Mode 1

In CORE_SLEEP mode, the system gates the clock to the Cortex-M3 core after the Cortex-M3 enters sleep mode. The rest of the system

remains active. No instructions can be executed; however, DMA transfers can continue to occur between peripherals and memories. The

Cortex-M3 processor FCLK is active, and the device wakes up using the nested vectored interrupt controller (NVIC).

Power Mode: SYS_SLEEP Mode, Mode 2

In SYS_SLEEP mode, the system gates the system bus clock (HCLK) and the peripheral bus clock (PCLK) after the Cortex-M3 enters

sleep mode. The gating of these clocks stops all advanced high performance bus (AHB) attached masters/slaves and all peripherals attached

to the advanced peripheral bus (APB). Peripheral clocks are all off, and they are no longer user programmable. The NVIC clock (FCLK)

remains active, and the NVIC processes wake-up events.

Power Mode: Hibernate Mode, Mode 3

In hibernate mode, the system disables power to all combinational logic and places sequential logic in retain mode. Because FCLK is

stopped, the number of sources capable of waking up the system is restricted. The sources listed in Table 54 are the only sources able to

wake up the system.

Power Mode 1 to Power Mode 3 must be entered when the processor is not in an interrupt handler. If Power Mode 1 to Power Mode 3

are entered when the processor is in an interrupt handler, the power-down mode can only be exited by a reset or a higher priority

interrupt source.

Rev. D | Page 15 of 195

�UG-868

ADuCM320i/ADuCM322/ADuCM322i Reference Manual

CODE EXAMPLES

Code Example to Enter Power Saving Modes

SCB->SCR = 0x04;

pADI_PWRCTL->PWRKEY = 0x4859;

pADI_PWRCTL->PWRKEY = 0xF27B;

pADI_PWRCTL->PWRMOD = 0x3;

__DSB();

__nop();

__nop();

__nop();

__nop();

__nop();

__nop();

__nop();

__nop();

__nop();

__nop();

__nop();

__nop();

__nop();

__nop();

__nop();

__nop();

__WFI();

__nop();

__nop();

__nop();

__nop();

__nop();

__nop();

// sleep deep mode

// key1

// key2

// Hibernate

Code Example to Achieve Further Power Savings

pADI_ADC->ADCCON = 0;

pADI_IDAC0->IDACCON = 0x1;

pADI_IDAC1->IDACCON = 0x1;

pADI_IDAC2->IDACCON = 0x1;

pADI_IDAC3->IDACCON = 0x1;

pADI_VDAC0->DACCON = 0x100;

pADI_VDAC1->DACCON = 0x100;

pADI_VDAC2->DACCON = 0x100;

pADI_VDAC3->DACCON = 0x100;

pADI_VDAC4->DACCON = 0x100;

pADI_VDAC5->DACCON = 0x100;

pADI_VDAC6->DACCON = 0x100;

pADI_VDAC7->DACCON = 0x100;

pADI_CLKCTL->CLKCON0 &= 0xFFFC;

pADI_CLKCTL->CLKCON1 = 0x505;

pADI_CLKCTL->CLKCON5 = 0x7B;

//

//

//

//

//

//

//

//

//

//

//

//

//

//

//

//

Power off the ADC

Turn off IDAC0

Turn off IDAC1

Turn off IDAC2

Turn off IDAC3

Turn off VDAC0

Turn off VDAC1

Turn off VDAC2

Turn off VDAC3

Turn off VDAC4

Turn off VDAC5

Turn off VDAC6

Turn off VDAC7

Switch to 16MHz clock

Slow down system clocks

Turn off clocks to peripherals

Rev. D | Page 16 of 195

�ADuCM320i/ADuCM322/ADuCM322i Reference Manual

UG-868

REGISTER SUMMARY: POWER MANAGEMENT UNIT

Table 8. Power Management Register Summary

Address

0x40002400

0x40002404

Name

PWRMOD

PWRKEY

Description

Power modes

Key protection for PWRMOD

Reset

0x0000

0x0000

Access

RW

RW

Reset

0x0

0x0

Access

R

RW

Reset

0x0

Access

RW

REGISTER DETAILS: POWER MANAGEMENT UNIT

Power Modes Register

Address: 0x40002400, Reset: 0x0000, Name: PWRMOD

Table 9. Bit Descriptions for PWRMOD

Bit(s)

[14:2]

[1:0]

Bit Name

RESERVED

PWRMOD

Description

Reserved. These bits must write 0 by user code.

Power modes control bits. When read, these bits contain the last power mode value entered

by user code. Note that, to place the Cortex in sleep deep mode for hibernate, the Cortex-M3

system control register (Address 0xE000ED10) must be configured to 0x4 or 0x06.

00: active mode

01: CORE_SLEEP mode

10: SYS_SLEEP mode

11: hibernate mode

Key Protection for PWRMOD Register

Address: 0x40002404, Reset: 0x0000, Name: PWRKEY

Table 10. Bit Descriptions for PWRKEY

Bit(s)

[15:0]

Bit Name

PWRKEY

Description

Power control key register. The PWRMOD register is key protected. Two writes to the key are

necessary to change the value in the PWRMOD register: first 0x4859, then 0xF27B. Then, write

to the PWRMOD register. A write to any other register before writing to PWRMOD returns the

protection to the lock state.

Rev. D | Page 17 of 195

�UG-868

ADuCM320i/ADuCM322/ADuCM322i Reference Manual

ARM CORTEX-M3 PROCESSOR

ARM CORTEX-M3 PROCESSOR FEATURES

High Performance

•

•

•

•

1.25 DMIPS/MHz.

Many instructions, including multiply, are single cycle.

Separate data and instruction buses allow simultaneous data and instruction accesses to be performed.

Optimized for single cycle flash usage.

Low Power

•

•

•

Low standby current.

Core implemented using advanced clock gating so that only the actively used logic consumes dynamic power.

Power saving mode support (sleep and deep sleep modes). The design has separate clocks to allow unused parts of the processor to

be stopped.

Advanced Interrupt Handling

•

•

•

•

•

The nested vectored interrupt controller (NVIC) supports up to 240 interrupts. The ADuCM320i/ADuCM322/ADuCM322i

supports 47 of these interrupts. The vectored interrupt feature greatly reduces interrupt latency because there is no need for software to

determine which interrupt handler to serve. In addition, there is no need to have software to set up nested interrupt support.

The ARM Cortex-M3 processor automatically pushes registers onto the stack at the entry interrupt and retrieves them at the exit

interrupt. The pushing and retrieving helps reduce interrupt handling latency and allow interrupt handlers to be normal C

functions.

Dynamic priority control for each interrupt.

Latency reduction using late arrival interrupt acceptance and tail-chain interrupt entry.

Immediate execution of a nonmaskable interrupt request for safety critical applications.

System Features

•

•

Support for bit band operation and unaligned data access.

Advanced fault handling features include various exception types and fault status registers.

Debug Support

•

•

•

Serial wire debug interfaces (SW-DP).

Flash patch and breakpoint (FPB) unit for implementing breakpoints. Limited to two hardware breakpoints.

Data watchpoint and trigger (DWT) unit for implementing watchpoints trigger resources and system profiling. Limited to one

hardware watchpoint. The DWT does not support data matching for watchpoint generation because it only has one comparator.

ARM CORTEX-M3 PROCESSOR OVERVIEW

The ADuCM320i/ADuCM322/ADuCM322i contain an embedded ARM Cortex-M3 processor, Revision r2p1. The ARM Cortex-M3

processor provides a high performance, low cost platform that meets the system requirements of minimal memory implementation,

reduced pin count, and low power consumption while delivering outstanding computational performance and exceptional system

response to interrupts.

ARM CORTEX-M3 PROCESSOR OPERATION

Several ARM Cortex-M3 processor components are flexible in their implementation. This section details the actual implementation of

these components in the ADuCM320i/ADuCM322/ADuCM322i.

Serial Wire Debug (SW/JTAG-DP)

The ADuCM320i/ADuCM322/ADuCM322i only support the serial wire interface via the SWCLK and SWDIO pins. It does not support

the 5-wire JTAG interface.

ROM Table

The ADuCM320i/ADuCM322/ADuCM322i implement the default ROM table.

Rev. D | Page 18 of 195

�ADuCM320i/ADuCM322/ADuCM322i Reference Manual

UG-868

Nested Vectored Interrupt Controller Interrupts (NVICs)

The ARM Cortex-M3 processor includes a NVIC, which offers several features:

•

•

•

•

Nested interrupt support

Vectored interrupt support

Dynamic priority changes support

Interrupt masking

In addition, the NVIC has a nonmaskable interrupt (NMI) input.

The NVIC is implemented on the ADuCM320i/ADuCM322/ADuCM322i, and more details are available in the System Exceptions and

Peripheral Interrupts section.

Wake-Up Interrupt Controller (WIC)

The ADuCM320i/ADuCM322/ADuCM322i have a modified WIC that provides the lowest possible power-down current. More details

on this feature are available in the Power Management Unit section. It is not recommended to enter power saving mode while servicing

an interrupt. However, if the device does enter power saving mode while servicing an interrupt, it can only wake up by a higher priority

interrupt source.

µDMA

The ADuCM320i/ADuCM322/ADuCM322i implement the ARM µDMA. More details are available in the Direct Memory Access

(DMA) Controller section.

ARM CORTEX-M3 PROCESSOR RELATED DOCUMENTS

•

•

•

•

•

•

Cortex-M3 Revision r2p1 Technical Reference Manual (DDI 0337)

ARM Processor Cortex-M3 (AT420) and Cortex-M3 with ETM AT425): Errata Notice

ARMv7-M Architecture Reference Manual (DDI 0403)

ARMv7-M Architecture Reference Manual Errata Markup

ARM Debug Interface v5 Architecture Specification (IHI 0031)

PrimeCell µDMA Controller (PL230) Technical Reference Manual Revision r0p0 (DDI 0417)

Rev. D | Page 19 of 195

�UG-868

ADuCM320i/ADuCM322/ADuCM322i Reference Manual

ADC CIRCUIT

ADC CIRCUIT FEATURES

The ADuCM320i/ADuCM322/ADuCM322i incorporate a fast, multichannel, 16-bit ADC. The ADC is specified to be 14-bit

(ADuCM320i) or 12-bit (ADuCM322/ADuCM322i) accurate.

A flexible input multiplexer supports 16 external inputs and 11 internal channels. The internal channels include the following:

•

•

•

•

•

•

•

A temperature sensor channel.

An internal 2.51 V reference.

An external reference.

Four IDAC channels. These are the voltage at each of the IDAC output pins (ADuCM320i only).

PVDD2 supply voltage (ADuCM320i only).

IOVDD/2 supply voltage.

AVDD/2 supply voltage.

For the ADuCM320i only, the input buffer can be selected for any channel to allow very low input current/input leakage specifications

on these input channels.

A high precision, low drift internal 2.51 V reference source is provided.

An external reference can also be connected to the ADC_REFP and ADC_REFN pins.

The programmable ADC update rate is from 19.55 kSPS to 1 MSPS.

An internal digital comparator is available for the AIN4 channel. An interrupt can be generated if the digital comparator detects an ADC

result above/below a user defined threshold.

Each channel has its own distinct data register for its conversion result. For example, when AIN0 is selected, the result appears in

ADCDAT0; if AIN7 is selected, the result appears in ADCDAT7. For a differential measurement, the result always appears in the data

register of the positive channel.

ADC CIRCUIT BLOCK DIAGRAM

I

AIN+

IBUF_BYP[1]

CAPACITOR

ARRAY

CONTROL

AIN0

P

BUSY

PRECHARGE

AIN15

INTERNAL

CHANNELS

CAPACITOR

ARRAY

COMP

CONTROL

LOGIC

P

OUTPUT CODE

ADCCHA

CNV

I

IBUF_BYP[0]

I = INPUT BUFFER

P = PRECHARGE BUFFER

Figure 5. ADC Circuit Block Diagram

Rev. D | Page 20 of 195

13437-004

AIN–

�ADuCM320i/ADuCM322/ADuCM322i Reference Manual

UG-868

ADC CIRCUIT OVERVIEW

The ADuCM320i/ADuCM322/ADuCM322i incorporates a fast, multichannel, 16-bit ADC. The ADC is specified to be 14-bit (ADuCM320i)

or 12-bit (ADuCM322/ADuCM322i) accurate. It can operate from a 2.9 V to 3.6 V supply and is capable of providing a throughput of up

to 1 MSPS. This ADC block provides the user with a multichannel multiplexer, input buffer for high impedance input channels (ADuCM320i

only), on-chip reference, and SAR ADC.

The SAR ADC circuit is implemented on the low voltage analog die. The ARM Cortex-M3 processor interfaces to the ADC via an

internal parallel die to die interface.

Depending on the input signal configuration, the ADC can operate in one of the following two modes:

•

•

Differential mode measures the difference between two signals.

Single-ended mode measures any signal relative to AGND.

The converter accepts an analog input range of 0 to VREF when operating in single-ended mode. In fully differential mode, the input

signal must be balanced around a common-mode voltage (VCM) in the 0 V to AVDD range and with a maximum amplitude of 2 × VREF.

AIN+

AVDD

AIN–

OUTPUT CODE

FS (VREF )

13437-105

0

–FS (–VREF )

Figure 6. Examples of Balanced Signals for Differential Mode

A high precision, low drift, factory-calibrated 2.51 V reference is provided on-chip. An external reference can also be connected to the

ADC_REFP and ADC_REFN pins.

Single or continuous conversion modes can be initiated in the software. An external pin (alternate function of P2.4) can also generate a

repetitive trigger for ADC conversions.

ADC CIRCUIT OPERATION

The SAR ADC is based on a charge redistribution DAC. The capacitive DAC consists of two identical arrays of 18 binary weighted

capacitors that are connected to the two inputs of the comparator.

The ADC converts the voltage applied to AIN+ and AIN− in the following three phases:

1.

2.

3.

During the precharge phase, the precharge buffers connect the inputs to the capacitor arrays, which charges the capacitors quickly

with minimal loading of the external input source.

During the acquisition phase, the capacitor arrays are connected directly to the inputs to fully charge the capacitor arrays and

eliminate any precharge buffer errors. The timing for the acquisition phase is set by ADCCNVC[25:16]. This value must be set to 500 ns. If

the input buffer is not used when measuring AVDD/2, IOVDD/2, or temperature sensor channels, set this value to 1.5 µs.

At the end of the acquisition phase, the internal CNV signal goes high and initiates the conversion phase. The conversion begins

with the SW+ and SW− switches opening, which disconnects the two capacitor arrays from the analog inputs and connects the

analog inputs to the AGND (−VREF) input. The conversion is completed by normal successive approximation.

The ADC block operates from an internally generated 20 MHz clock.

The ADC conversion rate is set by ADCCNVC[9:0].

Rev. D | Page 21 of 195

�UG-868

ADuCM320i/ADuCM322/ADuCM322i Reference Manual

ADC TRANSFER FUNCTION

Single-Ended Mode

In single-ended mode, the input range is 0 to VREF. The output coding is straight binary with

1 LSB = FS/65,536

or

VREF/65,536 = 2.51 V/65,536 = 38.30 µV

The data values in ADCDATx are aligned such that the MSB is in ADCDATx[27] and, therefore, the LSB is in ADCDATx[12]. The ideal

code transitions occur midway between successive integer LSB values (that is, 1/2 LSB, 3/2 LSB, 5/2 LSB, …, FS − 3/2 LSB). The ideal

input/output transfer characteristic is shown in Figure 7.

ADCDATx[31:12]

0000 1111 1111 1111 1111

0000 1111 1111 1111 1110

OUTPUT CODE

0000 1111 1111 1111 1101

0000 1111 1111 1111 1100

1LSB =

VREF

65536

0000 0000 0000 0000 0011

0000 0000 0000 0000 0010

0000 0000 0000 0000 0001

0V 1LSB

VREF – 1LSB

VOLTAGE INPUT

NOTES

1. IN ADCDATx, x IS 0 TO 27, AS SHOWN IN TABLE 10.

13437-013

0000 0000 0000 0000 0000

Figure 7. ADC Transfer Function: Single-Ended Mode

Differential Mode

The amplitude of the differential signal is the difference between the signals applied to the AIN+ and AIN− pins (that is, AIN+ − AIN−).

The maximum amplitude of the differential signal is, therefore, −VREF to +VREF p-p (2 × VREF), regardless of the common mode (CM). The

common mode is the average of the two signals (AIN+ + AIN−)/2 and is, therefore, the voltage that the two inputs are centered on. This

results in the span of each input being CM ± VREF/2. This voltage must be set up externally, and its range varies with VREF. The voltage at

the AIN+ and AIN− pins must be within the allowed input voltage range.

The output coding is twos complement in fully differential mode, with

1 LSB = 2 × VREF/65,536

or

2 × 2.51 V/65,536 = 76.60 µV

where VREF = 2.51 V.

The data values in ADCDATx are aligned such that the MSB is in ADCDATx[27] and, therefore, the LSB is in ADCDATx[13]. The ideal

input/output transfer characteristic is shown in Figure 8.

Rev. D | Page 22 of 195

�ADuCM320i/ADuCM322/ADuCM322i Reference Manual

UG-868

ADCDATx[31:12]

0000 0000 1111 1111 1110

0000 0000 1111 1111 1100

1LSB =

2 × VREF

65536

OUTPUT CODE

0000 0000 1111 1111 1010

0000 0000 0000 0000 0010

0000 0000 0000 0000 0000

1111 1111 1111 1111 1110

1111 0000 0000 0000 0100

1111 0000 0000 0000 0000

–VREF + 1LSB

0LSB

+VREF – 1LSB

VOLTAGE INPUT (VIN+ – VIN–)

NOTES

1. IN ADCDATx, x IS 0 TO 27, AS SHOWN IN TABLE 10.

13437-014

1111 0000 0000 0000 0010

Figure 8. ADC Transfer Function: Differential Mode

ADC TYPICAL SETUP SEQUENCE

After being configured via the ADC control and channel selection registers, the ADC converts the analog input and provides a 16-bit

result in the ADC data registers.

The following is an example sequence to set up the ADC and generate a single conversion on AIN0 using a single-ended measurement:

1.

2.

3.

Configure the device as follows:

ADCCON = 0x280;

// Power up the ADC, enable reference buffer, idle mode.

ADCCHA = 0x1100;

// Select AIN0 as the positive ADC input (AIN+) and ADC_REFN as

the negative ADC input (AIN−).

ADCCNVC = 0xA00C8;

// Select 100 kSPS ADC update rate and 500 ns acquisition time.

ADCCON | = 0x2;

// Enable single conversion.

Wait for the low voltage die interrupt

iADCRESULT = ADCDAT0;

// Read the ADC result.

Note that if the ADC is set from continuous conversion mode to idle mode after a full ADC sequence is completed, ADCSEQ[31] must

be set to 1 before starting another sequence and reconfiguring the ADC back to continuous conversion mode to ensure that the

sequencer restarts with the first selected channel in ADCSEQ.

ADC INPUT BUFFER

An optional input buffer can be enabled for any ADC input channel on the ADuCM320i only.

The control register, IBUFCON, controls the input buffer switches as follows:

•

•

IBUF_BYP (IBUFCON[1:0]) controls the bypass switches on the ADC input buffer. If the input buffer is required on either the

positive or negative input, the bypass switch must be turned off.

IBUF_PD (IBUFCON[3:2]) powers up or powers down the ADC input buffer.

Rev. D | Page 23 of 195

�UG-868

ADuCM320i/ADuCM322/ADuCM322i Reference Manual

ADC INTERNAL CHANNELS

Temperature Sensor Settings

The ADuCM320i/ADuCM322/ADuCM322i provide a voltage output from an on-chip band gap reference that is proportional to the

absolute temperature of the low voltage die. This voltage output is routed through the front end of the ADC multiplexer (effectively, an

additional ADC channel input), facilitating an internal temperature sensor channel that measures die temperature.

The internal temperature sensor is not designed for use as an absolute ambient temperature calculator. Its intended use is as an

approximate indicator of the temperature of the ADuCM320i/ADuCM322/ADuCM322i low voltage analog die.

An ADC temperature sensor conversion differs from a standard ADC voltage. The ADC performance specifications do not apply to the

temperature sensor.

When the temperature sensor channel is selected, the ADC update rate must be 80 kSPS.

The ADC automatically changes the ADC update rate to 80 kSPS when the temperature sensor, AVDD/2, or IOVDD/2 input channel is

selected. If a different ADC sampling rate is required for other channels after the conversion on any of these three channels is completed,

the ADCCNVC register must be updated.

Note that when the sequencer is enabled and includes any of these three channels, the value in the ADCCNVC register does not change

and the ADC sampling rate does not change.

The temperature sensor settings are as follows.

Enable the temperature sensor on the ADC; set ADCCHA[12:0] = 0x1116.

To calculate the die temperature, use the following formula:

T − TREF = (VADC − VTREF) × K

where:

T is the temperature result.

TREF is 25°C.

VADC is the average ADC result from two consecutive conversions.

VTREF is the ADC result in millivolts that corresponds to TREF = 25°C. The user must measure this in their own application because this

value varies from device to device. The typical value used for demonstration purposes is 1290 mV.

K is the gain of the ADC in temperature sensor mode. The user must determine the gain by performing a two-point temperature

calibration because this value varies from device to device. The typical value used for demonstration purposes only is 4.394 mV/°C.

This 4.394 mV/°C value corresponds to 1/V TC.

Using the default values from the ADuCM320i, the ADuCM322, the ADuCM322i data sheets without any calibration, the equation becomes

T − 25°C = (VADC − 1290) × 1/K

Therefore, assuming VADC at 25°C = 1290 mV and slope mV/C = 4.394 mV/C,

T = ((VADC − 1290)/4.394) + 25

where:

VADC is in millivolts.

See the latest version of the ADuCM320i, the ADuCM322, the ADuCM322i data sheets for the most up to date figures.

For increased accuracy, perform a two-point calibration at a controlled temperature value.

The values used in this example for VTREF and K are not guaranteed values. The VTREF and K values vary from device to device; therefore,

the user must derive the appropriate values by performing a calibration at ambient temperature.

AVDD/2 and IOVDD/2 Supply Voltage Channels

These supply voltage channels are measured via internal resistor dividers. Because the resistors used are high impedance and the divided

voltage is not buffered, a slower ADC update rate must be used.

The ADC automatically changes the ADC update rate to 80 kSPS when the temperature sensor, AVDD/2, or IOVDD/2 input channel is

selected. If a different ADC sampling rate is required for other channels after the conversion on any of these three channels is completed,

the ADCCNVC register must be updated.

Note that when the sequencer is enabled and includes any of these three channels, the value in the ADCCNVC register does not change and the

ADC sampling rate does not change. At rates above 80 kSPS, the accuracy is reduced on the ADuCM320i if the input buffer is disabled.

Rev. D | Page 24 of 195

�ADuCM320i/ADuCM322/ADuCM322i Reference Manual

UG-868

ADC SUPPORT CIRCUITS

IDAC Channels (ADuCM320i Only)

The ADuCM320i allows the voltage on the IDAC output pins to be selected as inputs to the ADC. These channels are useful for

determining the power consumed by each IDAC.

ADC Digital Comparator

A digital comparator is provided to allow an interrupt to be triggered if the ADC data result is above or below a programmable threshold.

Only the AIN4 external input channel can be used with the digital comparator.

To set up the ADC digital comparator, note the following:

•

•

•

•

•

•

ADCCMP[17:2] set a 16-bit ADC threshold value.

ADCCMP[1] configures the comparator to be triggered when the ADC result is above or below the threshold value.

To enable the ADC comparator interrupt, set INTSEL[2] = 1 to enable the digital comparator to the Low Voltage Die Interrupt 1 signal.

Similarly, set INTSEL[10] = 1 to enable the digital comparator interrupt to the Low Voltage Die Interrupt 0 signal.

The comparator output is asserted when the value in ADCDAT4[27:12] rises above the value in ADCCMP[17:2] if ADCCMP[1] =

1. If ADCDAT4[27:12] remains above ADCCMP[17:2], no further comparator interrupts occur. The interrupt only occurs when the

comparator circuit detects a rise above the threshold.

Similarly, if ADCCMP[1] = 0, the comparator output is asserted when the value in ADCDAT4[27:12] falls below the value in

ADCCMP[17:2]. If ADCDAT4[27:12] remains below ADCCMP[17:2], no further comparator interrupts occur. The interrupt only

occurs when the comparator circuit detects a fall below the threshold value.

ADC Channel Sequencer

An ADC sequencer is provided to reduce the processor overhead of sampling and reading individual channels. The ADC sequencer

allows the user to select the number and order of ADC input channels that the ADC samples and provides a single interrupt source that

is asserted when the sequence ends. The sequencer can also be programmed to restart automatically without a delay or with a

programmable delay between the end and start of sequences.

Some additional details about the sequencer include the following.

The sequencer reads the ADCSEQ[0:28] register to determine which channels need to be included and which need to be excluded from

the execution sequence.

ADCSEQ corresponds to the ADCCHA[4:0] for the list of ADC input channels. For example, to include AIN9, set ADCSEQ[9].

To enable the sequencer as the Low Voltage Die Interrupt 1 source, set INTSEL[1] = 1. To enable the sequencer as the Low Voltage Die

Interrupt 0 source, set INTSEL[9] = 1.

To start the sequencer, set ADCSEQ[31:30] = 0x3.

The ADCSEQC[27:20] register bits set the delay between finishing one sequence of channels and starting another sequence.

Normally, single-ended measurements are assumed by the ADC with AGND as the negative reference. However, for Channel 0, Channel 2,

Channel 4, and Channel 6, a differential measurement can be selected by configuring the appropriate bits in ADCSEQC[19:0]. For

example, ADCSEQC[4:0] selects the negative input when AIN0 is the positive. For single-ended measurements using the sequencer and

AIN0, ADCSEQC[4:0] must be set to 0x11 for VREFN_NADC (ADC_REFN pin).

On the ADuCM320i, take care when using the sequencer if the input buffer is enabled. The IBUFCON register controls the input buffer.

If the input buffer is enabled, all channels sampled in a sequence are sampled with the input buffer enabled. It is recommended to split

sequences into the following:

•

•

•

Sample unbuffered channels together in one sequence.

Sample buffered channels in a separate sequence.

If full accuracy results are required for the AVDD/2, IOVDD/2, or temperature channels, take care when measuring with the

sequencer. With the input buffer disabled, the acquisition time must be set to 1.5 µs via ADCCONV[25:16] = 0x1E. Alternatively,

enable the input buffer.

Rev. D | Page 25 of 195

�UG-868

ADuCM320i/ADuCM322/ADuCM322i Reference Manual

ADC Direct Memory Access (DMA)

The ADC or the ADC sequencer can be selected as the source channel for the DMA controller. This reduces processor overhead by

moving ADC results directly into SRAM with a single interrupt asserted when the required number of ADC conversions has been

completely logged to memory.

When using the ADC sequencer with the DMA controller, it is recommended to use DMA autorequest transfer types rather than basic

transfer types.

ADC Voltage Reference Selection

The ADuCM320i/ADuCM322/ADuCM322i integrate a low drift, 2.5 V ADC reference source. By default, this internal reference is

enabled and selected as the reference source for the ADC. When using the internal 2.5 V voltage reference, ensure the following:

•

•

ADCCON[7] = 1 to power up the internal reference buffer