LT1738

Slew Rate Controlled

Ultralow Noise DC/DC Controller

U

DESCRIPTIO

FEATURES

■

■

■

■

■

■

■

■

■

The LT ®1738 is a switching regulator controller designed

to lower conducted and radiated electromagnetic interference (EMI). Ultralow noise and EMI are achieved by

controlling the voltage and current slew rates of an external N-channel MOSFET switch. Current and voltage slew

rates can be independently set to optimize harmonic

content of the switching waveforms vs efficiency. The

LT1738 can reduce high frequency harmonic power by as

much as 40dB with only minor losses in efficiency.

The LT1738 utilizes a current mode architecture optimized for single switch topologies such as boost, flyback

and Cuk. The IC includes gate drive and all necessary

oscillator, control and protection circuitry. Unique error

amp circuitry can regulate both positive and negative

voltages. The internal oscillator may be synchronized to

an external clock for more accurate placement of switching harmonics.

Greatly Reduced Conducted and Radiated EMI

Low Switching Harmonic Content

Independent Control of Output Switch Voltage and

Current Slew Rates

Greatly Reduced Need for External Filters

Single N-Channel MOSFET Driver

20kHz to 250kHz Oscillator Frequency

Easily Synchronized to External Clock

Regulates Positive and Negative Voltages

Easier Layout Than with Conventional Switchers

U

APPLICATIO S

■

■

■

■

■

■

Power Supplies for Noise Sensitive Communication

Equipment

EMI Compliant Offline Power Supplies

Precision Instrumentation Systems

Isolated Supplies for Industrial Automation

Medical Instruments

Data Acquisition Systems

Protection features include gate drive lockout for low VIN,

soft-start, output current limit, short-circuit current limiting, gate drive overvoltage clamp and input supply

undervoltage lockout.

, LTC and LT are registered trademarks of Linear Technology Corporation.

U

TYPICAL APPLICATIO

Ultralow Noise 5V to 12V Converter

22µH

5V

VIN

MBRD620

P3

+

100µF

17

VIN

14

5

6

1.3nF

7

16.9k

25k

25k

3.3k

3.3k

22nF

0.22µF

8

16

15

12

B

4 × 150µF

OSCON

CAP

10µH

150µF

OSCON

A

+

12V

1A

OPTIONAL

3

GCL

SHDN

+

12V Output Noise

(Bandwidth = 100MHz)

5pF

POINT A

ON SCHEMATIC

500µV/DIV

2

V5

400µVP-P

SYNC

CT

GATE

1

Si9426

POINT B

ON SCHEMATIC

50mV/DIV

LT1738

RT

RVSL

CS

4

25mΩ

RCSL

PGND

VC

SS

1.5k

13

GND

11

FB

NFB

10

20

21.5k

9

5µs/DIV

1738 TA01a

2.5k

1738 TA01

10nF

1738fa

1

�LT1738

W

U

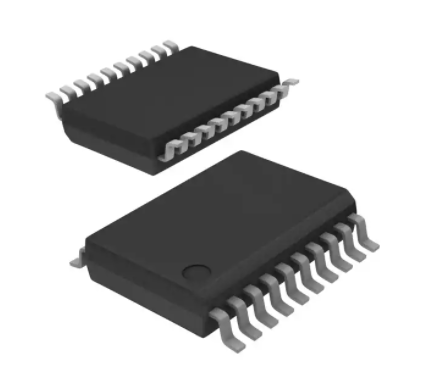

PACKAGE/ORDER I FOR ATIO

U

W W

W

ABSOLUTE

U

AXI U RATI GS

(Note 1)

Supply Voltage (VIN) ................................................ 20V

Gate Drive Current ..................................... Internal Limit

V5 Current ................................................. Internal Limit

SHDN Pin Voltage .................................................... 20V

Feedback Pin Voltage (Trans. 10ms) ...................... ±10V

Feedback Pin Current ............................................ 10mA

Negative Feedback Pin Voltage (Trans. 10ms) ........ ±10V

CS Pin .......................................................................... 5V

GCL Pin ..................................................................... 16V

SS Pin .......................................................................... 3V

Operating Junction Temperature Range

(Note 3) ............................................ – 40°C to 125°C

Storage Temperature Range ................. – 65°C to 150°C

Lead Temperature (Soldering, 10 sec).................. 300°C

TOP VIEW

GATE

1

20 PGND

CAP

2

19 NC

GCL

3

18 NC

CS

4

17 VIN

LT1738EG

LT1738IG

V5

5

16 RVSL

SYNC

6

15 RCSL

CT

7

14 SHDN

RT

8

13 SS

FB

9

12 VC

NFB 10

ORDER PART

NUMBER

11 GND

G PACKAGE

20-LEAD PLASTIC SSOP

TJMAX = 150°C, θJA = 110°C/ W

Consult LTC Marketing for parts specified with wider operating temperature ranges.

ELECTRICAL CHARACTERISTICS

The ● denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at TA = 25°C. VIN = 12V, VC = 0.9V, VFB = VREF, RVSL, RCSL = 16.9k, RT = 16.9k and

other pins open unless otherwise noted.

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

1.235

1.250

1.265

V

250

1000

nA

Error Amplifiers

VREF

Reference Voltage

Measured at Feedback Pin

●

IFB

Feedback Input Current

VFB = VREF

●

FBREG

Reference Voltage Line Regulation

2.7V ≤ VIN ≤ 20V

●

VNFR

Negative Feedback Reference Voltage

Measured at Negative Feedback Pin

with Feedback Pin Open

●

INFR

Negative Feedback Input Current

VNFB = VNFR

NFBREG

Negative Feedback Reference Voltage Line Regulation

2.7V ≤ VIN ≤ 20V

gm

Error Amplifier Transconductance

∆IC = ±50µA

0.012

0.03

%/V

–2.56

– 2.50

–2.45

V

–37

– 25

µA

0.009

0.03

%/V

1500

●

1100

700

2200

2500

µmho

µmho

●

IESK

Error Amp Sink Current

VFB = VREF + 150mV, VC = 0.9V

●

120

200

350

µA

IESRC

Error Amp Source Current

VFB = VREF – 150mV, VC = 0.9V

●

120

200

350

µA

VCLH

Error Amp Clamp Voltage

High Clamp, VFB = 1V

VCLL

Error Amp Clamp Voltage

Low Clamp, VFB = 1.5V

AV

Error Amplifier Voltage Gain

FBOV

FB Overvoltage Shutdown

ISS

Soft-Start Charge Current

1.27

V

0.12

V

250

V/V

Outputs Drivers Disabled

1.47

V

VSS = 1V

9.0

180

12

µA

1738fa

2

�LT1738

ELECTRICAL CHARACTERISTICS

The ● denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at TA = 25°C. VIN = 12V, VC = 0.9V, VFB = VREF, RVSL, RCSL = 16.9k, RT = 16.9k and

other pins open unless otherwise noted.

SYMBOL

PARAMETER

CONDITIONS

MIN

Oscillator Frequency = 250kHz

290

TYP

MAX

UNITS

Oscillator and Sync

fMAX

Max Switch Frequency

fSYNC

Synchronization Frequency Range

VSYNC

SYNC Pin Input Threshold

RSYNC

SYNC Pin Input Resistance

250

●

0.7

kHz

kHz

1.4

2

40

kΩ

90

93.5

%

10

7.6

10.4

7.9

10.7

8.1

V

V

0.2

0.35

V

Gate Drive

DCMAX

Maximum Switch Duty Cycle

RVSL = RCSL = 3.9k,

Osc Frequency = 25kHz

VGON

Gate On Voltage

VIN = 12, GCL = 12

VIN = 12, GCL = 8

VGOFF

Gate Off Voltage

VIN = 12V

IGSO

Max Gate Source Current

VIN = 12V

0.3

A

IGSK

Max Gate Sink Current

VIN = 12V

0.3

A

VINUVLO

Gate Drive Undervoltage Lockout (Note 5)

VGCL = 6.5V

●

7.3

7.5

V

Current Sense

tIBL

Switch Current Limit Blanking Time

VSENSE

Sense Voltage Shutdown Voltage

VSENSEF

Sense Voltage Fault Threshold

100

VC Pulled Low

●

86

ns

103

120

mV

220

300

mV

Slew Control for the Following Slew Tests See Test Circuit in Figure 1b

VSLEWR

Output Voltage Slew Rising Edge

RVSL = RCSL = 17k

26

V/µs

VSLEWF

Output Voltage Slew Falling Edge

RVSL = RCSL = 17k

19

V/µs

VISLEWR

Output Current Slew Rising Edge (CS pin V)

RVSL = RCSL = 17k

2.1

V/µs

VISLEWF

Output Current Slew Falling Edge (CS pin V)

RVSL = RCSL = 17k

2.1

V/µs

Supply and Protection

VINMIN

Minimum Input Voltage (Note 4)

VGCL = VIN

IVIN

Supply Current (Note 3)

RVSL = RCSL = 17k

RVSL = RCSL = 17k

VSHDN

Shutdown Turn-On Threshold

●

∆VSHDN

Shutdown Turn-On Voltage Hysteresis

●

VIN = 12

VIN = 20

●

2.55

3.6

V

●

12

35

40

55

mA

mA

1.31

1.39

1.48

V

50

110

180

mV

ISHDN

Shutdown Input Current Hysteresis

10

24

35

µA

V5

5V Reference Voltage

6.5V ≤ VIN ≤ 20V, IV5 = 5mA

6.5V ≤ VIN ≤ 20V, IV5 = – 5mA

4.85

4.80

5

5

5.20

5.15

V

V

IV5SC

5V Reference Short-Circuit Current

VIN = 6.5V Source

VIN = 6.5V Sink

10

–10

●

Note 1: Absolute Maximum Ratings are those values beyond which the

life of a device may be impaired.

Note 2: Supply current specification includes loads on each gate as in

Figure 1a. Actual supply currents vary with operating frequency, operating

voltages, V5 load, slew rates and type of external FET.

Note 3: The LT1738E is guaranteed to meet performance specifications

from 0°C to 70°C. Specifications from –40°C to 125°C are assured by

mA

mA

design, characterization and correlation with statistical process

controls.The LT1738I is guaranteed and tested to meet performance

specifications from – 40°C to 125°C.

Note 4: Output gate drive is enabled at this voltage. The GCL voltage will

also determine driver activity.

Note 5: Gate drive is ensured to be on when VIN is greater than max value.

1738fa

3

�LT1738

U W

TYPICAL PERFOR A CE CHARACTERISTICS

Negative Feedback Voltage and

Input Current vs Temperature

2.480

3.2

1.258

700

2.485

3.0

1.256

650

2.490

2.8

1.254

600

1.252

550

2.495

2.6

1.250

500

2.500

2.4

1.248

450

2.505

2.2

1.246

400

2.510

2.0

1.244

350

1.242

300

2.515

1.8

1.240

–50 –25

0

NEGATIVE FEEDBACK VOLTAGE (V)

750

2.520

–50 –25

250

25 50 75 100 125 150

TEMPERATURE (°C)

0

1.6

25 50 75 100 125 150

TEMPERATURE (°C)

1738 G01

Feedback Overvoltage Shutdown

vs Temperature

Error Amp Transconductance vs

Temperature

Error Amp Output Current vs

Feedback Pin Voltage from Nominal

500

1900

400

1800

300

1700

200

1.55

1.50

1.45

1.40

1.35

1.30

1.25

1.20

–50 –25

0

25 50 75 100 125 150

TEMPERATURE (°C)

CURRENT (µA)

2000

1.65

TRANSCONDUCTANCE (µmho)

FEEDBACK VOLTAGE (V)

1738 G02

1.70

1.60

1600

1500

1400

–300

1100

–400

1738 G03

SHDN Pin On and Off Thresholds

vs Temperature

1.50

240

CLAMP

220

1.0

0.8

0.6

0.4

THRESHOLD

FAULT

1.45

SHDN PIN VOLTAGE (V)

CS PIN VOLTAGE (mV)

VC PIN VOLTAGE (V)

1738 G05

CS Pin Trip Voltage and CS Fault

Voltage vs Temperature

1.4

200

180

160

140

120

ON

1.40

1.35

1.30

TRIP

0.2

0

–50 –25

–500

–400 –300 –200 –100 0 100 200 300 400

FEEDBACK PIN VOLTAGE FROM NOMINAL (mV)

1738 G04

VC Pin Threshold and Clamp

Voltage vs Temperature

1.2

125°C

–100

–200

25 50 75 100 125 150

TEMPERATURE (°C)

25°C

0

1200

0

–40°C

100

1300

1000

–50 –25

NFB INPUT CURRENT (µA)

1.260

FB INPUT CURRENT (nA)

FEEDBACK VOLTAGE (V)

Feedback Voltage and Input

Current vs Temperature

OFF

100

0

25 50 75 100 125 150

TEMPERATURE (°C)

1738 G06

80

–50 –25

0

25 50 75 100 125 150

TEMPERATURE (°C)

1738 G07

1.25

–50 –25

0

25 50 75 100 125 150

TEMPERATURE (°C)

1738 G08

1738fa

4

�LT1738

U W

TYPICAL PERFOR A CE CHARACTERISTICS

SHDN Pin Hysteresis Current vs

Temperature

27

21

19

17

0

25 50 75 100 125 150

TEMPERATURE (°C)

VIN = 20 RVSL, RCSL = 17k

14

13

VIN = 12 RVSL, RCSL = 17k

0.2

GATE DRIVE A/B PIN VOLTAGE (V)

PERCENT OF MAX CS VOLTAGE

80

70

60

40

60

DUTY CYCLE (%)

80

100

10.6

GCL = 12V

10.5

6.5

0.50

6.4

0.45

6.2

10.3

6.1

VIN = 12V

NO LOAD

10.2

6.0

10.1

5.9

10.0

5.8

GCL = 6V

9.90

5.7

9.80

5.6

9.70

–50 –25

9.3

0.25

0.20

0.15

0.10

0.05

5.5

0

25 50 75 100 125 150

TEMPERATURE (°C)

0

–50 –25

V5 Voltage vs Load Current

5.08

5.06

8.7

8.5

8.3

8.1

7.9

6.4

7.7

0

25 50 75 100 125 150

TEMPERATURE (°C)

1738 G15

25 50 75 100 125 150

TEMPERATURE (°C)

SS VOLTAGE = 0.9V

8.9

6.5

6.3

–50 –25

0

1738 G14

V5 PIN VOLTAGE (V)

6.6

VIN = 12V

NO LOAD

0.30

9.1

SS PIN CURRENT (µA)

7.1

120

0.35

9.5

GCL = 6V

6.7

100

0.40

Soft-Start Current vs Temperature

7.3

6.8

40

60

80

CS PIN VOLTAGE (mV)

1738 G13

Gate Drive Undervoltage Lockout

Voltage vs Temperature

6.9

20

1738 G11

6.3

10.4

1738 G12

7.0

0

Gate Drive Low Voltage vs

Temperature

10.7

90

7.2

0

Gate Drive High Voltage vs

Temperature

VC PIN = 0.9V

TA = 25°C

20

0.6

1738 G10

110

0

0.8

11 USING LOAD OF FIGURE 1A

fOSC = 120kHz

10

–50 –25 0

25 50 75 100 125 150

TEMPERATURE (°C)

Slope Compensation

50

1.0

0.4

1738 G09

100

1.2

12

GATE DRIVE A/B PIN VOLTAGE (V)

15

–50 –25

15

VC PIN VOLTAGE (V)

16

23

TA = 25°C

1.4

VIN = 12 RVSL, RCSL = 4.85k

17

VIN CURRENT (mA)

SHDN PIN CURRENT (µA)

1.6

18

25

VIN PIN VOLTAGE (V)

CS Pin to VC Pin Transfer

Function

VIN Current vs Temperature

7.5

–50 –25

T = 125°C

5.04

5.02

T = 25°C

5.00

T = –40°C

4.98

0

25 50 75 100 125 150

TEMPERATURE (°C)

1738 G16

4.96

–15

–10

–5

0

5

LOAD CURRENT (mA)

10

15

1738 G17

1738fa

5

�LT1738

U

U

U

PI FU CTIO S

Part Supply

V5 (Pin 5): This pin provides a 5V output that can sink or

source 10mA for use by external components. V5 source

current comes from VIN . Sink current goes to GND. VIN

must be greater than 6.5V in order for this voltage to be in

regulation. If this pin is used, a small capacitor ( VGCL + 0.8V. If this pin

is tied to VIN, then undervoltage lockout is disabled.

There is an internal 19V zener tied from this pin to ground

to provide a fail-safe for maximum gate voltage.

Slew Control

CAP (Pin 2): This pin is the feedback node for the external

voltage slewing capacitor. Normally a small 1pf to 5pf

capacitor is connected from this pin to the drain of the

MOSFET.

The voltage slew rate is inversely proportional to this

capacitance and proportional to the current that the part

will sink and source on this pin. That current is inversely

proportional to RVSL.

RCSL (Pin 15): A resistor to ground sets the current slew

rate for the external drive MOSFET during switching. The

minimum resistor value is 3.3k and the maximum value is

68k. The time to slew between on and off states of the

MOSFET current will determine how the di/dt related

harmonics are reduced. This time is proportional to RCSL

and RS (the current sense resistor) and maximum current.

Longer times produce a greater reduction of higher frequency harmonics.

RVSL (Pin 16): A resistor to ground sets the voltage slew

rate for the drain of the external drive MOSFET. The

minimum resistor value is 3.3k and the maximum value is

68k. The time to slew between on and off states on the

MOSFET drain voltage will determine how dv/dt related

harmonics are reduced. This time is proportional to RVSL,

CV and the input voltage. Longer times produce more

rolloff of harmonics. CV is the equivalent capacitance from

CAP to the drain of the MOSFET.

Switch Mode Control

SS (Pin 3): The SS pin allows for ramping of the switch

current threshold at startup. Normally a capacitor is placed

on this pin to ground. An internal 9µA current source will

charge this capacitor up. The voltage on the VC pin cannot

exceed the voltage on SS. Thus peak current will ramp up

as the SS pin ramps up. During a short circuit fault the SS

pin will be discharged to ground thus reinitializing softstart.

When SS is below the VC clamp voltage the VC pin will

closely track the SS pin.

This pin can be left open if not used.

CS (Pin 4): This is the input to the current sense amplifier.

It is used for both current mode control and current

slewing of the external MOSFET. Current sense is accomplished via a sense resistor (RS) connected from the

source of the external MOSFET to ground. CS is connected

to the top of RS. Current sense is referenced to the GND

pin.

The switch maximum operating current will be equal to

0.1V/RS. At CS = 0.1V, the gate driver will be immediately

turned off (no slew control).

If CS = 0.22V in addition to the drivers being turned off, VC

and SS will be discharged to ground (short-circuit protection). This will hasten turn off on subsequent cycles.

FB (Pin 9): The feedback pin is used for positive voltage

sensing. It is the inverting input to the error amplifier. The

noninverting input of this amplifier connects internally to

a 1.25V reference.

If the voltage on this pin exceeds the reference by 220mV,

then the output driver will immediately turn off the external

MOSFET (no slew control). This provides for output overvoltage protection

When this input is below 0.9V then the current sense

blanking will be disabled. This will assist start up.

NFB (Pin 10): The negative feedback pin is used for

sensing a negative output voltage. The pin is connected to

the inverting input of the negative feedback amplifier

through a 100k source resistor. The negative feedback

amplifier provides a gain of –0.5 to the FB pin. The nominal

regulation point would be –2.5V on NFB. This pin should

be left open if not used.

If NFB is being used then overvoltage protection will occur

at 0.44V below the NFB regulation point.

At NFB < –1.8 current sense blanking will be disabled.

1738fa

7

�LT1738

U

U

U

PI FU CTIO S

TEST CIRCUITS

VC (Pin 12): The compensation pin is used for frequency

compensation and current limiting. It is the output of the

error amplifier and the input of the current comparator.

Loop frequency compensation can be performed with an

RC network connected from the VC pin to ground. The

voltage on VC is proportional to the switch peak current.

The normal range of voltage on this pin is 0.25V to 1.27V.

However, during slope compensation the upper clamp

voltage is allowed to increase with the compensation.

During a short-circuit fault the VC pin will be discharged to

ground.

0.9A

20mA

5pF

5pF

IN5819

IN5819

CAP

CAP

GATE

GATE

Si4450DY

ZVN3306A

2

CS

+

–

10

0.1

10

+

–

1738 F01b

1738 F01a

Figure 1a. Typical Test Circuitry Figure 1b. Test Circuit for Slew

W

BLOCK DIAGRA

SHDN

VIN

V5

RCSL

RVSL

14

17

5

15

16

TO

DRIVERS

+

REGULATOR

NEGATIVE

FEEDBACK

AMP

–

100k

3 GCL

VREG

50k

NFB 10

2 CAP

–

FB 9

+

1 GATE

ERROR

AMP

SLEW

CONTROL

+

1.25V

VC 12

20 PGND

–

+

COMP

SS 13

4 CS

SENSE

AMP

+

–

S

Q

FF

RT 8

R

OSCILLATOR

SUB

CT 7

6

11

SYNC

GND

1738 BD

1738fa

8

�LT1738

U

OPERATIO

In noise sensitive applications switching regulators tend

to be ruled out as a power supply option due to their

propensity for generating unwanted noise. When switching supplies are required due to efficiency or input/output

constraints, great pains must be taken to work around the

noise generated by a typical supply. These steps may

include pre and post regulator filtering, precise synchronization of the power supply oscillator to an external clock,

synchronizing the rest of the circuit to the power supply

oscillator or halting power supply switching during noise

sensitive operations. The LT1738 greatly simplifies the

task of eliminating supply noise by enabling the design of

an inherently low noise switching regulator power supply.

transconductance amplifier that integrates the difference

between the feedback output voltage and an internal

1.25V reference. The output of the error amp adjusts the

switch current trip point to provide the required load

current at the desired regulated output voltage. This

method of controlling current rather than voltage provides faster input transient response, cycle-by-cycle

current limiting for better output switch protection and

greater ease in compensating the feedback loop. The VC

pin is used for loop compensation and current limit

adjustment. During normal operation the VC voltage will

be between 0.25V and 1.27V. An external clamp on VC or

SS may be used for lowering the current limit.

The LT1738 is a fixed frequency, current mode switching

regulator with unique circuitry to control the voltage and

current slew rates of the output switch. Current mode

control provides excellent AC and DC line regulation and

simplifies loop compensation.

The negative voltage feedback amplifier allows for direct

regulation of negative output voltages. The voltage on the

NFB pin gets amplified by a gain of – 0.5 and driven on to

the FB input, i.e., the NFB pin regulates to –2.5V while the

amplifier output internally drives the FB pin to 1.25V as in

normal operation. The negative feedback amplifier input

impedance is 100k (typ) referred to ground.

Slew control capability provides much greater control

over the power supply components that can create conducted and radiated electromagnetic interference. Compliance with EMI standards will be an easier task and will

require fewer external filtering components.

The LT1738 uses an external N-channel MOSFET as the

power switch. This allows the user to tailor the drive

conditions to a wide range of voltages and currents.

CURRENT MODE CONTROL

Referring to the block diagram. A switching cycle begins

with an oscillator discharge pulse, which resets the RS

flip-flop, turning on the GATE driver and the external

MOSFET. The switch current is sensed across the external

sense resistor and the resulting voltage is amplified and

compared to the output of the error amplifier (VC pin). The

driver is turned off once the output of the current sense

amplifier exceeds the voltage on the VC pin. In this way

pulse by pulse current limit is achieved.

Internal slope compensation is provided to ensure stability under high duty cycle conditions.

Output regulation is obtained using the error amp to set

the switch current trip point. The error amp is a

Soft-Start

Control of the switch current during start up can be

obtained by using the SS pin. An external capacitor from

SS to ground is charged by an internal 9µA current source.

The voltage on VC cannot exceed the voltage on SS. Thus

as the SS pin ramps up the VC voltage will be allowed to

ramp up. This will then provide for a smooth increase in

switch maximum current. SS will be discharged as a result

of the CS voltage exceeding the short circuit threshold of

approximately 0.22V.

Slew Control

Control of output voltage and current slew rates is achieved

via two feedback loops. One loop controls the MOSFET

drain dV/dt and the other loop controls the MOSFET dI/dt.

The voltage slew rate uses an external capacitor between

CAP and the MOSFET drain. This integrating cap closes the

voltage feedback loop. The external resistor RVSL sets the

current for the integrator. The voltage slew rate is thus

inversely proportional to both the value of capacitor and

RVSL.

1738fa

9

�LT1738

U

OPERATIO

The current slew feedback loop consists of the voltage

across the external sense resistor, which is internally

amplified and differentiated. The derivative is limited to a

value set by RCSL. The current slew rate is thus inversely

proportional to both the value of sense resistor and RCSL.

The two control loops are combined internally so that a

smooth transition from current slew control to voltage

slew control is obtained. When turning on, the driver

current will slew before voltage. When turning off, voltage

will slew before current. In general it is desirable to have

RVSL and RCSL of similar value.

Internal Regulator

Most of the control circuitry operates from an internal 2.4V

low dropout regulator that is powered from VIN. The

internal low dropout design allows VIN to vary from 2.7V

to 20V with stable operation of the controller. When SHDN

< 1.3V the internal regulator is completely disabled.

5V Regulator

A 5V regulator is provided for powering external circuitry.

This regulator draws current from VIN and requires VIN to

be greater than 6.5V to be in regulation. It can sink or

source 10mA. The output is current limited to prevent

against destruction from accidental short circuits.

Safety and Protection Features

There are several safety and protection features on the

chip. The first is overcurrent limit. Normally the gate driver

will go low when the output of the internal sense amplifier

exceeds the voltage on the VC pin. The VC pin is clamped

such that maximum output current is attained when the CS

pin voltage is 0.1V. At that level the outputs will be

immediately turned off (no slew). The effect of this control

is that the output voltage will foldback with overcurrent.

In addition, if the CS voltage exceeds 0.22V, the VC and SS

pins will be discharged to ground, resetting the soft-start

function. Thus if a short is present this will allow for faster

MOSFET turnoff and less MOSFET stress.

If the voltage on the FB pin exceeds regulation by approximately 0.22V, the outputs will immediately go low. The

implication is that there is an overvoltage fault.

The voltage on GCL determines two features. The first is

the maximum gate drive voltage. This will protect the

MOSFET gate from overvoltage.

With GCL tied to a zener or an external voltage source then

the maximum gate driver voltage is approximately

VGCL␣ – 0.2V. If GCL is tied to VIN, then the maximum gate

voltage is determined by VIN and is approximately

VIN – 1.6V. There is an internal 19V zener on the GCL pin

that prevents the gate driver pin from exceeding approximately 19V.

In addition, the GCL voltage determines undervoltage

lockout of the gate drive. This feature disables the gate

driver if VIN is too low to provide adequate voltage to turn

on the MOSFET. This is helpful during start up to insure the

MOSFET has sufficient gate drive to saturate.

If GCL is tied to a voltage source or zener less than 6.8V,

the gate driver will not turn on until VIN exceeds GCL

voltage by 0.8V. For VGCL above 6.5V, the gate drive is

insured to be off for VIN < 7.3V and it will be turned on by

VGCL + 0.8V.

If GCL is tied to VIN, the gate driver is always on

(undervoltage lockout is disabled).

The gate drive has current limits for the drive currents. If

the sink or source current is greater than 300mA then the

current will be limited.

The V5 regulator also has internal current limiting that will

only guarantee ±10mA output current.

There is also an on chip thermal shutdown circuit that will

turn off the output in the event the chip temperature rises

to dangerous levels. Thermal shutdown has hysteresis

that will cause a low frequency ( VREG + 0.22V

(Output Overvoltage)

Immediately Goes Low

Overridden

None

GCL Clamp

Set Max Gate Voltage to Prevent

FET Gate Breakdown

Limits Max Voltage

None

None

Gate Drive

Undervoltage Lockout

Disable Gate Drive When VIN

Is Too Low. Set Via GCL Pin

Immediately Goes Low

Overridden

None

Thermal Shutdown

Turn Off Driver If Chip

Temperature Is Too Hot

Immediately Goes Low

Overridden

None

VIN Undervoltage Lockout

Disable Part When VIN ≅ 2.55V

Immediately Goes Low

Overridden

None

Gate Drive Source and Sink Current Limit

Limit Gate Drive Current

Limit Drive Current

None

None

V5 Source/Sink Current Limit

Limit Current from V5

None

None

None

Shutdown

Disable Part When SHDN VGCL + 0.8V. This could be used to bias a zener.

The GCL pin has an internal 19V zener to ground that will

provide a failsafe for maximum gate voltage.

As an example say we are using a Siliconix Si4480DY

which has RDS(ON) rated at 6V. To get 6V, VGCL needs to

be set to 6.2V and VIN needs to be at least 7.6V.

Gate Driver Considerations

In general, the MOSFET should be positioned as close to

the part as possible to minimize inductance.

When the part is active the gate drive will be pulled low to

less than 0.2V. When the part is off, the gate drive contains

a 40k resistor in series with a diode to ground that will offer

passive holdoff protection. If you are using some logic

level MOSFETs this might not be sufficient. A resistor may

be placed from gate to ground, however the value should

be reasonably high to minimize DC losses and possible AC

issues.

The gate drive source current comes from VIN. The sink

current exits through PGND. In general the decoupling cap

should be placed close to these two pins.

Switching Diodes

In general, switching diodes should be Schottky diodes.

Size and breakdown voltage depend on the specific converter. A lower forward drop will improve converter efficiency. No other special requirements are needed.

PCB LAYOUT CONSIDERATIONS

As with any switcher, careful consideration should be given

to PC board layout. Because this part reduces high frequency EMI, the board layout is less critical. However, high

currents and voltages still produce the need for careful

board layout to eliminate poor and erratic performance.

Basic Considerations

Keep the high current loops physically small in area. The

main loops are shown in Figure 6: the power switch loops

(A) and the rectifier loop (B). These loops can be kept small

by physically keeping the components close to one another. In addition, connection traces should be kept wide

to lower resistance and inductances. Components should

be placed to minimize connecting paths. Careful attention

to ground connections must also be maintained. Be careful that currents from different high current loops do not

get coupled into the ground paths of other loops. Using

singular points of connection for the grounds is the best

way to do this. The two major points of connection are the

bottom of the input decoupling capacitor and the bottom

of the output decoupling capacitor. Typically, the sense

resistor device PGND and device GND will tie to the bottom

of the input capacitor.

VIN

CIN

•

A

•

B

COUT VOUT

GATE

CS

1738 F06

Figure 6

1738fa

18

�LT1738

U

U

W

U

APPLICATIO S I FOR ATIO

There are two other loops to pay attention to. The current

slew involves a high bandwidth control that goes through

the MOSFET switch, the sense resistor and into the CS pin

of the part and out the GATE pin to the MOSFET. Trace

inductance and resistance should be kept low on the GATE

drive trace. The CS trace should have low inductance.

MORE HELP

AN70 contains information about low noise switchers and

measurement of noise and should be consulted. AN19 and

AN29 also have general knowledge concerning switching

regulators. Also, our Application Department is always

ready to lend a helping hand.

Finally, care should be taken with the CAP pin. The part will

tolerate stray capacitance to ground on this pin (