LT3758/LT3758A

High Input Voltage,

Boost, Flyback, SEPIC and

Inverting Controller

DESCRIPTION

FEATURES

Wide Input Voltage Range: 5.5V to 100V

n Positive or Negative Output Voltage Programming

with a Single Feedback Pin

n Current Mode Control Provides Excellent Transient

Response

n Programmable Operating Frequency (100kHz to

1MHz) with One External Resistor

n Synchronizable to an External Clock

n Low Shutdown Current < 1µA

n Internal 7.2V Low Dropout Voltage Regulator

n Programmable Input Undervoltage Lockout with

Hysteresis

n Programmable Soft-Start

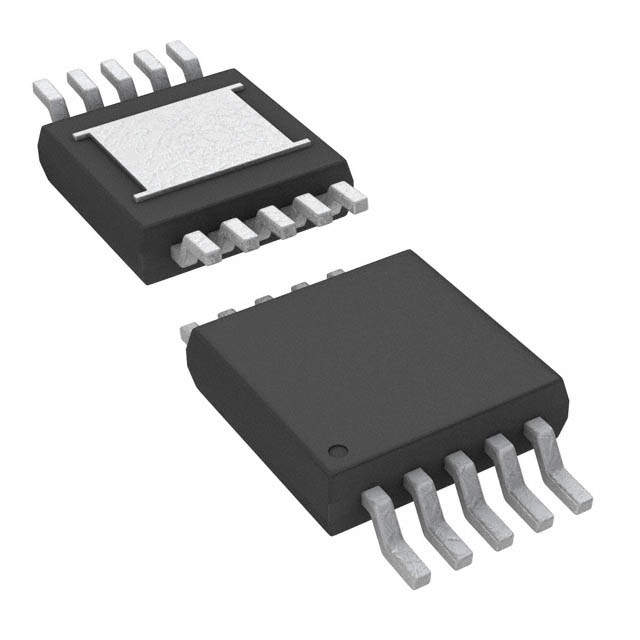

n Small 10-Lead DFN (3mm × 3mm) and

MSOPE Packages

n AEC-Q100 Qualification Is in Progress

The LT®3758/LT3758A are wide input range, current

mode, DC/DC controllers which are capable of generating

either positive or negative output voltages. They can be

configured as either a boost, flyback, SEPIC or inverting

converter. The LT3758/LT3758A drive a low side external

N-channel power MOSFET from an internal regulated 7.2V

supply. The fixed frequency, current-mode architecture

results in stable operation over a wide range of supply

and output voltages.

APPLICATIONS

The LT3758/LT3758A feature soft-start and frequency

foldback functions to limit inductor current during startup and output short-circuit. The LT3758A has improved

load transient performance compared to the LT3758.

n

The operating frequency of LT3758/LT3758A can be set

with an external resistor over a 100kHz to 1MHz range,

and can be synchronized to an external clock using the

SYNC pin. A minimum operating supply voltage of 5.5V,

and a low shutdown quiescent current of less than 1µA,

make the LT3758/LT3758A ideally suited for batterypowered systems.

Automotive

Telecom

n Industrial

n

n

All registered trademarks and trademarks are the property of their respective owners.

TYPICAL APPLICATION

12V Output Nonisolated Flyback Power Supply

VIN

36V TO

72V

D1

CIN

2.2µF

100V

X7R

0.022µF

100V

1M

6.2k

VIN

SYNC

LT3758

SW

GATE

M1

FBX

GND INTVCC

VC

1N4148

0.47µF

100pF

105k

1%

SENSE

RT

SS

63.4k

200kHz

4,5,6

(PARALLEL)

DSN

SHDN/UVLO

44.2k

T1

1,2,3

(SERIES)

VOUT

12V

1.2A

10k

10nF

CVCC

4.7µF

10V

X5R

5.1Ω

0.030Ω

15.8k

1%

COUT

47µF

X5R

3758 TA01

Rev G

Document Feedback

For more information www.analog.com

1

�LT3758/LT3758A

ABSOLUTE MAXIMUM RATINGS

(Note 1)

VIN, SHDN/UVLO (Note 7).......................................100V

INTVCC.....................................................VIN + 0.3V, 20V

GATE......................................................... INTVCC + 0.3V

SYNC...........................................................................8V

VC, SS..........................................................................3V

RT................................................................................................ 1.5V

SENSE.....................................................................±0.3V

FBX.................................................................. –6V to 6V

Operating Junction Temperature Range (Notes 2, 8)

LT3758E/LT3758AE............................ –40°C to 125°C

LT3758I/LT3758AI.............................. –40°C to 125°C

LT3758H/LT3758AH........................... –40°C to 150°C

LT3758MP/LT3758AMP...................... –55°C to 150°C

Storage Temperature Range

DFN..................................................... –65°C to 125°C

MSOP................................................. –65°C to 150°C

Lead Temperature (Soldering, 10 sec) MSOP......... 300°C

PIN CONFIGURATION

TOP VIEW

VC

1

FBX

2

SS

3

RT

4

SYNC

5

11

GND

TOP VIEW

10 VIN

9 SHDN/UVLO

VC

FBX

SS

RT

SYNC

8 INTVCC

7 GATE

6 SENSE

DD PACKAGE

10-LEAD (3mm × 3mm) PLASTIC DFN

TJMAX = 125°C, θJA = 43°C/W

EXPOSED PAD (PIN 11) IS GND, MUST BE SOLDERED TO PCB

1

2

3

4

5

11

GND

10

9

8

7

6

VIN

SHDN/UVLO

INTVCC

GATE

SENSE

MSE PACKAGE

10-LEAD PLASTIC MSOP

TJMAX = 150°C, θJA = 40°C/W

EXPOSED PAD (PIN 11) IS GND, MUST BE SOLDERED TO PCB

ORDER INFORMATION

LEAD FREE FINISH

TAPE AND REEL

PART MARKING*

PACKAGE DESCRIPTION

TEMPERATURE RANGE

LT3758EDD#PBF

LT3758EDD#TRPBF

LDNK

10-Lead (3mm × 3mm) Plastic DFN

–40°C to 125°C

LT3758IDD#PBF

LT3758IDD#TRPBF

LDNK

10-Lead (3mm × 3mm) Plastic DFN

–40°C to 125°C

LT3758EMSE#PBF

LT3758EMSE#TRPBF

LTDNM

10-Lead (3mm × 3mm) Plastic MSOP

–40°C to 125°C

LT3758IMSE #PBF

LT3758IMSE#TRPBF

LTDNM

10-Lead (3mm × 3mm) Plastic MSOP

–40°C to 125°C

LT3758HMSE#PBF

LT3758HMSE#TRPBF

LTDNM

10-Lead (3mm × 3mm) Plastic MSOP

–40°C to 150°C

LT3758MPMSE #PBF

LT3758MPMSE#TRPBF

LTDNM

10-Lead (3mm × 3mm) Plastic MSOP

–55°C to 150°C

LT3758AEDD#PBF

LT3758AEDD#TRPBF

LGGS

10-Lead (3mm × 3mm) Plastic DFN

–40°C to 125°C

LT3758AIDD#PBF

LT3758AIDD#TRPBF

LGGS

10-Lead (3mm × 3mm) Plastic DFN

–40°C to 125°C

LT3758AEMSE#PBF

LT3758AEMSE#TRPBF

LTGGK

10-Lead (3mm × 3mm) Plastic MSOP

–40°C to 125°C

LT3758AIMSE#PBF

LT3758AIMSE#TRPBF

LTGGK

10-Lead (3mm × 3mm) Plastic MSOP

–40°C to 125°C

LT3758AHMSE#PBF

LT3758AHMSE#TRPBF

LTGGK

10-Lead (3mm × 3mm) Plastic MSOP

–40°C to 150°C

LT3758AMPMSE#PBF

LT3758AMPMSE#TRPBF

LTGGK

10-Lead (3mm × 3mm) Plastic MSOP

–55°C to 150°C

2

Rev G

For more information www.analog.com

�LT3758/LT3758A

ORDER INFORMATION

LEAD FREE FINISH

TAPE AND REEL

PART MARKING*

PACKAGE DESCRIPTION

TEMPERATURE RANGE

LT3758AIDD#WTRPBF

LGGS

10-Lead (3mm × 3mm) Plastic DFN

–40°C to 125°C

AUTOMOTIVE PRODUCTS**

LT3758AIDD#WPBF

Contact the factory for parts specified with wider operating temperature ranges. *The temperature grade is identified by a label on the shipping container.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

**Versions of this part are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. These

models are designated with a #W suffix. Only the automotive grade products shown are available for use in automotive applications. Contact your

local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for

these models.

ELECTRICAL

CHARACTERISTICS

The

l denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at TA = 25°C. VIN = 24V, SHDN/UVLO = 24V, SENSE = 0V, unless otherwise noted.

PARAMETER

CONDITIONS

MIN

VIN Operating Range

TYP

5.5

MAX

UNITS

100

V

VIN Shutdown IQ

SHDN/UVLO = 0V

SHDN/UVLO = 1.15V

0.1

1

6

µA

µA

VIN Operating IQ

VC = 0.3V, RT = 41.2k

1.75

2.2

mA

VIN Operating IQ with Internal LDO Disabled

VC = 0.3V, RT = 41.2k, INTVCC = 7.5V

350

400

µA

110

120

mV

SENSE Current Limit Threshold

SENSE Input Bias Current

l

100

Current Out of Pin

–65

µA

Error Amplifier

FBX Regulation Voltage (VFBX(REG))

FBX > 0V (Note 3)

FBX < 0V (Note 3)

FBX Overvoltage Lockout

FBX > 0V (Note 4)

FBX < 0V (Note 4)

FBX Pin Input Current

FBX = 1.6V (Note 3)

FBX = –0.8V (Note 3)

Transconductance gm (∆IVC /∆FBX)

(Note 3)

230

µS

VC Output Impedance

(Note 3)

5

MΩ

VFBX Line Regulation (∆VFBX /[∆VIN • VFBX(REG)])

FBX > 0V, 5.5V < VIN < 100V (Notes 3, 6)

FBX < 0V, 5.5V < VIN < 100V (Notes 3, 6)

l

l

1.569

–0.816

1.6

–0.800

1.631

–0.784

V

V

6

7

8

11

10

14

%

%

70

100

10

nA

nA

–10

0.006

0.005

VC Current Mode Gain (∆VVC /∆VSENSE)

0.025

0.03

%/V

%/V

5.5

V/V

VC Source Current

VC = 1.5V

–15

µA

VC Sink Current

FBX = 1.7V

FBX = –0.85V

12

11

µA

µA

Oscillator

Switching Frequency

RT = 41.2k to GND, FBX = 1.6V

RT = 140k to GND, FBX = 1.6V

RT = 10.5k to GND, FBX = 1.6V

RT Voltage

FBX = 1.6V

270

300

100

1000

330

kHz

kHz

kHz

1.2

V

Minimum Off-Time

220

ns

Minimum On-Time

220

ns

SYNC Input Low

0.4

SYNC Input High

SS Pull-Up Current

1.5

SS = 0V, Current Out of Pin

–10

µA

Rev G

For more information www.analog.com

3

�LT3758/LT3758A

ELECTRICAL

CHARACTERISTICS

The

l denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at TA = 25°C. VIN = 24V, SHDN/UVLO = 24V, SENSE = 0V, unless otherwise noted.

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

7

7.2

7.4

V

4.3

4.5

0.5

4.7

V

V

Low Dropout Regulator

INTVCC Regulation Voltage

INTVCC Undervoltage Lockout Threshold

l

Falling INTVCC

UVLO Hysteresis

INTVCC Overvoltage Lockout Threshold

17.5

INTVCC Current Limit

VIN = 100V

VIN = 20V

11

16

50

INTVCC Load Regulation (∆VINTVCC / VINTVCC)

0 < IINTVCC < 10mA, VIN = 8V

–1

–0.4

INTVCC Line Regulation (∆VINTVCC / [∆VIN • VINTVCC])

8V < VIN < 100V

Dropout Voltage (VIN – VINTVCC)

VIN = 6V, IINTVCC = 10mA

500

INTVCC Current in Shutdown

SHDN/UVLO = 0V, INTVCC = 8V

16

0.005

INTVCC Voltage to Bypass Internal LDO

V

22

mA

mA

%

0.02

%/V

mV

µA

7.5

V

1.27

V

0.4

V

Logic Inputs

SHDN/UVLO Threshold Voltage Falling

VIN = INTVCC = 8V

SHDN/UVLO Input Low Voltage

IVIN Drops Below 1µA

SHDN/UVLO Pin Bias Current Low

SHDN/UVLO = 1.15V

2

2.5

µA

SHDN/UVLO Pin Bias Current High

SHDN/UVLO = 1.33V

10

100

nA

t r Gate Driver Output Rise Time

CL = 3300pF (Note 5), INTVCC = 7.5V

22

ns

t f Gate Driver Output Fall Time

CL = 3300pF (Note 5), INTVCC = 7.5V

20

ns

l

1.17

1.7

1.22

Gate Driver

Gate Output Low (VOL)

0.05

Gate Output High (VOH)

INTVCC

–0.05

Note 1: Stresses beyond those listed under Absolute Maximum Ratings

may cause permanent damage to the device. Exposure to any Absolute

Maximum Rating condition for extended periods may affect device

reliability and lifetime.

Note 2: The LT3758E/LT3758AE are guaranteed to meet performance

specifications from the 0°C to 125°C junction temperature. Specifications

over the –40°C to 125°C operating junction temperature range are

assured by design, characterization and correlation with statistical process

controls. The LT3758I/LT3758AI are guaranteed over the full –40°C to

125°C operating junction temperature range. The LT3758H/LT3758AH are

guaranteed over the full –40°C to 150°C operating junction temperature

range. High junction temperatures degrade operating lifetimes. Operating

lifetime is derated at junction temperatures greater than 125°C. The

LT3758MP/LT3758AMP are 100% tested and guaranteed over the full

–55°C to 150°C operating junction temperature range.

4

V

V

Note 3: The LT3758/LT3758A are tested in a feedback loop which servos

VFBX to the reference voltages (1.6V and –0.8V) with the VC pin forced

to 1.3V.

Note 4: FBX overvoltage lockout is measured at VFBX(OVERVOLTAGE) relative

to regulated VFBX(REG).

Note 5: Rise and fall times are measured at 10% and 90% levels.

Note 6: SHDN/UVLO = 1.33V when VIN = 5.5V.

Note 7: For VIN below 6V, the SHDN/UVLO pin must not exceed VIN .

Note 8: The LT3758/LT3758A include overtemperature protection that

is intended to protect the device during momentary overload conditions.

Junction temperature will exceed the maximum operating junction

temperature when overtemperature protection is active. Continuous

operation above the specified maximum operating junction temperature

may impair device reliability.

Rev G

For more information www.analog.com

�LT3758/LT3758A

TYPICAL PERFORMANCE CHARACTERISTICS

–790

VIN = 100V

1600

VIN = 24V

1595

VIN = 8V

1590

VIN = INTVCC = 5.5V

SHDN/UVLO = 1.33V

1585

1580

–75 –50 –25

0 25 50 75 100 125 150

TEMPERATURE (°C)

REGULATED FEEDBACK VOLTAGE (mV)

REGULATED FEEDBACK VOLTAGE (mV)

1605

Positive Feedback Voltage

vs Temperature, VIN

TA = 25°C, unless otherwise noted.

Negative Feedback Voltage

vs Temperature, VIN

VIN = INTVCC = 5.5V

SHDN/UVLO = 1.33V

–792

–794

VIN = 8V

–796

–798

VIN = 100V

–800

VIN = 24V

–802

–804

–75 –50 –25

0 25 50 75 100 125 150

TEMPERATURE (°C)

3758 G01

1.9

3758 G02

Quiescent Current

vs Temperature, VIN

Dynamic Quiescent Current

vs Switching Frequency

35

CGATE = 3300pF

1.8

25

VIN = 100V

IQ(mA)

QUIESCENT CURRENT (mA)

30

1.7

VIN = 24V

20

15

10

1.6

5

VIN = INTVCC = 5.5V

1.5

–75 –50 –25

0

0 25 50 75 100 125 150

TEMPERATURE (°C)

0 100 200 300 400 500 600 700 800 900 1000

SWITCHING FREQUENCY (kHz)

3758 G03

Normalized Switching

Frequency vs FBX

RT vs Switching Frequency

NORMALIZED FREQUENCY (%)

120

RT (kΩ)

1000

100

10

3758 G04

0 100 200 300 400 500 600 700 800 900 1000

SWITCHING FREQUENCY (kHz)

100

80

60

40

20

0

–0.8

–0.4

3758 G05

0

0.4

0.8

FBX VOLTAGE (V)

1.2

1.6

3758 G06

Rev G

For more information www.analog.com

5

�LT3758/LT3758A

TYPICAL PERFORMANCE CHARACTERISTICS

Switching Frequency

vs Temperature

SENSE Current Limit Threshold

vs Temperature

120

RT = 41.2K

320

115

SENSE THRESHOLD (mV)

SWITCHING FREQUENCY (kHz)

330

TA = 25°C, unless otherwise noted.

310

300

290

110

105

280

270

–75 –50 –25

100

–75 –50 –25

0 25 50 75 100 125 150

TEMPERATURE (°C)

0 25 50 75 100 125 150

TEMPERATURE (°C)

3758 G08

3758 G07

SENSE Current Limit Threshold

vs Duty Cycle

SHDN/UVLO Threshold

vs Temperature

1.28

110

SHDN/UVLO VOLTAGE (V)

SENSE THRESHOLD (mV)

115

105

100

95

0

20

40

60

DUTY CYCLE (%)

100

80

1.26

SHDN/UVLO RISING

1.24

1.22

SHDN/UVLO FALLING

1.20

1.18

–75 –50 –25

3758 G10

3758 G09

SHDN/UVLO Hysteresis Current

vs Temperature

SHDN/UVLO Current vs Voltage

2.4

40

2.2

ISHDN/ UVLO (µA)

SHDN/UVLO CURRENT (µA)

50

30

20

2.0

1.8

10

0

0

20

40

60

80

SHDN/UVLO VOLTAGE (V)

100

1.6

–75 –50 –25

3758 G11

6

0 25 50 75 100 125 150

TEMPERATURE (°C)

0 25 50 75 100 125 150

TEMPERATURE (°C)

3758 G12

Rev G

For more information www.analog.com

�LT3758/LT3758A

TYPICAL PERFORMANCE CHARACTERISTICS

INTVCC Minimum Output

Current vs VIN

INTVCC vs Temperature

45

TJ = 150°C

40

INTVCC CURRENT (mA)

7.2

7.1

30

25

INTVCC = 4.7V

20

15

10

0

1

10

VIN (V)

1000

DROPOUT VOLTAGE (mV)

INTVCC VOLTAGE (V)

7.20

7.15

VIN = 6V

800

90

150°C

10 20 30 40 50 60 70 80 90 100

VIN (V)

125°C

75°C

600

25°C

500

400

200

FALL TIME

RISE TIME

50

40

30

–55°C

20

10

0

0

2

4

6

INTVCC LOAD (mA)

8

10

0

0

5

10

15

3758 G17

25

30

3758 G18

FBX Frequency Foldback

Waveforms During Overcurrent

VIN = 48V

CL = 3300pF

20

CL (nF)

Typical Start-Up Waveforms

VIN = 48V

VOUT

20V/DIV

RISE TIME

20

TIME (ns)

25

INTVCC = 7.2V

60

0°C

300

Gate Drive Rise

and Fall Time vs INTVCC

25

20

70

700

3758 G16

30

15

10

INTVCC LOAD (mA)

Gate Drive Rise

and Fall Time vs CL

80

100

0

5

3758 G15

INTVCC Dropout Voltage

vs Current, Temperature

INTVCC Line Regulation

7.25

0

3758 G14

900

7.10

7

6.8

100

3758 G13

7.30

7.1

6.9

INTVCC = 6V

5

0 25 50 75 100 125 150

TEMPERATURE (°C)

VIN = 8V

7.2

35

TIME (ns)

INTVCC (V)

7.3

INTVCC Load Regulation

7.3

INTVCC VOLTAGE (V)

7.4

7.0

–75 –50 –25

TA = 25°C, unless otherwise noted.

FALL TIME

VOUT

10V/DIV

VSW

50V/DIV

IL1A + IL1B

1A/DIV

IL1A + IL1B

2A/DIV

15

10

5

0

2ms/DIV

3

6

9

INTVCC (V)

12

15

3758 G20

SEE TYPICAL APPLICATION: 18V TO 72V INPUT,

24V OUTPUT SEPIC CONVERTER

50µs/DIV

3758 G21

SEE TYPICAL APPLICATION: 18V TO 72V INPUT,

24V OUTPUT SEPIC CONVERTER

3758 G19

Rev G

For more information www.analog.com

7

�LT3758/LT3758A

PIN FUNCTIONS

VC (Pin 1): Error Amplifier Compensation Pin. Used to

stabilize the voltage loop with an external RC network.

FBX (Pin 2): Positive and Negative Feedback Pin.

Receives the feedback voltage from the external resistor

divider across the output. Also modulates the switching

frequency during start-up and fault conditions when FBX

is close to GND.

SS (Pin 3): Soft-Start Pin. This pin modulates compensation pin voltage (VC) clamp. The soft-start interval is set

with an external capacitor. The pin has a 10µA (typical)

pull-up current source to an internal 2.5V rail. The softstart pin is reset to GND by an undervoltage condition

at SHDN/UVLO, an INTVCC undervoltage or overvoltage

condition or an internal thermal lockout.

RT (Pin 4): Switching Frequency Adjustment Pin. Set the

frequency using a resistor to GND. Do not leave this pin

open.

SYNC (Pin 5): Frequency Synchronization Pin. Used to

synchronize the switching frequency to an outside clock.

If this feature is used, an RT resistor should be chosen

to program a switching frequency 20% slower than the

SYNC pulse frequency. Tie the SYNC pin to GND if this

feature is not used. SYNC is bypassed when FBX is close

to GND.

SENSE (Pin 6): The Current Sense Input for the Control

Loop. Kelvin connect this pin to the positive terminal of

the switch current sense resistor in the source of the

NFET. The negative terminal of the current sense resistor should be connected to GND plane close to the IC.

8

GATE (Pin 7): N-Channel MOSFET Gate Driver Output.

Switches between INTVCC and GND. Driven to GND when

IC is shut down, during thermal lockout or when INTVCC

is above or below the overvoltage or UV thresholds,

respectively.

INTVCC (Pin 8): Regulated Supply for Internal Loads and

Gate Driver. Supplied from VIN and regulated to 7.2V (typical). INTVCC must be bypassed with a minimum of 4.7µF

capacitor placed close to pin. INTVCC can be connected

directly to VIN, if VIN is less than 17.5V. INTVCC can also

be connected to a power supply whose voltage is higher

than 7.5V, and lower than VIN, provided that supply does

not exceed 17.5V.

SHDN/UVLO (Pin 9): Shutdown and Undervoltage Detect

Pin. An accurate 1.22V (nominal) falling threshold with

externally programmable hysteresis detects when power

is okay to enable switching. Rising hysteresis is generated

by the external resistor divider and an accurate internal

2µA pull-down current. An undervoltage condition resets

sort-start. Tie to 0.4V, or less, to disable the device and

reduce VIN quiescent current below 1µA.

VIN (Pin 10): Input Supply Pin. Must be locally bypassed

with a 0.22µF, or larger, capacitor placed close to the pin.

Exposed Pad (Pin 11): Ground. This pin also serves as

the negative terminal of the current sense resistor. The

exposed pad must be soldered directly to the local ground

plane.

Rev G

For more information www.analog.com

�LT3758/LT3758A

BLOCK DIAGRAM

CDC

L1

D1

VOUT

•

VIN

R4

+

R3

CIN

L2

•

9

2.5V

IS3

IS2

10µA

VC

1

CC2

A10

IS1

2µA

2.5V

CC1

1.72V

–0.88V

–

+

–

+

A12

G6

VC

2

8

+

–

5V UP

4.5V DOWN

G5

R

S

GATE

G2

O

A6

VISENSE

RAMP

1.28V

RAMP

GENERATOR

–

+A3

G1

+

+

–

SS

M1

–

+

+

A5

–

110mV

SENSE

6

GND

RSENSE

100kHz-1MHz

OSCILLATOR

A4

Q1

FREQ

PROG

RT

SYNC

5

CSS

7

11

D3

3

CVCC

PWM

COMPARATOR

1.2V

D2

INTVCC

DRIVER

–

+A7

FREQUENCY

FOLDBACK

R5

8k

CURRENT

LIMIT

7.2V LDO

SLOPE

+

A2

–

–0.8V

VIN

SR1

+

A1

–

1.6V

FBX

A8

TSD

165˚C

Q2

FBX

G3

A11

17.5V

+

A9

–

UVLO

Q3

RC

COUT2

1.22V

INTERNAL

REGULATOR

AND UVLO

G4

R2 + COUT1

R1

10

SHDN/UVLO

–

+

FBX

4

3758 F01

RT

Figure 1. LT3758 Block Diagram Working as a SEPIC Converter

Rev G

For more information www.analog.com

9

�LT3758/LT3758A

APPLICATIONS INFORMATION

Main Control Loop

The LT3758 uses a fixed frequency, current mode control scheme to provide excellent line and load regulation.

Operation can be best understood by referring to the

Block Diagram in Figure 1.

The start of each oscillator cycle sets the SR latch (SR1)

and turns on the external power MOSFET switch M1

through driver G2. The switch current flows through the

external current sensing resistor RSENSE and generates a

voltage proportional to the switch current. This current

sense voltage VISENSE (amplified by A5) is added to a

stabilizing slope compensation ramp and the resulting

sum (SLOPE) is fed into the positive terminal of the PWM

comparator A7. When SLOPE exceeds the level at the

negative input of A7 (VC pin), SR1 is reset, turning off the

power switch. The level at the negative input of A7 is set

by the error amplifier A1 (or A2) and is an amplified version of the difference between the feedback voltage (FBX

pin) and the reference voltage (1.6V or –0.8V, depending

on the configuration). In this manner, the error amplifier sets the correct peak switch current level to keep the

output in regulation.

The LT3758 has a switch current limit function. The current sense voltage is input to the current limit comparator A6. If the SENSE pin voltage is higher than the sense

current limit threshold VSENSE(MAX) (110mV, typical), A6

will reset SR1 and turn off M1 immediately.

The LT3758 is capable of generating either positive or

negative output voltage with a single FBX pin. It can be

configured as a boost, flyback or SEPIC converter to generate positive output voltage, or as an inverting converter

to generate negative output voltage. When configured as

a SEPIC converter, as shown in Figure 1, the FBX pin is

pulled up to the internal bias voltage of 1.6V by a voltage divider (R1 and R2) connected from VOUT to GND.

Comparator A2 becomes inactive and comparator A1 performs the inverting amplification from FBX to VC. When

the LT3758 is in an inverting configuration, the FBX pin

is pulled down to –0.8V by a voltage divider connected

from VOUT to GND. Comparator A1 becomes inactive and

comparator A2 performs the noninverting amplification

from FBX to VC.

10

The LT3758 has overvoltage protection functions to protect the converter from excessive output voltage overshoot during start-up or recovery from a short-circuit

condition. An overvoltage comparator A11 (with 20mV

hysteresis) senses when the FBX pin voltage exceeds the

positive regulated voltage (1.6V) by 8% and provides a

reset pulse. Similarly, an overvoltage comparator A12

(with 10mV hysteresis) senses when the FBX pin voltage

exceeds the negative regulated voltage (–0.8V) by 11%

and provides a reset pulse. Both reset pulses are sent to

the main RS latch (SR1) through G6 and G5. The power

MOSFET switch M1 is actively held off for the duration of

an output overvoltage condition.

Programming Turn-On and Turn-Off Thresholds with

the SHDN/UVLO Pin

The SHDN/UVLO pin controls whether the LT3758 is

enabled or is in shutdown state. A micropower 1.22V

reference, a comparator A10 and a controllable current

source IS1 allow the user to accurately program the supply

voltage at which the IC turns on and off. The falling value

can be accurately set by the resistor dividers R3 and R4.

When SHDN/UVLO is above 0.4V, and below the 1.22V

threshold, the small pull-down current source IS1 (typical

2µA) is active.

The purpose of this current is to allow the user to program

the rising hysteresis. The Block Diagram of the comparator and the external resistors is shown in Figure 1. The

typical falling threshold voltage and rising threshold voltage can be calculated by the following equations:

V VIN,FALLING = 1.22 •

(R3+R4)

R4

V VIN,RISING = 2µA • R3+ VIN,FALLING

For applications where the SHDN/UVLO pin is only used

as a logic input, the SHDN/UVLO pin can be connected

directly to the input voltage VIN through a 1k resistor for

always-on operation.

Rev G

For more information www.analog.com

�LT3758/LT3758A

APPLICATIONS INFORMATION

INTVCC Regulator Bypassing and Operation

QG = power MOSFET total gate charge

An internal, low dropout (LDO) voltage regulator produces

the 7.2V INTVCC supply which powers the gate driver, as

shown in Figure 1. The LT3758 contains an undervoltage

lockout comparator A8 and an overvoltage lockout comparator A9 for the INTVCC supply. The INTVCC undervoltage

(UV) threshold is 4.5V (typical), with 0.5V hysteresis, to

ensure that the MOSFETs have sufficient gate drive voltage

before turning on. The logic circuitry within the LT3758 is

also powered from the internal INTVCC supply.

The LT3758 uses packages with an Exposed Pad for

enhanced thermal conduction. With proper soldering to

the Exposed Pad on the underside of the package and a

full copper plane underneath the device, thermal resistance (θJA) will be about 43°C/W for the DD package and

40°C/W for the MSE package. For an ambient board temperature of TA = 70°C and maximum junction temperature

of 125°C, the maximum IDRIVE (IDRIVE(MAX)) of the DD

package can be calculated as:

The INTVCC overvoltage threshold is set to be 17.5V

(typical) to protect the gate of the power MOSFET. When

INTVCC is below the UV threshold, or above the overvoltage threshold, the GATE pin will be forced to GND and the

soft-start operation will be triggered.

The INTVCC regulator must be bypassed to ground immediately adjacent to the IC pins with a minimum of 4.7µF

ceramic capacitor. Good bypassing is necessary to supply the high transient currents required by the MOSFET

gate driver.

TJ = TA + PIC • θJA

TA = ambient temperature

Based on the preceding equation and the INTVCC Minimum

Output Current vs VIN graph, the user can calculate the

maximum MOSFET gate charge the LT3758 can drive at

a given VIN and switch frequency. A plot of the maximum

QG vs VIN at different frequencies to guarantee a minimum

4.7V INTVCC is shown in Figure 2.

140

100

80

60

40

PIC = IC power consumption

20

0

= VIN • (IQ + IDRIVE)

f = switching frequency

1MHz

1

10

VIN (V)

IQ = VIN operation IQ = 1.6mA

IDRIVE = average gate drive current = f • QG

300kHz

120

θJA = junction-to-ambient thermal resistance

(TJ − TA )

1.28W

−IQ =

−1.6mA

(θ JA • VIN )

VIN

The LT3758 has an internal INTVCC IDRIVE current limit

function to protect the IC from excessive on-chip power

dissipation. The IDRIVE current limit decreases as the VIN

increases (see the INTVCC Minimum Output Current vs VIN

graph in the Typical Performance Characteristics section).

If IDRIVE reaches the current limit, INTVCC voltage will fall

and may trigger the soft-start.

QG (nC)

In an actual application, most of the IC supply current is

used to drive the gate capacitance of the power MOSFET.

The on-chip power dissipation can be a significant concern when a large power MOSFET is being driven at a

high frequency and the VIN voltage is high. It is important to limit the power dissipation through selection of

MOSFET and/or operating frequency so the LT3758 does

not exceed its maximum junction temperature rating. The

junction temperature TJ can be estimated using the following equations:

IDRIVE(MAX) =

100

3758 F02

Figure 2. Recommended Maximum QG vs VIN at Different

Frequencies to Ensure INTVCC Higher Than 4.7V

Rev G

For more information www.analog.com

11

�LT3758/LT3758A

APPLICATIONS INFORMATION

As illustrated in Figure 2, a trade-off between the operating frequency and the size of the power MOSFET may be

needed in order to maintain a reliable IC junction temperature. Prior to lowering the operating frequency, however,

be sure to check with power MOSFET manufacturers for

their most recent low QG, low RDS(ON) devices. Power

MOSFET manufacturing technologies are continually

improving, with newer and better performance devices

being introduced almost yearly.

An effective approach to reduce the power consumption

of the internal LDO for gate drive is to tie the INTVCC pin

to an external voltage source high enough to turn off the

internal LDO regulator.

If the input voltage VIN does not exceed the absolute maximum rating of both the power MOSFET gate-source voltage (VGS) and the INTVCC overvoltage lockout threshold

voltage (17.5V), the INTVCC pin can be shorted directly

to the VIN pin. In this condition, the internal LDO will be

turned off and the gate driver will be powered directly

from the input voltage VIN . With the INTVCC pin shorted to

VIN, however, a small current (around 16µA) will load the

INTVCC in shutdown mode. For applications that require

the lowest shutdown mode input supply current, do not

connect the INTVCC pin to VIN .

A resistor RVCC can be connected, as shown in Figure 3, to

limit the inrush current from VOUT. Regardless of whether

or not the INTVCC pin is connected to an external voltage

source, it is always necessary to have the driver circuitry

bypassed with a 4.7µF low ESR ceramic capacitor to

ground immediately adjacent to the INTVCC and GND pins.

Operating Frequency and Synchronization

The choice of operating frequency may be determined

by on-chip power dissipation, otherwise it is a trade-off

between efficiency and component size. Low frequency

operation improves efficiency by reducing gate drive current and MOSFET and diode switching losses. However,

lower frequency operation requires a physically larger

inductor. Switching frequency also has implications

for loop compensation. The LT3758 uses a constantfrequency architecture that can be programmed over a

100kHz to 1000kHz range with a single external resistor

from the RT pin to ground, as shown in Figure 1. The

RT pin must have an external resistor to GND for proper

operation of the LT3758. A table for selecting the value

of RT for a given operating frequency is shown in Table 1.

Table 1. Timing Resistor (RT ) Value

SWITCHING FREQUENCY (kHz)

RT (kΩ)

In SEPIC or flyback applications, the INTVCC pin can be

connected to the output voltage VOUT through a blocking

diode, as shown in Figure 3, if VOUT meets the following

conditions:

100

140

200

63.4

300

41.2

400

30.9

1. VOUT < VIN (pin voltage)

500

24.3

600

19.6

700

16.5

800

14

900

12.1

1000

10.5

2. VOUT < 17.5V

3. VOUT < maximum VGS rating of power MOSFET

LT3758

DVCC

INTVCC

RVCC

VOUT

CVCC

4.7µF

GND

3758 F03

Figure 3. Connecting INTVCC to VOUT

12

The operating frequency of the LT3758 can be synchronized

to an external clock source. By providing a digital clock

signal into the SYNC pin, the LT3758 will operate at the

SYNC clock frequency. If this feature is used, an RT resistor

should be chosen to program a switching frequency 20%

slower than SYNC pulse frequency. It is recommended the

SYNC pulse have a minimum pulse width of 200ns. Tie the

SYNC pin to GND if this feature is not used.

Rev G

For more information www.analog.com

�LT3758/LT3758A

APPLICATIONS INFORMATION

Duty Cycle Consideration

Soft-Start

Switching duty cycle is a key variable defining converter operation. As such, its limits must be considered.

Minimum on-time is the smallest time duration that the

LT3758 is capable of turning on the power MOSFET. This

time is generally about 220ns (typical) (see Minimum

On-Time in the Electrical Characteristics table). In each

switching cycle, the LT3758 keeps the power switch off

for at least 220ns (typical) (see Minimum Off-Time in the

Electrical Characteristics table).

The LT3758 contains several features to limit peak switch

currents and output voltage (VOUT) overshoot during

start-up or recovery from a fault condition. The primary

purpose of these features is to prevent damage to external

components or the load.

The minimum on-time and minimum off-time and the

switching frequency define the minimum and maximum

switching duty cycles a converter is able to generate:

Minimum duty cycle = minimum on-time • frequency

Maximum duty cycle = 1 – (minimum off-time • frequency)

Programming the Output Voltage

The output voltage VOUT is set by a resistor divider, as

shown in Figure 1. The positive and negative VOUT are set

by the following equations:

⎛ R2 ⎞

VOUT,POSITIVE = 1.6V • ⎜ 1+ ⎟

⎝ R1⎠

The LT3758 addresses this mechanism with the SS pin.

As shown in Figure 1, the SS pin reduces the power

MOSFET current by pulling down the VC pin through

Q2. In this way the SS allows the output capacitor to

charge gradually toward its final value while limiting the

start-up peak currents. The typical start-up waveforms are

shown in the Typical Performance Characteristics section.

The inductor current IL slewing rate is limited by the softstart function.

Besides start-up (with SHDN/UVLO), soft-start can also

be triggered by the following faults:

⎛ R2 ⎞

VOUT,NEGATIVE = –0.8V • ⎜ 1+ ⎟

⎝ R1⎠

1. INTVCC > 17.5V

The resistors R1 and R2 are typically chosen so that

the error caused by the current flowing into the FBX pin

during normal operation is less than 1% (this translates

to a maximum value of R1 at about 158k).

In the applications where VOUT is pulled up by an external positive power supply, the FBX pin is also pulled up

through the R2 and R1 network. Make sure the FBX does

not exceed its absolute maximum rating (6V). The R5, D2,

and D3 in Figure 1 provide a resistive clamp in the positive

direction. To ensure FBX is lower than 6V, choose sufficiently large R1 and R2 to meet the following condition:

High peak switch currents during start-up may occur

in switching regulators. Since VOUT is far from its final

value, the feedback loop is saturated and the regulator

tries to charge the output capacitor as quickly as possible,

resulting in large peak currents. A large surge current may

cause inductor saturation or power switch failure.

R2

⎛ R2 ⎞

6V • ⎜ 1+ ⎟ + 3.5V •

> VOUT(MAX)

⎝

R1⎠

8kΩ

2. INTVCC < 4.5V

3. Thermal lockout

Any of these three faults will cause the LT3758 to stop

switching immediately. The SS pin will be discharged by

Q3. When all faults are cleared and the SS pin has been

discharged below 0.2V, a 10µA current source IS2 starts

charging the SS pin, initiating a soft-start operation.

The soft-start interval is set by the soft-start capacitor

selection according to the equation:

TSS = C SS •

1.25V

10µA

where VOUT(MAX) is the maximum VOUT that is pulled up

by an external power supply.

Rev G

For more information www.analog.com

13

�LT3758/LT3758A

APPLICATIONS INFORMATION

FBX Frequency Foldback

When VOUT is very low during start-up or a GND fault

on the output, the switching regulator must operate at

low duty cycles to maintain the power switch current

within the current limit range, since the inductor current decay rate is very low during switch off time. The

minimum on-time limitation may prevent the switcher

from attaining a sufficiently low duty cycle at the programmed switching frequency. So, the switch current

will keep increasing through each switch cycle, exceeding the programmed current limit. To prevent the switch

peak currents from exceeding the programmed value, the

LT3758 contains a frequency foldback function to reduce

the switching frequency when the FBX voltage is low (see

the Normalized Switching Frequency vs FBX graph in the

Typical Performance Characteristics section).

During frequency foldback, external clock synchronization is disabled to prevent interference with frequency

reducing operation.

Thermal Lockout

If LT3758 die temperature reaches 165°C (typical), the

part will go into thermal lockout. The power switch will

be turned off. A soft-start operation will be triggered. The

part will be enabled again when the die temperature has

dropped by 5°C (nominal).

Loop Compensation

Loop compensation determines the stability and transient

performance. The LT3758/LT3758A use current mode

control to regulate the output which simplifies loop compensation. The LT3758A improves the no-load to heavy

load transient response, when compared to the LT3758.

New internal circuits ensure that the transient from not

switching to switching at high current can be made in

a few cycles. The optimum values depend on the converter topology, the component values and the operating conditions (including the input voltage, load current,

etc.). To compensate the feedback loop of the LT3758/

LT3758A, a series resistor-capacitor network is usually

connected from the VC pin to GND. Figure 1 shows the

typical VC compensation network. For most applications,

the capacitor should be in the range of 470pF to 22nF,

and the resistor should be in the range of 5k to 50k. A

small capacitor is often connected in parallel with the RC

compensation network to attenuate the VC voltage ripple

induced from the output voltage ripple through the internal error amplifier. The parallel capacitor usually ranges in

value from 10pF to 100pF. A practical approach to design

the compensation network is to start with one of the circuits in this data sheet that is similar to your application, and tune the compensation network to optimize the

performance. Stability should then be checked across all

operating conditions, including load current, input voltage

and temperature.

SENSE Pin Programming

For control and protection, the LT3758 measures the

power MOSFET current by using a sense resistor (RSENSE)

between GND and the MOSFET source. Figure 4 shows a

typical waveform of the sense voltage (VSENSE) across the

sense resistor. It is important to use Kelvin traces between

the SENSE pin and RSENSE, and to place the IC GND as

close as possible to the GND terminal of the RSENSE for

proper operation.

VSENSE

∆VSENSE = χ • VSENSE(MAX)

VSENSE(MAX)

VSENSE(PEAK)

t

DTS

TS

3758 F04

Figure 4. The Sense Voltage During a Switching Cycle

14

Rev G

For more information www.analog.com

�LT3758/LT3758A

APPLICATIONS INFORMATION

Due to the current limit function of the SENSE pin,

RSENSE should be selected to guarantee that the peak

current sense voltage VSENSE(PEAK) during steady state

normal operation is lower than the SENSE current limit

threshold (see the Electrical Characteristics table). Given

a 20% margin, VSENSE(PEAK) is set to be 80mV. Then,

the maximum switch ripple current percentage can be

calculated using the following equation:

χ=

ΔVSENSE

80mV − 0.5 • ΔVSENSE

c is used in subsequent design examples to calculate

inductor value. ∆VSENSE is the ripple voltage across

RSENSE.

The LT3758 switching controller incorporates 100ns

timing interval to blank the ringing on the current sense

signal immediately after M1 is turned on. This ringing is

caused by the parasitic inductance and capacitance of the

PCB trace, the sense resistor, the diode, and the MOSFET.

The 100ns timing interval is adequate for most of the

LT3758 applications. In the applications that have very

large and long ringing on the current sense signal, a small

RC filter can be added to filter out the excess ringing.

Figure 5 shows the RC filter on the SENSE pin. It is usually

sufficient to choose 22Ω for RFLT and 2.2nF to 10nF for

CFLT. Keep RFLT’s resistance low. Remember that there is

65µA (typical) flowing out of the SENSE pin. Adding RFLT

will affect the SENSE current limit threshold:

VSENSE_ILIM = 110mV – 65µA • RFLT

LT3758

CFLT

Boost Converter: Switch Duty Cycle and Frequency

The LT3758 can be configured as a boost converter for

the applications where the converter output voltage is

higher than the input voltage. Remember that boost converters are not short-circuit protected. Under a shorted

output condition, the inductor current is limited only by

the input supply capability. For applications requiring a

step-up converter that is short-circuit protected, please

refer to the Applications Information section covering

SEPIC converters.

The conversion ratio as a function of duty cycle is:

VOUT

1

=

VIN 1−D

in continuous conduction mode (CCM).

For a boost converter operating in CCM, the duty cycle

of the main switch can be calculated based on the output

voltage (VOUT) and the input voltage (VIN). The maximum

duty cycle (DMAX) occurs when the converter has the

minimum input voltage:

DMAX =

VOUT − VIN(MIN)

VOUT

Boost Converter: Inductor and Sense Resistor Selection

RFLT

SENSE

GND

The LT3758 can be configured as different topologies. The

first topology to be analyzed will be the boost converter,

followed by the flyback, SEPIC and inverting converters.

Discontinuous conduction mode (DCM) provides higher

conversion ratios at a given frequency at the cost of

reduced efficiencies and higher switching currents.

M1

GATE

APPLICATION CIRCUITS

For the boost topology, the maximum average inductor

current is:

RSENSE

3758 F05

Figure 5. The RC Filter on the SENSE Pin

IL(MAX) = IO(MAX) •

1

1−DMAX

Then, the ripple current can be calculated by:

ΔIL = χ •IL(MAX) = χ •IO(MAX) •

For more information www.analog.com

1

1−DMAX

Rev G

15

�LT3758/LT3758A

APPLICATIONS INFORMATION

The constant c in the preceding equation represents the

percentage peak-to-peak ripple current in the inductor,

relative to IL(MAX).

The inductor ripple current has a direct effect on the

choice of the inductor value. Choosing smaller values of

∆IL requires large inductances and reduces the current

loop gain (the converter will approach voltage mode).

Accepting larger values of ∆IL provides fast transient

response and allows the use of low inductances, but

results in higher input current ripple, greater core

losses, and in some cases, subharmonic oscillation. A

good starting point for c is 0.2 and careful evaluation

of system stability should be made to ensure adequate

design margin.

Given an operating input voltage range, and having chosen the operating frequency and ripple current in the

inductor, the inductor value of the boost converter can

be determined using the following equation:

L=

VIN(MIN)

ΔIL • f

•DMAX

The peak and RMS inductor current are:

Based on these equations, the user should choose the

inductors having sufficient saturation and RMS current

ratings.

Set the sense voltage at IL(PEAK) to be the minimum of the

SENSE current limit threshold with a 20% margin. The

sense resistor value can then be calculated to be:

80mV

IL(PEAK)

PFET = I2L(MAX) • RDS(ON) • DMAX + 2 • V2OUT • IL(MAX)

• CRSS • f/1A

The first term in the preceding equation represents the

conduction losses in the device, and the second term, the

switching loss. CRSS is the reverse transfer capacitance,

which is usually specified in the MOSFET characteristics.

For maximum efficiency, RDS(ON) and CRSS should be

minimized. From a known power dissipated in the power

MOSFET, its junction temperature can be obtained using

the following equation:

Boost Converter: Output Diode Selection

To maximize efficiency, a fast switching diode with low

forward drop and low reverse leakage is desirable. The

peak reverse voltage that the diode must withstand is

equal to the regulator output voltage plus any additional

ringing across its anode-to-cathode during the on-time.

The average forward current in normal operation is equal

to the output current, and the peak current is equal to:

⎛ χ⎞

ID(PEAK) =IL(PEAK) = ⎜⎝ 1+ 2 ⎟⎠ •IL(MAX)

Boost Converter: Power MOSFET Selection

Important parameters for the power MOSFET include the

drain-source voltage rating (VDS), the threshold voltage

16

The power dissipated by the MOSFET in a boost converter is:

TJ must not exceed the MOSFET maximum junction

temperature rating. It is recommended to measure the

MOSFET temperature in steady state to ensure that absolute maximum ratings are not exceeded.

χ2

IL(RMS) = IL(MAX) • 1+

12

The power MOSFET will see full output voltage, plus a

diode forward voltage, and any additional ringing across

its drain-to-source during its off-time. It is recommended

to choose a MOSFET whose BVDSS is higher than VOUT by

a safety margin (a 10V safety margin is usually sufficient).

TJ = TA + PFET • θJA = TA + PFET • (θJC + θCA)

⎛ χ⎞

IL(PEAK) = IL(MAX) • ⎜ 1+ ⎟

⎝ 2⎠

R SENSE =

(VGS(TH)), the on-resistance (RDS(ON)), the gate to source

and gate to drain charges (QGS and QGD), the maximum

drain current (ID(MAX)) and the MOSFET’s thermal

resistances (RθJC and RθJA).

It is recommended that the peak repetitive reverse voltage

rating VRRM is higher than VOUT by a safety margin (a 10V

safety margin is usually sufficient).

Rev G

For more information www.analog.com

�LT3758/LT3758A

APPLICATIONS INFORMATION

The power dissipated by the diode is:

For the bulk C component, which also contributes 1% to

the total ripple:

PD = IO(MAX) • VD

and the diode junction temperature is:

TJ = TA + PD • RθJA

The RθJA to be used in this equation normally includes the

RθJC for the device plus the thermal resistance from the

board to the ambient temperature in the enclosure. TJ must

not exceed the diode maximum junction temperature rating.

Boost Converter: Output Capacitor Selection

Contributions of ESR (equivalent series resistance), ESL

(equivalent series inductance) and the bulk capacitance

tON

tOFF

∆VCOUT

VOUT

(AC)

∆VESR

RINGING DUE TO

TOTAL INDUCTANCE

(BOARD + CAP)

COUT ≥

IO(MAX)

0.01• VOUT • f

The output capacitor in a boost regulator experiences

high RMS ripple currents, as shown in Figure 6. The RMS

ripple current rating of the output capacitor can be determined using the following equation:

IRMS(COUT) ≥ IO(MAX) •

DMAX

1−DMAX

Multiple capacitors are often paralleled to meet ESR

requirements. Typically, once the ESR requirement is satisfied, the capacitance is adequate for filtering and has the

required RMS current rating. Additional ceramic capacitors in parallel are commonly used to reduce the effect of

parasitic inductance in the output capacitor, which reduces

high frequency switching noise on the converter output.

3758 F06

Figure 6. The Output Ripple Waveform of a Boost Converter

must be considered when choosing the correct output

capacitors for a given output ripple voltage. The effect of

these three parameters (ESR, ESL and bulk C) on the output voltage ripple waveform for a typical boost converter

is illustrated in Figure 6.

The choice of component(s) begins with the maximum

acceptable ripple voltage (expressed as a percentage of

the output voltage), and how this ripple should be divided

between the ESR step ∆VESR and the charging/discharging ∆VCOUT. For the purpose of simplicity, we will choose

2% for the maximum output ripple, to be divided equally

between ∆VESR and ∆VCOUT. This percentage ripple will

change, depending on the requirements of the application, and the following equations can easily be modified.

For a 1% contribution to the total ripple voltage, the ESR

of the output capacitor can be determined using the following equation:

ESRCOUT ≤

0.01• VOUT

ID(PEAK)

Boost Converter: Input Capacitor Selection

The input capacitor of a boost converter is less critical

than the output capacitor, due to the fact that the inductor

is in series with the input, and the input current waveform is continuous. The input voltage source impedance

determines the size of the input capacitor, which is typically in the range of 10µF to 100µF. A low ESR capacitor

is recommended, although it is not as critical as for the

output capacitor.

The RMS input capacitor ripple current for a boost converter is:

IRMS(CIN) = 0.3 • ∆IL

FLYBACK CONVERTER APPLICATIONS

The LT3758 can be configured as a flyback converter for

the applications where the converters have multiple outputs, high output voltages or isolated outputs. Figure 7

shows a simplified flyback converter.

The flyback converter has a very low parts count for multiple outputs, and with prudent selection of turns ratio,

can have high output/input voltage conversion ratios with

Rev G

For more information www.analog.com

17

�LT3758/LT3758A

APPLICATIONS INFORMATION

a desirable duty cycle. However, it has low efficiency due

to the high peak currents, high peak voltages and consequent power loss. The flyback converter is commonly

used for an output power of less than 50W.

VDS

The flyback converter can be designed to operate either

in continuous or discontinuous mode. Compared to continuous mode, discontinuous mode has the advantage of

smaller transformer inductances and easy loop compensation, and the disadvantage of higher peak-to-average

current and lower efficiency.

SUGGESTED

RCD SNUBBER

VIN

+

CIN

–

VSN

+

CSN

LS

LP

ISW(MAX)

ID

ID(MAX)

DTS

D

NP:NS

RSN

ISW

+

ID

+

D3TS

t

3758 F08

Figure 8. Waveforms of the Flyback Converter

in Discontinuous Mode Operation

COUT

–

DSN

D2TS

TS

Flyback Converter: Switch Duty Cycle and Turns Ratio

According to the preceding equations, the user has relative freedom in selecting the switch duty cycle or turns

ratio to suit a given application. The selections of the

duty cycle and the turns ratio are somewhat iterative processes, due to the number of variables involved. The user

can choose either a duty cycle or a turns ratio as the start

point. The following trade-offs should be considered when

selecting the switch duty cycle or turns ratio, to optimize

the converter performance. A higher duty cycle affects the

flyback converter in the following aspects:

The flyback converter conversion ratio in the continuous

mode operation is:

• Lower MOSFET RMS current ISW(RMS), but higher

MOSFET VDS peak voltage

LT3758

GATE

SENSE

ISW

M

+

VDS

–

RSENSE

GND

3758 F07

Figure 7. A Simplified Flyback Converter

• Lower diode peak reverse voltage, but higher diode

RMS current ID(RMS)

VOUT NS D

=

•

VIN NP 1−D

Where NS/NP is the second to primary turns ratio.

Figure 8 shows the waveforms of the flyback converter

in discontinuous mode operation. During each switching

period TS, three subintervals occur: DTS, D2TS, D3TS.

During DTS, M is on, and D is reverse-biased. During

D2TS, M is off, and LS is conducting current. Both LP and

LS currents are zero during D3TS.

The flyback converter conversion ratio in the discontinuous mode operation is:

VOUT

N

D

= S•

VIN NP D2

18

• Higher transformer turns ratio (NP/NS)

The choice,

D

=

1

D+D2 3

(for discontinuous mode operation with a given D3) gives

the power MOSFET the lowest power stress (the product

of RMS current and peak voltage). The choice,

D

=

2

D+D2 3

(for discontinuous mode operation with a given D3)

gives the diode the lowest power stress (the product of

Rev G

For more information www.analog.com

�LT3758/LT3758A

APPLICATIONS INFORMATION

RMS current and peak voltage). An extreme high or low

duty cycle results in high power stress on the MOSFET

or diode, and reduces efficiency. It is recommended to

choose a duty cycle between 20% and 80%.

Flyback Converter: Transformer Design for

Discontinuous Mode Operation

The transformer design for discontinuous mode of operation is chosen as presented here. According to Figure 8,

the minimum D3 (D3MIN) occurs when the the converter

has the minimum VIN and the maximum output power

(POUT). Choose D3MIN to be equal to or higher than 10%

to guarantee the converter is always in discontinuous

mode operation. Choosing higher D3 allows the use of

low inductances but results in higher switch peak current.

The user can choose a DMAX as the start point. Then, the

maximum average primary currents can be calculated by

the following equation:

ILP(MAX) =ISW(MAX) =

POUT(MAX)

If the flyback converter has multiple outputs, POUT(MAX)

is the sum of all the output power.

The maximum average secondary current is:

I OUT(MAX)

where

D2

D2 = 1 – DMAX – D3

the primary and secondary RMS currents are:

ILP(RMS) = 2 •ILP(MAX) •

ILS(RMS) = 2 •ILS(MAX) •

ILP(PEAK) = ISW(PEAK) = 2 • ILP(MAX)

ILS(PEAK) = ID(PEAK) = 2 • ILS(MAX)

The primary and second inductor values of the flyback

converter transformer can be determined using the following equations:

D 2 MAX • V 2 IN(MIN) • �

LP =

2 • POUT(MAX) • f

D2

3

D2 2 • (VOUT + VD)

2 •I OUT(MAX) • f

The primary to second turns ratio is:

NP

NS

=

LP

LS

Transformer leakage inductance (on either the primary

or secondary) causes a voltage spike to occur after the

MOSFET turn-off. This is increasingly prominent at higher

load currents, where more stored energy must be dissipated. In some cases a snubber circuit will be required

to avoid overvoltage breakdown at the MOSFET’s drain

node. There are different snubber circuits, and Application

Note 19 is a good reference on snubber design. An RCD

snubber is shown in Figure 7.

The snubber resistor value (RSN) can be calculated by the

following equation:

DMAX

3

LS =

Flyback Converter: Snubber Design

DMAX • VIN(MIN) • η

where h is the converter efficiency.

ILS(MAX) = ID(MAX) =

According to Figure 8, the primary and secondary peak

currents are:

RSN = 2 •

V 2 SN − VSN • VOUT •

NP

NS

I2 SW(PEAK) •L LK • f

where VSN is the snubber capacitor voltage. A smaller

VSN results in a larger snubber loss. A reasonable VSN is

2 to 2.5 times of:

VOUT • NP

NS

Rev G

For more information www.analog.com

19

�LT3758/LT3758A

APPLICATIONS INFORMATION

LLK is the leakage inductance of the primary winding,

which is usually specified in the transformer characteristics. LLK can be obtained by measuring the primary

inductance with the secondary windings shorted. The

snubber capacitor value (CCN) can be determined using

the following equation:

CCN =

VSN

ΔVSN •RCN • f

where ∆VSN is the voltage ripple across CCN. A reasonable

∆VSN is 5% to 10% of VSN. The reverse voltage rating of

DSN should be higher than the sum of VSN and VIN(MAX).

Flyback Converter: Sense Resistor Selection

In a flyback converter, when the power switch is turned on,

the current flowing through the sense resistor (ISENSE) is:

ISENSE = ILP

Set the sense voltage at ILP(PEAK) to be the minimum of

the SENSE current limit threshold with a 20% margin. The

sense resistor value can then be calculated to be:

R SENSE =

80mV

From a known power dissipated in the power MOSFET, its

junction temperature can be obtained using the following

equation:

TJ = TA + PFET • θJA = TA + PFET • (θJC + θCA)

TJ must not exceed the MOSFET maximum junction

temperature rating. It is recommended to measure the

MOSFET temperature in steady state to ensure that absolute maximum ratings are not exceeded.

Flyback Converter: Output Diode Selection

The output diode in a flyback converter is subject to large

RMS current and peak reverse voltage stresses. A fast

switching diode with a low forward drop and a low reverse

leakage is desired. Schottky diodes are recommended if

the output voltage is below 100V.

Approximate the required peak repetitive reverse voltage

rating VRRM using:

N

VRRM > S • VIN(MAX) + VOUT

NP

The power dissipated by the diode is:

ILP(PEAK)

PD = IO(MAX) • VD

Flyback Converter: Power MOSFET Selection

and the diode junction temperature is:

For the flyback configuration, the MOSFET is selected

with a VDC rating high enough to handle the maximum

VIN, the reflected secondary voltage and the voltage spike

due to the leakage inductance. Approximate the required

MOSFET VDC rating using:

TJ = TA + PD • RθJA

BVDSS > VDS(PEAK)

Flyback Converter: Output Capacitor Selection

where

VDS(PEAK) = VIN(MAX) + VSN

The power dissipated by the MOSFET in a flyback converter is:

PFET = I2M(RMS) • RDS(ON) + 2 • V2DS(PEAK) • IL(MAX) •

CRSS • f/1A

The first term in this equation represents the conduction

losses in the device, and the second term, the switching

loss. CRSS is the reverse transfer capacitance, which is

usually specified in the MOSFET characteristics.

20

The RθJA to be used in this equation normally includes the

RθJC for the device, plus the thermal resistance from the

board to the ambient temperature in the enclosure. TJ must

not exceed the diode maximum junction temperature rating.

The output capacitor of the flyback converter has a similar

operation condition as that of the boost converter. Refer to

the Boost Converter: Output Capacitor Selection section

for the calculation of COUT and ESRCOUT.

The RMS ripple current rating of the output capacitors

in discontinuous operation can be determined using the

following equation:

IRMS(COUT),DISCONTINUOUS ≥ IO(MAX) •

4−(3 •D2)

3 •D2

Rev G

For more information www.analog.com

�LT3758/LT3758A

APPLICATIONS INFORMATION

Flyback Converter: Input Capacitor Selection

The input capacitor in a flyback converter is subject to

a large RMS current due to the discontinuous primary

current. To prevent large voltage transients, use a low

ESR input capacitor sized for the maximum RMS current.

The RMS ripple current rating of the input capacitors in

discontinuous operation can be determined using the following equation:

IRMS(CIN),DISCONTINUOUS ≥

POUT(MAX)

VIN(MIN) • η

•

4−(3 •DMAX )

3 •DMAX

SEPIC CONVERTER APPLICATIONS

The LT3758 can be configured as a SEPIC (single-ended

primary inductance converter), as shown in Figure 1. This

topology allows for the input to be higher, equal, or lower

than the desired output voltage. The conversion ratio as

a function of duty cycle is:

VOUT + VD

D

=

VIN

1−D

in continuous conduction mode (CCM).

In a SEPIC converter, no DC path exists between the input

and output. This is an advantage over the boost converter

for applications requiring the output to be disconnected

from the input source when the circuit is in shutdown.

Compared to the flyback converter, the SEPIC converter

has the advantage that both the power MOSFET and the

output diode voltages are clamped by the capacitors (CIN,

CDC and COUT), therefore, there is less voltage ringing

across the power MOSFET and the output diodes. The

SEPIC converter requires much smaller input capacitors

than those of the flyback converter. This is due to the fact

that, in the SEPIC converter, the inductor L1 is in series

with the input, and the ripple current flowing through the

input capacitor is continuous.

The maximum duty cycle (DMAX) occurs when the converter has the minimum input voltage:

DMAX =

VOUT + VD

VIN(MIN) + VOUT + VD

SEPIC Converter: Inductor and Sense Resistor Selection

As shown in Figure 1, the SEPIC converter contains two

inductors: L1 and L2. L1 and L2 can be independent, but can

also be wound on the same core, since identical voltages

are applied to L1 and L2 throughout the switching cycle.

For the SEPIC topology, the current through L1 is the

converter input current. Based on the fact that, ideally, the

output power is equal to the input power, the maximum

average inductor currents of L1 and L2 are:

IL1(MAX) =IIN(MAX) =IO(MAX) •

DMAX

1−DMAX

IL2(MAX) =IO(MAX)

In a SEPIC converter, the switch current is equal to IL1 +

IL2 when the power switch is on, therefore, the maximum

average switch current is defined as:

ISW(MAX) =IL1(MAX) +IL2(MAX) =IO(MAX) •

1

1−DMAX

and the peak switch current is:

1

⎛ χ⎞

ISW(PEAK) = ⎜ 1+ ⎟ •IO(MAX) •

⎝ 2⎠

1−DMAX

The constant c in the preceding equations represents the

percentage peak-to-peak ripple current in the switch, relative to ISW(MAX), as shown in Figure 9. Then, the switch

ripple current ∆ISW can be calculated by:

∆ISW = c • ISW(MAX)

The inductor ripple currents ∆IL1 and ∆IL2 are identical:

SEPIC Converter: Switch Duty Cycle and Frequency

∆IL1 = ∆IL2 = 0.5 • ∆ISW

For a SEPIC converter operating in CCM, the duty cycle

of the main switch can be calculated based on the output

voltage (VOUT), the input voltage (VIN) and the diode forward voltage (VD).

The inductor ripple current has a direct effect on the

choice of the inductor value. Choosing smaller values of

∆IL requires large inductances and reduces the current

loop gain (the converter will approach voltage mode).

Rev G

For more information www.analog.com

21

�LT3758/LT3758A

APPLICATIONS INFORMATION

Accepting larger values of ∆IL allows the use of low inductances, but results in higher input current ripple, greater

core losses, and in some cases, subharmonic oscillation.

A good starting point for c is 0.2 and careful evaluation

of system stability should be made to ensure adequate

design margin.

IL1(MAX)

χ 2 L2

I

=I

• 1+

L2(RMS) L2(MAX)

12

t

DTS

TS

3758 F09

Figure 9. The Switch Current Waveform of the SEPIC Converter

Given an operating input voltage range, and having chosen the operating frequency and ripple current in the

inductor, the inductor value (L1 and L2 are independent)

of the SEPIC converter can be determined using the following equation:

L1= L2 =

VIN(MIN)

0.5 • ΔISW • f

•DMAX

By making L1 = L2, and winding them on the same core,

the value of inductance in the preceding equation is

replaced by 2L, due to mutual inductance:

VIN(MIN)

ΔISW • f

This maintains the same ripple current and energy storage

in the inductors. The peak inductor currents are:

IL2(PEAK) = IL2(MAX) + 0.5 • ∆IL2

The RMS inductor currents are:

χ 2 L1

IL1(RMS) =IL1(MAX) • 1+

12

22

ΔIL2

IL2 (MAX)

In a SEPIC converter, when the power switch is turned on,

the current flowing through the sense resistor (ISENSE) is

the switch current.

Set the sense voltage at ISENSE(PEAK) to be the minimum

of the SENSE current limit threshold with a 20% margin.

The sense resistor value can then be calculated to be:

R SENSE =

80 mV

ISW(PEAK)

SEPIC Converter: Power MOSFET Selection

For the SEPIC configuration, choose a MOSFET with a

VDC rating higher than the sum of the output voltage and

input voltage by a safety margin (a 10V safety margin is

usually sufficient).

The power dissipated by the MOSFET in a SEPIC converter is:

•DMAX

IL1(PEAK) = IL1(MAX) + 0.5 • ∆IL1

χL2 =

Based on the preceding equations, the user should choose

the inductors having sufficient saturation and RMS current ratings.

For most SEPIC applications, the equal inductor values

will fall in the range of 1µH to 100µH.

ΔIL1

∆ISW = χ • ISW(MAX)

ISW(MAX)

L=

χL1 =

where

ISW

where

PFET = I2SW(MAX) • RDS(ON) • DMAX

+ 2 • (VIN(MIN) + VOUT)2 • IL(MAX) • CRSS • f/1A

The first term in this equation represents the conduction

losses in the device, and the second term, the switching

loss. CRSS is the reverse transfer capacitance, which is

usually specified in the MOSFET characteristics.

For maximum efficiency, RDS(ON) and CRSS should be

minimized. From a known power dissipated in the power

Rev G

For more information www.analog.com

�LT3758/LT3758A

APPLICATIONS INFORMATION

MOSFET, its junction temperature can be obtained using

the following equation:

TJ = TA + PFET • θJA = TA + PFET • (θJC + θCA)

TJ must not exceed the MOSFET maximum junction

temperature rating. It is recommended to measure the

MOSFET temperature in steady state to ensure that absolute maximum ratings are not exceeded.

SEPIC Converter: Output Diode Selection

To maximize efficiency, a fast switching diode with a low

forward drop and low reverse leakage is desirable. The

average forward current in normal operation is equal to

the output current, and the peak current is equal to:

1

⎛ χ⎞

ID(PEAK) = ⎜ 1+ ⎟ •IO(MAX) •

⎝ 2⎠

1−DMAX

It is recommended that the peak repetitive reverse voltage

rating VRRM is higher than VOUT + VIN(MAX) by a safety

margin (a 10V safety margin is usually sufficient).

CDC has nearly a rectangular current waveform. During

the switch off-time, the current through CDC is IIN, while

approximately –IO flows during the on-time. The RMS

rating of the coupling capacitor is determined by the following equation:

IRMS(CDC) > IO(MAX) •

VOUT + VD

VIN(MIN)

A low ESR and ESL, X5R or X7R ceramic capacitor works

well for CDC.

INVERTING CONVERTER APPLICATIONS

The LT3758 can be configured as a dual-inductor inverting

topology, as shown in Figure 10. The VOUT to VIN ratio is:

VOUT − VD

D

=−

VIN

1−D

in continuous conduction mode (CCM).

The power dissipated by the diode is:

L1

VIN

PD = IO(MAX) • VD

+

and the diode junction temperature is:

CDC

+

L2

–

–

CIN

COUT

LT3758

TJ = TA + PD • RθJA

GATE

The RθJA used in this equation normally includes the RθJC

for the device, plus the thermal resistance from the board,

to the ambient temperature in the enclosure. TJ must not

exceed the diode maximum junction temperature rating.

SEPIC Converter: Selecting the DC Coupling Capacitor

The DC voltage rating of the DC coupling capacitor (CDC,

as shown in Figure 1) should be larger than the maximum

input voltage:

D1

SENSE

RSENSE

GND

+

3758 F10

Figure 10. A Simplified Inverting Converter

SEPIC Converter: Output and Input Capacitor Selection

The selections of the output and input capacitors of

the SEPIC converter are similar to those of the boost

converter. Please refer to the Boost Converter: Output

Capacitor Selection and Boost Converter: Input Capacitor

Selection sections.

M1

VOUT

+

Inverting Converter: Switch Duty Cycle and Frequency

For an inverting converter operating in CCM, the duty

cycle of the main switch can be calculated based on the

negative output voltage (VOUT) and the input voltage (VIN).

The maximum duty cycle (DMAX) occurs when the converter has the minimum input voltage:

DMAX =

VOUT − VD

VOUT − VD − VIN(MIN)

VCDC > VIN(MAX)

Rev G

For more information www.analog.com

23

�LT3758/LT3758A

APPLICATIONS INFORMATION

Inverting Converter: Inductor, Sense Resistor, Power

MOSFET, Output Diode and Input Capacitor Selections

The selections of the inductor, sense resistor, power

MOSFET, output diode and input capacitor of an inverting converter are similar to those of the SEPIC converter.

Please refer to the corresponding SEPIC converter

sections.

Inverting Converter: Output Capacitor Selection

The inverting converter requires much smaller output

capacitors than those of the boost, flyback and SEPIC

converters for similar output ripples. This is due to the

fact that, in the inverting converter, the inductor L2 is

in series with the output, and the ripple current flowing

through the output capacitors are continuous. The output

ripple voltage is produced by the ripple current of L2 flowing through the ESR and bulk capacitance of the output

capacitor:

⎛

⎞

1

ΔVOUT(P–P) = ΔIL2 • ⎜ ESRCOUT +

8 • f •COUT ⎟⎠

⎝

After specifying the maximum output ripple, the user can

select the output capacitors according to the preceding

equation.

The ESR can be minimized by using high quality X5R or

X7R dielectric ceramic capacitors. In many applications,

ceramic capacitors are sufficient to limit the output voltage ripple.

The RMS ripple current rating of the output capacitor

needs to be greater than:

IRMS(COUT) > 0.3 • ∆IL2

Inverting Converter: Selecting the DC Coupling Capacitor

The DC voltage rating of the DC coupling capacitor (CDC,

as shown in Figure 10) should be larger than the maximum input voltage minus the output voltage (negative

voltage):

VCDC > VIN(MAX) – VOUT

24

CDC has nearly a rectangular current waveform. During

the switch off-time, the current through CDC is IIN, while

approximately –IO flows during the on-time. The RMS

rating of the coupling capacitor is determined by the following equation:

IRMS(CDC) >IO(MAX) •

DMAX

1−DMAX

A low ESR and ESL, X5R or X7R ceramic capacitor works

well for CDC.

Board Layout

The high speed operation of the LT3758 demands careful

attention to board layout and component placement. The

Exposed Pad of the package is the only GND terminal of

the IC, and is important for thermal management of the

IC. Therefore, it is crucial to achieve a good electrical and

thermal contact between the Exposed Pad and the ground

plane of the board. For the LT3758 to deliver its full output