LT3999

Low Noise, 1A, 1MHz

Push-Pull DC/DC Driver

with Duty Cycle Control

FEATURES

DESCRIPTION

Wide Input Operating Range: 2.7V to 36V

n Dual 1A Switches with Programmable Current Limit

n Programmable Switching Frequency: 50kHz to 1MHz

n Frequency Synchronization Up to 1MHz

n ∆V Compensation Using Duty Cycle Control

IN

n Low Noise Topology

n Programmable Input Over and Undervoltage Lockout

n Cross Conduction Prevention Circuitry

n Programmable Soft-Start

n Low Shutdown Current: 4.7µF), low ESR ceramic will be adequate to filter

high frequency noise at the input. The output capacitors

supply energy to the output load only during switch

transitions. Therefore, large capacitance values are not

necessary on the output.

Transformer winding capacitance between the isolated

primary and secondary has parasitic currents that can

cause noise on the grounds. Providing a high frequency,

low impedance path between the primary and secondary

gives the parasitic currents a local return path. A 2.2nF,

1kV ceramic capacitor is recommended.

Optional LC Filter

An optional LC filter, as shown on the Typical Application

on the first page of this data sheet, should be included if

ultralow noise and ripple are required. It is recommended

that the corner frequency of the filter should be set a

decade below the switching frequency so that the switch

noise is attenuated by a factor of 100. For example, if the

fOSC = 100kHz, then fCORNER = 10kHz where:

fCORNER =

1

2 • π LC

Switching Diode Selection

A fast recovery, surface mount diode such as a Schottky

is recommended. The proximity of the diodes to the

transformer outputs is important and should be as close

as possible with short, wide traces connecting them.

where POUT is the output power of the converter and eff

is the converter efficiency, typically around 85%.

10

3999fa

For more information www.linear.com/LT3999

�LT3999

APPLICATIONS INFORMATION

Output Voltage Regulation

The junction temperature is computed as:

The output voltage of the DC transformer topology is

unregulated. Variations in the input voltage will cause

the output voltage to vary because the output voltage is

a function of the input voltage and the transformer turn

ratio. Also, variations in the output load will cause the

output voltage to change because of circuit parasitics,

such as the transformer DC resistance and power switch

on resistance. If regulation is necessary, a post regulator

such as a linear regulator can be added to the output of

the supply. See the Typical Applications for examples of

adding a linear regulator.

TJ = TAMB + PD • θJA

Power Consideration

The current derived from the VIN pin and the SWA and

SWB switching currents are the sources of the LT3999

power dissipation. The power dissipation is the sum of:

where:

PD = PVIN + PVCESAT + PSW and θJA is the package

thermal resistance.

Layout Consideration Check List

The following is a list of recommended layout considerations:

• Locate the bypass capacitor on the VIN pin of the transformer close to the transformer.

• Create a solid GND plane, preferably on layer two of

the PCB.

• Use short wide traces to connect to the transformer.

1) The quiescent current and switch drive power

dissipation:

• The transformer and PCB routing should be carefully designed to maximize the symmetry between two

switching half cycles.

I •DC

PVIN = VIN SW

+ 4mA

30

• Solder the LT3999 exposed pad to the PCB. Add multiple

vias to connect the exposed pad to the GND plane.

where ISW is the average switch current.

More Help

2) The conducting power dissipation of the switches during

on state:

AN70: “A Monolithic Switching Regulator with 100mV

Output Noise” contains much information concerning

applications and noise measurement techniques.

PVCESAT = VCESAT • ISW • 2DC

where DC is the duty cycle and VCESAT is the collector

to emitter voltage drop during the switch saturation.

3) The dynamic power dissipation due to the switching

transitions:

PSW = VIN • ISW • fOSC • (tr + tf)

where tr and tf are the rise and fall times.

3999fa

For more information www.linear.com/LT3999

11

�LT3999

TYPICAL APPLICATIONS

30V to 12V, 10W Push-Pull DC Transformer

VIN

30V

CIN

10µF

50V

VIN

R1

499k

SYNC

SWA

UVLO

R2

19.1k

LT3999

•

•

•

SWB

ILIM/SS

RBIAS

RBIAS

49.9k

VOUT

12V

COUT 0.8A

10µF

16V

D2

RT

C1

0.1µF

•

OVLO/DC

RDC

RT

28k

500kHz

L1

OPTIONAL

D1

T1

3999 TA02

D1, D2: DIODES INC. B260

L1: COILCRAFT M56132-153

T1: COOPER BUSSMANN CTX02-19062

GND

5V to 5V, 4W Low Part Count Push-Pull DC Transformer

VIN

5V

CIN

47µF

10V

VIN

UVLO

D1

T1

SWA

SYNC

•

•

•

•

VOUT

5V

COUT 0.8A

10µF

10V

OVLO/DC

LT3999

RDC

D2

RT

ILIM/SS

RT

12.1k

1MHz

RBIAS

49.9k

RBIAS

SWB

3999 TA03

D1, D2: CENTRAL SEMI. CMSH1-20M

T1: COILCRAFT PA6383

GND

10V-15V to ±12V, 200mA Isolated Switching Regulator

VIN

10V TO 15V

CIN

10µF

100V

R1

715k

VIN

SYNC

R2

36.5k

SWA

UVLO

ILIM/SS

12

CSS

0.01µF

RBIAS

49.9k

RBIAS

•

•

D2

•

•

D3

SWB

RT

RDC

13.3k

R4

39k

LT3999

RDC

RT

12.1k

1MHz

C3

180pF

OVLO/DC

R3

66.5k

D1

T1

GND

D4

D1-D4: CENTRAL SEMI. CMSH1-200HE

L1, L2: COILCRAFT XFL3012-393MEG

T1: WÜRTH 750314781

L1

39µH

C1

10µF

R7 50V

10k

0.01µF

L2

39µH

C2

10µF

50V

SHDN OUT

IN

LT3065

ADJ

REF/BYP

SHDN OUT

IN

ILIM

LT3090

SET

GND

1M

COUT1

10µF

25V

VOUT

12V

200mA

R8

52.3k

COUT2

10µF

25V

–VOUT

–12V

R6 200mA

10k

R10

243k

3999 TA04

3999fa

For more information www.linear.com/LT3999

�LT3999

PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

MSE Package

10-Lead Plastic MSOP, Exposed Die Pad

(Reference LTC DWG # 05-08-1664 Rev I)

BOTTOM VIEW OF

EXPOSED PAD OPTION

1.88 ±0.102

(.074 ±.004)

5.10

(.201)

MIN

1

0.889 ±0.127

(.035 ±.005)

1.68 ±0.102

(.066 ±.004)

0.05 REF

10

0.305 ± 0.038

(.0120 ±.0015)

TYP

RECOMMENDED SOLDER PAD LAYOUT

3.00 ±0.102

(.118 ±.004)

(NOTE 3)

DETAIL “B”

CORNER TAIL IS PART OF

DETAIL “B” THE LEADFRAME FEATURE.

FOR REFERENCE ONLY

NO MEASUREMENT PURPOSE

10 9 8 7 6

DETAIL “A”

0° – 6° TYP

1 2 3 4 5

GAUGE PLANE

0.53 ±0.152

(.021 ±.006)

DETAIL “A”

0.18

(.007)

0.497 ±0.076

(.0196 ±.003)

REF

3.00 ±0.102

(.118 ±.004)

(NOTE 4)

4.90 ±0.152

(.193 ±.006)

0.254

(.010)

0.29

REF

1.68

(.066)

3.20 – 3.45

(.126 – .136)

0.50

(.0197)

BSC

1.88

(.074)

SEATING

PLANE

0.86

(.034)

REF

1.10

(.043)

MAX

0.17 – 0.27

(.007 – .011)

TYP

0.50

(.0197)

BSC

NOTE:

1. DIMENSIONS IN MILLIMETER/(INCH)

2. DRAWING NOT TO SCALE

3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

6. EXPOSED PAD DIMENSION DOES INCLUDE MOLD FLASH. MOLD FLASH ON E-PAD

SHALL NOT EXCEED 0.254mm (.010") PER SIDE.

0.1016 ±0.0508

(.004 ±.002)

MSOP (MSE) 0213 REV I

3999fa

For more information www.linear.com/LT3999

13

�LT3999

PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

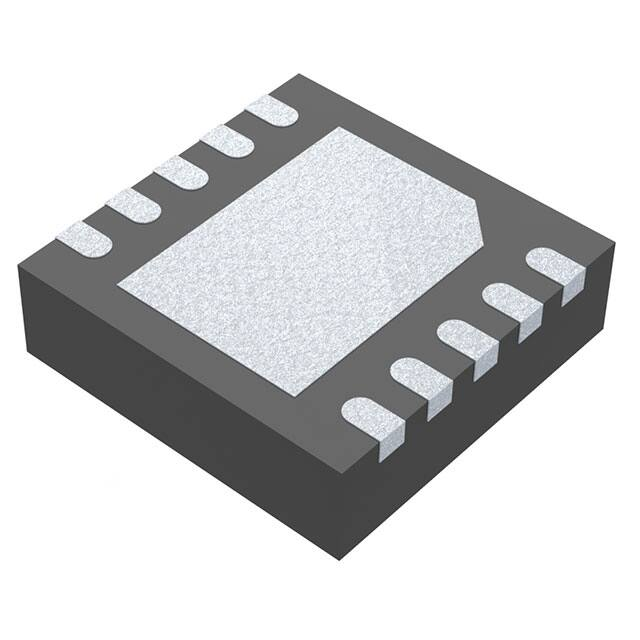

DD Package

10-Lead Plastic DFN (3mm × 3mm)

(Reference LTC DWG # 05-08-1699 Rev C)

0.70 ±0.05

3.55 ±0.05

1.65 ±0.05

2.15 ±0.05 (2 SIDES)

PACKAGE

OUTLINE

0.25 ± 0.05

0.50

BSC

2.38 ±0.05

(2 SIDES)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

3.00 ±0.10

(4 SIDES)

R = 0.125

TYP

6

0.40 ± 0.10

10

1.65 ± 0.10

(2 SIDES)

PIN 1 NOTCH

R = 0.20 OR

0.35 × 45°

CHAMFER

PIN 1

TOP MARK

(SEE NOTE 6)

0.200 REF

0.75 ±0.05

0.00 – 0.05

5

1

(DD) DFN REV C 0310

0.25 ± 0.05

0.50 BSC

2.38 ±0.10

(2 SIDES)

BOTTOM VIEW—EXPOSED PAD

NOTE:

1. DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE M0-229 VARIATION OF (WEED-2).

CHECK THE LTC WEBSITE DATA SHEET FOR CURRENT STATUS OF VARIATION ASSIGNMENT

2. DRAWING NOT TO SCALE

3. ALL DIMENSIONS ARE IN MILLIMETERS

4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE

TOP AND BOTTOM OF PACKAGE

14

3999fa

For more information www.linear.com/LT3999

�LT3999

REVISION HISTORY

REV

DATE

DESCRIPTION

A

04/15

Corrected pin assignments

PAGE NUMBER

Revised schematics

5

13, 16

3999fa

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection

of its circuits

as described

herein will not infringe on existing patent rights.

For more

information

www.linear.com/LT3999

15

�LT3999

TYPICAL APPLICATION

5V to 12V, 1W Low Power Push-Pull DC Transformer

VIN

5V

CIN

10µF

10V

VIN

R1

261k

SYNC

SWA

UVLO

R2

100k

LT3999

ILIM/SS

RILIM

40.3k

•

•

COUT

2.2µF

16V

RBIAS

49.9k

RBIAS

VOUT

12V

0.08A

D1B

RT

CSS

0.1µF

•

OVLO/DC

RDC

RT

12.1k

1MHz

D1A

T1

•

GND

SWB

3999 TA05

D1, D2: VISHAY BAT54C

T1: COOPER BUSSMANN CTX02-19065R

RELATED PARTS

PART NUMBER

DESCRIPTION

COMMENTS

LT3439

Slew Rate Controlled Ultralow Noise 1A Isolated DC/DC

Transformer Driver

VIN: 2.7V to 17.5V, IQ (Supply) = 12mA, ISD < 12mA, SO-16,

Low Noise:

很抱歉,暂时无法提供与“LT3999IDD#PBF”相匹配的价格&库存,您可以联系我们找货

免费人工找货