LTC1043

Dual Precision

Instrumentation Switched Capacitor

Building Block

DESCRIPTIO

U

FEATURES

■

■

■

■

■

■

■

The LTC®1043 is a monolithic, charge-balanced, dual

switched capacitor instrumentation building block. A pair

of switches alternately connects an external capacitor to

an input voltage and then connects the charged capacitor

across an output port. The internal switches have a

break-before-make action. An internal clock is provided

and its frequency can be adjusted with an external

capacitor. The LTC1043 can also be driven with an external

CMOS clock.

Instrumentation Front End with 120dB CMRR

Precise, Charge-Balanced Switching

Operates from 3V to 18V

Internal or External Clock

Operates up to 5MHz Clock Rate

Low Power

Two Independent Sections with One Clock

U

APPLICATIO S

■

■

■

■

■

The LTC1043, when used with low clock frequencies,

provides ultra precision DC functions without requiring

precise external components. Such functions are

differential voltage to single-ended conversion, voltage

inversion, voltage multiplication and division by 2, 3, 4, 5,

etc. The LTC1043 can also be used for precise V–F and

F–V circuits without trimming, and it is also a building

block for switched capacitor filters, oscillators and

modulators.

Precision Instrumentation Amplifiers

Ultra Precision Voltage Inverters, Multipliers

and Dividers

V–F and F–V Converters

Sample-and-Hold

Switched Capacitor Filters

The LTC1043 is manufactured using Linear Technology’s

enhanced LTCMOSTM silicon gate process.

, LTC and LT are registered trademarks of Linear Technology Corporation.

LTCMOS is a trademark of Linear Technology Corporation.

U

TYPICAL APPLICATIO

Instrumentation Amplifier

5V

4

140

5V

3

8

1µF

CH

11

1µF

(EXTERNAL)

CS

+

1/2 LTC1013

2

–

CS = CH = 1µF

120

8

1

VOUT

4

–5V

100

CMRR (dB)

7

DIFFERENTIAL

INPUT

CMRR vs Frequency

80

60

12

1µF

13

14

R1

16

1/2 LTC1043

0.01µF

17

LTC1043 • TA01

–5V

R2

CMRR > 120dB AT DC

CMRR > 120dB AT 60Hz

DUAL SUPPLY OR SINGLE 5V

GAIN = 1 + R2/R1

VOS ≈ 150µV

40

20

100

1k

10k

100k

FREQUENCY OF COMMON MODE SIGNAL

LTC1043 • TA02

∆ VOS

≈ 2µV/°C

∆T

COMMON MODE INPUT VOLTAGE INCLUDES THE SUPPLIES

1043fa

1

�LTC1043

W W

W

AXI U

U

ABSOLUTE

RATI GS

U

U

W

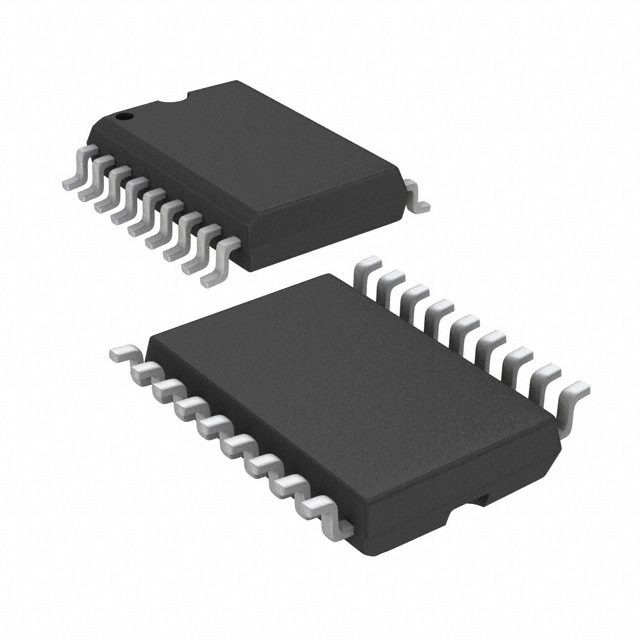

PACKAGE/ORDER I FOR ATIO

(Note 1)

ORDER PART

NUMBER

TOP VIEW

Supply Voltage ........................................................ 18V

Input Voltage at Any Pin .......... –0.3V ≤ VIN ≤ V+ + 0.3V

Operating Temperature Range

LTC1043C ................................... –40°C ≤ TA ≤ 85°C

LTC1043M (OBSOLETE).............– 55°C ≤ TA ≤ 125°C

Storage Temperature Range ................. –65°C to 150°C

Lead Temperature (Soldering, 10 sec).................. 300°C

SH B

1

18 S3B

CB+

2

17 V –

CB–

3

16 COSC

V+

4

15 S4B

S2B

5

14 S4A

S1B

6

13 S3A

S1A

7

12 CA–

S2A

8

11 CA+

NC

9

10 SHA

LTC1043CN

LTC1043CSW

N PACKAGE

18-LEAD PDIP

SW PACKAGE

18-LEAD PLASTIC SO

TJMAX = 100°C, θJA = 100°C/W PACKAGE (N)

TJMAX = 150°C, θJA = 85°C/W PACKAGE (SW)

LTC1043MD

D PACKAGE

18-LEAD SIDE BRAZED (HERMETIC)

OBSOLETE PACKAGE

Consider the N18 Package as an Alternate Source

LTC1043 • POI01

Consult LTC Marketing for parts specified with wider operating temperature ranges.

ELECTRICAL CHARACTERISTICS

+

The ● denotes specifications which apply over the full operating temperature

range, otherwise specifications are at TA = 25°C. V = 10V, V– = 0V, LTC1043M operates from –55°C ≤ TA ≤ 125°C; LTC1043C operates from

–40°C ≤ TA ≤ 85°C, unless otherwise noted.

SYMBOL PARAMETER

IS

Power Supply Current

CONDITIONS

MIN

Pin 16 Connected High or Low

LTC1043M

TYP MAX

OFF Leakage Current

Any Switch, Test Circuit 1 (Note 2)

●

RON

RON

fOSC

IOSC

ON Resistance

ON Resistance

Internal Oscillator Frequency

Pin Source or Sink Current

Test Circuit 2, VIN = 7V, 1 = ±0.5mA

V+ = 10V, V – = 0V

●

Test Circuit 2, VIN = 3.1V, 1 = ±0.5mA

V + = 5V, V – = 0V

●

COSC (Pin 16 to V –) = 0pF

COSC (Pin 16 to V –) = 100pF

Test Circuit 3

●

Pin 16 at V+ or V –

20

15

0.25

0.4

0.7

mA

mA

0.4

0.65

1

0.4

0.65

1

mA

mA

6

6

100

500

6

6

100

pA

nA

240

400

700

240

400

700

Ω

Ω

400

700

1

400

700

1

Ω

kΩ

50

75

kHz

kHz

kHz

70

100

µA

µA

185

34

40

●

Break-Before-Make Time

UNITS

0.4

0.7

●

II

LTC1043C

TYP MAX

0.25

●

COSC (Pin 16 to V –) = 100pF

MIN

50

75

70

100

20

15

185

34

40

25

25

ns

Clock to Switching Delay

COSC Pin Externally Driven

75

75

ns

fM

Max External CLK Frequency

COSC Pin Externally Driven with CMOS Levels

5

5

MHz

CMRR

Common Mode Rejection Ratio

V+ = 5V, V – = –5V, –5V < VCM < 5V

DC to 400Hz

120

120

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

2

dB

Note 2: OFF leakage current is guaranteed but not tested at 25°C.

1043fa

�LTC1043

U W

TYPICAL PERFOR A CE CHARACTERISTICS

Power Supply Current vs

Power Supply Voltage

RON vs VIN

1.6

550

TA = –55°C

COSC = 0pF

1.4

COSC = 0.0047pF

RON vs VIN

RON (PEAK)

500

I = 100µA

450 V

IN

1.2

TA = 25°C

COSC = 0pF

1.0

COSC = 0.0047pF

0.8

TA = 125°C

COSC = 0pF

0.6

COSC = 0.0047pF

0.4

280

V+ = 5V

V – = 0V

TA = 25°C

0.2

V+ = 10V

V – = 0V

TA = 25°C

RON (PEAK)

260

240 VIN

I = 100µA

220

400

350

300

I = 100µA

250

200

RON (Ω)

RON (Ω)

SUPPLY CURRENT (mA)

(Test Circuits 2 through 4)

180

I = 100µA

160

I = mA

200

140

150

120

100

100

I = mA

0

2

4

6

1

0

8 10 12 14 16 18 20

VSUPPLY (V)

3

2

4

LTC1043 • TPC01

180

160

I = 100µA

140

800

600

700

500

200

80

100

8

0

10 12 14 16 18 20

VIN (V)

VIN ≈ 3.2V

400

300

6

VIN ≈ 7V

3V ≤ V+ + ≤18V

V – = 0V

TA = 25°C

0

2

4

6

250

225

VIN ≈ 15.1V

fOSC (kHz)

fOSC (Hz)

TA = 125°C

TA = 70°C

TA = –55°C

200

100

8 10 12 14 16 18 20

VSUPPLY (V)

0

V+ = 15V, V – = 0V

2

4

6

8 10 12 14 16 18 20

VSUPPLY (V)

LTC1043 • TPC06

Normalized Oscillator Frequency,

fOSC vs Supply Voltage

2.0

COSC = 0pF

175

V+ = 10V, V – = 0V

V+ = 5V, V – = 0V

150

125

100

75

1k

50

10

300

TA = 25°C

200

100k

9

500

Oscillator Frequency, fOSC

vs Supply Voltage

TA = 25°C

10k

600

LTC1043 • TPC05

Oscillator Frequency, fOSC

vs COSC

8

I = 100µA

VIN

400

VIN ≈ 11V

LTC1043 • TPC04

1M

900

I = 100µA

VIN

800

100

4

7

RON (PEAK)

1000

700

120

2

5 6

VIN (V)

1100

RON (PEAK)

VIN = 1.6V

900

I = mA

0

4

RON (Peak) vs Power Supply

Voltage and Temperature

RON (Ω)

I = 100µA

1000

RON (Ω)

RON (Ω)

220 V

IN

200

V+ = 15V

V – = 0V

TA = 25°C

3

LTC1043 • TPC03

RON (Peak) vs Power Supply

Voltage

RON (PEAK)

240

2

LTC1043 • TPC02

RON vs VIN

260

1

0

5

VIN (V)

OSCILLATOR FREQUENCY

NORMALIZED TO fOSC AT 5V SUPPLY

0

COSC = 100pF

25

0pF < COSC < 0.01µF

TA = 25°C

1.8

1.6

1.4

1.2

1

0.8

0.6

0.4

0.2

0

100

0

2k

4k

6k

COSC (pF)

8k

10k

LTC1043 • TPC07

0

2

4

6

8 10 12 14 16 18 20

VSUPPLY (V)

LTC1043 • TPC08

0

2

4

6

8 10 12 14 16 18 20

VSUPPLY (V)

LTC1043 • TPC09

1043fa

3

�LTC1043

U W

TYPICAL PERFOR A CE CHARACTERISTICS

Oscillator Frequency, fOSC

vs Ambient Temperature, TA

COSC Pin ISINK, ISOURCE

vs Supply Voltage

350

fOSC (kHz)

275

250

225

200

V+ = 10V, V– = 0V

175

125

V+

–

= 5V, V = 0V

V+ = 15V, V– = 0V

100

50

25

0

75 100

–50 –25

AMBIENT TEMPERATURE (°C)

80

ISINK, TA = –55°C

75

60

ISINK, TA = 25°C

ISOURCE, TA = –55°C

50

ISOURCE, TA = 25°C

50

40

30

25

ISINK, TA = 125°C

20

ISOURCE, TA = 125°C

0

0

125

TA = 25°C

70

tNOV (ns)

300

150

Break-Before-Make Time, tNOV,

vs Supply Voltage

100

COSC = 0pF

PIN 16 SOURCE OR SINK CURRENT (µA)

325

(Test Circuits 2 through 4)

2

4

6

8

10

12

14

16

10

18

0

LTC1043 • TPC11

LTC1043 • TPC10

2

4

6

8 10 12 14 16 18 20

VSUPPLY (V)

LTC1043 • TPC12

W

BLOCK DIAGRA

S1A

7

S2A

8

SHA 10

11 CA+

12 CA–

S3A

13

S4A

14

CHARGE

BALANCING

CIRCUITRY

S1B

6

SHB 1

S2B

5

2 CB+

3 CB–

S3B

18

S4B

15

CHARGE

BALANCING

CIRCUITRY

NON-OVERLAPPING

CLOCK

V+

V–

COSC

16

OSCILLATOR

V+

4

V–

17

THE CHARGE BALANCING CIRCUITRY SAMPLES THE VOLTAGE

AT S3 WITH RESPECT TO S4 (PIN 16 HIGH) AND INJECTS A

SMALL CHARGE AT THE C+ PIN (PIN 16 LOW).

THIS BOOSTS THE CMRR WHEN THE LTC1043 IS USED AS AN

INSTRUMENTATION AMPLIFIER FRONT END.

FOR MINIMUM CHARGE INJECTION IN OTHER TYPES OF

APPLICATIONS, S3A AND S3B SHOULD BE GROUNDED

THE SWITCHES ARE TIMED AS SHOWN WITH PIN 16 HIGH

LTC1043 • BD01

1043fa

4

�LTC1043

TEST CIRCUITS

Test Circuit 1. Leakage Current Test

(7, 13, 6, 18)

(7, 13, 6, 18)

(8, 14, 5, 15)

A

0V TO 10V

Test Circuit 2. RON Test

+

(11, 12, 2, 3)

NOTE: TO OPEN SWITCHES,

S1 AND S3

SHOULD BE CONNECTED

TO V –. TO OPEN S2, S4,

COSC PIN SHOULD BE

TO V+ COSC

+

(8, 14, 5, 15)

VIN

(11, 12, 2, 3)

100µA to 1mA

CURRENT SOURCE

LTC1043 • TC01

A

LTC1043 • TC02

Test Circuit 3. Oscillator Frequency, fOSC

Test Circuit 4. CMRR Test

7

V–

(TEST PIN) 2

17

10

COSC

V+

4

+

LTC1043

VOUT

8

11

+

16

1µF

1µF

CAPACITORS ARE

NOT ELECTROLYTIC

5

12

+

6

IV

13

14

LTC1043 • TC03

+

V– ≤ VCM ≤ V+

CMRR = 20 LOG

( )

VCM

VOUT

NOTE: FOR OPTIMUM CMRR, THE COSC SHOULD

BE LARGER THAN 0.0047µF, AND

THE SAMPLING CAPACITOR ACROSS

PINS 11 AND 12 SHOULD BE PLACED

OVER A SHIELD TIED TO PIN 10

LTC1043 • TC04

U

W

U U

APPLICATIO S I FOR ATIO

Common Mode Rejection Ratio (CMRR)

The LTC1043, when used as a differential to single-ended

converter rejects common mode signals and preserves

differential voltages (Figure 1). Unlike other techniques,

the LTC1043’s CMRR does not degrade with increasing

common mode voltage frequency. During the sampling

mode, the impedance of Pins 2, 3 (and 11, 12) should be

reasonably balanced, otherwise, common mode signals

will appear differentially. The value of the CMRR depends

on the value of the sampling and holding capacitors

(CS, CH) and on the sampling frequency. Since the

common mode voltages are not sampled, the

common mode signal frequency can well exceed the

sampling frequency without experiencing aliasing

phenomena. The CMRR of Figure 1 is measured by

1/2 LTC1043

7

8

C+ 11

VD

+

+

CS

VD

CH

C– 12

13

VCM

14

+

CS, CH ARE MYLAR OR POLYSTRENE

LTC1043 • AI01

Figure 1. Differential to Single-Ended Converter

1043fa

5

�LTC1043

U

W

U U

APPLICATIO S I FOR ATIO

shorting Pins 7 and 13 and by observing, with a precision

DVM, the change of the voltage across CH with respect to

an input CM voltage variation. During the sampling and

holding mode, charges are being transferred and minute

voltage transients will appear across the holding capacitor. Although the RON on the switches is low enough to

allow fast settling, as the sampling frequency increases,

the rate of charge transfer increases and the average

voltage measured with a DVM across it will increase

proportionally; this causes the CMRR of the sampled data

system, as seen by a “continuous” instrument (DVM), to

decrease (Figure 2).

Switch Charge Injection

Figure 3 shows one out of the eight switches of the

LTC1043, configured as a basic sample-and-hold circuit.

When the switch opens, a ‘‘hold step’’ is observed and its

magnitude depends on the value of the input voltage.

Figure 4 shows charge injected into the hold capacitor. For

instance, a 2pCb of charge injected into a 0.01µF capacitor

causes a 200µV hold step. As shown in Figure 4, there is

a predictable and repeatable charge injection cancellation

when the input voltage is close to half the supply voltage

of the LTC1043. This is a unique feature of this product,

containing charge-balanced switches fabricated with a

self-aligning gate CMOS process. Any switch of the

LTC1043, when powered with symmetrical dual supplies,

will sample-and-hold small signals around ground without any significant error.

Shielding the Sampling Capacitor for Very High CMRR

Internal or external parasitic capacitors from the C + pin(s)

to ground affect the CMRR of the LTC1043 (Figure 1).

The common mode error due to the internal junction

capacitances of the C + Pin(s) 2 and 11 is cancelled through

internal circuitry. The C + pin, therefore, should be used as

the top plate of the sampling capacitor. The interpin

capacitance between pin 2 and dummy Pin 1 (11 and 10)

appears in parallel with the sampling capacitor so it does

not degrade the CMRR. A shield placed underneath

the sampling capacitor and connected to either Pin 1 or 3

helps to boost the CMRR in excess of 120dB (Figure 5).

Excessive external parasitic capacitance between the C –

pins and ground indirectly degrades CMRR; this becomes

visible especially when the LTC1043 is used with clock

frequencies above 2kHz. Because of this, if a shield is

used, the parasitic capacitance between the shield and

circuit ground should be minimized.

It is recommended that the outer plate of the sampling

capacitor be connected to the C – pin(s).

Input Pins, SCR Sensitivity

An internal 60Ω resistor is connected in series with the

input of the switches (Pins 5, 6, 7, 8, 13, 14, 15, 18) and

it is included in the RON specification. When the input

voltage exceeds the power supply by a diode drop, current

will flow into the input pin(s). The LTC1043 will not latch

until the input current reaches 2mA–3mA. The device will

140

120

CS = CH = 1µF

5V

CS = 1µF, CZH = 0.1µF

2

+

6

CMRR (dB)

100

1/2 LTC1013

1/8 LTC1043

VOUT

–

80

VIN

1000pF

–5V

60

V+

40

SAMPLE

HOLD TO PIN 16

0V

LTC1043 • AI03

20

100

1k

10k

100k

fOSC (Hz)

LTC1043 • AI02

Figure 2. CMRR vs Sampling Frequency

Figure 3

1043fa

6

�LTC1043

U

W

U U

APPLICATIO S I FOR ATIO

recover from the latch mode when the input drops 3V to 4V

below the voltage value which caused the latch. For

instance, if an external resistor of 200Ω is connected in

series with an input pin, the input can be taken 1.3V above

the supply without latching the IC. The same applies for the

C + and C – pins.

COSC Pin (16), Figure 6

The Cosc pin can be used with an external capacitor, Cosc,

connected from Pin 16 to Pin 17, to modify the internal

oscillator frequency. If Pin 16 is floating, the internal 24pF

capacitor, plus any external interpin capacitance, set the

oscillator frequency around 190kHz with ±5V supply. The

typical performance characteristics curves provide the

necessary information to set the oscillator frequency for

various power supply ranges. Pin 16 can also be driven

with an external clock to override the internal oscillator.

Although standard 7400 series CMOS gates do not

guarantee CMOS levels with the current source and sink

requirements of Pin 16, they will in reality drive the Cosc

pin. CMOS gates conforming to standard B series output

drive have the appropriate voltage levels and more than

enough output current to simultaneously drive several

LTC1043 COSC pins. The typical trip levels of the Schmitt

trigger (Figure 6) are given below.

SUPPLY

V+ = 5V,

TRIP LEVELS

V – = 0V

VH = 3.4VVL = 1.35V

V+ = 10V, V – = 0V

VH = 6.5VVL = 2.8V

V+ = 15V, V – = 0V

VH = 9.5VVL = 4.1V

12

V+ = 15V

V– = 0V

CHARGE INJECTION (pCb)

10

8

V+ = 10V

V– = 0V

6

1

OUTSIDE FOIL

4

V+ = 5V

V– = 0V

2

CS

2

3

0

0

2

4

6

10

8

VIN (V)

12

14

PRINTED CIRCUIT

BOARD AREA

16

LTC1043

LTC1043 • AI05

LTC1043 • AI04

Figure 5. Printed Circuit Board Layout

Showing Shielding the Sampling Capacitor

Figure 4. Individual Switch Charge Injection

vs Input Voltage

V+

4

38µF

COSC

16

COSC

(EXTERNAL)

TO CLK GENERATOR

24pF

17

fOSC = 190kHz •

V–

(24pF)

(24pF + COSC)

LTC1043 * AI06

Figure 6. Internal Oscillator

1043fa

7

�LTC1043

U

TYPICAL APPLICATIO S

Divide by 2

Multiply by 2

Ultra Precision Voltage Inverter

1/2 LTC1043

1/2 LTC1043

VIN

1/2 LTC1043

7

8

VOUT

VOUT = VIN /2

7

7

8

VOUT = –VIN

8

VIN

1µF

11

11

11

1µF

1µF

1µF

1µF

1µF

12

12

12

VIN

13

14

13

17

16

13

14

14

16

16

17

17

0.01µF

0.01µF

0.01µF

VOUT = VIN /2 ± 1ppm

0 ≤ VIN ≤ V+

3 ≤ V+ ≤ 18V

VOUT = 2VIN ± 5ppm

0 ≤ VIN ≤ V+ /2

3 ≤ V+ ≤ 18V

LTC1043 • A01

Precision Multiply by 3

VOUT = –VIN ±2ppm

V – < VIN < V +

V + = +5V, V – = –5V

LTC1043 * A03

LTC1043 • A02

Precision Multiply by 4

Divide by 3

VIN

LTC1043

LTC1043

LTC1043

7

8

7

11

8

VIN

VIN

7

11

11

1µF

1µF

1µF

12

12

12

13

8

13

14

14

13

14

6

5

VOUT

VOUT

2VIN

5

6

2

1µF

5

6

VOUT = 4VIN

1µF

2

2

1µF

1µF

1µF

3

18

1µF

1µF

1µF

3

3

15

18

VOUT

15

18

15

1µF

16

17

0.01µF

VOUT = 3VIN ±10ppm

0 < VIN < V+/3

3V < V+ < 18V

17

16

16

LTC1043 • A04

VOUT = 4VIN ±40ppm

0 ≤ VIN ≤ V+/4

3V < V+ < 18V

17

0.01µF

0.01µF

VOUT = VIN /3 ±3ppm

0 ≤ VIN ≤ V+

LTC1043 • A05

LTC1043 • A06

1043fa

8

�LTC1043

U

TYPICAL APPLICATIO S

Divide by 4

0.005% V/F Converter

–5V

VIN

7

LT1009

2.5k

1k

LTC1043

8

17

5V

1/2 LTC1043

11

8

1µF

1µF

7

1µF

12

11

fOUT: 0kHz TO 30kHz

14

13

13

14

4

VIN

0V TO 3V

VOUT

5

6

6.19k

12

5V

GAIN

2.5k

16

0.01µF

–

1µF

LF356

+

2

1µF

1µF

–5V

3

30pF

22k

18

15

16

17

330k

Q1

2N2907A

0.01µF

1µF

–5V

LTC1043 • A08

0 ≤ VIN ≤ V+

VOUT = VIN /4 ±5ppm

LTC1043 • A07

0.01% Analog Multiplier

1/4 LTC1043

14

1k

–5V

13

LT1004-1.2V

1µF

12

5V

YINPUT

7.5k*

2

1µF

–

+

†

80.6k*

0.01µF

6

16

4

XINPUT

30pF

6

2

5

–

7

LT1056

3

330k

OPERATE LTC1043 FROM ±5V

POLYSTYRENE, MOUNT CLOSE

*1% FILM RESISTOR

ADJUST OUTPUT TRIM

SO X • Y = OUTPUT ±0.01%

†

2N2907A

(FOR START-UP)

1µF

–5V

5V

1/4 LTC1043

–5V

22k

20k

OUTPUT

TRIM

7

LT1056

3

0.001µF

2

0.001µF

†

+

6

OUTPUT

XY ±0.01%

4

–5V

LTC1043 • A09

1043fa

9

�LTC1043

U

TYPICAL APPLICATIO S

Voltage Controlled Current Source with

Ground Referred Input and Output

Single 5V Supply, Ultra Precision

Instrumentation Amplifier

5V

5V

+

LTC1043

7

3

8

7

+

6

LTC1052

2

4

1µF

INPUT

8

+

1/2 LT1013

OUTPUT

AV = 1000

8

–

11

3

INPUT

0V TO 2V

2

–

1

4

1

0.1µF 0.1µF

1µF

0.68µF

12

–

99.9k

100Ω

13

5V

14

1k

4

V+ = 5V

43k

5

6

8

0.22µF

7

10k

2

11

1µF

NONPOLARIZED

1µF

1N914

1µF

1µF

3

18

100Ω

12

15

14

≈ –0.5V

13

1/2 LTC1043

16

17

4

INPUT AND OUTPUT VOLTAGE RANGE INCLUDES GROUND.

INPUT REFERRED OFFSET ERRORS ARE TYPICALLY 3µV WITH

1µV OF NOISE

CMRR ~ 120dB

5V

0.0047

1OUT =

VIN

100Ω

16

17

0.001µF

LTC1043 • A10

OPERATES FROM A SINGLE 5V SUPPLY

LTC1043 • A11

Precision Instrumentation Amplifier

5V

CHOPPER

4

1/2 LTC1043

+ INPUT

6

AC AMPLIFIER

1/4 LTC1043

11

8

2

1µF

1µF

5V

1µF

7

5

PHASE

SENSITIVE

DEMODULATOR

3

1M 2

+

7

LT1056

–

1/4 LTC1043

1µF

6

13

100k

12

4

100k

2

–

100k

5V

7

LT1056

14

–5V

DC

OUTPUT AMPLIFIER

1µF

3

3

+

6

OUTPUT

4

–5V

100Ω

– INPUT

18

15

16

17

0.01µF

0.01

–5V

OFFSET = 10µV

DRIFT = 0.1µV/°C

FULL DIFFERENTIAL INPUT

CMRR = 140dB

OPEN LOOP GAIN > 10 8

GAIN = R2/R1 + 1

IBIAS = 1nA

R2

100k

R1

100Ω

LTC1043 • A12

1043fa

10

�LTC1043

U

TYPICAL APPLICATIO S

Lock-In Amplifier (= Extremely Narrow-Band Amplifier)

THERMISTOR BRIDGE

IS THE SIGNAL SOURCE

SYNCHRONOUS

DEMODULATOR

10k*

10k*

T1

500Hz

SINE DRIVE

4

1

6.19k

3

3

6.19k 2

RT

5V

5V

6.19k

2

+

1/4 LTC1043

6

LT1007

–

3

12

–

5V

LM301A

13

+

2

8

1

100k

1M

–

LT1012

–5V

14

3

–5V

16

30pF

+

T1 = TF5SX17ZZ, TOROTEL

RT = YSI THERMISTOR 44006

≈ 6.19k AT 37.5°C

*MATCH 0.05%

6.19k = VISHAY S-102

OPERATE LTC1043 WITH

±5V SUPPLIES

47µF

PHASE TRIM

5V

0.002

4

–5V

+

50k

VOUT = 1000 • DC

BRIDGE SIGNAL

1µF

100Ω

0.01µF

6

5V

10k

2

7

LT1011

3

–

LOCK-IN AMPLIFIER TECHNIQUE

USED TO EXTRACT VERY SMALL

SIGNALS BURIED INTO NOISE

1k

8

+

LTC1043 • A013

4

1

–5V

ZERO CROSSING DETECTOR

50MHz Termal RMS/DC Converter

5V

5V

4

30k*

30k*

5V

1/2 LTC1043

6

3

5

8

+

10k

LT1013

2

2

1µF

1µF

1µF

3

–

18

15

0.01µF

1µF

5V

+

LT1013

100k*

301Ω*

10k

6

–

7

DC OUTPUT

0V TO 3.5V

10k

10k

10k

17

BRN

RED

N

CALIBRATION ADJUST

20k

5

16

0.01µF

300mV

10VRMS

INPUT

4

1

RED

T2

T2A

1A

GRN

T1B

T2B

*1% RESISTOR

GRN

2% ACCURACY DC 50MHZ

100:1 CREST FACTOR CAPABILITY

T1 TO T2 = YELLOW SPRINGS INST. CO.

THERMISTOR COMPOSITE

ENCLOSE T1 AND T2 IN STYROFOAM

LTC1043 • A14

1043fa

11

�LTC1043

U

TYPICAL APPLICATIO S

Quad Single 5V Supply, Low Hold Step, Sample-and-Hold

5V

2

1/4 LT1014

NC

7

3

8

13

4

–

+

1

OUTPUT

1/4 LT1014

NC

11

6

14

OUTPUT

+

CL

0.01µF

2

VIN

VIN

6

9

–

1/4 LT1014

NC

12

5

CL

0.01µF

11

–

13

5

14

7

OUTPUT

1/4 LT1014

+

NC

18

10

15

CL

0.01µF

12

OUTPUT

+

VIN

HOLD

LTC1043 • A15

16

SAMPLE

8

CL

0.01µF

3

VIN

–

17

4

– 5V

FOR 1V ≤ VIN ≤ 4V, THE HOLD STEP IS ≤ 300µV

ACQUISITION TIME ~ 8 • RON CH FOR 10-BIT ACCURACY

LTC1043 • A16

Single Supply Precision Linearized Platinum RTD Signal Conditioner

250k*

(LINEARITY CORRECTION LOOP)

5V

3

10k*

+

8

1/2 LT1013

2

–

5V

2.4k

1

2.74k*

4

LT1009

2.5V

50k

ZERO

ADJUST

8.25k*

0.1µF

4

2k

1/2 LTC1043

7

0V TO 4V = 0°C TO 400°C

±0.05°C

1/2 LTC1043

8

5

5

6

+

1/2 LT1013

6

11

1µF

2

1µF

13

8.06k*

3

14

1mA

Rp

100Ω

AT 0°C

15

16

Rp = ROSEMOUNT 118MFRTD

* 1% FILM RESISTOR

TRIM SEQUENCE:

SET SENSOR TO 0°C VALUE. ADJUST ZERO FOR 0V OUT

SET SENSOR TO 100°C VALUE. ADJUST GAIN FOR 1,000V OUT

SET SENSOR TO 400°C VALUE. ADJUST LINEARITY FOR 4,000V OUT

REPEAT AS REQUIRED

5k

1µF

1µF

887Ω

12

–

7

1k

GAIN

ADJUST

18

1k*

17

0.01µF

LTC1043 • A17

1043fa

12

�LTC1043

U

TYPICAL APPLICATIO S

0.005% F/V Converter

75k*

10k

GAIN TRIM

1µF

1/4 LTC1043

1k

5V

13

–5V

–

14

1µF

LT1004-1.2C

12

–5V

1000pF

FREQUENCY IN

0kHz TO 30kHz

0V TO 3V OUTPUT

LF356

+

4

5V

17

–5V

*75k = TRW # MTR-5/120ppm

16

LTC1043 • A18

High Frequency Clock Tunable Bandpass Filter

R1

10k

R2

10k

10k

RIN

VIN

5V

–

1/2 LTC1043

LT1056

7

8

+

–5V

CLOCK

INPUT

11

16

1000pF

200pF

BANDPASS

OUTPUT

12

5V

13

14

4

–

1/2 LTC1043

LT1056

RQ = 10k

5V

5

6

+

–5V

2

1000pF

200pF

3

fCLK

•

BANDPASS CENTER FREQUENCY fO =

31.4

BANDPASS GAIN AT fO IS: RQ /RIN

RQ

R2

Q=

R2

R1

fO MAX ≤ 100kHz

QMAX AT 100kHz fO IS ≤10

(fO • Q) MAX ≤ 1MHz

fCLK MAX ≤ 3MHz, Q < 2

R2

R1

5V

15

18

–

LT1056

17

–5V

+

– 5V

LTC1043 • A19

1043fa

13

�LTC1043

U

TYPICAL APPLICATIO S

Frequency-Controlled Gain Amplifier

13A 1/2 LTC1043A

12A

16A

GAIN CONTROL

0kHz TO 10kHz = GAIN 0 TO 1000

13B 1/2 LTC1043B

14A

14B

12B

16B

0.01µF

100pF

11A

11B

7A

7B

8A

8B

VIN

5V

2

–

0.01µF

7

6

LT1056

3

FOR DIFFERENTIAL INPUT, GROUND PIN 8A AND USE PINS 13A AND 7A FOR INPUTS

fIN • 0.01µF

GAIN =

; GAIN IS NEGATIVE AS SHOWN

1kHz • 100pF

FOR SINGLE-ENDED INPUT AND POSITIVE GAIN, GROUND PIN 8A AND USE PIN 7A FOR INPUT

USE ± 5V SUPPLIES FOR LTC1043

+

VOUT

4

–5V

LTC1043 • A20

Relative Humidity Sensor Signal Conditioner

0.01µF

1/4 LTC1043

8

7

16

–5V

17

11

470k

100pF

1k*

500

90%

RH TRIM

5V

1/4 LTC1043

13

2

14

–

7

LT1056

3

12

1µF

+

4

–5V

1µF

6

10k

3

+

6

LM301A

2

8

–

OUTPUT

0V TO 1V = 0% TO 100%

1

LT1004

1.2V

SENSOR

9k*

22M

100pF

10k

5% RH TRIM

33k

* = 1% FILM RESISTOR

SENSOR = PANAMETRICS # RHS

≈ 500pF AT RH = 76%

1.7 pF/%RH

1k*

LTC1043 • A21

1043fa

14

�LTC1043

U

TYPICAL APPLICATIO S

Linear Variable Differential Transformer (LVDT), Signal Conditioner

1/4 LTC1043

0.005µF

0.005µF

30k

7

5V

5V

30k

3

4

11

8

+

1.5kHz

1

LT1013

2

8

RD-BLUE

YEL-BLK

–

4

100k

5

– 5V

BLUE

GRN

AMPLITUDE STABLE

SINE WAVE SOURCE

6

10k

1N914

4.7k

LT1004

1.2V

Q1

2N4338

1.2k

+

1/2 LT1013

1µF

–

10µF

OUTPUT

0V ±2.5V

0M 2.50M

200k

YEL-RED

BLK

10k GAIN TRIM

LVDT

+

7

12

7.5k

–5V

17

13

14

1/4 LTC1043

LVDT = SCHAEVITZ E-100

5V

100k

5V

0.01µF

3

100k

PHASE

TRIM

1k

8

+

7

LT1011

2

TO PIN 16, LTC1043

1

–

4

–5V

LTC1043 • A22

Precision Current Sensing in Supply Rails

IIN

SHUNT CAN BE IN POSITIVE

OR NEGATIVE SUPPLY LEAD

RSHUNT

1/2 LTC1043

7

VOUT

8

11

+

1µF

1µF

12

13

14

16

17

0.01µF

LTC1043 • A23

1043fa

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

15

�LTC1043

U

PACKAGE DESCRIPTIO

D Package

18-Lead Side Brazed (Hermetic)

(Reference LTC DWG # 05-08-1210)

.165

(4.191)

MAX

.485

(12.319)

MAX

.020 – .060

(0.508 – 1.524)

.910

(23.114)

MAX

.005

(0.127)

MIN

17

18

16

15

14

13

12

11

10

.290

(7.366)

TYP

.008 – .015

(0.203 – 0.381)

.100

(2.54)

BSC

.125

(3.175)

MIN

.300

(7.620)

REF

PIN NO. 1

IDENT

.054

(1.372)

TYP

.015 – .023

(0.381 – 0.584)

3

2

1

4

5

7

6

8

9

D18 0801

OBSOLETE PACKAGE

N Package

18-Lead PDIP (Narrow .300 Inch)

(Reference LTC DWG # 05-08-1510)

.900*

(22.860)

MAX

18

17

16

15

14

.130 ± .005

(3.302 ± 0.127)

.300 – .325

(7.620 – 8.255)

13

12

11

10

.045 – .065

(1.143 – 1.651)

.020

(0.508)

MIN

.065

(1.651)

TYP

.008 – .015

(0.203 – 0.381)

.255 ± .015*

(6.477 ± 0.381)

+.035

.325 –.015

1

2

3

5

4

6

8

7

(

9

8.255

+0.889

–0.381

.120

(3.048)

MIN

)

.005

(0.127)

MIN

.018 ± .003

(0.457 ± 0.076)

.100

(2.54)

BSC

NOTE:

1. DIMENSIONS ARE

INCHES

MILLIMETERS

*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .010 INCH (0.254mm)

N18 1002

SW Package

18-Lead Plastic Small Outline (Wide .300 Inch)

(Reference LTC DWG # 05-08-1620)

.050 BSC .045 ±.005

.030 ±.005

TYP

.447 – .463

(11.354 – 11.760)

NOTE 4

N

18

17

16

15

14

13

12

11

10

N

.325 ±.005

.420

MIN

.394 – .419

(10.007 – 10.643)

NOTE 3

1

2

3

N/2

NOTE:

1. DIMENSIONS IN

N/2

RECOMMENDED SOLDER PAD LAYOUT

.005

(0.127)

RAD MIN

.009 – .013

(0.229 – 0.330)

.291 – .299

(7.391 – 7.595)

NOTE 4

.010 – .029 × 45°

(0.254 – 0.737)

1

3

.093 – .104

(2.362 – 2.642)

0° – 8° TYP

.050

(1.270)

BSC

NOTE 3

.016 – .050

(0.406 – 1.270)

16

2

Linear Technology Corporation

.014 – .019

(0.356 – 0.482)

TYP

4

5

6

7

8

9

.037 – .045

(0.940 – 1.143)

INCHES

(MILLIMETERS)

2. DRAWING NOT TO SCALE

3. PIN 1 IDENT, NOTCH ON TOP AND CAVITIES

ON THE BOTTOM OF PACKAGES ARE THE

MANUFACTURING OPTIONS.

THE PART MAY BE SUPPLIED WITH OR

WITHOUT ANY OF THE OPTIONS

4. THESE DIMENSIONS DO NOT INCLUDE

MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT

EXCEED .006" (0.15mm)

.004 – .012

(0.102 – 0.305)

S18 (WIDE) 0502

1043fa

LW/TP 1202 1K REV A • PRINTED IN USA

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900 ● FAX: (408) 434-0507

●

www.linear.com

LINEAR TECHNOLOGY CORPORATION 1985

�