LTC6228/LTC6229

0.88nV/√Hz 730MHz, 500V/µs,

Low Distortion Rail-to-Rail Output Op

Amps with Shutdown

DESCRIPTION

FEATURES

Ultra Low Voltage Noise: 0.88nV/√Hz

n Low Distortion at High Speeds:

HD2/HD3 < −100dBc (Av = +1, 4VP-P, 2MHz, RL = 1kΩ)

n High Slew Rate: 500V/μs

n GBW = 890MHz

n –3dB Frequency (A = +1): 730MHz

V

n Input Offset Voltage: 250μV Max Across Temperature

n Offset Drift :0.4μV/°C

n Input Common Mode Range Includes Negative Rail

n Output Swings Rail-to-Rail

n Supply Current: 16mA/Channel Typ

n Shutdown Supply Current = 500µA

n Operating Supply Range: 2.8V to 11.75V

n Large Output Current: 80mA Min

n Very High Open Loop Gain: 5.6V/μV (135dB), R = 1kΩ

L

n Operating Temp Range: –40°C to 125°C

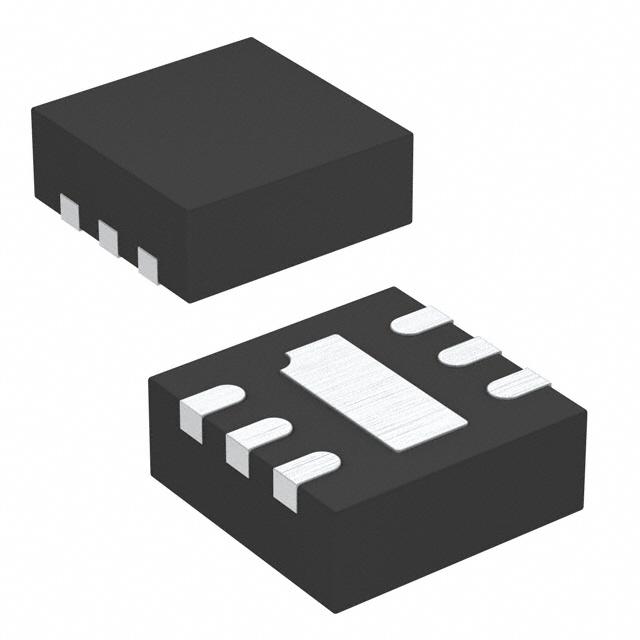

n Singles in 8-Lead SOIC, TSOT-23, DC-6, Duals in

DD10, MS8

n

APPLICATIONS

Optical Electronics: Fast Transimpedance Amplifiers

Driving High Dynamic Range A/D Converters

n Active Filters

n Video Amplifiers

n High Speed Differential to Single-Ended Conversion

n Low Voltage Hi-Fi Amplification

n

n

All registered trademarks and trademarks are the property of their respective owners.

TYPICAL APPLICATION

LTC6228 Based Driver for the LTC2387-18 SAR ADC

The LTC®6228/LTC6229 are single/dual very fast, low

noise rail-to-rail output, unity gain stable op amps. They

have a gain-bandwidth product of 890MHz and a slew rate

of 500V/μs. The low input referred voltage noise of only

0.88nV/√Hz and low distortion performance of better than

−100dB at 4VP-P even for signals as fast as 2MHz make

them ideal for applications that require high dynamic

range and deal with high slew rate signals, such as driving

A/D converters. Additional features include Shutdown and

the ability to enable/disable internal bias current cancellation to optimize noise performance.

The combination of low offset, low offset drift, high gain

and high CMRR make the LTC6228 family the superior

choice for wide dynamic range applications.

The LTC6228 family maintains excellent performance for

supply voltages of 2.8V to 11.75V and the devices are

specified at supplies of 3V, 5V and 10V(±5V). With an

input range extending to the negative rail and an output range that encompasses the entire supply range, the

operational amplifier can accommodate wide swinging

signals, and single supply operation.

For space constrained PCB layouts, the LTC6228 is available in a 2mm × 2mm DFN and the LTC6229 is available in a

3mm × 3mm DFN. The amplifiers are also available in conventional leaded packages. These amplifiers can be used

as improved replacements for many high speed op amps

to improve speed, noise, distortion and dynamic range.

System Performance: 2 x LTC6228 Driving LTC2387-18

8192 Point FFT, –1dBFS

fSMPL = 15Msps, fIN = 1MHz

0

0V

+

–20

CLK

LTC6228

–

DCO

25Ω

IN+

DA

LVDS

INTERFACE

DB

82pF

LTC2387-18

82pF

4.096V

0V

+

–

IN–

25Ω

LTC6228

TWOLANES

TESTPAT

VCM

PD

0.1µF

REFB

CNV

SAMPLE

CLOCK

–2.5V

6228 TA01a

AMPLITUDE (dBFS)

4.096V

7.5V

–40

7.3VP-P 1MHz INPUT SIGNAL

SNR = 93.4dB

SFDR = 95dB

THD = –93.8dB

–60

–80

–100

–120

–140

0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5 5.5 6 6.5 7 7.5

FREQUENCY (MHz)

6228 TA02

Rev. B

Document Feedback

For more information www.analog.com

1

�LTC6228/LTC6229

ABSOLUTE MAXIMUM RATINGS

(Note 1)

Total Supply Voltage (V– to V+)..................................12V

Input Voltage (–IN, +IN, SHDN).... V– – 0.3V to V+ + 0.3V

Input Current (–IN, +IN, SHDN) (Note 2)............... ±10mA

Operating Temperature Range

LTC6228I/LTC6229I (Note 4)................–40°C to 85°C

LTC6228H/LTC6229H (Note 4)........... –40°C to 125°C

Specified Temperature Range

LTC6228I/LTC6229I (Note 4)................–40°C to 85°C

LTC6228H/LTC6229H (Note 4)........... –40°C to 125°C

Output Current (OUT, FB)(Note 3)....................... ±100mA

Output Short-Circuit Duration..............Thermally Limited

Storage Temperature Range................... –65°C to 150°C

Maximum Junction Temperature........................... 150°C

Lead Temperature (Soldering 10s)

(MSOP/S8/TSOT Only).......................................... 300°C

PIN CONFIGURATION

TOP VIEW

TOP VIEW

8

SHDN

–IN 2

7

V+

6

OUT

5

V–

+IN 3

– +

FB 1

V– 4

V– 2

V– 3

4 –IN

TOP VIEW

6 OUT

7

V–

5 SHDN

S6 PACKAGE

6-LEAD PLASTIC TSOT-23

TJMAX = 150°C, θJA = 192°C/W (NOTE 7)

TOP VIEW

+IN 2

+ –

+IN 3

S8 PACKAGE

8-LEAD PLASTIC SO

TJMAX = 150°C, θJA = 120°C/W (NOTE 7)

V+ 1

6 V+

OUT 1

5 –IN

4 SHDN

DC PACKAGE

6-LEAD (2mm × 2mm) PLASTIC DFN

TJMAX = 150°C, θJA = 80°C/W (NOTE 7)

EXPOSED PAD (PIN 7) IS V–, MUST BE SOLDERED TO PCB

OUTA

1

–INA

2

+INA

3

V–

4

SHDNA

5

10 V+

11

V–

9 OUTB

8 –INB

7 +INB

6 SHDNB

DD PACKAGE

10-LEAD (3mm × 3mm) PLASTIC DFN

TJMAX = 125°C, θJA = 43°C/W (NOTE 2)

EXPOSED PAD (PIN 11) IS V–, MUST BE SOLDERED TO PCB

1

2

3

4

– +

OUTA

–INA

+INA

V–

9

V–

+ –

TOP VIEW

8

7

6

5

V+

OUTB

–INB

+INB

MSE PACKAGE

8-LEAD PLASTIC MSOP

TJMAX = 150°C, θJA = 35°C/W (NOTE 8)

EXPOSED PAD (PIN 9) IS V–, MUST BE SOLDERED TO PCB

Rev. B

2

For more information www.analog.com

�LTC6228/LTC6229

ORDER INFORMATION

LEAD FREE FINISH

TAPE AND REEL

PART MARKING

PACKAGE DESCRIPTION

TEMPERATURE RANGE

LTC6228IS6#TRMPBF

LTC6228IS6#TRPBF

LTHGB

6-Lead TSOT-23

–40°C to 85°C

LTC6228HS6#TRMPBF

LTC6228HS6#TRPBF

LTHGB

6-Lead TSOT-23

–40ºC to 125°C

LTC6228IDC#TRMPBF

LTC6228IDC#TRPBF

LHGC

6-Lead 2mm × 2mm DFN

–40°C to 85°C

LTC6228HDC#TRMPBF

LTC6228HDC#TRPBF

LHGC

6-Lead 2mm × 2mm DFN

–40ºC to 125°C

LTC6228IS8#TRMPBF

LTC6228IS8#TRPBF

6228

8-Lead SOIC-8

–40°C to 85°C

LTC6228HS8#TRMPBF

LTC6228HS8#TRPBF

6228

8-Lead SOIC-8

–40ºC to 125°C

LTC6229IMS8E#PBF

LTC6229IMS8E#TRPBF

LTGHD

8-Lead MSOP

–40ºC to 85°C

LTC6229HMS8E#PBF

LTC6229HMS8E#TRPBF

LTGHD

8-Lead MSOP

–40ºC to 125°C

LTC6229IDD#PBF

LTC6229IDD#TRPBF

LHGF

10-Lead 3mm × 3mm DFN

–40ºC to 85°C

LTC6229HDD#PBF

LTC6229HDD#TRPBF

LHGF

10-Lead 3mm × 3mm DFN

–40ºC to 125°C

Consult ADI Marketing for parts specified with wider operating temperature ranges.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

ELECTRICAL CHARACTERISTICS (V = ±5V)

The

l denotes the specifications which apply over the

S

full operating temperature range, otherwise specifications are at TA = 25°C. VS = ±5V,VCM = 0V, VSHDN = floating unless otherwise noted.

SYMBOL PARAMETER

VOS

∆VOS

CONDITIONS

MIN

TYP

MAX

UNITS

20

l

–95

–250

95

250

μV

μV

–140

–400

18

l

140

400

µV

µV

Input Offset Voltage

Input Offset Voltage Match (LTC6229)

TCVOS

Input Offset Voltage Drift

IB

Input Bias Current (Note 6)

l

Bias Cancellation Disabled

Input Bias Current Match (LTC6229)

Input Offset Current

–16

–2.5

–4.1

0.6

l

2.5

4.1

μA

μA

–2

–3

0.3

l

2

3

µA

µA

–3

–4

0.3

l

3

4

µA

µA

–0.55

–0.8

0.1

l

0.55

0.8

μA

μA

–0.9

–1

0.1

l

0.9

1

μA

μA

–1

–1.4

0.15

l

1

1.4

µA

µA

–1.3

–1.6

0.25

l

1.3

1.6

µA

µA

Bias Cancellation Disabled

Bias Cancellation Disabled

Bias Cancellation Enabled

∆IOS

Input Offset Current Match (LTC6229)

Bias Cancellation Disabled

Bias Cancellation Enabled

en

μA

μA

–40

–44

Bias Cancellation Enabled

IOS

μV/°C

l

Bias Cancellation Enabled

∆IB

0.4

Input Noise Voltage Spectral Density

f = 1MHz

0.88

nV/√Hz

Integrated 1/f Noise

0.1Hz to 10Hz

0.94

μVP-P

in

Input Current Noise Spectral Density

f = 1MHz Bias Cancellation Disabled

f = 1MHz Bias Cancellation Enabled

3

6.3

pA/√Hz

pA/√Hz

CIN

Input Capacitance

Differential Mode

Common Mode

3.5

1.5

pF

pF

RIN

Input Resistance

Differential Mode

Common Mode

2.6

4

kΩ

MΩ

Rev. B

For more information www.analog.com

3

�LTC6228/LTC6229

ELECTRICAL CHARACTERISTICS (V = ±5V)

The

l denotes the specifications which apply over the

S

full operating temperature range, otherwise specifications are at TA = 25°C. VS = ±5V,VCM = 0V, VSHDN = floating unless otherwise noted.

SYMBOL PARAMETER

AVOL

Large Signal Voltage Gain

CONDITIONS

MIN

TYP

RL = 1kΩ to Half Supply VOUT = ±4V

135

l

120

113

dB

dB

100

92

120

l

dB

dB

100

94

110

l

dB

dB

l

V– – 0.1

100

95

110

l

dB

dB

101

99

126

l

dB

dB

l

2.8

RL = 100Ω to Half Supply VOUT = ±3V

CMRR

VCMR

PSRR+

PSRR–

Common Mode Rejection Ratio

VCM = V– – 0.1 to V+ – 1.2V

Input Common Mode Range

Positive Power Supply Rejection Ratio

Negative Power Supply Rejection Ratio

V– = –1V, V+ = 1.8V to 10.75V

V+ = 1.5V, V– = –1.3V to –10.25V

Supply Voltage Range (V+ – V–) (Note 5)

VOL

Output Swing Low (VOUT – V–)

No Load

V+ – 1.2

11.75

8

16.9

19.8

mA

mA

500

l

610

770

μA

μA

l

V+ – 2.75

V

V+ – 1

V

ISINK = 25mA

140

l

No Load

27

l

ISINK = 5mA

90

l

ISOURCE = 25mA

250

l

Output Short-Circuit Current

Sourcing

–130

l

Sinking

l

IS

80

60

Supply Current per Channel

140

l

ISD

VL_SHDN

Disable Supply Current per Channel, Amplifier

Off

VSHDN = V+ – 2.75V

SHDN Pin Input Voltage Low, Disable Amplifier

V+ – 1.6

VH_SHDN

SHDN Pin Input Voltage High, Enable Amplifier

l

VL_IBIAS

SHDN Pin Input Voltage Low, Disable Bias

Cancellation

l

VH_IBIAS

SHDN Pin Input Voltage Low, Enable Bias

Cancellation

l

V+ – 0.35

IL_SHDN

SHDN Pin Input Current, Disable Amplifier

l

–10

VSHDN = V+ – 2.75V

= V+ – 1.6V

V

16

46

l

ISC

V

mV

mV

mV

mV

mV

mV

mV

mV

mV

mV

mV

mV

mA

mA

mA

mA

l

Output Swing High (V+ – VOUT)

UNITS

16

20

70

85

220

280

50

60

140

180

340

450

–80

–65

ISINK = 5mA

VOH

MAX

V

V

–2.5

10

μA

IH_SHDN

SHDN Pin Input Current, Enable Amplifier

VSHDN

l

–10

–0.3

10

μA

IL_IBIAS

SHDN Pin Input Current Low, Disable Bias

Cancellation

VSHDN = V+ – 1V

l

–10

0.265

10

μA

IH_IBIAS

SHDN Pin Input Current Low, Enable Bias

Cancellation

VSHDN = V+ – 0.35V

l

–10

1

10

μA

IOSD

Output Leakage Current in Shutdown

VSHDN = V+ – 2.75V, OUT Shorted to V+ or V–

BW

–3dB Closed Loop Bandwidth

AV = 1, RL = 1kΩ to Half Supply

GBW

Gain-Bandwidth Product

f = 5MHz, RL = 1kΩ to Half Supply

100

l

tON

Turn-On Time

VSHDN

= V+ – 2.75V to V+ – 1.6V

700

650

nA

730

MHz

890

MHz

MHz

900

ns

Rev. B

4

For more information www.analog.com

�LTC6228/LTC6229

ELECTRICAL CHARACTERISTICS (V = ±5V)

The

l denotes the specifications which apply over the

S

full operating temperature range, otherwise specifications are at TA = 25°C. VS = ±5V,VCM = 0V, VSHDN = floating unless otherwise noted.

SYMBOL PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

tOFF

Turn-Off Time

VSHDN = V+ – 1.6V to V+ – 2.75V

500

ns

tS_0.1

Settling Time to 0.1%

AV = 1, 2V Output Step, RL = 1kΩ

26

ns

AV = 1, 4V Output Step, RL = 1kΩ

34

ns

tS_0.01

Settling Time to 0.01%

AV = 1, 6V Output Step, RL = 1kΩ

SR

Slew Rate

AV = +4, 8V Output Step (Note 8)

FPBW

Full Power Bandwidth

VOUT = 8VP-P, AV = +2, THD < –40dBc

l

320

250

HD2/HD3 Harmonic Distortion, RL = 1kΩ to Half Supply, fC = 100kHz, VO = 4VP-P

AV = +1

fC = 100kHz, VO = 2VP-P

fC = 1MHz, VO = 4VP-P

fC = 1MHz, VO = 2VP-P

fC = 5MHz, VO = 4VP-P

fC = 5MHz, VO = 2VP-P

fC = 10MHz, VO = 2VP-P

53

ns

500

V/μs

V/μs

12.5

MHz

–113/–119

–126/–131

–107/–114

–119/–132

–83/–96

–90/–113

–74/–89

dBc

dBc

dBc

dBc

dBc

dBc

dBc

–105/–106

–118/–124

–97/–107

–100/–114

–79/–75

–83/–82

–72/–68

dBc

dBc

dBc

dBc

dBc

dBc

dBc

Harmonic Distortion, RL = 100Ω to Half

Supply, AV = +1

fC = 100kHz, VO = 4VP-P

fC = 100kHz, VO = 4VP-P

fC = 1MHz, VO = 4VP-P

fC = 1MHz, VO = 2VP-P

fC = 5MHz, VO = 4VP-P

fC = 5MHz, VO = 2VP-P

fC = 10MHz, VO = 2VP-P

ΔG

Differential Gain (NTSC)

AV = 2, RL = 150Ω

AV = +1, RL = 1kΩ

0.008

0.001

%

%

Δθ

Differential Phase (NTSC)

AV = 2, RL = 150Ω

AV = +1, RL = 1kΩ

0.004

0.09

Deg

Deg

ELECTRICAL

CHARACTERISTICS (VS = 5V, 0V)

The

l denotes the specifications which apply

over the full operating temperature range, otherwise specifications are at TA = 25°C. VS = 5V, 0V,VCM = VOUT = 2.5V, VSHDN = floating

unless otherwise noted.

SYMBOL PARAMETER

VOS

∆VOS

CONDITIONS

MIN

TYP

MAX

UNITS

20

l

–105

–290

105

290

μV

μV

–140

–400

18

l

140

400

µV

µV

Input Offset Voltage

Input Offset Voltage Match (LTC6229)

TCVOS

Input Offset Voltage Drift

IB

Input Bias Current (Note 6)

l

Bias Cancellation Disabled

l

Bias Cancellation Enabled

l

∆IB

Input Bias Current Match (LTC6229)

Bias Cancellation Disabled

l

Bias Cancellation Enabled

l

IOS

Input Offset Current

Bias Cancellation Disabled

l

Bias Cancellation Enabled

l

∆IOS

Input Offset Current Match (LTC6229)

Bias Cancellation Disabled

l

Bias Cancellation Enabled

l

–40

–44

–3

–4.4

–2

–3

–3

–4

–0.55

–0.8

–0.9

–1

–1

–1.4

–1.3

–1.6

0.4

μV/°C

–16

μA

μA

μA

μA

µA

µA

µA

µA

μA

μA

μA

μA

µA

µA

µA

µA

1

0.3

0.3

0.1

0.15

0.15

0.25

3

4.4

2

3

3

4

0.55

0.8

0.9

1

1

1.4

1.3

1.6

Rev. B

For more information www.analog.com

5

�LTC6228/LTC6229

ELECTRICAL

CHARACTERISTICS (VS = 5V, 0V)

The

l denotes the specifications which apply

over the full operating temperature range, otherwise specifications are at TA = 25°C. VS = 5V, 0V,VCM = VOUT = 2.5V, VSHDN = floating

unless otherwise noted.

SYMBOL PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

Input Noise Voltage Spectral Density

f = 1MHz

0.88

nV/√Hz

Integrated 1/f Noise

0.1Hz to 10Hz

0.94

μVP-P

in

Input Current Noise Spectral Density

f = 1MHz Bias Cancellation Disabled

f = 1MHz Bias Cancellation Enabled

3

6.3

pA/√Hz

pA/√Hz

CIN

Input Capacitance

Differential Mode

Common Mode

3.5

1.5

pF

pF

RIN

Input Resistance

Differential Mode

Common Mode

2.6

4

kΩ

MΩ

AVOL

Large Signal Voltage Gain

RL = 1kΩ to Half Supply, VOUT = VCM ±2

en

120

115

140

l

dB

dB

106

100

120

l

dB

dB

97

92

110

l

dB

dB

l

V– – 0.1

110

l

100

95

dB

dB

103

100

126

l

dB

dB

l

2.8

RL = 100Ω to Half Supply, VOUT = VCM ±2

CMRR

Common Mode Rejection Ratio

VCM = V– – 0.1 to V+ – 1.2V

VCMR

Input Common Mode Range

PSRR+

Positive Power Supply Rejection Ratio

V– = –1V, V+ = 1.8V to 10.75V

PSRR–

Negative Power Supply Rejection Ratio

V+ = 1.5V, V– = –1.3V to –10.25V

Supply Voltage Range (V+ – V–) (Note 5)

VOL

Output Swing Low (VOUT

– V–)

No Load

V+ – 1.2

11.75

18

32

mV

mV

40

70

90

mV

mV

150

220

300

mV

mV

26

48

58

mV

mV

93

144

185

mV

mV

255

347

459

mV

mV

–110

–65

–52

mA

mA

l

ISINK = 25mA

l

VOH

Output Swing High (VCC – V+)

No Load

l

ISINK = 5mA

l

ISOURCE = 25mA

l

ISC

Output Short-Circuit Current

Sourcing

l

Sinking

l

IS

70

45

Supply Current per Channel

110

VL_SHDN

Disable Supply Current per Channel, Amplifier

Off

VSHDN = V+ – 2.65V

17.8

19.6

mA

mA

300

380

430

μA

μA

V+ – 2.65

V

V+ – 1

V

l

SHDN Pin Input Voltage Low, Disable Amplifier

l

V+ – 1.6

VH_SHDN

SHDN Pin Input Voltage High, Enable Amplifier

l

VL_IBIAS

SHDN Pin Input Voltage Low, Disable Bias

Cancellation

l

VH_IBIAS

SHDN Pin Input Voltage Low, Enable Bias

Cancellation

l

V+ – 0.35

IL_SHDN

SHDN Pin Input Current, Disable Amplifier

l

–10

VSHDN = V+ – 2.65V

mA

mA

16.5

l

ISD

V

7

l

ISINK = 5mA

V

V

V

–2.5

10

μA

Rev. B

6

For more information www.analog.com

�LTC6228/LTC6229

ELECTRICAL

CHARACTERISTICS (VS = 5V, 0V)

The

l denotes the specifications which apply

over the full operating temperature range, otherwise specifications are at TA = 25°C. VS = 5V, 0V,VCM = VOUT = 2.5V, VSHDN = floating

unless otherwise noted.

SYMBOL PARAMETER

IH_SHDN

SHDN Pin Input Current, Enable Amplifier

CONDITIONS

VSHDN = V+ – 1.6V

= V+ – 1V

MIN

TYP

MAX

l

–10

–0.3

10

UNITS

μA

l

–10

0.265

10

μA

l

–10

1

10

μA

IL_IBIAS

SHDN Pin Input Current Low, Disable Bias

Cancellation

VSHDN

IH_IBIAS

SHDN Pin Input Current Low, Enable Bias

Cancellation

VSHDN = V+ – 0.35V

IOSD

Output Leakage Current in Shutdown

VSHDN = V+ – 2.65V, OUT Shorted to V+ or V–

100

nA

BW

–3dB Closed Loop Bandwidth

AV = 1, RL = 1kΩ to Half Supply

800

MHz

GBW

Gain-Bandwidth Product

f = 5MHz, RL = 1kΩ to Half Supply

865

MHz

MHz

l

700

600

tON

Turn-On Time

VSHDN = V+ – 2.65V to V+ – 1.6V

900

ns

tOFF

Turn-Off Time

VSHDN = V+ – 1.6V to V+ – 2.65V

500

ns

tS_0.1

Settling Time to 0.1%

AV = 1, 2V Output Step, RL = 1kΩ

26

ns

SR

Slew Rate

AV = +4, 4V Output Step (Note 8)

350

V/μs

FPBW

Full Power Bandwidth

18

MHz

fC = 100kHz, VO = 2VP-P

fC = 1MHz, VO = 2VP-P

fC = 5MHz, VO = 2VP-P

fC = 10MHz, VO = 2VP-P

–106/–130

–95/–105

–88/–114

–78/–90

dBc

dBc

dBc

dBc

Harmonic Distortion, RL = 100Ω to Half

Supply

fC = 100kHz, VO = 2VP-P

fC = 1MHz, VO = 2VP-P

fC = 5MHz, VO = 2VP-P

fC = 10MHz, VO = 2VP-P

–112/–115

–99/–120

–83/–88

–70/–73

dBc

dBc

dBc

dBc

ΔG

Differential Gain (NTSC)

AV = 2, RL = 150Ω

AV = +1, RL = 1kΩ

0.005

0.002

%

%

Δθ

Differential Phase (NTSC)

AV = 2, RL = 150Ω

AV = +1, RL = 1kΩ

0.007

0.018

Deg

Deg

HD2/HD3 Harmonic Distortion, RL = 1kΩ to Half Supply

VOUT = 4VP-P, AV = +2, THD < –40dBc

ELECTRICAL

CHARACTERISTICS (VS = 3V, 0V)

The

l denotes the specifications which apply

over the full operating temperature range, otherwise specifications are at TA = 25°C. VS = 3V, 0V,VCM = 1.5V, VSHDN = floating unless

otherwise noted.

SYMBOL PARAMETER

VOS

∆VOS

CONDITIONS

MIN

TYP

MAX

UNITS

24

l

–110

–300

110

300

μV

μV

–140

–400

18

l

140

400

µV

µV

0.4

μV/°C

–16

l

–38

–44

μA

μA

–3.5

–4.3

1.5

l

3.5

4.1

μA

μA

–2

–3

0.3

l

2

3

µA

µA

–3

–4

0.3

l

3

4

µA

µA

Input Offset Voltage

Input Offset Voltage Match (LTC6229)

TCVOS

Input Offset Voltage Drift

IB

Input Bias Current (Note 6)

l

Bias Cancellation Disabled

Bias Cancellation Enabled

∆IB

Input Bias Current Match (LTC6229)

Bias Cancellation Disabled

Bias Cancellation Enabled

Rev. B

For more information www.analog.com

7

�LTC6228/LTC6229

ELECTRICAL

CHARACTERISTICS (VS = 3V, 0V)

The

l denotes the specifications which apply

over the full operating temperature range, otherwise specifications are at TA = 25°C. VS = 3V, 0V,VCM = 1.5V, VSHDN = floating unless

otherwise noted.

SYMBOL PARAMETER

IOS

CONDITIONS

Input Offset Current

MIN

TYP

MAX

UNITS

–0.55

–0.8

0.1

l

0.55

0.8

μA

μA

–0.9

–1

0.15

l

0.9

1

μA

μA

–1

–1.4

0.15

l

1

1.4

µA

µA

–1.3

–1.6

0.25

l

1.3

1.6

µA

µA

Bias Cancellation Disabled

Bias Cancellation Enabled

∆IOS

Input Offset Current Match (LTC6229)

Bias Cancellation Disabled

Bias Cancellation Enabled

en

Input Noise Voltage Spectral Density

f = 1MHz

0.88

nV/√Hz

Integrated 1/f Noise

0.1Hz to 10Hz

0.94

μVP-P

in

Input Current Noise Spectral Density

f = 1MHz Bias Cancellation Disabled

f = 1MHz Bias Cancellation Enabled

3

6.3

pA/√Hz

pA/√Hz

CIN

Input Capacitance

Differential Mode

Common Mode

3.5

1.5

pF

pF

RIN

Input Resistance

Differential Mode

Common Mode

2.6

4

kΩ

MΩ

AVOL

Large Signal Voltage Gain

RL = 1kΩ to Half Supply,

(VOUT = VCM ±1V)

130

dB

dB

120

dB

110

dB

dB

l

118

113

RL = 100Ω to Half Supply,

(VOUT = VCM ±1V)

CMRR

VCMR

PSRR+

PSRR–

Common Mode Rejection Ratio

VCM = V– to V+ – 1.2V

Input Common Mode Range

Positive Power Supply Rejection Ratio

Negative Power Supply Rejection Ratio

VOL

Output Swing Low (VOUT

95

91

l

V– – 0.1

100

95

110

l

dB

dB

101

99

126

l

dB

dB

l

2.8

V– = –1V, V+ = 1.8V to 10.75V

V+ = 1.5V, V– = –1.3V to –10.25V

Supply Voltage Range (V+ – V–) (Note 5)

– V–)

l

No Load

V+ – 1.2

11.75

10

18

mV

mV

48

74

100

mV

mV

165

320

430

mV

mV

27

49

59

mV

mV

106

166

213

mV

mV

290

520

580

mV

mV

l

ISINK = 25mA

l

VOH

Output Swing High (VCC – V+)

No Load

l

ISINK = 5mA

l

ISOURCE = 25mA

l

ISC

Output Short-Circuit Current

IS

Supply Current per Channel

Sourcing

–67

Sinking

Disable Supply Current per Channel, Amplifier

Off

mA

84

VSHDN = V+ – 2.65V

l

mA

16.4

17.6

19

mA

mA

260

305

350

μA

μA

l

ISD

V

7

l

ISINK = 5mA

V

Rev. B

8

For more information www.analog.com

�LTC6228/LTC6229

ELECTRICAL

CHARACTERISTICS (VS = 3V, 0V)

The

l denotes the specifications which apply

over the full operating temperature range, otherwise specifications are at TA = 25°C. VS = 3V, 0V,VCM = 1.5V, VSHDN = floating unless

otherwise noted.

SYMBOL PARAMETER

CONDITIONS

MIN

VL_SHDN

SHDN Pin Input Voltage Low, Disable Amplifier

l

VH_SHDN

SHDN Pin Input Voltage High, Enable Amplifier

l

V+ – 1.6

l

VH_IBIAS

SHDN Pin Input Voltage Low, Enable Bias

Cancellation

l

V+ – 0.35

IL_SHDN

SHDN Pin Input Current, Disable Amplifier

l

–10

UNITS

V

V

V+ – 1

SHDN Pin Input Voltage Low, Disable Bias

Cancellation

= V+ – 1.6V

MAX

V+ – 2.65

VL_IBIAS

VSHDN = V+ – 2.65V

TYP

V

V

–2.5

10

μA

IH_SHDN

SHDN Pin Input Current, Enable Amplifier

VSHDN

l

–10

–0.3

10

μA

IL_IBIAS

SHDN Pin Input Current Low, Disable Bias

Cancellation

VSHDN = V+ – 1V

l

–10

0.265

10

μA

IH_IBIAS

SHDN Pin Input Current Low, Enable Bias

Cancellation

VSHDN = V+ – 0.35V

l

–10

1

10

μA

IOSD

Output Leakage Current in Shutdown

VSHDN = V+ – 2.65V, OUT Shorted to V+ or V–

100

nA

BW

–3dB Closed Loop Bandwidth

AV = 1, RL = 1kΩ to Half Supply

763

MHz

GBW

Gain-Bandwidth Product

f = 5MHz, RL = 1kΩ to Half Supply

845

MHz

MHz

ns

l

700

560

Turn-On Time

VSHDN = V+ – 2.65V to V+ – 1.6V

900

tOFF

Turn-Off Time

VSHDN

= V+ – 1.6V to V+ – 2.65V

500

ns

tS_0.1

Settling Time to 0.1%

AV = 1, VCM = 1V, 1V Output Step,

RL = 1kΩ

31

ns

SR

Slew Rate

AV = +4, 2V Output Step

200

V/μs

FPBW

Full Power Bandwidth

VOUT = 2VP-P, VCM = 1V, AV = –1,

THD < –40dBc

22

MHz

fC = 100kHz

fC = 1MHz

fC = 5MHz

fC = 10MHz

–106/–127

–110/–128

–82/–105

–77/–96

dBc

dBc

dBc

dBc

fC = 100kHz

fC = 1MHz

fC = 5MHz

fC = 10MHz

–116/–123

–105/–132

–89/–98

–77/–86

dBc

dBc

dBc

dBc

tON

HD2/HD3 Harmonic Distortion, RL = 1kΩ to VCM,

VOUT = 1VP-P, VCM = 1.25V

Harmonic Distortion, RL = 100Ω to VCM,

VOUT = 1VP-P, VCM = 1.25V

Note 1: Stresses beyond those listed under Absolute Maximum Ratings

may cause permanent damage to the device. Exposure to any Absolute

Maximum Rating condition for extended periods may affect device

reliability and lifetime.

Note 2: The inputs are protected by back-to-back diodes. If any of

the input or shutdown pins goes 300mV beyond either supply or the

differential input voltage exceeds 0.7V, the input current should be limited

to less than 10mA.

Note 3: A heat sink may be required to keep the junction temperature

below the absolute maximum rating when the output current is high.

Note 4: The LTC6228I/LTC6229I is guaranteed functional and specified

over the temperature range of –40°C to 85°C. The LTC6228H/LTC6229H is

guaranteed functional and specified over the temperature range of –40°C

to 125°C.

Note 5: Supply range voltage is guaranteed by power supply rejection ratio test.

Note 6: The input bias current is the average of the currents through the

non-inverting and inverting input pins.

Note 7: Thermal resistance varies with the amount of PC board metal

connected to the package. The specified values are with short traces

connected to the leads with minimal metal area.

Note 8: Middle 2/3 of the output waveform is observed. RL = 1kΩ at half supply.

Rev. B

For more information www.analog.com

9

�LTC6228/LTC6229

TYPICAL

PERFORMANCE CHARACTERISTICS S = ±5V, VCM = 0V, TA = 25°C, unless otherwise noted.

V

Offset Distribution

VS = ±5V

VCM = 0V

TA = 25°C

45

40

35

30

25

20

15

35

30

25

20

15

40

35

30

25

20

15

10

10

5

5

5

0

–60–50–40–30–20–10 0 10 20 30 40 50 60

INPUT OFFSET VOLTAGE (µV)

0

–60–50–40–30–20–10 0 10 20 30 40 50 60

INPUT OFFSET VOLTAGE (µV)

0

–60–50–40–30–20–10 0 10 20 30 40 50 60

INPUT OFFSET VOLTAGE (µV)

VOS vs Temperature, 5V Supply

VS = ±2.5V

VCM = 0V

5 DEVICES

INPUT OFFSET VOLTAGE (µV)

140

120

100

80

60

40

20

120

100

80

60

40

100

80

60

40

0

–55 –35 –15

5 25 45 65 85 105 125

TEMPERATURE (°C)

6228 G04

6228 G06

Offset Voltage vs Output Current

VS = ±5V

180

VS = ±5V

OFFSET VOLTAGE (µV)

160

TA = 85°C

TA = –55°C

140

120

100

TA = 125°C

80

60

TA = 85°C

40

20

TA = 25°C

5

Warm

Up Drift

Warm–up

Drift vs

vs Time

Time

50

TA = –55°C

CHANGE IN OFFSET VOLTAGE (µV)

200

TA = 125°C

5 25 45 65 85 105 125

TEMPERATURE (°C)

6228 G05

Offset Voltage vs Input Common

Mode Voltage

–6 –5 –4 –3 –2 –1 0 1 2 3 4

INPUT COMMON MODE VOLTAGE (V)

120

20

0

–55 –35 –15

5 25 45 65 85 105 125

TEMPERATURE (°C)

VS = 3V, 0V

VCM = 1.5V

5 DEVICES

140

20

0

–55 –35 –15

100

90

80

70

60

50

40

30

20

10

0

–10

–20

–30

–40

VOS vs Temperature, 3V Supply

160

INPUT OFFSET VOLTAGE (µV)

160

VS = ±5V

VCM = 0V

5 DEVICES

140

6228 G03

6228 G02

VOS vs Temperature, 10V Supply

160

OFFSET VOLTAGE (µV)

VS = 3V, 0V

VCM = 1.5V

TA = 25°C

45

10

6228 G01

INPUT OFFSET VOLTAGE (µV)

Offset Distribution

50

VS = 5V, 0V

VCM = 2.5V

TA = 25°C

45

PERCENT OF UNITS (%)

40

PERCENT OF UNITS (%)

Offset Distribution

50

PERCENT OF UNITS (%)

50

VS = ±5V

TA=25°C

40

30

20

10

0

TA = 25°C

0

–50 –40 –30 –20 –10 0 10 20 30 40 50

OUTPUT CURRENT (mA)

6228 G07

6228 G08

–10

0

1

2

3

4

5

6

TIME AFTER POWER UP (s)

7

8

6228 G09

Rev. B

10

For more information www.analog.com

�LTC6228/LTC6229

TYPICAL PERFORMANCE CHARACTERISTICS

VS = ±5V, VCM = 0V, TA = 25°C, unless otherwise noted.

2

VS = ±5V

TA = 125°C

0

INPUT BIAS CURRENT (µA)

INPUT BIAS CURRENT (µA)

VS = ±5V

1

0

0.1Hz to 10Hz Voltage Noise

–5

TA = 25°C

–10

TA = –55°C

–15

–20

TA = 125°C

TA = –55°C

–2

–3

TA = 25°C

–4

TA = 85°C

–5

–6

–7

–8

TA = 85°C

–25

–1

–9

–30

–5.1 –4.2 –3.3 –2.4 –1.5 –0.7 0.2 1.1 2.0 2.9 3.8

INPUT COMMON MODE VOLTAGE (V)

–10

–5.1 –4.2 –3.3 –2.4 –1.5 –0.7 0.2 1.1 2.0 2.9 3.8

INPUT COMMON MODE VOLTAGE (V)

6228 G10

6228 G11

Input

and

Current

Noise

InputVoltage

VoltageNoise

Noise

and

Current

Noise

Spectral Densities

Spectral

DensitiesvsvsFrequency

Frequency

iN,bias cancellation disabled

1k

20

20

VS = ±5V

TA=25°C

iN,bias cancellation enabled

100

eN

10

18

TA = 25°C

14

TA = –55°C

12

10

8

6

2

0

10 100 1k 10k 100k 1M 10M100M

FREQUENCY (Hz)

0

2

5.0

INPUT BIAS CURRENT (µA)

TA = 25°C

10

TA = –55°C

6

4

2

0

6228 G15

4

5

6228 G16

SHDN Pin Current vs SHDN Pin

Voltage

SHDN Pin Voltage

5.0

0

–5.0

–7.5

–10.0

–12.5

–15.0

–20.0

3.4

TA = –55°C

TA = 25°C

TA = 85°C

3.8 4 4.2 4.4 4.6

SHDN PIN VOLTAGE (V)

0

–2.5

–5.0

–7.5

4.8

5.0

6228 G17

TA = –55°C

–10.0

TA = 25°C

–12.5

–15.0

–17.5

TA = 125°C

3.6

VS = ±5V

2.5

–2.5

–17.5

–5 –4 –3 –2 –1 0 1 2 3

SHDN PIN VOLTAGE (V)

TA = –55°C

13

10

–5.1 –4.2 –3.3 –2.4 –1.5 –0.6 0.3 1.2 2.1 3.0 3.9

INPUT COMMON MODE VOLTAGE (V)

12

VS = ±5V

2.5

TA = 125°C

12

8

14

Input Bias Current vs SHDN Pin

Voltage

SHDN Pin Voltage

16

14

4

6

8

10

TOTAL SUPPLY VOLTAGE (V)

SHDN PIN CURRENT (µA)

VS = ±5V

15

6228 G14

Supply Current vs SHDN Pin

Voltage

18

TA = 25°C

16

11

VCM = VS/2

6228 G13

20

17

12

4

1

TA = 125°C

19

TA = 125°C

18

16

1

0.5

0.1

SUPPLY CURRENT (mA)

Supply Current vs Input Common

Mode Voltage

Supply Current vs Supply Voltage

SUPPLY CURRENT (mA)

INPUT VOLTAGE NOISE (nV/√Hz)

INPUT CURRENT NOISE (pA/√Hz)

5k

6228 G12

1s/DIV

SUPPLY CURRENT (mA)

5

Input Bias Current vs Input

Common Mode Voltage, Bias

Cancellation Enabled

INPUT VOLTAGE NOISE (200 nV/Div)

Input Bias Current vs Input

Common Voltage, Bias

Cancellation Disabled

–20.0

TA = 125°C

–5 –4 –3 –2 –1 0 1 2 3

SHDN PIN VOLTAGE (V)

4

5

6228 G18

Rev. B

For more information www.analog.com

11

�LTC6228/LTC6229

TYPICAL PERFORMANCE CHARACTERISTICS

VS = ±5V, VCM = 0V, TA = 25°C, unless otherwise noted.

Output Saturation Voltage vs

Load Current (Output High)

VCM = 1V

INPUT OFFSET VOLTAGE (µV)

160

120

TA = 125°C

80

40

TA = 25°C

0

TA = –55°C

–40

–80

–120

–160

–200

2

1

OUTPUT HIGH SATURATION VOLTAGE (V)

200

1

VS = ±5V

TA = 125°C

TA = 25°C

0.1

TA = –55°C

0.01

0.001

2.2 2.4 2.6 2.8 3.0 3.2 3.4 3.6 3.8 4.0

TOTAL SUPPLY VOLTAGE (V)

0.01

0.1

1

10

LOAD CURRENT (mA)

6228 G19

250

40

TA = 25°C

130

TA = 85°C

90

TA = 125°C

50

10

TA = 85°C

–30

TA = 125°C

–70

TA = 25°C

–110 SOURCE

TA = –55°C

–150

2.8 3.7 4.6 5.5 6.4 7.3 8.2 9.1 10.0 10.9 11.8

TOTAL SUPPLY VOLTAGE (V)

0

–8

–16

–24

–40

4

5

–40

–1.5

–1

–0.5

0

0.5

OUTPUT VOLTAGE (V)

1

1.5

24

16

8

0

–8

–16

–24

9

2

2.5

Gain vs Frequency, AV = 2

6

3

0

–4

–6

–10

TA = 25°C

RL = 1kΩ

RL = 100Ω

6228 G24

Gain vs Frequency, AV = 1

–2

–8

–24

–32

–5 –4 –3 –2 –1 0 1 2 3

OUTPUT VOLTAGE (V)

GAIN (dB)

GAIN (dB)

INPUT OFFSET VOLTAGE (µV)

–16

Open Loop Gain, VS = ±2.5V

TA = 25°C

–40

–2.5 –2 –1.5 –1 –0.5 0 0.5 1 1.5

OUTPUT VOLTAGE (V)

0

16

100

–32

TA = 25°C

2

24

–8

0.1

1

10

LOAD CURRENT (mA)

6228 G23

RL = 1kΩ

RL = 100Ω

0

0.01

32

8

4

8

TA = –55°C

6228 G21

RL = 1kΩ

RL = 100Ω

16

–32

Open Loop Gain, VS = ±1.5V

32

TA = 25°C

0.1

40

24

6228 G22

40

100

INPUT OFFSET VOLTAGE (µV)

170

TA = 125°C

0.01

0.001

Open Loop Gain, VS = ±5V

32

INPUT OFFSET VOLTAGE (µV)

SHORT CIRCUIT CURRENT (mA)

TA = –55°C

SINK

VS = ±5V

6228 G20

Output Short Circuit vs Supply

vs

Supply Voltage

Voltage

210

Output Saturation Voltage vs

Load Current (Output Low)

OUTPUT LOW SATURATION VOLTAGE (V)

Minimum Supply Voltage

–3

–6

–9

–12

–15

VS = ±5V

RL = 1kΩ

TA = 25°C

–12

10k

100k

–18

–21

1M

10M

100M

FREQUENCY (Hz)

6228 G25

1G

6228 G26

VS = ±5V

TA = 25°C

RF = RG = 301Ω C F = 2.7pF

RL = 1kΩ

–24

10k

100k

1M

10M

100M

FREQUENCY (Hz)

1G

6228 G27

Rev. B

12

For more information www.analog.com

�LTC6228/LTC6229

TYPICAL PERFORMANCE CHARACTERISTICS

VS = ±5V, VCM = 0V, TA = 25°C, unless otherwise noted.

Gain Bandwidth and Phase

Margin vs Supply Voltage

VS = ±5V

TA = 25 °C

RL = 1kΩ

920

60

1000

910

59

970

900

57

PHASE MARGIN

890

880

54

870

53

GAIN BANDWIDTH

PRODUCT

860

850

840

820

2.80

1G

51

50

VCM = HALF SUPPLY

RL = 1kΩ TO HALF SUPPLY

TA = 25 °C

830

10M

100M

FREQUENCY (Hz)

56

AV = 2

AV = 1

0.1

0.01

10k

100k

1M

10M

FREQUENCY (Hz)

100M

90

60

50

40

400

300

200

RISING

FALLING

VS = ±2.5V, VOUT = 4VP-P

VS = ±1.5V, VOUT = 2VP-P

RISING

FALLING

100

–55 –35 –15

5 25 45 65 85 105 125

TEMPERATURE (°C)

SLEW RATE MEASURED AT

MIDDLE 2/3 OF OUTPUT

760

VS = ±5V

VS = ±2.5V

VS = ±1.5V

730

25

GAIN

BANDWIDTH

20

15

10

5 25 45 65 85 105 125

TEMPERATURE (°C)

Power Supply Rejection Ratio vs

Frequency

PSRR+

PSRR–

70

50

20

VS = ±5V

VCM = 0V

TA = 25°C

10

10

1M

10M

FREQUENCY (Hz)

100M

–10

100

500M

1k

10k 100k 1M 10M 100M

FREQUENCY (Hz)

6228 G33

Series Output Resistor vs

Capacitive Load, AV = 1

55

50

VS = ±5V

45

OVERSHOOT (%)

SLEW RATE (V/µS)

500

30

RL = 1kΩ

790

6228 G32

VS = ±5V, VOUT = 8VP-P

RISING

35

820

30

30

0

100k

1G

AV = 4, R L=1kΩ

600

40

850

90

70

Slew Rate vs Temperature

FALLING

45

880

110

80

6228 G31

700

910

130

VS = ±5V

TA = 25°C

VIN

40

–

+

Series Output Resistor vs

Capacitive Load, AV = 2

150

VOUT

135

RS

35

30

RS = 20Ω

25

20

RS = 10Ω

RS = 50Ω

90

6228 G35

6228 G34

–

+

VOUT RS

1kΩ CL

45

15

10000

C1 301Ω

60

30

100

1000

CAPACITIVE LOAD (pF)

VIN

75

10

10

301Ω

105

15

5

VS = ±5V

120

1kΩ CL

OVERSHOOT (%)

AV = 10

1

50

6228 G30

Common Mode Rejection Ratio vs

Frequency

100

55

940

700

–55 –35 –15

PSRR (dB)

COMMON MODE REJECTION RATIO (dB)

OUTPUT IMPEDANCE (Ω)

110

10

60

PHASE MARGIN

6228 G29

Output Impedance vs Frequency

VS = ±5 V

47

45

4.29 5.78 7.27 8.77 10.26 11.75

TOTAL SUPPLY VOLTAGE (V)

6228 G28

80

48

GAIN BANDWIDTH PRODUCT (MHz)

GAIN BANDWIDTH (MHz)

Gain

Phase

PHASE MARGIN (°)

70

65

60

55

50

45

40

35

30

25

20

15

10

5

0

–5

500k 1M

Gain Bandwidth and Phase

Margin vs Temperature

PHASE MARGIN (°)

GAIN (dB)

PHASE (°)

Open Loop Gain

Gain and

and Phase

Phase vs

vs Frequency

Frequency

0

10

100

1000

CAPACITIVE LOAD (pF)

RS = 10Ω, CF = 0pF

RS = 20Ω, CF = 0pF

RS = 50Ω, CF = 0pF

10000

RS = 10Ω, CF = 2.7pF

RS = 20Ω, CF = 2.7pF

RS = 50Ω, CF = 2.7pF

6228 G36

Rev. B

For more information www.analog.com

13

�LTC6228/LTC6229

TYPICAL PERFORMANCE CHARACTERISTICS

VS = ±5V, VCM = 0V, TA = 25°C, unless otherwise noted.

Distortion vs

vs Frequency,

Frequency, AAVV == 11,

Distortion

±5V Supply

Supply

–30

–50

–70 VOUT = 4VP–Pnd

RL = 100Ω, 2

–80

VOUT = 4VP–P

–90 R = 100Ω, 3rd

L

–100

–60

RL = 100Ω, 2nd

–70

–80 RL = 1kΩ, 2nd

–90

–100

–120

VOUT = 2VP–P

RL = 1kΩ, 3rd

1M

FREQUENCY (Hz)

–130

100k

10M

1M

FREQUENCY (Hz)

–50

–100

VOUT = 2VP–P

RL = 1kΩ, 2nd

VOUT = 2VP–P

RL = 1kΩ, 3rd

–120

–130

100k

1M

FREQUENCY (Hz)

–60

–80

–90

–100

–110

RL = 1kΩ, 3rd

–120

RL = 100Ω, 3rd

VS = ±5V

50

AV = –1

45

8

7

6

VS = ±2.5V

5

AV = –1

4

VS = ±1.5V

3

2

1

AV = 2

TA = 25°C

RL = 1kΩ

HD2, HD3 < –40dBc

0

0.1

AV = –1

1

10

FREQUENCY (MHz)

1M

FREQUENCY (Hz)

10M

40

35

VIN

–

+

VOUT

1kΩ

30

6228 G43

20

–20

–30

–40

–50

VS = 3V, 0V

VCM = 1V

VOUT = 1VP-P

RL to VCM

TA = 25°C

–60

RL = 100Ω, 2ND

–70

–80

RL = 1kΩ, 2ND

–90

–100

RL = 100Ω, 3RD

–110

–120

RL = 1kΩ, 3RD

–130

100k

1M

10M

FREQUENCY (Hz)

6228 G44

50M

6228 G42

0.1% Settling Time vs Output

Step

(Inverting)

vs Output

Step (Inverting)

50

2.7pF

45

301Ω

VIN

301Ω

40

–

+

VOUT

1kΩ

35

30

25

–8 –7 –6 –5 –4 –3 –2 –1 0 1 2 3 4 5 6 7 8

OUTPUT STEP (V)

50M

Distortion vs Frequency, AV = 2,

3V Supply

Av = +1

TA=25°C

VS=±5V (5.5V/–4.5V for step size>7V)

25

40

1M

10M

FREQUENCY (Hz)

6228 G39

0.1% Settling Time vs Output

Step

(Non-Inverting)

vs

Output

Step (Non–inverting)

SETTLING TIME (ns)

OUTPUT VOLTAGE SWING (VP-P)

AV = 2

RL = 100Ω, 3rd

–130

100k

6228 G41

Maximum Undistorted Output

Signal vs Frequency

9

RL = 1kΩ, 2nd

–130

100k

10M

RL = 1kΩ, 3rd

–110

10M

–70

6228 G40

10

–90

–120

VS = 5V,0V

VOUT=2VP–P

RL to Mid–Supply

TA=25°C

RL = 100Ω, 2nd

–40

DISTORTION (dBc)

DISTORTION (dBc)

–30

VS = ±5V

TA=25°C

–110

–70 RL = 1kΩ, 2nd

–80

Distortion

Distortion vs

vs Frequency,

Frequency, A

AVV == 2,

2

5V Supply

Supply

VOUT = 4VP–P

–50 VOUT = 4VP–P

RL = 1kΩ, 3rd RL =1kΩ, 2nd

–60

V

= 4VP–P

–70 ROUT

nd

L = 100Ω, 2

–80

VOUT = 4VP–P

–90 RL = 100Ω, 3rd

RL = 100Ω, 2nd

–60

6228 G38

Distortion vs Frequency, AV = 22,

±5V Supply

Supply

–40

–50

–100

RL = 100Ω, 3rd

6228 G37

–30

–40

DISTORTION (dBc)

–130

100k

–30

SETTLING TIME (ns)

–120

VS = 3V,0V

VOUT=1VP–P

VCM=1.25V

RL to VCM

TA=25°C

–20

RL = 1kΩ, 3rd

–110

–110

–10

VS = 5V,0V

VOUT=2VP–P

RL to Mid–Supply

TA=25°C

–40

VOUT = 2VP–P

RL = 1kΩ, 2nd

Distortion vs Frequency, AV = 11,

3V Supply

Supply

DISTORTION (dBc)

VS = ±5V

TA=25°C

–40 VOUT = 4VP–P

RL =1kΩ, 2nd

–50

VOUT = 4VP–P

rd

–60 RL = 1kΩ, 3

DISTORTION (dBc)

DISTORTION (dBc)

–30

Distortion vs

vs Frequency,

Frequency, AAVV == 11,

Distortion

5V Supply

5V

20

Av = –1

TA=25°C

VS=±5V

–8 –7 –6 –5 –4 –3 –2 –1 0 1 2 3 4 5 6 7 8

OUTPUT STEP (V)

6228 G45

Rev. B

14

For more information www.analog.com

�LTC6228/LTC6229

TYPICAL PERFORMANCE CHARACTERISTICS

VS = ±5V, VCM = 0V, TA = 25°C, unless otherwise noted.

SHDN Pin Response Time

Input

0V

500mV/DIV

Output

0V

500mV/DIV

Large Signal

Signal Response

Response

Large

VS = ±5V

AV=1

RL=1kΩ

TA=25°C

VS = ±5V

TA=25°C

AV=1

0V

1.5V/DIV

SHDN

2.25V

1V/DIV

1µs/DIV

6228 G46

Small Signal Response

Output Overdrive Recovery

VS = ±5V

RL=1kΩ

AV=1

TA=25°C

Input

0

50mV/DIV

Input

Output

Input

1V/DIV

Output

2V/DIV

Output

0

50mV/DIV

5ns/DIV

6228 G47

20ns/DIV

6228 G48

VS = ±5V

AV=2

RF=RG=500Ω

CF=2.7pF

RL=1kΩ

TA=25°C

25ns/DIV

6228 G49

Rev. B

For more information www.analog.com

15

�LTC6228/LTC6229

PIN FUNCTIONS

FB (SOIC-8 Only): Feedback Pin. Internally connected to

OUT.

+IN: Non-Inverting Input of Amplifier. Valid input range is

from V– to V+ – 1.2V

–IN: Inverting Input of Amplifier. Valid input range is from

V– to V+ – 1.2V

OUT: Output of the Amplifier. Swings rail to rail and can

typically source/sink more than 90mA of current.

SHDN: Shutdown Pin (Active Low). Referenced to V+.

When taken 2.75V below V+, the amplifier shuts down

and enters low power mode, with the outputs in a high

impedance state. When taken to within 350mV of V+, bias

current cancellation is enabled. When left floating, the

amplifier is on but bias cancellation is not enabled.

V+: Positive Supply to Amplifier. Valid range is from 2.8V

to 11.75V when V– is 0V.

V–: Negative Supply to Amplifier. Typically 0V. This can be

made a negative voltage as long as 2.8V ≤ (V+ – V–) ≤ 11.75V

Rev. B

16

For more information www.analog.com

�LTC6228/LTC6229

APPLICATIONS INFORMATION

Circuit Description

supplies via M2 and M1), and disable_bias, which disables

the input bias cancellation circuit, by shorting the base of

Q19 to V– through M3.

The LTC6228/LTC6229 have an input signal range that

extends from the negative power supply to 1.2V below

the positive power supply. Figure 1 depicts a simplified

schematic of the amplifier. The input stage consists of

PNP transistors Q1 and Q2. At the input stage, devices

Q18 and Q19 act to cancel the bias current of the input

pair when bias cancellation is enabled. Bootstrap transistor

Q13 and R5 match the collector and emitter voltages of

Q11 and Q12, thus enhancing gain by improving output

impedance. By making the collector current of Q13 twice

that of Q11 and Q12, the base currents of Q11 and Q12

do not contribute towards mismatch between the collector currents of Q9 and Q8. This improves DC accuracy. A

pair of complementary common emitter stages, Q15 and

Q14, enables the output to swing to either rail. The SHDN

Interface block translates the SHDN signal into 2 signals,

pwr_dn for powering down the device (by deactivating

current sources I1 - I4) and putting the output in a high

impedance state (by shorting the bases of Q15/Q14 to the

Input Bias Current

The LTC6228 family has an input bias current of approximately 16μA. For the LTC6228 and the LTC6229DD10,

the input bias current can be reduced to under 2.5μA at

room temperature when the SHDN pin voltage is taken to

within 350mV of the positive power supply. This capability enables the input bias current cancellation circuitry,

allowing the amplifiers to be used in DC applications

involving source impedances.

When input bias current cancellation is enabled and the

input common mode voltage is within approximately

500mV of V–, the bias cancellation is no longer effective, because transistors Q18 and Q19 in Figure 1 enter

saturation. The input bias current can then exceed 50μA

or higher, which is more than the input bias current

V+

pwr_dn

pwr_dn

V+

+

V–

pwr_dn

I2

ESDD1

ESDD2

I3

pwr_dn

M2

Q15

+

R3

I1

R4

R5

ESDD5

C2

Q12

Q13

Q11

+IN

V–

pwr_dn

SHDN

SHDN

INTERFACE

BLOCK

D5

disable_bias

D7

OUT

V+

–IN

ESDD4

Q16

V–

Q17

CC

Q1 Q2

pwr_dn

ESDD3

V+

Q9

Q18

Q8

Q19

disable_bias

M3

I4

R1

R2

ESDD6

Q10

pwr_dn

V–

BUFFER

AND

OUTPUT BIAS

M1

C1

Q14

R3

6228 F01

Figure 1. LTC6228 Simplified Schematic Diagram

Rev. B

For more information www.analog.com

17

�LTC6228/LTC6229

APPLICATIONS INFORMATION

without input bias cancellation. Additionally when input

bias current cancellation is enabled, the current noise

increases. The decision to use input bias cancellation

should be made with the end application’s specifications

and conditions in mind.

If the SHDN pin is left floating, input bias cancellation is

not enabled, which may be suitable for many applications.

Output

The LTC6228 family has excellent output drive capability.

The amplifiers can typically deliver more than 90mA of

output current at a total supply of 10V, and can typically

swing to within 320mV of the supply with load currents

as high as 25mA. As the supply voltage to the amplifier

decreases, the output current capability also decreases.

Attention must be paid to keep the junction temperature

of the IC below 150°C (refer to Power Dissipation section)

when the output is in continuous short-circuit. The output

of the amplifier has reverse-biased diodes connected to

each supply. If the output is forced beyond either supply,

extremely high currents will flow through those diodes,

which may result in damage to the device.

Input Protection

The LTC6228 has a pair of back to back diodes (D5 and

D7) to prevent the emitter base breakdown of the input

transistors and limit the differential input to ±700mV.

Unlike many other high performance amplifiers, the

bases of the input pair transistors Q1 and Q2 are not

connected to the pins through internal resistors to limit

input current, since doing so would cause the noise to

increase. For instance, a 100Ω resistor in series with

each input generates 1.8nV/√Hz of noise, and the total

amplifier noise voltage would rise from 0.88nV/√Hz to

2nV/√Hz. If the input differential voltage exceeds ±0.7V,

current conducted though the protection diodes D5 and

D7 should be limited to under 10mA. This implies 25Ω of

protection resistance per quarter volt (250mV) of overdrive

beyond ±0.7V. In addition, the input and shutdown pins

have reverse biased diodes connected to the supplies. The

current in these diodes must be limited to under 10mA.

The amplifiers should not be used as comparators or in

other open loop applications.

ESD

The LTC6228 family has reverse biased ESD protection

diodes on all inputs as shown in Figure 1. There is an

additional clamp between the positive and negative supplies that further protects the device during ESD strikes.

Hot plugging of the device into a powered socket should

be avoided since this can trigger the clamp resulting in

larger currents flowing between the supply pins.

Capacitive Loads

Because the LTC6228/LTC6229 is designed for high

bandwidth applications, the output has not been designed

to drive capacitive loads directly. Load capacitance at the

output creates a non-dominant pole in the open loop frequency response, worsening the phase margin. When

driving capacitive loads, a resistor of 10Ω to 100Ω should

be connected between the amplifier output and the capacitive load to avoid ringing or oscillation. The feedback

should be taken directly from the amplifier output. Higher

voltage gain configurations tend to have better capacitive drive capability than lower gain configurations due

to lower closed loop bandwidth. The graphs titled Series

Output Resistor vs Capacitive Load demonstrate the transient response of the amplifier when driving capacitive

loads with various series resistors.

Feedback Components

When feedback resistors are used to set up gain, care

must be taken to ensure that the non-dominant pole

formed by the feedback resistors and the parasitic capacitance at the inverting input does not degrade stability. For

example if the amplifier is set up in a gain of +2 configuration with gain and feedback resistors of 1k, a parasitic

capacitance of 7pF (device + PC board) at the amplifier’s

Rev. B

18

For more information www.analog.com

�LTC6228/LTC6229

APPLICATIONS INFORMATION

inverting input will cause the part to oscillate, due to the

pole formed at 45MHz. Adding a capacitor of 7pF across

the feedback resistor as shown in Figure 2 will eliminate

any ringing or oscillation. In general, if the resistive feedback network results in a pole whose frequency lies within

the closed loop bandwidth of the amplifier, a capacitor can

be added in parallel with the feedback resistor to introduce

a zero whose frequency is close to the frequency of the

pole, improving stability.

7pF

1k

–

1k

CPAR

VIN

VOUT

+

Power Dissipation

Care must be taken to ensure that the junction temperature of the die does not exceed 150°C.

The junction temperature, TJ, is calculated from the ambient temperature, TA, power dissipation, PD, and thermal

resistance, θJA:

TJ = TA + (PD • θJA).

The power dissipation in the IC is a function of the supply

voltage, output voltage and load resistance. For a given

supply voltage with output load connected to mid supply,

the worst-case power dissipation PD(MAX) occurs when

the supply current is maximum and the output voltage at

half of either supply voltage for a given load resistance.

PD(MAX) is approximately (since IS actually changes with

output load current) given by:

PD(MAX) = (2 • VS • IS(MAX)) + (VS/2)2/RL

6228 F02

Figure 2. 7pF Feedback Cancels Parasitic Pole

For high speed designs, minimizing parasitic inductance

is important. The use of capacitors where the electrodes

are terminated on the long side instead of the short side

(for example the use of 0306 instead of 0603 components) can help in this regard.

Shutdown

The LTC6228/LTC6229 have shutdown pins (SHDN),

which disable the amplifiers and reduce the quiescent

current per channel to approximately 500µA. The SHDN

pin needs to be driven at least 2.75V below V+ to disable

amplifier operation. For total supply voltages of 5V and or

less, the amplifier can be disabled at a pin voltage of V+ –

2.65V. During shutdown, the output transistors Q15 and

Q14 in Figure 1 are placed into a high impedance state. If

SHDN is left floating, the pin is internally biased to 1.2V

below the positive supply, and the amplifier remains on.

Example: For an LTC6228 in a 6-lead DC package operating on ±5V supplies and driving a 500Ω load to ground,

the worst-case power dissipation is approximately given

by PD(MAX)/Amp = (10 • 19mA) + (5)2/500 = 240mW.

At the Absolute Maximum ambient operating temperature,

the junction temperature under these conditions will be:

TJ = TA + (PD • θJA) = 125 + 0.24 • 80 = 144.2°C

which is slightly less than the absolute maximum junction

temperature for the LTC6228/LTC6229.

Refer to the Pin Configuration section for thermal resistances of various packages

Board Layout and Bypass Capacitors

High speed and RF board layout techniques should be

used due to the very high speeds of the signals involved.

For the LTC6228 SOIC-8 package option, the feedback

should be taken from the FB pin rather than from the

output pin, to reduce signal trace length.

Rev. B

For more information www.analog.com

19

�LTC6228/LTC6229

APPLICATIONS INFORMATION

Stray capacitances at the –IN and +IN pins should be

made as low as possible to reduce stability degradation.

For example, ground or supply planes on a PCB should

not encompass the areas just beneath the input pins.

For single supply applications, it is recommended that high

quality 0.1µF||1000pF ceramic bypass capacitors be placed

directly between each V+ pin and its closest V– pin with

short connections. The V– pins (including the Exposed Pad)

should be tied directly to a low impedance ground plane

with minimal routing. For dual (split) power supplies, it is

recommended that additional high quality 0.1µF||1000pF

ceramic capacitors be used to bypass V+ pins to ground

and V– pins to ground, again with minimal routing.

Noise Considerations

The ultralow input referred voltage noise of 0.88nV/√Hz is

equivalent to that of a 47Ω resistor at room temperature.

As with all BJT input amplifiers, lowering input referred

voltage noise is achieved by increasing the collector current of the input differential pair, which increases the input

referred current noise.

RG

–

en

RS1

LTC6228

in

6228 F03

Figure 3.

Figure 3 shows the LTC6228 in a typical gain configuration.

As can be seen, the input referred noise spectral density

of the gain stage (eT) can be calculated by the following

equations:

}

}

}

opamp opamp

voltage current

noise noise

resistor

thermal

noise

Where

REQ = RS1 + RG||RF

Resistor noise dominates the input referred noise of the

gain stage when

REQ >> en2/4KT and REQ > 4kT/in2

To summarize, initially en dominates for low resistance values. As the resistance increased, resistor noise starts to

dominate, then on further increase current noise dominates.

With an input referred voltage noise spectral density of

0.88nV/Hz and an input referred current noise of 3pA/Hz

(bias cancellation disabled), it is easy to see that the gain

stage’s input referred noise is dominated by op amp voltage noise when REQ