LTM4601/LTM4601-1

12A µModule Regulators

with PLL, Output Tracking

and Margining

Description

Features

n

n

n

n

n

n

n

n

n

n

n

n

n

n

n

n

n

Complete Switch Mode Power Supply

Wide Input Voltage Range: 4.5V to 20V

12A DC Typical, 14A Peak Output Current

0.6V to 5V Output Voltage

Output Voltage Tracking and Margining

Parallel Multiple µModule Regulators for Current

Sharing

Differential Remote Sensing for Precision

Regulation (LTM4601 Only)

PLL Frequency Synchronization

±1.5% Regulation

Current Foldback Protection (Disabled at Start-Up)

SnPb or RoHS Compliant Finish

UltraFast™ Transient Response

Current Mode Control

Up to 95% Efficiency at 5VIN, 3.3VOUT

Programmable Soft-Start

Output Overvoltage Protection

Small Footprint, Low Profile

(15mm × 15mm × 2.82mm) Surface Mount LGA and

(15mm × 15mm × 3.42mm) BGA Packages

The LTM®4601 is a complete 12A step-down switch mode

DC/DC power supply with onboard switching controller,

MOSFETs, inductor and all support components. The

µModule® regulator is housed in small surface mount

15mm × 15mm × 2.82mm LGA and 15mm × 15mm ×

3.42mm BGA packages. Operating over an input voltage

range of 4.5V to 20V, the LTM4601 supports an output

voltage range of 0.6V to 5V as well as output voltage

tracking and margining. The high efficiency design delivers 12A continuous current (14A peak). Only bulk input

and output capacitors are needed to complete the design.

The low profile and light weight package easily mounts

in unused space on the back side of PC boards for high

density point of load regulation. The µModule regulator

can be synchronized with an external clock for reducing

undesirable frequency harmonics and allows PolyPhase®

operation for high load currents.

A high switching frequency and adaptive on-time current

mode architecture deliver a very fast transient response

to line and load changes without sacrificing stability. An

onboard differential remote sense amplifier can be used

to accurately regulate an output voltage independent of

load current. The onboard remote sense amplifier is not

available in the LTM4601-1.

Applications

Telecom and Networking Equipment

Servers

n Industrial Equipment

n Point of Load Regulation

n

n

L, LT, LTC, LTM, Linear Technology, the Linear logo, µModule and PolyPhase are registered

trademarks and UltraFast and LTpowerCAD are trademarks of Linear Technology Corporation.

All other trademarks are the property of their respective owners. Protected by U.S. Patents

including 5481178, 5847554, 6580258, 6304066, 6476589, 6774611, 6677210.

Typical Application

Efficiency and Power Loss

vs Load Current

1.5V/12A Power Supply with 4.5V to 20V Input

95

CLOCK SYNC

TRACK/SS CONTROL

ON/OFF

CIN

R1

392k

5% MARGIN

RUN

COMP

INTVCC

DRVCC

MPGM

SGND

PLLIN TRACK/SS

VOUT

LTM4601

PGND

VFB

MARG0

MARG1

VOUT

1.5V

12A

100pF

MARGIN

CONTROL

COUT

VOUT_LCL

DIFFVOUT

VOSNS+

VOSNS–

fSET

3.5

85

12VIN

80

12VIN

70

1.5

POWER LOSS

55

4601 TA01a

2.0

5VIN

65

50

3.0

2.5

75

60

RSET

40.2k

4.0

5VIN

0

2

4

6

8

10

LOAD CURRENT (A)

1.0

12

14

4601 TA01b

For more information www.linear.com/LTM4601

POWER LOSS (W)

VIN

PGOOD

EFFICIENCY

90

EFFICIENCY (%)

VIN

4.5V TO 20V

0.5

4601fe

1

�LTM4601/LTM4601-1

Absolute Maximum Ratings

(Note 1)

INTVCC, DRVCC, VOUT_LCL, VOUT (VOUT ≤ 3.3V with

DIFFVOUT )..................................................... –0.3V to 6V

PLLIN, TRACK/SS, MPGM, MARG0, MARG1,

PGOOD, fSET...............................–0.3V to INTVCC + 0.3V

RUN (Note 5)................................................ –0.3V to 5V

VFB, COMP................................................. –0.3V to 2.7V

VIN.............................................................. –0.3V to 20V

VOSNS+, VOSNS –...........................–0.3V to INTVCC + 0.3V

Operating Temperature Range (Note 2)....–40°C to 85°C

Junction Temperature............................................ 125°C

Storage Temperature Range................... –55°C to 125°C

Reflow (Peak Body) Temperature........................... 245°C

fSET

VIN

MPGM

COMP

RUN

fSET

MARG0

MARG1

MARG1

DRVCC

DRVCC

VFB

PGND

PGOOD

PGOOD

SGND

SGND

VOSNS+/NC2*

VOSNS+/NC2*

DIFFVOUT/NC3*

VOUT

TRACK/SS

VIN

MARG0

VFB

PGND

PLLIN

INTVCC

MPGM

COMP

TOP VIEW

RUN

PLLIN

INTVCC

TOP VIEW

TRACK/SS

Pin Configuration

DIFFVOUT/NC3*

VOUT

VOUT_LCL

VOUT_LCL

VOSNS–/NC1*

VOSNS–/NC1*

BGA PACKAGE

118-LEAD (15mm × 15mm × 3.42mm)

LGA PACKAGE

118-LEAD (15mm × 15mm × 2.82mm)

TJMAX = 125°C, θJA = 15.5°C/W, θJC = 6.5°C/W,

θJA DERIVED FROM 95mm × 76mm PCB WITH 4 LAYERS

WEIGHT = 1.9g

*LTM4601-1 ONLY

TJMAX = 125°C, θJA = 15°C/W, θJC = 6°C/W,

θJA DERIVED FROM 95mm × 76mm PCB WITH 4 LAYERS

WEIGHT = 1.7g

*LTM4601-1 ONLY

Order Information

PART NUMBER

PAD OR BALL FINISH

LTM4601EV#PBF

Au (RoHS)

PART MARKING*

DEVICE

FINISH CODE

PACKAGE

TYPE

LTM4601V

e4

LGA

MSL

RATING

3

TEMPERATURE RANGE

(Note 2)

–40°C to 85°C

LTM4601IV#PBF

Au (RoHS)

LTM4601V

e4

LGA

3

–40°C to 85°C

LTM4601EV-1#PBF

Au (RoHS)

LTM4601V-1

e4

LGA

3

–40°C to 85°C

LTM4601IV-1#PBF

Au (RoHS)

LTM4601V-1

e4

LGA

3

–40°C to 85°C

LTM4601EY#PBF

SAC305 (RoHS)

LTM4601Y

e1

BGA

3

–40°C to 85°C

LTM4601IY#PBF

SAC305 (RoHS)

LTM4601Y

e1

BGA

3

–40°C to 85°C

LTM4601EY-1#PBF

SAC305 (RoHS)

LTM4601Y-1

e1

BGA

3

–40°C to 85°C

LTM4601IY-1#PBF

SAC305 (RoHS)

LTM4601Y-1

e1

BGA

3

–40°C to 85°C

LTM4601IY

SnPb (63/37)

LTM4601Y

e0

BGA

3

–40°C to 85°C

LTM4601IY-1

SnPb (63/37)

LTM4601Y-1

e0

BGA

3

–40°C to 85°C

2

4601fe

For more information www.linear.com/LTM4601

�LTM4601/LTM4601-1

Order Information

Consult Marketing for parts specified with wider operating temperature

ranges. *Device temperature grade is indicated by a label on the shipping

container. Pad or ball finish code is per IPC/JEDEC J-STD-609.

• Recommended LGA and BGA PCB Assembly and Manufacturing

Procedures:

www.linear.com/umodule/pcbassembly

• Terminal Finish Part Marking:

www.linear.com/leadfree

• LGA and BGA Package and Tray Drawings:

www.linear.com/packaging

Electrical Characteristics

The l denotes the specifications which apply over the –40°C to 85°C

temperature range (Note 2), otherwise specifications are at TA = 25°C, VIN = 12V, per typical application (front page) configuration.

SYMBOL

PARAMETER

VIN(DC)

Input DC Voltage

VOUT(DC)

Output Voltage

CONDITIONS

CIN = 10µF ×3, COUT = 200µF, RSET = 40.2k

VIN = 5V, VOUT = 1.5V, IOUT = 0A

VIN = 12V, VOUT = 1.5V, IOUT = 0A

MIN

l

4.5

l

l

1.478

1.478

TYP

MAX

UNITS

20

V

1.5

1.5

1.522

1.522

V

V

4

V

Input Specifications

VIN(UVLO)

Undervoltage Lockout Threshold

IOUT = 0A

3.2

IINRUSH(VIN)

Input Inrush Current at Start-Up

IOUT = 0A. VOUT = 1.5V

VIN = 5V

VIN = 12V

0.6

0.7

A

A

IQ(VIN,NOLOAD)

Input Supply Bias Current

VIN = 12V, No Switching

VIN = 12V, VOUT = 1.5V, Switching Continuous

VIN = 5V, No Switching

VIN = 5V, VOUT = 1.5V, Switching Continuous

Shutdown, RUN = 0, VIN = 12V

3.8

38

2.5

42

22

mA

mA

mA

mA

µA

IS(VIN)

Input Supply Current

VIN = 12V, VOUT = 1.5V, IOUT = 12A

VIN = 12V, VOUT = 3.3V, IOUT = 12A

VIN = 5V, VOUT = 1.5V, IOUT = 12A

1.81

3.63

4.29

A

A

A

INTVCC

VIN = 12V, RUN > 2V

No Load

4.7

5

5.3

V

12

A

Output Specifications

IOUTDC

Output Continuous Current Range

VIN = 12V, VOUT = 1.5V (Note 6)

0

ΔVOUT(LINE)

Line Regulation Accuracy

VOUT = 1.5V, IOUT = 0A, VIN from 4.5V to 20V

l

0.3

%

Load Regulation Accuracy

VOUT = 1.5V, 0A to 12A (Note 6)

VIN = 12V, with Remote Sense Amplifier

VIN = 12V (LTM4601-1)

l

l

0.25

1

%

%

VOUT

ΔVOUT(LOAD)

VOUT

VOUT(AC)

Output Ripple Voltage

IOUT = 0A, COUT = 2× 100µF X5R Ceramic

VIN = 12V, VOUT = 1.5V

VIN = 5V, VOUT = 1.5V

20

18

mVP-P

mVP-P

fS

Output Ripple Voltage Frequency

IOUT = 5A, VIN = 12V, VOUT = 1.5V

850

kHz

ΔVOUT(START)

Turn-On Overshoot

COUT = 200µF, VOUT = 1.5V, IOUT = 0A,

TRACK/SS = 10nF

VIN = 12V

VIN = 5V

20

20

mV

mV

COUT = 200µF, VOUT = 1.5V, TRACK/SS = Open,

IOUT = 1A Resistive Load

VIN = 12V

VIN = 5V

0.5

0.5

ms

ms

tSTART

Turn-On Time

4601fe

For more information www.linear.com/LTM4601

3

�LTM4601/LTM4601-1

Electrical Characteristics

The l denotes the specifications which apply over the –40°C to 85°C

temperature range (Note 2), otherwise specifications are at TA = 25°C, VIN = 12V, per typical application (front page) configuration.

SYMBOL

PARAMETER

CONDITIONS

MIN

ΔVOUTLS

Peak Deviation for Dynamic Load

Load: 0% to 50% to 0% of Full Load,

COUT = 2 × 22µF Ceramic, 470µF 4V Sanyo

POSCAP

VIN = 12V

VIN = 5V

tSETTLE

Settling Time for Dynamic Load Step Load: 0% to 50%, or 50% to 0% of Full Load

VIN = 12V

IOUTPK

Output Current Limit

COUT = 200µF Ceramic

VIN = 12V, VOUT = 1.5V

VIN = 5V, VOUT = 1.5V

TYP

MAX

UNITS

35

35

mV

mV

25

µs

17

17

A

A

Remote Sense Amp (Note 3) (LTM4601 Only, Not Supported in the LTM4601-1)

VOSNS+, VOSNS–

CM Range

Common Mode Input Voltage Range VIN = 12V, RUN > 2V

0

INTVCC – 1

V

DIFFVOUT Range

Output Voltage Range

0

INTVCC – 1

V

VOS

Input Offset Voltage Magnitude

AV

Differential Gain

1

V/V

GBP

Gain Bandwidth Product

3

MHz

SR

Slew Rate

2

V/µs

20

kW

100

dB

RIN

Input Resistance

CMRR

Common Mode Rejection Mode

VIN = 12V, DIFFVOUT Load = 100k

1.25

VOSNS+ to GND

mV

Control Stage

VFB

Error Amplifier Input Voltage

Accuracy

IOUT = 0A, VOUT = 1.5V

VRUN

RUN Pin On/Off Threshold

ITRACK/SS

Soft-Start Charging Current

VTRACK/SS = 0V

tON(MIN)

Minimum On Time

(Note 4)

tOFF(MIN)

Minimum Off Time

(Note 4)

RPLLIN

PLLIN Input Resistance

IDRVCC

Current into DRVCC Pin

l

0.594

0.6

0.606

V

1

1.5

1.9

V

–1.0

–1.5

–2.0

µA

50

100

ns

250

400

ns

50

VOUT = 1.5V, IOUT = 1A, DRVCC = 5V

60.098

kΩ

18

25

mA

60.4

60.702

kΩ

RFBHI

Resistor Between VOUT_LCL and VFB

VMPGM

Margin Reference Voltage

1.18

V

VMARG0, VMARG1

MARG0, MARG1 Voltage Thresholds

1.4

V

PGOOD Output

ΔVFBH

PGOOD Upper Threshold

VFB Rising

7

10

13

%

ΔVFBL

PGOOD Lower Threshold

VFB Falling

–7

–10

–13

%

ΔVFB(HYS)

PGOOD Hysteresis

VFB Returning

Note 1: Stresses beyond those listed under Absolute Maximum Ratings

may cause permanent damage to the device. Exposure to any Absolute

Maximum Rating condition for extended periods may affect device

reliability and lifetime.

Note 2: The LTM4601 is tested under pulsed load conditions such that

TJ ≈ TA. The LTM4601E/LTM4601E-1 are guaranteed to meet performance

specifications from 0°C to 85°C. Specifications over the –40°C to 85°C

operating temperature range are assured by design, characterization and

4

1.5

%

correlation with statistical process controls. The LTM4601I/LTM4601I-1

are guaranteed over the –40°C to 85°C operating temperature range.

Note 3: Remote sense amplifier recommended for ≤3.3V output.

Note 4: 100% tested at wafer level only.

Note 5: Limit current into RUN pin to less than 1mA.

Note 6: See output current derating curves for different VIN, VOUT and TA.

4601fe

For more information www.linear.com/LTM4601

�LTM4601/LTM4601-1

Typical Performance Characteristics (See Figure 18 for all curves)

Efficiency vs Load Current

with 5VIN

100

95

100

95

95

85

80

75

0.6VOUT

1.2VOUT

1.5VOUT

2.5VOUT

3.3VOUT

70

65

0

5

90

85

80

75

70

0.6VOUT

1.2VOUT

1.5VOUT

2.5VOUT

3.3VOUT

5VOUT

65

60

55

10

50

15

EFFICIENCY (%)

EFFICIENCY (%)

EFFICIENCY (%)

100

90

90

60

Efficiency vs Load Current

with 20VIN

Efficiency vs Load Current

with 12VIN

0

LOAD CURRENT (A)

80

75

65

15

60

0

10

5

LOAD CURRENT (A)

1.5V Transient Response

1.8V Transient Response

VOUT

50mV/DIV

VOUT

50mV/DIV

VOUT

50mV/DIV

0A TO 6A

LOAD STEP

0A TO 6A

LOAD STEP

0A TO 6A

LOAD STEP

4601 G04

20µs/DIV

1.5V AT 6A/µs LOAD STEP

COUT = 3 • 22µF 6.3V CERAMICS

470µF 4V SANYO POSCAP

C3 = 100pF

2.5V Transient Response

4601 G05

20µs/DIV

1.8V AT 6A/µs LOAD STEP

COUT = 3 • 22µF 6.3V CERAMICS

470µF 4V SANYO POSCAP

C3 = 100pF

4601 G06

3.3V Transient Response

VOUT

50mV/DIV

VOUT

50mV/DIV

0A TO 6A

LOAD STEP

0A TO 6A

LOAD STEP

20µs/DIV

2.5V AT 6A/µs LOAD STEP

COUT = 3 • 22µF 6.3V CERAMICS

470µF 4V SANYO POSCAP

C3 = 100pF

15

4601 G03

4601 G02

1.2V Transient Response

20µs/DIV

1.2V AT 6A/µs LOAD STEP

COUT = 3 • 22µF 6.3V CERAMICS

470µF 4V SANYO POSCAP

C3 = 100pF

1.2VOUT

1.5VOUT

2.5VOUT

3.3VOUT

5.0VOUT

70

10

5

LOAD CURRENT (A)

4601 G01

85

4601 G07

20µs/DIV

3.3V AT 6A/µs LOAD STEP

COUT = 3 • 22µF 6.3V CERAMICS

470µF 4V SANYO POSCAP

C3 = 100pF

4601 G08

4601fe

For more information www.linear.com/LTM4601

5

�LTM4601/LTM4601-1

Typical Performance Characteristics (See Figure 18 for all curves)

Start-Up, IOUT = 12A

(Resistive Load)

Start-Up, IOUT = 0A

VOUT

0.5V/DIV

VOUT

0.5V/DIV

IIN

1A/DIV

IIN

0.5A/DIV

5ms/DIV

VIN = 12V

VOUT = 1.5V

COUT = 470µF, 3 × 22µF

SOFT-START = 10nF

5.5

VIN to VOUT Step-Down Ratio

3.3V OUTPUT WITH

130k FROM VOUT

TO ION

4.5

5V OUTPUT WITH

100k RESISTOR

ADDED FROM fSET

TO GND

4.0

3.5

3.0

2.0

5V OUTPUT WITH

NO RESISTOR ADDED

FROM fSET TO GND

1.5

2.5V OUTPUT

1.0

1.8V OUTPUT

0.5

1.5V OUTPUT

2.5

0

TRACK/SS

0.5V/DIV

VFB

0.5V/DIV

VOUT

1V/DIV

2ms/DIV

VIN = 12V

VOUT = 1.5V

COUT = 470µF, 3 × 22µF

SOFT-START = 10nF

1.2V OUTPUT

0

2

4

4601 G10

Track, IOUT = 12A

5.0

OUTPUT VOLTAGE (V)

2ms/DIV

VIN = 12V

VOUT = 1.5V

COUT = 470µF, 3 × 22µF

SOFT-START = 10nF

4601 G09

4601 G12

6 8 10 12 14 16 18 20

INPUT VOLTAGE (V)

4601 G11

Short-Circuit Protection, IOUT = 0A

VOUT

0.5V/DIV

VOUT

0.5V/DIV

IIN

1A/DIV

IIN

1A/DIV

50µs/DIV

VIN = 12V

VOUT = 1.5V

COUT = 470µF, 3 × 22µF

SOFT-START = 10nF

6

Short-Circuit Protection, IOUT = 12A

4601 G13

50µs/DIV

VIN = 12V

VOUT = 1.5V

COUT = 470µF, 3 × 22µF

SOFT-START = 10nF

4601 G14

4601fe

For more information www.linear.com/LTM4601

�LTM4601/LTM4601-1

Pin Functions

(See Package Description for Pin Assignment)

VIN (Bank 1): Power Input Pins. Apply input voltage between these pins and PGND pins. Recommend placing

input decoupling capacitance directly between VIN pins

and PGND pins.

VOUT (Bank 3): Power Output Pins. Apply output load

between these pins and PGND pins. Recommend placing

output decoupling capacitance directly between these pins

and PGND pins. See Figure 15.

PGND (Bank 2): Power ground pins for both input and

output returns.

TRACK/SS (Pin A9): Output Voltage Tracking and SoftStart Pin. When the module is configured as a master

output, then a soft-start capacitor is placed from this pin

to ground to control the master ramp rate. A soft-start

capacitor can also be used for soft-start turn-on of a stand

alone regulator. Slave operation is performed by putting

a resistor divider from the master output to the ground,

and connecting the center point of the divider to this pin.

See the Applications Information section.

NC1 (Pin M12): No internal connection on the LTM4601-1.

MPGM (Pin A12): Programmable Margining Input. A resistor from this pin to ground sets a current that is equal

to 1.18V/R. This current multiplied by 10kΩ will equal a

value in millivolts that is a percentage of the 0.6V reference voltage. See the Applications Information section.

To parallel LTM4601s, each requires an individual MPGM

resistor. Do not tie MPGM pins together.

VOSNS+ (Pin J12): (+) Input to the Remote Sense Amplifier. This pin connects to the output remote sense point.

The remote sense amplifier is used for VOUT ≤3.3V. Tie to

ground if not used.

fSET (Pin B12): Frequency Set Internally to 850kHz. An

external resistor can be placed from this pin to ground

to increase frequency. See the Applications Information

section for frequency adjustment.

NC2 (Pin J12): No internal connection on the LTM4601-1.

VFB (Pin F12): The Negative Input of the Error Amplifier.

Internally, this pin is connected to VOUT_LCL pin with a

60.4k precision resistor. Different output voltages can be

programmed with an additional resistor between VFB and

SGND pins. See the Applications Information section.

VOSNS– (Pin M12): (–) Input to the Remote Sense Amplifier. This pin connects to the ground remote sense point.

The remote sense amplifier is used for VOUT ≤3.3V. Tie to

INTVCC if not used.

DIFFVOUT (Pin K12): Output of the Remote Sense Amplifier. This pin connects to the VOUT_LCL pin. Leave floating

if not used.

NC3 (Pin K12): No internal connection on the LTM4601-1.

DRVCC (Pin E12): This pin normally connects to INTVCC

for powering the internal MOSFET drivers. This pin can be

biased up to 6V from an external supply with about 50mA

capability, or an external circuit as shown in Figure 16.

This improves efficiency at the higher input voltages by

reducing power dissipation in the module.

INTVCC (Pin A7): This pin is for additional decoupling of

the 5V internal regulator.

PLLIN (Pin A8): External Clock Synchronization Input

to the Phase Detector. This pin is internally terminated

to SGND with a 50k resistor. Apply a clock with a high

level above 2V and below INTVCC. See the Applications

Information section.

MARG0 (Pin C12): This pin is the LSB logic input for the

margining function. Together with the MARG1 pin it will

determine if margin high, margin low or no margin state

is applied. The pin has an internal pull-down resistor of

50k. See the Applications Information section.

MARG1 (Pin D12): This pin is the MSB logic input for the

margining function. Together with the MARG0 pin it will

determine if margin high, margin low or no margin state

is applied. The pin has an internal pull-down resistor of

50k. See the Applications Information section.

4601fe

For more information www.linear.com/LTM4601

7

�LTM4601/LTM4601-1

Pin Functions

(See Package Description for Pin Assignment)

SGND (Pin H12): Signal Ground. This pin connects to

PGND at output capacitor point. See Figure 15.

COMP (Pin A11): Current Control Threshold and Error

Amplifier Compensation Point. The current comparator

threshold increases with this control voltage. The voltage

ranges from 0V to 2.4V with 0.7V corresponding to zero

sense voltage (zero current).

PGOOD (Pin G12): Output Voltage Power Good Indicator.

Open-drain logic output that is pulled to ground when the

output voltage is not within ±10% of the regulation point,

after a 25µs power bad mask timer expires.

8

RUN (Pin A10): Run Control Pin. A voltage above 1.9V

will turn on the module, and when below 1V, will turn

off the module. A programmable UVLO function can be

accomplished by connecting to a resistor divider from

VIN to ground. See Figure 1. This pin has a 5.1V Zener to

ground. Maximum pin voltage is 5V. Limit current into the

RUN pin to less than 1mA.

VOUT_LCL (Pin L12): VOUT connects directly to this pin

to bypass the remote sense amplifier, or DIFFVOUT connects to this pin when the remote sense amplifier is used.

VOUT_LCL can be connected to VOUT on the LTM4601-1,

VOUT is internally connected to VOUT_LCL with 50Ω in the

LTM4601-1.

4601fe

For more information www.linear.com/LTM4601

�LTM4601/LTM4601-1

Simplified Block Diagram

VOUT_LCL

VIN

R1

UVLO

FUNCTION

>1.9V = ON

4.8V use 4.8V.

LTM4601 minimum on-time = 100ns

tON = ((VOUT • 10pF)/IfSET)

LTM4601 minimum off-time = 400ns

tOFF = t – tON, where t = 1/Frequency

LTM4601 minimum off-time = 400ns

tOFF = t – tON, where t = 1/Frequency

Duty Cycle = tON/t or VOUT/VIN

Duty Cycle (DC) = tON/t or VOUT/VIN

Equations for setting frequency:

Equations for setting frequency:

IfSET = (VIN/(3 • RfSET)), for 20V operation, IfSET = 170µA,

tON = ((4.8 • 10pF)/IfSET), tON = 282ns, where the internal

RfSET is 39.2k. Frequency = (VOUT/(VIN • tON)) = (5V/(20

• 282ns)) ~ 886kHz. The inductor ripple current begins

to get high at the higher input voltages due to a larger

voltage across the inductor. This is noted in the Inductor

Ripple Current vs Duty Cycle graph (Figure 3) where IL ≈

10A at 25% duty cycle. The inductor ripple current can be

lowered at the higher input voltages by adding an external

resistor from fSET to ground to increase the switching

frequency. An 8A ripple current is chosen, and the total

peak current is equal to 1/2 of the 8A ripple current plus

the output current. The 5V output current is limited to 8A,

so the total peak current is less than 12A. This is below the

14A peak specified value. A 100k resistor is placed from

fSET to ground, and the parallel combination of 100k and

39.2k equates to 28k. The IfSET calculation with 28k and

20V input voltage equals 238µA. This equates to a tON of

200ns. This will increase the switching frequency from

~886kHz to ~1.25MHz for the 20V to 5V conversion. The

minimum on-time is above 100ns at 20V input. Since

the switching frequency is approximately constant over

input and output conditions, then the lower input voltage

range is limited to 10V for the 1.25MHz operation due to

the 400ns minimum off-time. Equation: tON = (VOUT/VIN)

• (1/Frequency) equates to a 400ns on-time, and a 400ns

off-time. The VIN to VOUT Step-Down Ratio curve reflects

an operating range of 10V to 20V for 1.25MHz operation

with a 100k resistor to ground, and an 8V to 16V operation

for fSET floating. These modifications are made to provide

wider input voltage ranges for the 5V output designs while

limiting the inductor ripple current, and maintaining the

400ns minimum off-time.

IfSET = (VIN /(3 • RfSET)), for 20V operation, IfSET = 170µA,

tON = ((3.3 • 10pf)/IfSET), tON = 195ns, where the internal

RfSET is 39.2k. Frequency = (VOUT/(VIN • tON)) = (3.3V/

(20 • 195ns)) ~ 846kHz. The minimum on-time and minimum off-time are within specification at 195ns and 980ns.

The 4.5V minimum input for converting 3.3V output will

not meet the minimum off-time specification of 400ns.

tON = 868ns, Frequency = 850kHz, tOFF = 315ns.

Solution

Lower the switching frequency at lower input voltages to

allow for higher duty cycles, and meet the 400ns minimum

off-time at 4.5V input voltage. The off-time should be about

500ns, which includes a 100ns guard band. The duty cycle

for (3.3V/4.5V) = ~73%. Frequency = (1 – DC)/tOFF or

(1 – 0.73)/500ns = 540kHz. The switching frequency

needs to be lowered to 540kHz at 4.5V input. tON = DC/

frequency, or 1.35µs. The fSET pin voltage is 1/3 of VIN, and

the IfSET current equates to 38µA with the internal 39.2k.

The IfSET current needs to be 24µA for 540kHz operation. A resistor can be placed from VOUT to fSET to lower

the effective IfSET current out of the fSET pin to 24µA.

The fSET pin is 4.5V/3 =1.5V and VOUT = 3.3V, therefore

130k will source 14µA into the fSET node and lower the

IfSET current to 24µA. This enables the 540kHz operation

and the 4.5V to 20V input operation for down converting to

3.3V output. The frequency will scale from 540kHz to 1.1

MHz over this input range. This provides for an effective

output current of 8A over the input range.

4601fe

For more information www.linear.com/LTM4601

21

�LTM4601/LTM4601-1

Applications information

VOUT

VIN

10V TO 20V

R2

100k

TRACK/SS CONTROL

R4

100k

VIN

PGOOD

MPGM

RUN

COMP

INTVCC

DRVCC

5% MARGIN

CIN

10µF

25V

×2

R1

392k

1%

SGND

REVIEW TEMPERATURE

DERATING CURVE

PLLIN TRACK/SS

VOUT

LTM4601-1

+

C3 100pF

VFB

MARG0

MARG1

VOUT

5V

8A

COUT1

100µF

REFER TO

6.3V

SANYO POSCAP TABLE 2

VOUT_LCL

NC3

NC1

NC2

fSET

PGND

RfSET

100k

RSET

8.25k

MARGIN CONTROL

IMPROVE

EFFICIENCY

FOR ≥12V INPUT

SOT-323

DUAL

CMSSH-3C3

4601 F16

Figure 16. 5V at 8A Design Without Differential Amplifier

VIN

4.5V TO 16V

VOUT

R2

100k

TRACK/SS CONTROL

R4

100k

VIN

PGOOD

PGOOD

CIN

10µF

25V

×3

MPGM

RUN

COMP

INTVCC

DRVCC

PLLIN TRACK/SS

VOUT

LTM4601

R1

392k

SGND

5% MARGIN

PGND

REVIEW TEMPERATURE

DERATING CURVE

VFB

MARG0

MARG1

VOUT_LCL

DIFFVOUT

VOSNS+

VOSNS–

fSET

C3 100pF

+

RfSET

130k

MARGIN CONTROL

VOUT

3.3V

10A

COUT1

100µF

6.3V

SANYO POSCAP

RSET

13.3k

4601 F17

Figure 17. 3.3V at 10A Design

22

4601fe

For more information www.linear.com/LTM4601

�LTM4601/LTM4601-1

Applications information

CLOCK SYNC

C5

0.01µF

VOUT

VIN

4.5V TO 20V

R2

100k

R4

100k

PGOOD

CIN

BULK

OPT

+

CIN

10µF

25V

×3 CER

PLLIN TRACK/SS

VOUT

VIN

PGOOD

MPGM

RUN

ON/OFF

COMP

INTVCC

DRVCC

R1

392k

LTM4601

SGND

PGND

REVIEW TEMPERATURE

DERATING CURVE

VFB

MARG0

MARG1

C3 100pF

COUT1

100µF

6.3V

MARGIN

CONTROL

VOUT_LCL

DIFFVOUT

VOSNS+

VOSNS–

fSET

RSET

40.2k

4601 F18

5% MARGIN

+

COUT2

470µF

6.3V

VOUT

1.5V

12A

REFER TO

TABLE 2 FOR

DIFFERENT

OUTPUT

VOLTAGE

Figure 18. Typical 4.5V to 20V, 1.5V at 12A Design

VOUT

VIN

4.5V TO 20V

118k

1%

R2

100k

+

C1

0.1µF

LTC6908-1

1

2

3

V+

OUT1

GND

OUT2

SET

MOD

6

5

4

CLOCK SYNC

0° PHASE

C5*

100µF

25V

C2

10µF

25V

×2

R4

100k

VIN

PGOOD

MPGM

RUN

COMP

INTVCC

DRVCC

R1

392k

SGND

PLLIN TRACK/SS

VOUT

LTM4601

PGND

VFB

MARG0

MARG1

TRACK/SS CONTROL

C6 220pF

VOUT_LCL

DIFFVOUT

VOSNS+

VOSNS–

C3

22µF

6.3V

C4

470µF

6.3V

VOUT

1.5V

24A

+

REFER TO

TABLE 2

fSET

5%

MARGIN

2-PHASE

OSCILLATOR

60.4k + R

SET

N

RSET

N = NUMBER OF PHASES

VOUT = 0.6V

RSET

20k

100pF

MARGIN

CONTROL

CLOCK SYNC

180° PHASE

TRACK/SS CONTROL

4.5V TO 20V

C7

0.033µF

VIN

PGOOD

PGOOD

MPGM

RUN

COMP

INTVCC

DRVCC

C8

10µF

25V

×2

PLLIN TRACK/SS

VOUT

LTM4601-1

392k

SGND

PGND

C3

22µF

6.3V

VFB

MARG0

MARG1

C4

470µF

6.3V

REFER TO

TABLE 2

VOUT_LCL

NC3

NC2

NC1

fSET

+

4601 F19

*C5 OPTIONAL TO REDUCE ANY LC RINGING.

NOT NEEDED FOR LOW INDUCTANCE PLANE CONNECTION

Figure 19. 2-Phase Parallel, 1.5V at 24A Design

4601fe

For more information www.linear.com/LTM4601

23

�24

+

C11

100µF

35V

OPT

For more information www.linear.com/LTM4601

C2

10µF

25V

×3

VIN

PGOOD

SGND

SGND

MPGM

RUN

ON/OFF

COMP

INTVCC

DRVCC

R1

392k

R3

100k

8V TO 16V

5% MARGIN

PGOOD

R2

100k

3.3V

VIN

PGOOD

MPGM

RUN

ON/OFF

COMP

INTVCC

DRVCC

R27

392k

5% MARGIN

C8

10µF

25V

×3

PGOOD

R7

100k

8V TO 16V

INTERMEDIATE

BUS

3.3V

R6

100k

–48V

INPUT

fSET

VOUT_LCL

DIFFVOUT

VOSNS+

VOSNS–

PGND

LTM4601

fSET

VOUT_LCL

DIFFVOUT

VOSNS+

VOSNS–

VFB

MARG0

MARG1

PLLIN TRACK/SS

VOUT

CLOCK SYNC 3

PGND

LTM4601

VFB

MARG0

MARG1

PLLIN TRACK/SS

VOUT

MARGIN

CONTROL

C8 100pF

R19

30.1k

MARGIN

CONTROL

R8

13.3k

R12

30.1k

R21

60.4k

C7

0.15µF

C12 100pF

TRACK/SS

CONTROL

CLOCK SYNC 1

3.3V

+

REFER TO

TABLE 2

C3

22µF

6.3V

+

1.8V AT 12A

REFER TO

TABLE 2

C9

22µF

6.3V

R17

59k

LTC6902

C4

470µF

6.3V

C10

470µF

6.3V

V+

SET

DIV

MOD

PH

GND

OUT1 OUT4

OUT2 OUT3

3.3V AT 10A

4-PHASE

OSCILLATOR

8V TO 16V

C26

0.1µF

C14

10µF

25V

×3

PGND

LTM4601

VIN

PGOOD

SGND

PGND

LTM4601

fSET

VOUT_LCL

DIFFVOUT

VOSNS+

VOSNS–

VFB

MARG0

MARG1

PLLIN TRACK/SS

VOUT

fSET

VOUT_LCL

DIFFVOUT

VOSNS+

VOSNS–

VFB

MARG0

MARG1

PLLIN TRACK/SS

VOUT

CLOCK SYNC 4

SGND

MPGM

RUN

ON/OFF

COMP

INTVCC

DRVCC

R14

392k

R16

100k

8V TO 16V

5% MARGIN

PGOOD

R15

100k

VIN

PGOOD

CLOCK SYNC 2

MPGM

RUN

ON/OFF

COMP

INTVCC

DRVCC

R9

392k

5% MARGIN

3.3V

C14

10µF

25V

×3

8V TO 16V

R11

100k

PGOOD

R10

100k

3.3V

4-Phase, Four Outputs (3.3V, 2.5V, 1.8V and 1.5V) with Coincident Tracking

R18

19.1k

R13

40.2k

R25

60.4k

4601 TA02

MARGIN

CONTROL

C24 100pF

R26

40.2k

MARGIN

CONTROL

C18 100pF

R24

19.1k

R23

60.4k

3.3V

3.3V

+

REFER TO

TABLE 2

C16

22µF

6.3V

+

1.5V AT 12A

REFER TO

TABLE 2

C16

22µF

6.3V

2.5V AT 12A

C15

470µF

6.3V

C15

470µF

6.3V

LTM4601/LTM4601-1

Typical Applications

4601fe

�aaa Z

0.630 ±0.025 Ø 118x

3.1750

3.1750

SUGGESTED PCB LAYOUT

TOP VIEW

1.9050

PACKAGE TOP VIEW

E

0.6350

0.0000

0.6350

4

1.9050

PIN “A1”

CORNER

6.9850

5.7150

4.4450

4.4450

5.7150

6.9850

Y

For more information www.linear.com/LTM4601

6.9850

5.7150

4.4450

3.1750

1.9050

0.6350

0.0000

0.6350

1.9050

3.1750

4.4450

5.7150

6.9850

X

D

aaa Z

bbb Z

0.27

2.45

MIN

2.72

0.60

NOM

2.82

0.63

15.00

15.00

1.27

13.97

13.97

0.32

2.50

DIMENSIONS

0.37

2.55

0.15

0.10

0.05

MAX

2.92

0.66

NOTES

DETAIL B

PACKAGE SIDE VIEW

A

TOTAL NUMBER OF LGA PADS: 118

SYMBOL

A

b

D

E

e

F

G

H1

H2

aaa

bbb

eee

H1

SUBSTRATE

eee S X Y

DETAIL A

0.630 ±0.025 SQ. 118x

DETAIL B

H2

MOLD

CAP

Z

(Reference LTC DWG # 05-08-1801 Rev B)

LGA Package

118-Lead (15mm × 15mm × 2.82mm)

e

b

L

K

J

G

G

F

e

E

PACKAGE BOTTOM VIEW

H

D

C

B

A

DETAILS OF PAD #1 IDENTIFIER ARE OPTIONAL,

BUT MUST BE LOCATED WITHIN THE ZONE INDICATED.

THE PAD #1 IDENTIFIER MAY BE EITHER A MOLD OR

MARKED FEATURE

4

7

TRAY PIN 1

BEVEL

!

PACKAGE IN TRAY LOADING ORIENTATION

LTMXXXXXX

µModule

1

2

3

4

5

6

7

8

9

7

SEE NOTES

C(0.30)

PAD 1

10

11

12

LGA 118 1212 REV B

PACKAGE ROW AND COLUMN LABELING MAY VARY

AMONG µModule PRODUCTS. REVIEW EACH PACKAGE

LAYOUT CAREFULLY

6. THE TOTAL NUMBER OF PADS: 118

5. PRIMARY DATUM -Z- IS SEATING PLANE

LAND DESIGNATION PER JESD MO-222, SPP-010

3

2. ALL DIMENSIONS ARE IN MILLIMETERS

NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994

COMPONENT

PIN “A1”

3

SEE NOTES

F

b

M

DETAIL A

LTM4601/LTM4601-1

Package Description

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

25

4601fe

�aaa Z

0.630 ±0.025 Ø 118x

4

E

PACKAGE TOP VIEW

3.1750

3.1750

SUGGESTED PCB LAYOUT

TOP VIEW

1.9050

PIN “A1”

CORNER

0.6350

0.0000

0.6350

Y

For more information www.linear.com/LTM4601

6.9850

5.7150

4.4450

3.1750

1.9050

0.6350

0.0000

0.6350

1.9050

3.1750

4.4450

5.7150

6.9850

X

D

2.45 – 2.55

aaa Z

SYMBOL

A

A1

A2

b

b1

D

E

e

F

G

aaa

bbb

ccc

ddd

eee

NOM

3.42

0.60

2.82

0.75

0.63

15.0

15.0

1.27

13.97

13.97

DIMENSIONS

0.15

0.10

0.20

0.30

0.15

MAX

3.62

0.70

2.92

0.90

0.66

NOTES

DETAIL B

PACKAGE SIDE VIEW

TOTAL NUMBER OF BALLS: 118

MIN

3.22

0.50

2.72

0.60

0.60

b1

0.27 – 0.37

SUBSTRATE

ddd M Z X Y

eee M Z

DETAIL A

Øb (118 PLACES)

DETAIL B

MOLD

CAP

ccc Z

A1

A2

A

(Reference LTC DWG # 05-08-1903 Rev B)

// bbb Z

26

1.9050

BGA Package

118-Lead (15mm × 15mm × 3.42mm)

Z

e

b

L

K

J

G

G

F

e

E

PACKAGE BOTTOM VIEW

H

D

C

B

A

DETAILS OF PIN #1 IDENTIFIER ARE OPTIONAL,

BUT MUST BE LOCATED WITHIN THE ZONE INDICATED.

THE PIN #1 IDENTIFIER MAY BE EITHER A MOLD OR

MARKED FEATURE

BALL DESIGNATION PER JESD MS-028 AND JEP95

7

TRAY PIN 1

BEVEL

!

PACKAGE IN TRAY LOADING ORIENTATION

LTMXXXXXX

µModule

1

2

3

4

5

6

7

8

9

10

11

12

7

SEE NOTES

PIN 1

BGA 118 1112 REV B

PACKAGE ROW AND COLUMN LABELING MAY VARY

AMONG µModule PRODUCTS. REVIEW EACH PACKAGE

LAYOUT CAREFULLY

6. SOLDER BALL COMPOSITION IS 96.5% Sn/3.0% Ag/0.5% Cu

5. PRIMARY DATUM -Z- IS SEATING PLANE

4

3

2. ALL DIMENSIONS ARE IN MILLIMETERS

NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994

COMPONENT

PIN “A1”

3

SEE NOTES

F

b

M

DETAIL A

LTM4601/LTM4601-1

Package Description

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

4601fe

6.9850

5.7150

4.4450

4.4450

5.7150

6.9850

�LTM4601/LTM4601-1

Package Description

Table 5. Pin Assignment (Arranged by Pin Number)

PIN ID

FUNCTION

PIN ID

FUNCTION

PIN ID

FUNCTION

PIN ID

FUNCTION

PIN ID

FUNCTION

PIN ID

FUNCTION

A1

VIN

B1

VIN

C1

VIN

D1

PGND

E1

PGND

F1

PGND

A2

VIN

B2

VIN

C2

VIN

D2

PGND

E2

PGND

F2

PGND

A3

VIN

B3

VIN

C3

VIN

D3

PGND

E3

PGND

F3

PGND

A4

VIN

B4

VIN

C4

VIN

D4

PGND

E4

PGND

F4

PGND

A5

VIN

B5

VIN

C5

VIN

D5

PGND

E5

PGND

F5

PGND

A6

VIN

B6

VIN

C6

VIN

D6

PGND

E6

PGND

F6

PGND

A7

INTVCC

B7

–

C7

–

D7

–

E7

PGND

F7

PGND

A8

PLLIN

B8

–

C8

–

D8

–

E8

–

F8

PGND

A9

TRACK/SS

B9

–

C9

–

D9

–

E9

–

F9

PGND

A10

RUN

B10

–

C10

–

D10

–

E10

–

F10

–

A11

COMP

B11

–

C11

–

D11

–

E11

–

F11

–

A12

MPGM

B12

fSET

C12

MARG0

D12

MARG1

E12

DRVCC

F12

VFB

PIN ID

FUNCTION

PIN ID

FUNCTION

PIN ID

FUNCTION

PIN ID

FUNCTION

PIN ID

FUNCTION

PIN ID

FUNCTION

G1

PGND

H1

PGND

J1

VOUT

K1

VOUT

L1

VOUT

M1

VOUT

G2

PGND

H2

PGND

J2

VOUT

K2

VOUT

L2

VOUT

M2

VOUT

G3

PGND

H3

PGND

J3

VOUT

K3

VOUT

L3

VOUT

M3

VOUT

G4

PGND

H4

PGND

J4

VOUT

K4

VOUT

L4

VOUT

M4

VOUT

G5

PGND

H5

PGND

J5

VOUT

K5

VOUT

L5

VOUT

M5

VOUT

G6

PGND

H6

PGND

J6

VOUT

K6

VOUT

L6

VOUT

M6

VOUT

G7

PGND

H7

PGND

J7

VOUT

K7

VOUT

L7

VOUT

M7

VOUT

G8

PGND

H8

PGND

J8

VOUT

K8

VOUT

L8

VOUT

M8

VOUT

G9

PGND

H9

PGND

J9

VOUT

K9

VOUT

L9

VOUT

M9

VOUT

G10

–

H10

–

J10

VOUT

K10

VOUT

L10

VOUT

M10

VOUT

G11

–

H11

–

J11

–

K11

VOUT

L11

VOUT

M11

VOUT

G12

PGOOD

H12

SGND

J12

VOSNS+/NC2*

K12

DIFFVOUT/NC2*

L12

VOUT_LCL

M12

VOSNS–/NC1*

*LTM4601-1 Only

4601fe

For more information www.linear.com/LTM4601

27

�LTM4601/LTM4601-1

Package Description

Table 6. Pin Assignment (Arranged by Pin Function)

PIN NAME

PIN NAME

A1

A2

A3

A4

A5

A6

VIN

VIN

VIN

VIN

VIN

VIN

D1

D2

D3

D4

D5

D6

PGND

PGND

PGND

PGND

PGND

PGND

B1

B2

B3

B4

B5

B6

VIN

VIN

VIN

VIN

VIN

VIN

C1

C2

C3

C4

C5

C6

VIN

VIN

VIN

VIN

VIN

VIN

E1

E2

E3

E4

E5

E6

E7

PGND

PGND

PGND

PGND

PGND

PGND

PGND

F1

F2

F3

F4

F5

F6

F7

F8

F9

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

G1

G2

G3

G4

G5

G6

G7

G8

G9

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

H1

H2

H3

H4

H5

H6

H7

H8

H9

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

PGND

28

PIN NAME

J1

J2

J3

J4

J5

J6

J7

J8

J9

J10

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

K1

K2

K3

K4

K5

K6

K7

K8

K9

K10

K11

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

L1

L2

L3

L4

L5

L6

L7

L8

L9

L10

L11

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

M1

M2

M3

M4

M5

M6

M7

M8

M9

M10

M11

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

PIN NAME

A7

A8

A9

A10

A11

A12

INTVCC

PLLIN

TRACK/SS

RUN

COMP

MPGM

B12

fSET

C12

MARG0

D12

MARG1

E12

DRVCC

F12

VFB

G12

PGOOD

H12

SGND

J12

VOSNS+/NC2*

K12

DIFFVOUT/NC3*

L12

VOUT_LCL

M12

VOSNS–/NC1*

*LTM4601-1 Only

PIN NAME

B7

B8

B9

B10

B11

-

C7

C8

C9

C10

C11

-

D7

D8

D9

D10

D11

-

E8

E9

E10

E11

-

F10

F11

-

G10

G11

-

H10

H11

-

J11

-

4601fe

For more information www.linear.com/LTM4601

�LTM4601/LTM4601-1

Revision History

(Revision history begins at Rev B)

REV

DATE

DESCRIPTION

PAGE NUMBER

B

01/10

Added Note 5

2, 4

C

03/12

Revised entire data sheet to include the BGA package.

D

02/14

Added SnPb BGA option

E

04/14

Added LTM4601-1 BGA package diagram and package information

1 to 30

1, 2

2

4601fe

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representaFor more

www.linear.com/LTM4601

tion that the interconnection

of its information

circuits as described

herein will not infringe on existing patent rights.

29

�LTM4601/LTM4601-1

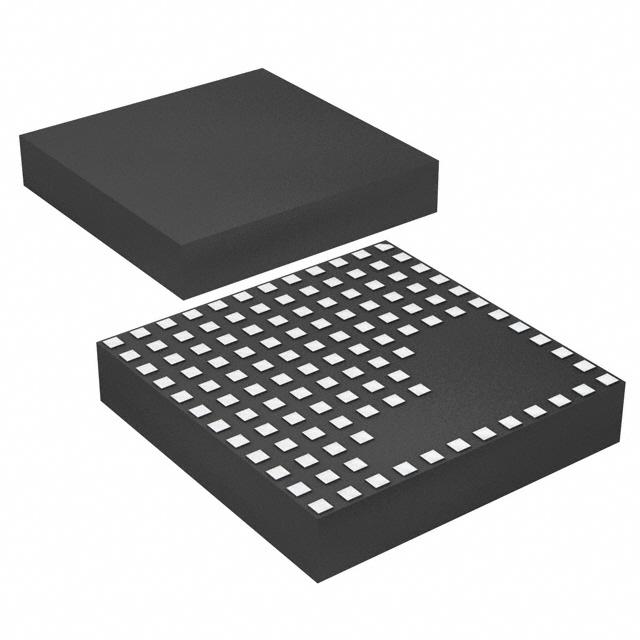

Package Photo

2.82mm

15mm

3.42mm

15mm

15mm

15mm

Related Parts

PART NUMBER DESCRIPTION

COMMENTS

LTM4628

26V, Dual 8A, DC/DC Step-Down μModule Regulator 4.5V ≤ VIN ≤ 26.5V, 0.6V ≤ VOUT ≤ 5V, Remote Sense Amplifier, Internal

Temperature Sensing Output, 15mm × 15mm × 4.32mm LGA

LTM4627

20V, 15A DC/DC Step-Down μModule Regulator

4.5V ≤ VIN ≤ 20V, 0.6V ≤ VOUT ≤ 5V, PLL Input, VOUT Tracking, Remote Sense

Amplifier, 15mm × 15mm × 4.32mm LGA

LTM4611

1.5VIN(MIN), 15A DC/DC Step-Down μModule

Regulator

1.5V ≤ VIN ≤ 5.5V, 0.8V ≤ VOUT ≤ 5V, PLL Input, Remote Sense Amplifier,

VOUT Tracking, 15mm × 15mm × 4.32mm LGA

LTM4613

8A EN55022 Class B DC/DC Step-Down μModule

Regulator

5V ≤ VIN ≤ 36V, 3.3V ≤ VOUT ≤ 15V, PLL Input, VOUT Tracking and Margining,

15mm × 15mm × 4.32mm LGA

LTM4601AHV

28V, 12A DC/DC Step-Down μModule Regulator

4.5V ≤ VIN ≤ 28V, 0.6V ≤ VOUT ≤ 5V, PLL Input, Remote Sense Amplifier,

VOUT Tracking and Margining, 15mm × 15mm × 2.82mm LGA or

15mm × 15mm × 3.42mm BGA

LTM4601A

20V, 12A DC/DC Step-Down μModule Regulator

4.5V ≤ VIN ≤ 20V, 0.6V ≤ VOUT ≤ 5V, PLL Input, Remote Sense Amplifier,

VOUT Tracking and Margining, 15mm × 15mm × 2.82mm LGA or

15mm × 15mm × 3.42mm BGA

LTM8027

60V, 4A DC/DC Step-Down μModule Regulator

4.5V ≤ VIN ≤ 60V, 2.5V ≤ VOUT ≤ 24V, CLK Input, 15mm × 15mm × 4.32mm LGA

LTM8032

36V, 2A EN55022 Class B DC/DC Step-Down

μModule Regulator

3.6V ≤ VIN ≤ 36V, 0.8V ≤ VOUT ≤ 10V, Synchronizable,

9mm × 15mm × 2.82mm LGA or 9mm × 15mm × 3.42mm BGA

LTM8061

32V, 2A Step-Down μModule Battery Charger with

Programmable Input Current Limit

Compatible with Single Cell or Dual Cell Li-Ion or Li-Poly Battery Stacks

(4.1V, 4.2V, 8.2V, or 8.4V), 4.95V ≤ VIN ≤ 32V, C/10 or Adjustable Timer Charge

Termination, NTC Resistor Monitor Input, 9mm × 15mm × 4.32mm LGA

30

This product contains technology licensed from Silicon Semiconductor Corporation.

Linear Technology Corporation

1630 McCarthy Blvd., Milpitas, CA 95035-7417

For more information www.linear.com/LTM4601

(408) 432-1900 ● FAX: (408) 434-0507

●

www.linear.com/LTM4601

®

4601fe

LT 0414 REV E • PRINTED IN USA

LINEAR TECHNOLOGY CORPORATION 2007

�