LTM4646

Dual 10A or

Single 20A µModule Regulator

FEATURES

n

n

n

n

n

n

n

n

n

n

n

n

n

n

n

n

DESCRIPTION

Dual 10A or Single 20A Output

Wide Input Voltage Range: 4.5V to 20V

n 2.375V

MIN with CPWR Bias

Output Voltage Range: 0.6V to 5.5V

±1.5% Maximum Total DC Output Error

Multiphase Current Sharing

Differential Remote Sense Amplifier, Each Channel

Current Mode Control/Fast Transient Response

Up to 96% Efficiency

Adjustable Switching Frequency (250kHz to 1.3MHz)

Frequency Synchronization

Overcurrent Foldback Protection

Output Overvoltage Protection

Internal or External Compensation

Built-In Temperature Monitoring Diode

SnPb or RoHS Compliant Finish

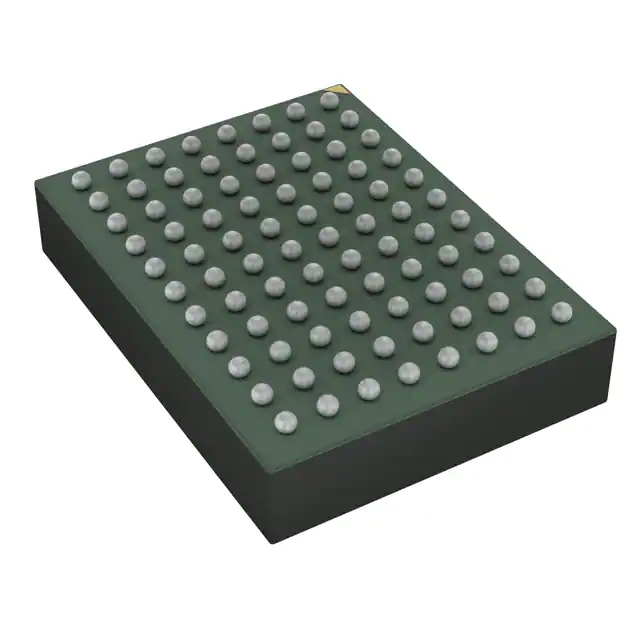

11.25mm × 15mm × 5.01mm BGA Package

The LTM®4646 is a complete dual 10A output switching

mode DC/DC power supply. Included in the package are

the switching controller, power FETs, inductors, and all

supporting components. Operating from an input voltage

range of 4.5V to 20V, the LTM4646 supports two outputs

each with an output voltage range of 0.6V to 5.5V, set by

external resistors. Its high efficiency design delivers up to

10A continuous current for each output. Only a few input

and output capacitors are needed.

The device supports frequency synchronization, multiphase

operation, high efficiency light load operation and output

voltage tracking for supply rail sequencing and has an

onboard temperature diode per channel for device temperature monitoring. High switching frequency and a current

mode architecture enable a very fast transient response to

line and load changes without sacrificing stability.

Fault protection features include overvoltage and overcurrent protection. The power module is offered in a small

footprint 11.25mm × 15mm × 5.01mm BGA package.

The LTM4646 is available with SnPb or RoHS compliant

terminal finish.

APPLICATIONS

n

n

n

n

Point-of-Load Power Supplies

Telecom and Networking Equipment

Industrial Equipment

Medical Equipment

All registered trademarks and trademarks are the property of their respective owners. Protected

by U.S. patents, including 5481178, 5847554, 6580258, 6304066, 6476589, 6774611.

Click to view associated TechClip Videos.

Efficiency, 12V to 0.9V,

1.2V at 10A Each

TYPICAL APPLICATION

95

10μF

×4

130k

VOUT1

0.9V

AT 10A

100μF

×4

VIN1 VIN2 CPWR

RUN1

RUN2

VOUT1

VOUTS1

VFB1

INTVCC

VRNG

MODE_PLLIN

DRVCC

4.7µF

LTM4646

60.4k

VOUTS1–

COMP1A

COMP1B

TRACK/SS1

FREQ

115k

VOUT2

1.2V

AT 10A

VOUT2

VOUTS2

VFB2

121k

0.1µF

90

SGND GND

VOUTS2–

COMP2A

COMP2B

TRACK/SS2

4646 TA01a

30.1k

100µF

×4

EFFICIENCY (%)

VIN

4.5V

TO 20V

85

80

75

70

PINS NOT USED IN THIS CIRCUIT:

PGOOD1, PGOOD2, EXTVCC,

0.1µF TEMP1+, TEMP1–, TEMP2+, TEMP2–

PHASMD, CLKOUT, SW1, SW2

12VIN TO 1.2V EFF, 500kHz

12VIN TO 0.9V EFF, 400kHz

1

2

3

4

5

6

7

8

OUTPUT CURRENT (A)

9

10

4646 TA01b

4646f

For more information www.linear.com/LTM4646

1

�LTM4646

ABSOLUTE MAXIMUM RATINGS

PIN CONFIGURATION

(Note 1)

CPWR, VIN1, VIN2 ....................................... –0.3V to 22V

VSW1, VSW2 ................................................... –2V to 22V

PGOOD1, PGOOD2, RUN1, RUN2, DRVCC,

INTVCC, EXTVCC, VOUT1, VOUT2, VOUTS1,

VOUTS2 ..................................................... –0.3V to 6V

TRACK/SS1, TRACK/SS2............................. –0.3V to 5V

FREQ, VRNG, PHASMD,

MODE_PLLIN ............................–0.3V to INTVCC+0.3

VOUTS1– (Note 6) ....................................... –0.3V to VFB1

VOUTS2– (Note 6) ..........................–0.3V to INTVCC+0.3V

COMP1A, COMP2A (Note 6) ..................... –0.3V to 2.7V

COMP1B, COMP2B, VFB1, VFB2 ................. –0.3V to 2.7V

DRVCC Peak Output Current .................................100mA

Internal Operating Temperature

Range (Note 2) .................................. –40°C to 125°C

Storage Temperature Range .................. –55°C to 125°C

Peak Solder Reflow Package Body Temperature .... 245°C

1

2

3

TOP VIEW

4

5

6

7

A

VIN2

TEMP2+

B

VOUT2

8

TEMP2–

GND

C

D

E

F

G

H

GND

–

SGND VOUTS2 RUN2

VRNG

COMP2B VOUTS2 COMP2A VFB2

EXTVCC

PGOOD2

MODE_

FREQ TRACK/SS2 PLLIN CLKOUT

COMP1B VOUTS1 COMP1A VFB1

SW2

CPWR

INTVCC

DRVCC

PGOOD1

PHASMD SGND TRACK/SS1 RUN1

VOUTS1–

SW1

GND

J

VOUT1

TEMP1–

K

GND

VIN1

TEMP1+

L

BGA PACKAGE

88-LEAD (15mm 11.25mm

5..01mm)

TJMAX = 125°C,

JCtop = 12.6°C/W, JCbottom = 1.8°C/W,

JB = 2.3°C/W, JA = 9.6°C/W

VALUES DEFINED PER JESD51-12

WEIGHT = 2.1g

ORDER INFORMATION

http://www.linear.com/product/LTM4646#orderinfo

PART MARKING*

PART NUMBER

LTM4646EY#PBF

LTM4646IY#PBF

LTM4646IY

BALL FINISH

SAC305 (RoHS)

SnPb (63/37)

DEVICE

FINISH CODE

LTM4646Y

LTM4646Y

LTM4646Y

• Consult Marketing for parts specified with wider operating temperature

ranges. *Device temperature grade is indicated by a label on the shipping

container. Ball finish code is per IPC/JEDEC J-STD-609.

• Terminal Finish Part Marking: www.linear.com/leadfree

2

e1

PACKAGE

TYPE

MSL

RATING

BGA

3

TEMPERATURE RANGE

(SEE NOTE 2)

–40°C to 125°C

e0

• Recommended BGA PCB Assembly and Manufacturing Procedures:

www.linear.com/umodule/pcbassembly

• BGA Package and Tray Drawings: www.linear.com/packaging

4646f

For more information www.linear.com/LTM4646

�LTM4646

ELECTRICAL CHARACTERISTICS

The l denotes the specifications which apply over the specified internal

operating temperature range (Note 2). Specified as each individual output channel. TA = 25°C, VIN = 12V and VRUN1, VRUN2 at 5V

unless otherwise noted. Per the typical application in Figure 18.

SYMBOL

PARAMETER

CONDITIONS

MIN

VIN(DC)

Input DC Voltage

2.375V with 5V External Bias on CPWR, 4.5V

Min without Bias

VCPWR(DC)

Input Control Power Voltage

Input Range of Bias

Normally Connected to VIN

VOUT1, 2 (Range)

Output Voltage Range

(Note 8)

VOUT1(DC),

VOUT2(DC)

Output Voltage, Total Variation

with Line and Load

CIN = 10µF 4, COUT = 100µF 4, Ceramic VOUT l

= 1.5V

RUN Pin On/Off Threshold

RUN Rising

l

l

TYP

MAX

UNITS

2.375

20

V

4.5

20

V

0.6

1.4775

5.5

V

1.5

1.5225

V

1.2

1.3

Input Specifications

VRUN1, VRUN2

1.1

VRUN1HYS, VRUN2HYS RUN Pin On Hysteresis

V

160

mV

100

kΩ

RRUN1, RRUN2

RUN1, RUN2 Resistance

Pull-Down Resistance

IINRUSH(VIN)

Input Inrush Current at Start-Up

IOUT = 0A, CIN = 10µF ×4, CSS = 0.01µF,

COUT = 100µF ×4, VOUT1 = 1.5V, VOUT2 = 1.5V,

VIN = 12V

1

A

IQ(VIN)

Input Supply Bias Current

IOUT = 0.1A, fSW = 1MHz, Pulse-Skipping Mode

IOUT = 0.1A, fSW = 1MHz, Switching Continuous

Shutdown, RUN = 0, VIN = 12V

17

35

40

mA

mA

µA

IS(VIN)

Input Supply Current

VIN = 4.5V, VOUT = 1.5V, IOUT = 10A, fSW = 1MHz

VIN = 12V, VOUT = 1.5V, IOUT = 10A, fSW = 1MHz

3.9

1.45

IOUT1(DC), IOUT2(DC)

Output Continuous Current Range

VIN = 12V, VOUT = 1.5V (Notes 7, 8)

∆VOUT1(LINE)/VOUT1

∆VOUT2(LINE)/VOUT2

Line Regulation Accuracy

∆VOUT1(LOAD)/VOUT1

∆VOUT2(LOAD)/VOUT2

Load Regulation Accuracy

A

A

Output Specifications

0

10

VOUT = 1.5V, VIN from 4.5V to 20V

IOUT = 0A for Each Output

l

0.01

0.025

For Each Output, VOUT = 1.5V, 0A to 10A

VIN = 12V (Note 7)

l

0.15

0.3

A

%/V

%

VOUT1(AC), VOUT2(AC) Output Ripple Voltage

For Each Output, IOUT = 0A, COUT = 100µF ×4,

VOUT = 1.5V, Frequency = 350kHz

15

mVP-P

fS (Each Channel)

Output Ripple Voltage Frequency

VIN = 12V, VOUT = 1.5V, RFREQ = 115kΩ (Note 4)

350

kHz

∆VOUTSTART

(Each Channel)

Turn-On Overshoot

COUT = 100µF ×4, VOUT = 1.5V, IOUT = 0A VIN =

12V, CSS = 0.01µF

10

mV

tSTART

(Each Channel)

Turn-On Time

COUT = 100µF ×4, No Load, TRACK/SS with

0.01µF to GND, VIN = 12V

5

ms

∆VOUT(LS)

(Each Channel)

Peak Deviation for Dynamic Load

Load: 0A to 6A to 0A

COUT = 100µF ×4

VIN = 12V, VOUT = 1.5V

50

mV

tSETTLE

(Each Channel)

Settling Time for Dynamic Load Step Load: 0A to 6A to 0A

COUT = 100µF ×4

VIN = 12V, VOUT = 1.5V

20

µs

IOUT(PK)

(Each Channel)

Output Current Limit

20

A

VIN = 12V, VOUT = 1.5V

4646f

For more information www.linear.com/LTM4646

3

�LTM4646

ELECTRICAL CHARACTERISTICS

The l denotes the specifications which apply over the specified internal

operating temperature range (Note 2). Specified as each individual output channel. TA = 25°C, VIN = 12V and VRUN1, VRUN2 at 5V

unless otherwise noted. Per the typical application in Figure 18.

SYMBOL

PARAMETER

CONDITIONS

VFB1

Voltage at VFB1 Pin

IOUT = 0A, VOUT = 1.5V

VFB2

Voltage at VFB2 Pin

IOUT = 0A, VOUT = 1.5V

VFB2 is Gained Back Up by 2x Internal to 0.6V

MIN

TYP

MAX

UNITS

l

0.592

0.600

0.608

V

l

0.296

0.3

0.304

V

0

±50

nA

l

l

0.630

0.315

0.645

0.323

0.660

0.330

V

V

Control Section

IFB1, IFB2

(Note 6)

VOVL1, VOVL2

Feedback Overvoltage Lockout

VFB1 Rising

VFB2 Rising

ITRACK/SS1,

ITRACK/SS2

Track Pin Soft-Start Pull-Up Current

TRACK/SS1,TRACK/SS2 = 0V

UVLO

INTVCC Undervoltage Lockout

INTVCC Falling VIN (Note 6)

INTVCC Rising VIN (Note 6)

tOFF(MIN)

Minimum Top Gate Off-Time

(Note 6)

tON(MIN)

Minimum Top Gate On-Time

(Note 6)

RFBHI1, RFBHI2

Resistor Between VOUTS1, VOUTS2

and VFB1, VFB2 Pins for Each Output

VPGOOD1, VPGOOD2

Low

PGOOD Voltage Low

IPGOOD = 2mA

IPGOOD

PGOOD Leakage Current

VPGOOD = 5V

VPGOOD

PGOOD Trip Level

VFB with Respect to Set Output Voltage

VFB Ramping Negative

VFB Ramping Positive

1.0

3.3

3.7

4.2

µA

4.5

90

ns

30

60.05

–2

V

V

ns

60.4

60.75

0.1

0.3

V

0

2

µA

–7.5

7.5

kΩ

%

%

Internal Linear Regulator

DRVCC

Internal DRVCC Voltage

6V < CPWR < 20V

DRVCC

Load Regulation

DRVCC Load Regulation

ICC = 0mA to 100mA

VEXTVCC

EXTVCC Switchover Voltage

EXTVCC Ramping Positive

VEXTVCC(DROP)

EXTVCC Dropout

ICC = 20mA, VEXTVCC = 5V

VEXTVCC(HYST)

EXTVCC Hysteresis

5.0

4.4

5.3

5.6

V

–1.3

–3.0

%

4.6

4.8

V

80

120

mV

200

mV

Frequency and Clock Synchronization

Frequency Nominal

Nominal Frequency

RFREQ = 115kΩ

Frequency Low

Lowest Frequency

RFREQ = 165kΩ (Note 5)

Frequency High

Highest Frequency

RFREQ = 29.4kΩ

RMODE_PLLIN

MODE_PLLIN Input Resistance

MODE_PLLIN to SGND

600

kΩ

Channel 2 Phase

VOUT2 Phase Relative to VOUT1

PHASMD = SGND

PHASMD = Float

PHASMD = INTVCC

180

180

240

Deg

Deg

Deg

CLKOUT Phase

Phase (Relative to VOUT1)

PHASMD = SGND

PHASMD = Float

PHASMD = INTVCC

60

90

120

Deg

Deg

Deg

VPLLIN High

VPLLIN Low

Clock Input High Level to MODE_PLLIN

Clock Input Low Level to MODE_PLLIN

4

300

350

400

250

1.17

2

1.3

kHz

kHz

1.43

0.5

MHz

V

V

4646f

For more information www.linear.com/LTM4646

�LTM4646

ELECTRICAL CHARACTERISTICS

The l denotes the specifications which apply over the specified internal

operating temperature range (Note 2). Specified as each individual output channel. TA = 25°C, VIN = 12V and VRUN1, VRUN2 at 5V

unless otherwise noted. Per the typical application in Figure 18.

SYMBOL

PARAMETER

CONDITIONS

MIN

fSYNC

(Each Channel)

Frequency SYNC Capture Range

MODE_PLLIN Clock Duty Cycle = 50%

250

VRNG ILIMIT

SET Current Limit

Per Channel

VRNG = INTVCC, IOUT to 10A, ILIMIT ~22A

VRNG = SGND, IOUT to 5A, ILIMIT ~11A

20

9

A

A

tD(PGOOD)

Delay from VFB Fault (OV/UV) to

PGOOD Falling

(Note 6)

50

μs

tD(PGOOD)

Delay from VFB Fault (OV/UV Clear)

to PGOOD

(Note 6)

20

μs

VTEMP1, VTEMP2

TC VTEMP1,2

TEMP Diode Voltage

ITEMP = 100µA

0.598

V

–2.0

mV/°C

VTEMP Temperature Coefficient

Note 1: Stresses beyond those listed under Absolute Maximum Ratings

may cause permanent damage to the device. Exposure to any Absolute

Maximum Rating condition for extended periods may affect device

reliability and lifetime.

Note 2: The LTM4646 is tested under pulsed load conditions such

that TJ ≈ TA. The LTM4646E is guaranteed to meet specifications from

0°C to 125°C internal temperature. Specifications over the –40°C to

125°C internal operating temperature range are assured by design,

characterization and correlation with statistical process controls. The

LTM4646I is guaranteed over the full –40°C to 125°C internal operating

temperature range. Note that the maximum ambient temperature

consistent with these specifications is determined by specific operating

conditions in conjunction with board layout, the rated package thermal

impedance and other environmental factors.

TYP

MAX

UNITS

1300

kHz

Note 3: Two outputs are tested separately and the same testing condition

is applied to each output.

Note 4: The switching frequency is programmable from 250kHz to 1.3MHz.

Note 5: LTM4646 device is optimized to operate from 300kHz to 750kHz.

Note 6: These parameters are tested at wafer sort.

Note 7: See output current derating curves for different VIN, VOUT and TA.

Note 8: For 6V ≤ VIN ≤ 20V, the 3.3 to 5V output current needs to be

limited to 9A/channel. All other input and output combinations are 10A/

channel with recommended switching frequency included in the efficiency

graphs. Derating curves and airflow apply.

4646f

For more information www.linear.com/LTM4646

5

�LTM4646

TYPICAL PERFORMANCE CHARACTERISTICS

95

95

95

90

90

90

85

3.3VOUT, 550kHz

2.5VOUT, 550kHz

1.8VOUT, 500kHz

1.5VOUT, 450kHz

1.2VOUT, 400kHz

1.0VOUT, 350kHz

0.9VOUT, 350kHz

80

75

70

1

2

3

4

5

6

7

8

OUTPUT CURRENT (A)

9

85

5.0VOUT, 900kHz

3.3VOUT, 850kHz

2.5VOUT, 750kHz

1.8VOUT, 600kHz

1.5VOUT, 550kHz

1.2VOUT, 475kHz

1.0VOUT, 400kHz

0.9VOUT, 400kHz

80

75

10

70

1

2

3

4

5

6

7

8

OUTPUT CURRENT (A)

10

85

5.0VOUT, 1.3MHz

3.3VOUT, 1.1MHz

2.5VOUT, 850kHz

1.8VOUT, 700kHz

1.5VOUT, 600kHz

1.2VOUT, 500kHz

1.0VOUT, 400kHz

0.9VOUT, 400kHz

80

75

70

1

2

3

4

5

6

7

8

OUTPUT CURRENT (A)

Dual Phase Single Output Efficiency

vs Output Current, VIN = 12V

9

10

4646 G03

4646 G02

4646 G01

100

9

EFFICIENCY (%)

100

EFFICIENCY (%)

100

100

EFFICIENCY (%)

Efficiency vs Output Current,

VIN = 12V

Efficiency vs Output Current,

VIN = 8V

Efficiency vs Output Current,

VIN = 5V

0.9V Single Phase Single Output

Load Transient Response

1V Single Phase Single Output

Load Transient Response

EXTVCC = 5V

EFFICIENCY (%)

95

90

85

5.0VOUT, 1.3MHz

3.3VOUT, 1.1MHz

2.5VOUT, 850kHz

1.8VOUT, 700kHz

1.5VOUT, 600kHz

1.2VOUT, 500kHz

1.0VOUT, 400kHz

0.9VOUT, 400kHz

80

75

70

2

4

6

8 10 12 14 16

OUTPUT CURRENT (A)

IOUT

5A/DIV

IOUT

5A/DIV

0.9VOUT

33mV/DIV

1VOUT

33mV/DIV

50µs/DIV

18

20

50µs/DIV

4646 G05

4646 G06

COUT = 470µF POSCAP, 5mΩ,

100µF ×4, CERAMIC

CCOMP = 100pF,

f = 350kHz

COUT = 470µF POSCAP, 5mΩ,

100µF ×4, CERAMIC

CCOMP = 100pF,

f = 350kHz

1.5V Single Phase Single Output

Load Transient Response

1.8V Single Phase Single Output

Load Transient Response

4646 G04

1.2V Single Phase Single Output

Load Transient Response

IOUT

5A/DIV

IOUT

IOUT

5A/DIV

5A/DIV

IOUT

5A/DIV

1.2VOUT

33mV/DIV

1.5V

1.5VOUT

OUT

33mV/DIV

33mV/DIV

1.8VOUT

33mV/DIV

50µs/DIV

COUT = 470µF POSCAP, 5mΩ,

100µF ×4, CERAMIC

CCOMP = 100pF,

f = 350kHz

6

4646 G07

50µs/DIV

50µs/DIV

4646

4646G08

G08

100µF ×3, CERAMIC

CERAMIC

CCOUT

OUT == 100µF

100pF,, C

CFF

COMP == 100pF

FF =

= 47pF

47pF

CCCOMP

450kHz

ff== 450kHz

50µs/DIV

4646 G09

COUT = 100µF ×3, CERAMIC

CCOMP = 100pF, CFF = 47pF

f = 500kHz

4646f

For more information www.linear.com/LTM4646

�LTM4646

TYPICAL PERFORMANCE CHARACTERISTICS

2.5V Single Phase Single Output

Load Transient Response

IOUT

5A/DIV

2.5VOUT

67mV/DIV

50µs/DIV

3.3V Single Phase Single Output

Load Transient Response

IOUT

3.3A/DIV

IOUT

3.3A/DIV

3.3VOUT

67mV/DIV

5VOUT

67mV/DIV

50µs/DIV

4646 G10

COUT = 100µF ×2, CERAMIC

CCOMP = 100pF, CFF = 47pF

f = 500kHz

Single Phase Single Output

Start-Up, No Load

50ms/DIV

Single Phase Single Output

Start-Up, 10A Load

Two-Phase Switching and Ripple

VOUT

5V/DIV

VOUT

10mV/DIV

20ms/DIV

4646 G13

12VIN, 1.5VOUT AT NO LOAD

COUT = 470µF ×1, 2.5V, SANYO POSCAP,

100µF ×4, 6.3V, CERAMIC

SOFT-START CAPACITOR = 0.1µF

USE RUN PIN TO CONTROL START-UP

4646 G12

COUT = 100µF ×1, CERAMIC

CCOMP = 100pF, CFF = 47pF

f = 950kHz

IOUT

6.7A/DIV

IOUT

6.7A/DIV

50µs/DIV

4646 G11

COUT = 100µF ×1, CERAMIC

CCOMP = 100pF, CFF = 47pF

f = 750kHz

VOUT

0.5V/DIV

VOUT

0.5V/DIV

5V Single Phase Single Output

Load Transient Response

1µs/DIV

4646 G14

12VIN, 1.5VOUT AT 10A LOAD

COUT = 470µF ×1, 2.5V, SANYO POSCAP,

100µF ×4, 6.3V, CERAMIC

SOFT-START CAPACITOR = 0.1µF

USE RUN PIN TO CONTROL START-UP

Short-Circuit Protection, No Load

VOUT

500mV/DIV

4646 G15

12V TO 1V AT 20A TWO-PHASE

12V TO 1V AT 350kHz

RIPPLE AT 20A LOAD

COUT = 330μF, 9mΩ, 100μF ×4, CERAMIC

Short-Circuit Protection, 10A Load

VOUT

500mV/DIV

IIN

1A/DIV

IIN

1A/DIV

VIN = 12V

VOUT = 1.5V

IOUT = NO LOAD

20ms/DIV

20ms/DIV

4646 G16

4646 G17

VIN = 12V

VOUT = 1.5V

IOUT = 10A

4646f

For more information www.linear.com/LTM4646

7

�LTM4646

PIN FUNCTIONS

(Recommended to Use Test Points to Monitor Signal Pin Connections.)

PACKAGE ROW AND COLUMN LABELING MAY VARY

AMONG µModule PRODUCTS. REVIEW EACH PACKAGE

LAYOUT CAREFULLY.

VOUT1 (H1, J1-J2, K1-K2, L1-L2): Power Output Pins.

Apply output load between these pins and GND pins.

Recommend placing output decoupling capacitance

directly between these pins and GND pins. There is a

49.9Ω resistor connected between VOUT1 and VOUTS1 to

protect the output from an open VOUTS1. Review Table 5.

See Note 8 in the Electrical Characteristics section for

output current guideline.

GND (A3, A6-A7, B3, B6-B7, C3-C7, D6-D7, E6, E8, F5,

F7, G6, G8, H6-H7, J4-J7, K3, K6-K7, L3, L6-L7 ): Power

Ground Pins for Both Input and Output Returns.

VOUT2 (A1-A2, B1-B2, C1-C2, D1): Power Output Pins.

Apply output load between these pins and GND pins.

Recommend placing output decoupling capacitance

directly between these pins and GND pins. There is a

49.9Ω resistor connected between VOUT2 and VOUTS2 to

protect the output from an open VOUTS2. Review Table 5.

See Note 8 in the Electrical Characteristics section for

output current guideline.

VOUTS1, VOUTS2 (G2, E2): These pins are connected to

the top of the internal top feedback resistor for each output. Each pin can be directly connected to its specific

output, or connected to the remote sense point of VOUT.

It is important to connect these pins to their designated

outputs for proper regulation.

In paralleling modules, the VOUTS1 pin is left floating, and

the VFB1 pin is connected to INTVCC. This will disable channel 1’s error amplifier and internally connect COMP1A to

COMP2A. The PGOOD1 and TRACK/SS1 will be disabled

in this mode. Channel 2’s error amplifier will regulate the

two channel single output. See VFB pin description and

Applications Information section.

FREQ (F1): Frequency Set Pin. A resistor from this pin to

SGND sets the operating frequency. The Equation:

41550

f(kHz)

8

– 2.2 = RFREQ (kΩ)

An external clock applied to MODE_PLLIN should be

within ±30% of this programmed frequency to ensure

frequency lock. See the Applications Information section.

SGND (D3, H3): Signal Ground Pin. Return ground path

for all analog and low power circuitry. Tie a single connection to the output capacitor GND in the application.

See layout guidelines in Figure 17.

VFB1 (G4): This pin is the + input to a unity gain differential amplifier. This pin is connected to VOUTS1 with a 60.4k

precision resistor internal. Different output voltages can be

programmed with an additional resistor between VFB1 and

VOUTS1– pins. The differential amplifier is feeding back the

divided down output voltage from a remote sense divider

network to compare to the internal 0.6V reference. In 2-phase

single output operation, tie the VFB1 pin to INTVCC. See

Figure 1 and Applications Information section for details.

VFB2 (E4): This pin is the + input to a non-inverting gain

of two amplifier utilizing three resistors in the feedback

network to develop a remote sense divider network. This

pin is connected to VOUTS2 with an internal 60.4k precision resistor. The VOUT2 voltage is divided down to 0.3V

then gained back up to 0.6V to compare with the internal

0.6V reference. This technique provides for equivalent

remote sensing on VOUT2. See Figure 1 and Applications

Information section for details.

TRACK/SS1,TRACK/SS2 (H4, F2): Output Voltage Tracking

Pin and Soft-Start Inputs. Each channel has a 1.0μA pull-up

current source. Each pin can be programmed with a softstart ramp rate up to the 0.6V internal reference level, then

beyond this point the internal 0.6V reference will control the

feedback loop. When one channel is configured to be master

of the two channels, then a capacitor from this pin to ground

will set the soft-start ramp rate. The remaining channel can

be set up as the slave, and have the master’s output applied

through a voltage divider to the slave output’s track pin. This

voltage divider is equal to the slave output’s feedback divider

for coincidental tracking. See the Applications Information

section. (Recommended to use test points to monitor signal

pin connections.)

DRVCC (G7): Internal 5.3V regulator output used to source

the power MOSFET drivers, and supply power to the

INTVCC input. A 4.7µF ceramic capacitor is needed on

this pin to GND.

4646f

For more information www.linear.com/LTM4646

�LTM4646

PIN FUNCTIONS

(Recommended to Use Test Points to Monitor Signal Pin Connections.)

CPWR (F8): Input Power to the Control IC, and Power

to the DRVCC Regulator. This pin is connected to VIN for

normal 4.5V to 20V operation. For lower voltage inputs

below 4.5V, CPWR can be powered with an external 5V

bias. See Application section.

COMP1A, COMP2A (G3, E3): Current Control Threshold.

These pins are the output of the error amplifier and the

switching regulator’s compensation point. The current

comparator threshold increases with this control voltage.

The voltage ranges from 0V to 2.4V.

COMP1B, COMP2B (G1, E1): Internal Compensation

Network .These pins are to be connected to their respected

COMPA pins. When Utilizing specific external compensation, then float these pins.

MODE_PLLIN (F3): Operation Mode Selection or External

Clock Synchronization Input. When this pin is tied to INTVCC,

forced continuous mode operation is selected. Tying this pin

to SGND allows discontinuous mode operation. When an

external clock is applied at this pin, both channels operate

in forced continuous mode and synchronize to the external

clock. This pin has an internal 600k pull-down resistor to

SGND. An external clock applied to MODE_PLLIN should

be within ±30% of this programmed frequency to ensure

frequency lock.

CLKOUT (F4): Clock output with phase control using the

PHASMD pin to enable multiphase operation between

devices. Its output level swings between INTVCC and SGND.

If clock input is present at the MODE_PLLIN pin, it will

be synchronized to the input clock, with phase set by the

PHASMD pin. If no clock is present at MODE_PLLIN, its

frequency will be set by the FREQ pin. To synchronize other

controllers, it can be connected to their MODE_PLLIN pins.

See the Applications Information section.

RUN1, RUN2 (H5, D5): Run Control Pins. A voltage above

1.3V will turn on each channel in the module. A voltage below

1.0V on the RUN pin will turn off the related channel. Each

RUN pin has a 1.2μA pull-up current, once the RUN pin

reaches 1.2V an additional 4.5μA pull-up current is added

to this pin. A 100k resistor to ground is internal, and can be

used with a pull-up resistor to VIN to turn on the module using

the external and internal resistor to program under voltage

lockout. Otherwise, an external enable signal or source can

drive these pins directly below the 6V max. Enabling either

RUN pin will turn on the DRVCC, and turn on the INTVCC path

for operation. See Figure 1 and Applications section.

PHASMD (H2): Connect this pin to SGND, INTVCC, or

floating this pin to select the phase of CLKOUT and channel 2. See Electrical Characteristics table and Application

section.

PGOOD1, PGOOD2 (G5, E5): Output Voltage Power Good

Indicator. Open-drain logic output that is pulled to ground

when the output voltage is not within ±7.5% of the regulation point. See Applications section.

INTVCC (F6): Supply Input for Internal Circuitry (Not

Including Gate Drivers). This bias is derived from DRVCC

internally.

EXTVCC (E7): External Power Input. When EXTVCC exceeds

the switchover voltage (typically 4.6V), an internal switch

connects this pin to DRVCC and shuts down the internal

regulator so that INTVCC and gate drivers draw power

from EXTVCC. The VIN pin still needs to be powered up

but draws minimum current.

TEMP1+,TEMP1– and TEMP2+, TEMP2– (L8, K8 and

B8, A8): Onboard temperature diode for monitoring each

channel with differential connections for noise immunity.

VIN1 (K4-K5, L4-L5) and VIN2 (A4-A5, B4-B5): Power

Input Pins. Apply input voltage between these pins and

GND pins. Recommend placing input decoupling capacitance directly between VIN pins and GND pins.

VOUTS1– (J3): Differential Output Sense Amplifier (–) Input

of channel 1. Connect this pin to the negative terminal of

the output load capacitor of VOUT1.

VOUTS2– (D4): Differential Output Sense Amplifier (–)

Input of channel 2. Connect this pin to the negative terminal of the output load capacitor of VOUT2.

SW1 (H8, J8) and SW2 (C8, D8): Switching node of each

channel that is used for testing purposes. Also an R-C

snubber network can be applied to reduce or eliminate

switch node ringing, or otherwise leave floating. See the

Applications Information section.

VRNG (D2): Current Limit Adjustment Range. Tying this

pin to INTVCC sets full 10A current, or tying to SGND will

lower the current limit to 5A. Default to INTVCC.

For more information www.linear.com/LTM4646

4646f

9

�LTM4646

BLOCK DIAGRAM

CPWR

EXTVCC

DRVCC

LDO

DRVCC

4.7µF

CPWR

VIN

DRVCC

1µF

2Ω

VIN

1µF

TOP G

INTVCC

COMP1B

RUN1 AND RUN2

SEPARATE:

RPULLUP =

(

INTVCC

–

gm +

+

RUN1

100k

VFB1

+

–

RUN2

)

VIN(MIN) • 100k

1.3

SGND

130k

– 50k

POWER

CONTROL

LOGIC

BLOCK

MODE_PLLIN

( )

PHASMD

tSOFT-START =

VOUT1

1µA

0.645V

VFB1

470pF

–

VIN

MTOP2

SW2

0.47µH

GATE

DRIVE

50k

VOUT2

CIN4

10µF

25V

VOUT2 1.2V/10A

+

VFB2

0.6V

COUT2

+

–

TRACK/SS2

–

0.645V

PGOOD2 VFB1

+

BLOCK

–

+ 0.555V

VOUTS2–

x2

+

–

gm +

+

R7

50k

–

SGND

PGOOD2

CIN3

10µF

25V

GND

INTERNAL

COMP

1µA

GND

1µF

MBOT2

COMP2B

SS

TEMP SENSOR

TEMP1–

C8

1µF

DRVCC

COMP2A

TEMP1+

PGOOD1

+ PGOOD1

BLOCK

–

+

0.555V

VIN

CSS

SGND

VOUTS1

PNP

CSS

• 0.6V

1µA

TRACK/SS1

CSS

60.4k

LOCATED NEAR POWER STAGES

FREQ

SGND

VFB1

49.9Ω

( )

RFB1

40.2k

×1

115k

VRNG

350kHz INTVCC

SGND

VOUTS1–

SS

CLKOUT

41550

RFREQ =

– 2.2

f(kHz)

0.6V

REF

SGND

100k

– 100k

COUT1

GND

+

1.3

)

1.5V/10A

+

1µF

MBOT1

–

VIN(MIN) • 50k

BOT G

VOUT1

INTERNAL

COMP

VIN

100µF

25V

SW1

0.47µH

GATE

DRIVE

COMP1A

(

GND

MTOP1

1µF

RUN1 AND RUN2

TIED TOGETHER:

RPULLUP =

VIN 4.5V TO 20V

CIN1

CIN2 +

10µF

10µF

25V

25V

0.6V REF

VFB2

0.3V

VOUT2

SGND

49.9Ω

RFB3

30.1k

SGND

60.4k

VOUTS2

LOCATED NEAR

POWER STAGES

PNP

RFB2

60.4k

SEE FIGURE 18

TEMP2+

470pF

TEMP2–

TEMP SENSOR

4646 F01

Figure 1. Simplified LTM4646 Block Diagram

10

4646f

For more information www.linear.com/LTM4646

�LTM4646

DECOUPLING REQUIREMENTS

TA = 25°C. Use Figure 1 configuration.

SYMBOL

PARAMETER

CONDITIONS

CIN1, CIN2

CIN3, CIN4

External Input Capacitor Requirement

(VIN = 4.5V to 20V, VOUT1 = 1.5V)

(VIN = 4.5V to 20V, VOUT2 = 1.5V)

MIN

IOUT1 = 10A

IOUT2 = 10A

COUT1

COUT2

External Output Capacitor Requirement

(VIN = 4.5V to 20V, VOUT1 = 1.5V)

(VIN = 4.5V to 20V, VOUT2 = 1.5V)

IOUT1 = 10A (Note 8)

IOUT2 = 10A (Note 8)

10μF ×2 (Note 8)

10μF ×2 (Note 8)

TYP

MAX

UNITS

20

20

µF

µF

400

400

µF

µF

OPERATION

Power Module Description

The LTM4646 is a dual-output standalone non-isolated

switching mode DC/DC power supply. It can provide two

10A outputs with few external input and output capacitors

and setup components. This module provides precisely

regulated output voltages programmable via external

resistors from 0.6VDC to 5.5VDC over 4.5V to 20V input

voltages. The typical application schematic is shown in

Figure 18. See Note 8 in the Electrical Characteristics section for output current guideline.

The LTM4646 has dual integrated controlled-on time current mode regulators and built-in power MOSFET devices

with fast switching speed. The controlled on-time, valley

current mode control architecture, allows for not only

fast response to transients without clock delay, but also

constant frequency switching at steady load condition.

The typical switching frequency is 400kHz. For switchingnoise sensitive applications, it can be externally synchronized from 250kHz to 1.3MHz. A resistor can be used to

program a free run frequency on the FREQ pin. See the

Applications Information section.

With current mode control and internal feedback loop

compensation, the LTM4646 module has sufficient stability margins and good transient performance with a wide

range of output capacitors, even with all ceramic output

capacitors. Optimized external compensation is supported

by disconnecting the internal compensation.

Current mode control provides cycle-by-cycle fast current

limit and foldback current limit in an overcurrent condition. Internal overvoltage and undervoltage comparators

pull the open-drain PGOOD outputs low if the output feedback voltage exits a ±7.5% window around the regulation

point. As the output voltage exceeds 7.5% above regulation, the bottom MOSFET will turn on to clamp the output

voltage. The top MOSFET will be turned off. This overvoltage protect is feedback voltage referred.

Pulling the RUN pins below 1.3V forces the regulators

into a shutdown state, by turning off both MOSFETs.

The TRACK/SS pins are used for programming the output voltage ramp and voltage tracking during start-up or

used for soft-starting the regulator. See the Applications

Information section. The LTM4646 is internally compensated to be stable over all operating conditions. Table 5

provides a guideline for input and output capacitances

for several operating conditions. The LTpowerCAD® will

be provided for transient and stability analysis. The VFB1

pin is used to program the channel 1 output voltage with

a single external resistor to ground, and VFB2 pin requires

two resistors to program the output. Both channel 1 and 2

have remote sense capability.

Multiphase operation can be easily employed with the

MODE_PLLIN, PHASMD, and CLKOUT pins. Up to 6

phases can be cascaded to run simultaneously with

respect to each other by programming the PHASMD pin to

different levels. See the Applications Information section.

High efficiency at light loads can be accomplished

with selectable pulse-skipping operation using the

MODE_PLLIN. These light load features will accommodate

battery operation. Efficiency graphs are provided for light

load operation in the Typical Performance Characteristics

section. Each channel has temperature diode included

inside the module to monitor the temperature of the

module. See the Applications Information section for

details.

4646f

For more information www.linear.com/LTM4646

11

�LTM4646

APPLICATIONS INFORMATION

The typical LTM4646 application circuit is shown in

Figure 18. External component selection is primarily

determined by the maximum load current and output

voltage. Refer to Table 5 for specific external capacitor

requirements for particular applications.

The Thevenin equivalent of the VOUT2 equation would

be the 0.6V with a series resistance of (60.4k || RFB2),

thus RFB3 connected to the series resistance would be

(60.4k || RFB2) to equal the 0.3V reference.

Table 1. VFB1, VFB2, Resistor Table vs Various Output Voltages

VIN to VOUT Step-Down Ratios

There are restrictions in the maximum VIN and VOUT stepdown ratio that can be achieved for a given input voltage.

Each output of the LTM4646 is capable of a wide duty

cycle that is limited by the minimum on-time tON(MIN) of

30ns defined as tON(MIN) < D/fSW for narrow duty cycle,

where D is duty cycle (VOUT/VIN) and fSW is the switching frequency. The minimum off-time of 90ns tOFF(MIN)