LTM9012

Quad 14-Bit, 125Msps ADC

with Integrated Drivers

Features

Description

4-Channel Simultaneous Sampling ADC with

Integrated, Fixed Gain, Differential Drivers

n 68.3dB SNR

n 78dB SFDR

n Low Power: 1.27W Total, 318mW per Channel

n 1.8V ADC Core and 3.3V Analog Input Supply

n Serial LVDS Outputs: 1 or 2 Bits per Channel

n Shutdown and Nap Modes

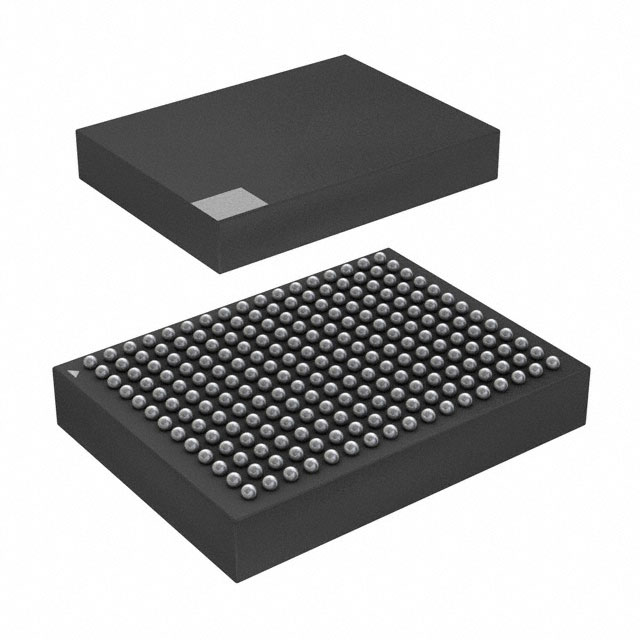

n 11.25mm × 15mm BGA Package

The LTM®9012 is a 4-channel, simultaneous sampling

14-bit µModule® analog-to-digital converter (ADC) with

integrated, fixed gain, differential ADC drivers. The low

noise amplifiers are suitable for single-ended drive and

pulse train signals such as imaging applications. Each

channel includes a lowpass filter between the driver output and ADC input.

n

DC specs include ±1.2LSB INL (typ), ±0.3LSB DNL (typ)

and no missing codes over temperature. The transition

noise is a low 1.2LSBRMS.

Applications

n

n

n

n

The digital outputs are serial LVDS and each channel outputs two bits at a time (2-lane mode). At lower sampling

rates there is a one bit option (1-lane mode). The LVDS

drivers have optional internal termination and adjustable

output levels to ensure clean signal integrity.

Industrial Imaging

Medical Imaging

Multichannel Data Acquisition

Nondestructive Testing

L, LT, LTC, LTM, Linear Technology, the Linear logo and µModule are registered trademarks of

Linear Technology Corporation. All other trademarks are the property of their respective owners.

The ENC+ and ENC– inputs may be driven differentially

or single-ended with a sine wave, PECL, LVDS, TTL or

CMOS inputs. An internal clock duty cycle stabilizer allows high performance at full speed for a wide range of

clock duty cycles.

Typical Application

Single-Ended Sensor Digitization

3.3V

1.8V

1.8V

VCC

VDD

OVDD

IMAGE

SENSOR

•

•

•

PIPELINE

ADC

PIPELINE

ADC

PIPELINE

ADC

VREF

0

LTM9012

–10

–20

14

14

DATA

CHANNEL 1

SERIALIZER

ENCODER

AND

CHANNEL 2

LVDS

DRIVERS

14

–30

FPGA

CHANNEL 3

AMPLITUDE (dBFS)

PIPELINE

ADC

LTM9012, 125Msps, 70MHz FFT

–40

–50

–60

–70

–80

–90

CHANNEL 4

14

INTERNAL

REFERENCE & SUPPLY

BYPASS CAPACITORS

ENCODE CLOCK

FR+

–110

FR–

–120

DCO+

PLL

SCK SDI SDO CS PAR/SER ENC+

–100

ENC–

DCO–

0

5 10 15 20 25 30 35 40 45 50 55 60

FREQUENCY (MHz)

9012 TA01b

9012 TA01a

9012fa

For more information www.linear.com/LTM9012

1

�LTM9012

Absolute Maximum Ratings

Pin Configuration

(Notes 1, 2)

Supply Voltages

VDD, OVDD................................................. –0.3V to 2V

VCC........................................................ –0.3V to 5.5V

Analog Input Voltage (CHn +, CHn –, SHDNn )

(Note 3)........................................................–0.3V to VCC

Analog Input Voltage (PAR/SER, SENSE)

(Note 4)......................................... –0.3V to (VDD + 0.2V)

Digital Input Voltage (ENC +, ENC –, CS, SDI, SCK)

(Note 5)...................................................... –0.3V to 3.9V

SDO (Note 5)............................................. –0.3V to 3.9V

Digital Output Voltage................. –0.3V to (OVDD + 0.3V)

Operating Temperature Range

LTM9012C................................................ 0°C to 70°C

LTM9012I.............................................–40°C to 85°C

Storage Temperature Range................... –65°C to 150°C

TOP VIEW

1

2

3

4

CH4+ CH4–

5

6

CH3+ CH3–

7

8

9

10

CH2+ CH2–

11

12

13

CH1+ CH1–

A

B

VCC3

SHDN3

VCC2

C

SHDN2

D

E

F

SHDN4

VCC4

SHDN1

G

VCC1

H

J

K

L

SDI

VDD

ENC+

ENC –

CS

OUT4B –

OUT4B+

SENSE

M

VDD

N

SDO

PAR/SER

P

REF

Q

OUT1A+

OUT1A–

R

S

FR–

OUT4A–

OUT3A–

OUT4A+

OUT3A+

OUT3B–

FR+

SCK

OUT3B+

DCO– DCO+

OVDD

OUT2A–

OUT2A+

BGA PACKAGE

221-LEAD (15mm × 11.25mm)

OUT1B+

OUT2B+

OUT1B–

OUT2B–

ALL ELSE = GND

TJMAX = 125°C, θJA = 16.5°C/W, θJCtop = 15°C/W,

θJCbottom = 6.3°C/W, θJBOARD = 10.4°C/W

θ VALUES DETERMINED PER JESD 51-9

WEIGHT = 1.07g

Order Information

http://www.linear.com/product/LTM9012#orderinfo

LEAD FREE FINISH

TRAY

PART MARKING*

PACKAGE DESCRIPTION

TEMPERATURE RANGE

LTM9012CY-AB#PBF

LTM9012CY-AB#PBF

LTM9012YAB

221-Lead (15mm × 11.25mm) Plastic BGA

0°C to 70°C

LTM9012IY-AB#PBF

LTM9012IY-AB#PBF

LTM9012YAB

221-Lead (15mm × 11.25mm) Plastic BGA

–40°C to 85°C

Consult LTC Marketing for parts specified with wider operating temperature ranges. *The temperature grade is identified by a label on the shipping container.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through

designated sales channels with #TRMPBF suffix.

9012fa

2

For more information www.linear.com/LTM9012

�LTM9012

Converter

Characteristics l denotes the specifications which apply over the full operating

The

temperature range, otherwise specifications are at TA = 25°C. (Note 6)

PARAMETER

CONDITIONS

MIN

Resolution (No Missing Codes)

l

14

TYP

MAX

UNITS

Bits

Integral Linearity Error

Differential Analog Input (Note 7)

l

–5

±1.2

5

LSB

Differential Linearity Error

Differential Analog Input

l

–0.9

±0.3

0.9

LSB

Offset Error

(Note 8)

l

–37

±3

37

mV

Gain Error

Internal Reference

External Reference

l

–3.6

–1.3

–1.3

3.0

%FS

%FS

Offset Drift

±20

µV/°C

Full-Scale Drift

Internal Reference

External Reference

±35

±25

ppm/°C

ppm/°C

Gain Matching

External Reference

±0.2

%FS

±3

mV

1.2

LSBRMS

Offset Matching

Transition Noise

External Reference

Analog

Input l denotes the specifications which apply over the full operating temperature range, otherwise

The

specifications are at TA = 25°C. (Note 6)

SYMBOL

PARAMETER

CONDITIONS

VIN

Differential Analog Input Range (CH+ – CH – )

LTM9012-AB

VIN(CM)

Analog Input Common Mode (CH+ + CH – )/2

Differential Analog Input (Note 9)

VSENSE

External Voltage Reference Applied to SENSE External Reference Mode

RIN

Differential Input Resistance

LTM9012-AB

at –1dBFS

MIN

TYP

MAX

UNITS

0.2

l

VP-P

0 to 1.5

l

0.625

1.250

V

1.300

V

100

Ω

IIN(P/S)

Input Leakage Current

0 < PAR/SER < VDD

l

–3

3

µA

IIN(SENSE)

Input Leakage Current

0.625V < SENSE < 1.3V

l

–6

6

µA

tAP

Sample-and-Hold Acquisition Delay Time

0

0.15

ns

tJITTER

Sample-and-Hold Acquisition Delay Jitter

CMRR

Analog Input Common Mode Rejection Ratio

90

psRMS

dB

BW-3dB

3dB Corner of Internal Lowpass Filter

90

MHz

Dynamic

Accuracy l denotes the specifications which apply over the full operating temperature range,

The

otherwise specifications are at TA = 25°C. (Note 6)

SYMBOL

PARAMETER

CONDITIONS

SNR

Signal-to-Noise Ratio

70MHz Input

SFDR

Spurious Free Dynamic Range

2nd or 3rd Harmonic

70MHz Input

Spurious Free Dynamic Range

4th Harmonic or Higher

S/N+D

MIN

TYP

MAX

UNITS

l

66.5

68.3

dBFS

l

66.9

78

dBFS

70MHz Input

l

76.9

86

dBFS

l

64.7

Signal-to-Noise Plus Distortion Ratio

70MHz Input

66.7

dBFS

Crosstalk, Near Channel

10MHz (Note 12)

70

dBc

Crosstalk, Far Channel

10MHz (Note 12)

90

dBc

9012fa

For more information www.linear.com/LTM9012

3

�LTM9012

Internal

Reference Characteristics l denotes the specifications which apply over the

The

full operating temperature range, otherwise specifications are at TA = 25°C.

PARAMETER

CONDITIONS

MIN

TYP

MAX

VREF Output Voltage

IOUT = 0

1.225

1.250

1.275

VREF Output Temperature Drift

UNITS

V

±25

VREF Output Resistance

–400μA < IOUT < 1mA

VREF Line Regulation

1.7V < VDD < 1.9V

ppm/°C

7

Ω

0.6

mV/V

Digital

Inputs and Outputs l denotes the specifications which apply over the full operating

The

temperature range, otherwise specifications are at TA = 25°C. (Note 6)

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

ENCODE INPUTS (ENC+, ENC–)

Differential Encode Mode (ENC– Not Tied to GND)

VID

Differential Input Voltage

(Note 9)

l

0.2

VICM

Common Mode Input Voltage

Internally Set

Externally Set (Note 9)

l

1.1

l

0.2

VIN

Input Voltage Range

ENC+, ENC– to GND

RIN

Input Resistance

(See Figure 3)

CIN

Input Capacitance

V

1.2

1.6

V

V

3.6

V

10

kΩ

3.5

pF

Single-Ended Encode Mode (ENC– Tied to GND)

VIH

High Level Input Voltage

VDD = 1.8V

1.26

V

VIL

Low Level Input Voltage

VDD = 1.8V

0.54

V

VIN

Input Voltage Range

ENC+ to GND

0 to 3.6

RIN

Input Resistance

(See Figure 4)

30

kΩ

CIN

Input Capacitance

3.5

pF

V

Digital Inputs (CS, SDI, SCK in Serial or Parallel Programming Mode. SDO in Parallel Programming Mode)

VIH

High Level Input Voltage

VDD = 1.8V

l

VIL

Low Level Input Voltage

VDD = 1.8V

l

IIN

Input Current

VIN = 0V to 3.6V

l

CIN

Input Capacitance

1.3

V

–10

0.6

V

10

µA

3

pF

200

Ω

SDO Output (Serial Programming Mode. Open-Drain Output. Requires 2k Pull-Up Resistor if SDO is Used)

ROH

Logic Low Output Resistance to GND

VDD = 1.8V, SDO = 0V

IOH

Logic High Output Leakage Current

SDO = 0V to 3.6V

COUT

Output Capacitance

l

–10

10

3

µA

pF

Digital Input (SHDN)

VIH

High Level Input Voltage

VCC = 3.3V

l

VIL

Low Level Input Voltage

VCC = 3.3V

l

0.6

0.97

0.95

1.4

V

RSHDN

SHDN Pull-Up Resistor

VSHDN = 0V to 0.5V

l

90

150

210

kΩ

mV

mV

V

Digital Data Outputs

VOD

Differential Output Voltage

100Ω Differential Load, 3.5mA Mode

100Ω Differential Load, 1.75mA Mode

l

l

247

125

350

175

454

250

VOS

Common Mode Output Voltage

100Ω Differential Load, 3.5mA Mode

100Ω Differential Load, 1.75mA Mode

l

l

1.125

1.125

1.250

1.250

1.375

1.375

RTERM

On-Chip Termination Resistance

Termination Enabled, OVDD = 1.8V

100

V

V

Ω

9012fa

4

For more information www.linear.com/LTM9012

�LTM9012

Power

Requirements l denotes the specifications which apply over the full operating temperature

The

range, otherwise specifications are at TA = 25°C. (Note 6)

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

VDD

ADC Supply Voltage

(Note 10)

l

1.7

1.8

1.9

UNITS

V

OVDD

ADC Output Supply Voltage

(Note 10)

l

1.7

1.8

1.9

V

VCC

Amplifier Supply Voltage

(Note 10)

l

2.7

3.3

3.6

V

IVDD

ADC Supply Current

Sine Wave Input

l

298

320

mA

IOVDD

ADC Output Supply Current

2-Lane Mode, 1.75mA Mode

2-Lane Mode, 3.5mA Mode

l

l

27

49

31

54

mA

mA

IVCC

Amplifier Supply Current

l

208

224

mA

l

l

1271

1311

1473

1517

mW

mW

PDISS

2-Lane Mode, 1.75mA Mode

2-Lane Mode, 3.5mA Mode

PSLEEP

3

mW

PNAP

85

mW

20

mW

PDIFFCLK

Power Decrease with Single-Ended

Encode Mode Enabled

Timing

Characteristics l denotes the specifications which apply over the full operating temperature

The

range, otherwise specifications are at TA = 25°C. (Note 6)

SYMBOL

PARAMETER

CONDITIONS

fS

Sampling Frequency

(Note 10, Note 11)

l

MIN

5

tENCL

ENC Low Time (Note 9)

Duty Cycle Stabilizer Off

Duty Cycle Stabilizer On

l

l

3.8

2

tENCH

ENC High Time (Note 9)

Duty Cycle Stabilizer Off

Duty Cycle Stabilizer On

l

l

3.8

2

tAP

Sample-and-Hold

Acquisition Delay Time

TYP

MAX

UNITS

125

MHz

4

4

100

100

ns

ns

4

4

100

100

ns

ns

0

ns

1/(8•fS)

1/(7•fS)

1/(6•fS)

1/(16•fS)

1/(14•fS)

1/(12•fS)

sec

sec

sec

sec

sec

sec

Digital Data Outputs (RTERM = 100Ω Differential, CL = 2pF to GND on Each Output)

tSER

Serial Data Bit Period

2-Lanes, 16-Bit Serialization

2-Lanes, 14-Bit Serialization

2-Lanes, 12-Bit Serialization

1-Lane, 16-Bit Serialization

1-Lane, 14-Bit Serialization

1-Lane, 12-Bit Serialization

tFRAME

FR to DCO Delay

(Note 9)

l

tDATA

DATA to DCO Delay

(Note 9)

l

0.35•tSER

tPD

Propagation Delay

(Note 9)

l

0.7n + 2•tSER

tR

Output Rise Time

Data, DCO, FR, 20% to 80%

0.17

ns

tF

Output Fall Time

Data, DCO, FR, 20% to 80%

0.17

ns

DCO Cycle-Cycle Jitter

tSER = 1ns

0.35•tSER

Pipeline Latency

0.5•tSER

0.65•tSER

sec

0.5•tSER

0.65•tSER

sec

1.1n + 2•tSER

1.5n + 2•tSER

sec

60

psP-P

6

Cycles

SPI Port Timing (Note 9)

tSCK

SCK Period

tS

Write Mode

Read Back Mode, CSDO = 20pF, RPULLUP = 2k

l

l

40

250

ns

ns

CS to SCK Setup Time

l

5

ns

tH

SCK to CS Setup Time

l

5

ns

tDS

SDI Setup Time

l

5

ns

tDH

SDI Hold Time

l

5

tDO

SCK Falling to SDO Valid

Read Back Mode, CSDO = 20pF, RPULLUP = 2k

l

ns

125

ns

9012fa

For more information www.linear.com/LTM9012

5

�LTM9012

Electrical Characteristics

Note 1: Stresses beyond those listed under Absolute Maximum Ratings

may cause permanent damage to the device. Exposure to any Absolute

Maximum Rating condition for extended periods may affect device

reliability and lifetime.

Note 2: All voltage values are with respect to GND (unless otherwise

noted).

Note 3: Input pins are protected by steering diodes to either supply. If

the inputs should exceed either supply voltage, the input current should

be limited to less than 10mA. In addition, the inputs CHn +, CHn – are

protected by a pair of back-to-back diodes. If the differential input voltage

exceeds 1.4V, the input current should be limited to less than 10mA.

Note 4: When these pin voltages are taken below GND or above VDD, they

will be clamped by internal diodes. This product can handle input currents

greater than 100mA below GND or above VDD without latchup.

Note 5: When these pin voltages are taken below GND they will be

clamped by internal diodes. When these pin voltages are taken above VDD

they will not be clamped by internal diodes. This product can handle input

currents greater than 100mA below GND without latchup.

Note 6: VCC = 3.3V, VDD = OVDD = 1.8V, fSAMPLE = 125MHz, 2-lane output

mode, differential ENC+/ENC – = 2VP-P sine wave, input range = 200mVP-P

with differential drive, unless otherwise noted.

Note 7: Integral nonlinearity is defined as the deviation of a code from a

best fit straight line to the transfer curve. The deviation is measured from

the center of the quantization band.

Note 8: Offset error is the offset voltage measured from –0.5 LSB when

the output code flickers between 00 0000 0000 0000 and 11 1111 1111

1111 in 2’s complement output mode.

Note 9: Guaranteed by design, not subject to test.

Note 10: Recommended operating conditions.

Note 11: The maximum sampling frequency depends on the speed grade

of the part and also which serialization mode is used. The maximum serial

data rate is 1000Mbps so tSER must be greater than or equal to 1ns.

Note 12: Near-channel crosstalk refers to CH1 and CH2. Far channel

crosstalk refers to CH1 to CH4.

Timing Diagrams

2-Lane Output Mode, 16-Bit Serialization*

tAP

ANALOG

INPUT

N+1

N

tENCH

ENC–

tENCL

ENC+

tSER

DCO–

DCO+

tFRAME

FR–

FR+

OUT#A–

OUT#A+

OUT#B–

OUT#B+

tDATA

tSER

tPD

tSER

D5

D3

D1

0

D13 D11 D9

D7

D5

D3

D1

0

D13 D11 D9

D4

D2

D0

0

D12 D10 D8

D6

D4

D2

D0

0

D12 D10 D8

SAMPLE N-6

SAMPLE N-5

SAMPLE N-4

9012 TD01

*SEE THE DIGITAL OUTPUTS SECTION

9012fa

6

For more information www.linear.com/LTM9012

�LTM9012

Timing Diagrams

2-Lane Output Mode, 14-Bit Serialization

tAP

ANALOG

INPUT

N+2

N

tENCH

ENC–

N+1

tENCL

ENC+

tSER

DCO–

DCO+

tFRAME

FR–

FR+

OUT#A–

OUT#A+

OUT#B–

OUT#B+

tDATA

tSER

tPD

tSER

D7

D5

D3

D1 D13 D11 D9

D7

D5

D3

D1 D13 D11 D9

D7

D5

D3

D1 D13 D11 D9

D6

D4

D2

D0 D12 D10 D8

D6

D4

D2

D0 D12 D10 D8

D6

D4

D2

D0 D12 D10 D8

SAMPLE N-6

SAMPLE N-5

SAMPLE N-4

SAMPLE N-3

9012 TD02

NOTE THAT IN THIS MODE FR+/FR– HAS TWO TIMES THE PERIOD OF ENC+/ENC–

2-Lane Output Mode, 12-Bit Serialization

tAP

ANALOG

INPUT

N

N+1

tENCH

ENC–

tENCL

ENC+

tSER

DCO–

DCO+

FR+

tFRAME

tDATA

tPD

tSER

FR–

OUT#A–

OUT#A+

OUT#B–

OUT#B+

tSER

D9

D7

D5

D3 D13 D11 D9

D7

D5

D3 D13 D11 D9

D8

D6

D4

D2 D12 D10 D8

D6

D4

D2 D12 D10 D8

SAMPLE N-6

SAMPLE N-5

SAMPLE N-4

9012 TD03

9012fa

For more information www.linear.com/LTM9012

7

�LTM9012

Timing Diagrams

1-Lane Output Mode, 16-Bit Serialization

tAP

ANALOG

INPUT

N+1

N

tENCH

ENC–

tENCL

ENC+

tSER

DCO–

DCO+

tFRAME

FR–

FR+

OUT#A–

OUT#A+

tDATA

tSER

tPD

D1

D0

0

tSER

0

SAMPLE N-6

D13 D12 D11 D10 D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

0

SAMPLE N-5

0

D13 D12 D11 D10

SAMPLE N-4

9012 TD04

OUT#B+, OUT#B– ARE DISABLED

1-Lane Output Mode, 14-Bit Serialization

tAP

ANALOG

INPUT

N+1

N

tENCH

ENC–

tENCL

ENC+

tSER

DCO–

DCO+

tFRAME

FR–

FR+

OUT#A–

OUT#A+

tDATA

tSER

tPD

D3

D2

SAMPLE N-6

D1

tSER

D0 D13 D12 D11 D10 D9

D8

D7

D6

D5

D4

D3

D2

SAMPLE N-5

D1

D0 D13 D12 D11 D10

SAMPLE N-4

9012 TD05

OUT#B+, OUT#B– ARE DISABLED

9012fa

8

For more information www.linear.com/LTM9012

�LTM9012

Timing Diagrams

1-Lane Output Mode, 12-Bit Serialization

tAP

ANALOG

INPUT

N+1

N

tENCH

ENC–

tENCL

ENC+

tSER

DCO–

DCO+

tFRAME

FR–

FR+

OUT#A–

OUT#A+

tDATA

tSER

tPD

D5

D4

D3

tSER

D2 D13 D12 D11 D10 D9

SAMPLE N-6

D8

D7

D6

D5

D4

D3

D2 D13 D12 D11

SAMPLE N-5

SAMPLE N-4

9012 TD06

OUT#B+, OUT#B– ARE DISABLED

SPI Port Timing (Readback Mode)

tDS

tS

tDH

tSCK

tH

CS

SCK

tDO

SDI

SDO

R/W

A6

A5

A4

A3

A2

A1

A0

XX

D7

HIGH IMPEDANCE

XX

D6

XX

D5

XX

D4

XX

D3

XX

D2

XX

XX

D1

D0

SPI Port Timing (Write Mode)

CS

SCK

SDI

SDO

R/W

A6

A5

A4

A3

A2

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

9012 TD07

HIGH IMPEDANCE

9012fa

For more information www.linear.com/LTM9012

9

�LTM9012

Typical Performance Characteristics

IOVDD vs Sample Rate, 5MHz Sine

Wave Input –1dBFS

60

0

50

64K Point FFT, fIN = 5MHz,

–1dBFS, SENSE = VDD

0

–10

–10

–20

–20

–30

IOVDD (mA)

30

20

1-LANE 1.75mA

1-LANE 3.5mA

2-LANE 1.75mA

2-LANE 3.5mA

10

0

0

25

50

75

100

SAMPLE RATE (Msps)

125

AMPLITUDE (dBFS)

AMPLITUDE (dBFS)

–30

40

–40

–50

–60

–70

–80

–90

–110

–110

–120

–120

0

5 10 15 20 25 30 35 40 45 50 55 60

FREQUENCY (MHz)

0

–10

–20

–20

0.5

0.4

0.3

DNL ERROR (LSB)

–40

–50

–60

–70

–80

0.2

0.1

0

–0.1

–0.2

–90

–100

–100

–110

–110

–0.4

–120

–120

–0.5

5 10 15 20 25 30 35 40 45 50 55 60

FREQUENCY (MHz)

–0.3

0

5 10 15 20 25 30 35 40 45 50 55 60

FREQUENCY (MHz)

9012 G04

Pulse Response

1.5

14000

–5

1.0

12000

–10

0.5

10000

–15

0

8000

–0.5

6000

–25

–1.0

4000

–30

–1.5

2000

–35

8192

12288

OUTPUT CODE

16384

9012 G07

0

dBFS

0

4096

8192

12288

OUTPUT CODE

0

16384

Frequency Response

16000

0

4096

9012 G06

2.0

–2.0

0

9012 G05

Integral Non-Linearity (INL)

vs Output Code

INL ERROR (LSB)

Differential Non-Linearity (DNL)

vs Output Code

–90

0

5 10 15 20 25 30 35 40 45 50 55 60

FREQUENCY (MHz)

9012 G03

–30

AMPLITUDE (dBFS)

AMPLITUDE (dBFS)

–30

–80

0

9012 G02

64K Point 2-Tone FFT, fIN = 70MHz

and fIN = 75MHz, –7dBFS per Tone,

SENSE = VDD

0

–70

–70

–80

–100

–10

–50

–50

–60

–90

9012 G01

–60

–40

–100

64K Point 2-Tone FFT, fIN = 4.8MHz

and fIN = 5.2MHz, –7dBFS per Tone,

SENSE = VDD

–40

64K Point FFT, fIN = 70MHz,

–1dBFS, SENSE = VDD

0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9

TIME (µs)

1

9012 G08

–20

–40

1

10

100

BASEBAND FREQUENCY (MHz)

1000

9012 G09

9012fa

10

For more information www.linear.com/LTM9012

�LTM9012

Pin Functions

VCC1 (H10, H13): Channel 1 Amplifier Supply. VCC is

internally bypassed to ground with 0.1µF in parallel with

0.01µF ceramic capacitors, additional bypass capacitance

is optional. The recommended operating voltage is 3.3V.

VCC2 (C8, C12): Channel 2 Amplifier Supply. VCC is internally bypassed to ground with 0.1µF in parallel with

0.01µF ceramic capacitors, additional bypass capacitance

is optional. The recommended operating voltage is 3.3V.

VCC3 (C2, C6): Channel 3 Amplifier Supply. VCC is internally bypassed to ground with 0.1µF in parallel with

0.01µF ceramic capacitors, additional bypass capacitance

is optional. The recommended operating voltage is 3.3V.

VCC4 (H1, H4): Channel 4 Amplifier Supply. VCC is internally bypassed to ground with 0.1µF in parallel with

0.01µF ceramic capacitors, additional bypass capacitance

is optional. The recommended operating voltage is 3.3V.

VDD (N4, N5, N9, N10): ADC Analog Supply. VDD is internally bypassed to ground with 0.1µF ceramic capacitors,

additional bypass capacitance is optional. The recommended operating voltage is 1.8V.

OVDD (R7, R8, S8): ADC Digital Output Supply. OVDD

is internally bypassed to ground with 0.1µF ceramic capacitors, additional bypass capacitance is optional. The

recommended operating voltage is 1.8V.

GND: Ground. Use multiple vias close to pins.

CH1+ (A11): Channel 1 Noninverting Analog Input.

CH1– (A12): Channel 1 Inverting Analog Input.

CH2+ (A8): Channel 2 Noninverting Analog Input.

CH2– (A9): Channel 2 Inverting Analog Input.

CH3+ (A5): Channel 3 Noninverting Analog Input.

CH3– (A6): Channel 3 Inverting Analog Input.

CH4+ (A2): Channel 4 Noninverting Analog Input.

CH4– (A3): Channel 4 Inverting Analog Input.

SHDN1 (G11): Channel 1 Amplifier Shutdown. Connecting SHDN1 to VCC or floating results in normal (active)

operating mode. Connecting SHDN1 to GND results in a

low power shutdown state on amplifier 1.

SHDN2 (D9): Channel 2 Amplifier Shutdown. Connecting SHDN2 to VCC or floating results in normal (active)

operating mode. Connecting SHDN2 to GND results in a

low power shutdown state on amplifier 2.

SHDN3 (D3): Channel 3 Amplifier Shutdown. Connecting SHDN3 to VCC or floating results in normal (active)

operating mode. Connecting SHDN3 to GND results in a

low power shutdown state on amplifier 3.

SHDN4 (G1): Channel 4 Amplifier Shutdown. Connecting SHDN4 to VCC or floating results in normal (active)

operating mode. Connecting SHDN4 to GND results in a

low power shutdown state on amplifier 4.

ENC+ (N1): Encode Input. Conversion starts on the rising

edge.

ENC– (P1): Encode Complement Input. Conversion starts

on the falling edge.

CS (P4): In serial programming mode, (PAR/SER = 0V),

CS is the serial interface chip select input. When CS is

low, SCK is enabled for shifting data on SDI into the mode

control registers. In the parallel programming mode (PAR/

SER = VDD), CS selects 2-lane or 1-lane output mode. CS

can be driven with 1.8V to 3.3V logic.

SCK (P5): In serial programming mode, (PAR/SER =

0V), SCK is the serial interface clock input. In the parallel

programming mode (PAR/SER = VDD), SCK selects 3.5mA

or 1.75mA LVDS output currents. SCK can be driven with

1.8V to 3.3V logic.

SDI (P3): In serial programming mode, (PAR/SER = 0V),

SDI is the serial interface data Input. Data on SDI is clocked

into the mode control registers on the rising edge of SCK.

In the parallel programming mode (PAR/SER = VDD), SDI

can be used to power down the part. SDI can be driven

with 1.8V to 3.3V logic.

SDO (P9): In serial programming mode, (PAR/SER = 0V),

SDO is the optional serial interface data output. Data on

SDO is read back from the mode control registers and can

be latched on the falling edge of SCK. SDO is an opendrain NMOS output that requires an external 2k pull-up

resistor to 1.8V – 3.3V. If read back from the mode control

registers is not needed, the pull-up resistor is not necessary and SDO can be left unconnected. In the parallel

programming mode (PAR/SER = VDD), SDO is an input

that enables internal 100Ω termination resistors. When

used as an input, SDO can be driven with 1.8V to 3.3V

logic through a 1k series resistor.

9012fa

For more information www.linear.com/LTM9012

11

�LTM9012

Pin Functions

PAR/SER (P10): Programming Mode Selection Pin. Connect to ground to enable the serial programming mode. CS,

SCK, SDI and SDO become a serial interface that controls

the A/D operating modes. Connect to VDD to enable the

parallel programming mode where CS, SCK, SDI and SDO

become parallel logic inputs that control a reduced set of

the A/D operating modes. PAR/SER should be connected

directly to ground or the VDD of the part and not be driven

by a logic signal.

LVDS Outputs

VREF (P11): Reference Voltage Output. VREF is internally

bypassed to ground with a 2.2μF ceramic capacitor, nominally 1.25V.

OUT2A–/OUT2A+, OUT2B–/OUT2B+ (R9/R10, S11/S12):

Serial data outputs for Channel 2. In 1-lane output mode

only OUT2A–/OUT2A+ are used.

SENSE (N11): Reference Programming Pin. Connecting

SENSE to VDD selects the internal reference and a ±0.1V

input range. Connecting SENSE to ground selects the

internal reference and a ±0.05V input range. An external

reference between 0.625V and 1.3V applied to SENSE

selects an input range of ±0.08 • VSENSE. SENSE is internally bypassed to ground with a 0.1μF ceramic capacitor.

OUT3A–/OUT3A+, OUT3B–/OUT3B+ (S2/S3, R4/R5): Serial data outputs for Channel 3. In 1-lane output mode

only OUT3A–/OUT3A+ are used.

All pins in this section are differential LVDS outputs. The

output current level is programmable. There is an optional

internal 100Ω termination resistor between the pins of

each LVDS output pair.

OUT1A–/OUT1A+, OUT1B–/OUT1B+ (Q9/Q10, R11/R12):

Serial data outputs for Channel 1. In 1-lane output mode

only OUT1A–/OUT1A+ are used.

OUT4A–/OUT4A+, OUT4B–/OUT4B+ (R2/R3, Q4/Q5): Serial data outputs for Channel 4. In 1-lane output mode

only OUT4A–/OUT4A+ are used.

FR–/FR+ (S4/S5): Frame Start Output.

DCO–/DCO+ (S9/S10): Data Clock Output.

Pin Configuration Table

1

2

3

4

5

6

7

8

9

10

11

12

13

A

GND

CH4+

CH4–

GND

CH3+

CH3–

GND

CH2+

CH2–

GND

CH1+

CH1–

GND

B

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

C

GND

VCC3

GND

GND

GND

VCC3

GND

VCC2

GND

GND

GND

VCC2

GND

D

GND

GND

SHDN3

GND

GND

GND

GND

GND

SHDN2

GND

GND

GND

GND

E

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

F

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

G

SHDN4

GND

GND

GND

GND

GND

GND

GND

GND

GND

SHDN1

GND

GND

H

VCC4

GND

GND

VCC4

GND

GND

GND

GND

GND

VCC1

GND

GND

VCC1

J

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

K

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

L

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

M

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

N

ENC+

GND

GND

VDD

VDD

GND

GND

GND

VDD

VDD

SENSE

GND

GND

P

ENC–

GND

SDI

CS

SCK

GND

GND

GND

SDO

PAR/SER

REF

GND

GND

Q

GND

GND

GND

OUT4B–

OUT4B+

GND

GND

GND

OUT1A–

OUT1A+

GND

GND

GND

R

GND

OUT4A–

OUT4A+

OUT3B–

OUT3B+

GND

OVDD

OVDD

OUT2A–

OUT2A+

OUT1B–

OUT1B+

GND

GND

OUT3A–

OUT3A+

FR–

FR+

OVDD

DCO–

DCO+

OUT2B–

OUT2B+

GND

S

GND

GND

9012fa

12

For more information www.linear.com/LTM9012

�LTM9012

Block Diagram

3.3V

1.8V

VCC

LTM9012

1.8V

VDD

OVDD

OUT1A+

CH 1

ANALOG

INPUT

OUT1A–

14-BIT

ADC CORE

SHDN1

OUT1B+

OUT1B–

DATA

SERIALIZER

VDD/2

OUT2A+

CH 2

ANALOG

INPUT

OUT2A–

14-BIT

ADC CORE

OUT2B+

OUT2B–

SHDN2

OUT3A+

CH 3

ANALOG

INPUT

OUT3A–

14-BIT

ADC CORE

OUT3B+

OUT3B–

SHDN3

VDD/2

OUT4A+

CH 4

ANALOG

INPUT

OUT4A–

14-BIT

ADC CORE

OUT4B+

OUT4B–

SHDN4

ENC+

DCO±

PLL

ENC–

VREF

FR±

1.25V

REFERENCE

REFH REFL

RANGE

SELECT

REF

BUFFER

SENSE

SDO

SDI

SCK

CS

PAR/SER

MODE

CONTROL

REGISTERS

DIFF. REF.

AMP.

GND

9012 BD

Figure 1. Block Diagram

9012fa

For more information www.linear.com/LTM9012

13

�LTM9012

Applications Information

Converter Operation

The LTM9012 is a low power, 4-channel, 14-bit, 125Msps

A/D converter that is powered by a 1.8V ADC supply and

3.3V driver supplies. Each input includes a fixed gain,

differential amplifier. The analog inputs can be driven differentially or single-ended. The encode input can be driven

differentially for optimal jitter performance, or single-ended

for lower power consumption. The digital outputs are serial

LVDS to minimize the number of data lines. Each channel

outputs two bits at a time (2-lane mode). At lower sampling

rates there is a one bit per channel option (1-lane mode).

Many additional features can be chosen by programming

the mode control registers through a serial SPI port.

Analog Inputs

The analog inputs for each channel of the LTM9012 consist of a differential amplifier with fixed gain followed by

a lowpass filter. The 10x gain version has 49.9Ω series

resistance in each input.

The differential input can support single-ended operation

by connecting the inverting input to a fixed DC voltage or

ground. However, if ground is used, there will be a 6dB

loss of dynamic range. For maximum dynamic range, connect the inverting inputs of the LTM9012 to a DC voltage

equal to the median of the voltage excursions of the noninverting input. An op amp provides an excellent means

of providing a low impedance voltage source capable of

sourcing and sinking small amounts of current. Note the

value of this DC voltage should fall between the limits of

allowable input common mode voltages. See Figure 2 for

an example.

LTM9012

(1 CHANNEL SHOWN)

SIGNAL

–

+

¼LTC6254

VREF

0.1µF

–

+

9012 F02

The gain of the LTM9012 may also be decreased from

the nominal value by adding resistance in series with

the signal inputs. The internal op amps are fed by 49.9Ω

series resistors and employ 511Ω feedback resistors. The

voltage gain of the stage is set by the ratio of the feedback

resistance to the total series resistance. Unity gain, for

example, can be realized by adding a 464Ω resistor in

series with each input.

Reference

The LTM9012 has an internal 1.25V voltage reference. For

a 2V input range using the internal reference with a unity

gain internal amplifier configuration, connect SENSE to VDD.

For a 1V input range using the internal reference, connect

SENSE to ground. For a 2V input range with an external

reference, apply a 1.25V reference voltage to SENSE.

The input range can be adjusted by applying a voltage to

SENSE that is between 0.625V and 1.30V. The input range

will then be 1.6 • VSENSE.

The reference is shared by all four ADC channels, so it is

not possible to independently adjust the input range of

individual channels.

Encode Input

The signal quality of the encode inputs strongly affects

the A/D noise performance. The encode inputs should be

treated as analog signals—do not route them next to digital

traces on the circuit board. There are two modes of operation for the encode inputs: the differential encode mode

(Figure 3), and the single-ended encode mode (Figure 4).

The differential encode mode is recommended for sinusoidal, PECL, or LVDS encode inputs (Figure 5 and Figure 6).

The encode inputs are internally biased to 1.2V through

10k equivalent resistance. The encode inputs can be taken

above VDD (up to 3.6V), and the common mode range is

from 1.1V to 1.6V. In the differential encode mode, ENC–

should stay at least 200mV above ground to avoid falsely

triggering the single-ended encode mode. For good jitter

performance ENC+ should have fast rise and fall times.

RF

SET VREF EQUAL TO THE DC MEDIAN OF THE SIGNAL VOLTAGE

Figure 2. Single-Ended Operation

14

For more information www.linear.com/LTM9012

9012fa

�LTM9012

Applications Information

LTM9012

The single-ended encode mode should be used with CMOS

encode inputs. To select this mode, ENC– is connected

to ground and ENC+ is driven with a square wave encode

input. ENC+ can be taken above VDD (up to 3.6V) so 1.8V

to 3.3V CMOS logic levels can be used. The ENC+ threshold

is 0.9V. For good jitter performance ENC+ should have fast

rise and fall times.

VDD

DIFFERENTIAL

COMPARATOR

VDD

15k

ENC+

ENC–

Clock PLL and Duty Cycle Stabilizer

30k

The encode clock is multiplied by an internal phase-locked

loop (PLL) to generate the serial digital output data. If the

encode signal changes frequency or is turned off, the PLL

requires 25μs to lock onto the input clock.

9012 F03

Figure 3. Equivalent Encode Input Circuit

for Differential Encode Mode

A clock duty cycle stabilizer circuit allows the duty cycle

of the applied encode signal to vary from 30% to 70%.

In the serial programming mode it is possible to disable

the duty cycle stabilizer, but this is not recommended. In

the parallel programming mode the duty cycle stabilizer

is always enabled.

LTM9012

ENC+

1.8V TO 3.3V

0V

ENC–

30k

CMOS LOGIC

BUFFER

9012 F04

Figure 4. Equivalent Encode Input Circuit

for Single-Ended Encode Mode

0.1µF

ENC+

T1

50Ω

0.1µF

Digital Outputs

LTM9012

100Ω

50Ω

0.1µF

ENC–

9012 F05

T1 = MA/COM ETC1-1-13

RESISTORS AND CAPACITORS

ARE 0402 PACKAGE SIZE

Figure 5. Sinusoidal Encode Drive

0.1µF

PECL OR

LVDS

CLOCK

The digital outputs of the LTM9012 are serialized LVDS

signals. Each channel outputs two bits at a time (2-lane

mode). At lower sampling rates there is a one bit per channel option (1-lane mode). The data can be serialized with

16-, 14-, or 12-bit serialization (see the Timing Diagrams

for details). Note that with 12-bit serialization the two LSBs

are not available—this mode is included for compatibility

with potential 12-bit versions of these parts.

The output data should be latched on the rising and falling

edges of the data clock out (DCO). A data frame output

(FR) can be used to determine when the data from a new

conversion result begins. In the 2-lane, 14-bit serialization

mode, the frequency of the FR output is halved.

The maximum serial data rate for the data outputs is 1Gbps,

so the maximum sample rate of the ADC will depend on

the serialization mode as well as the speed grade of the

ENC+

LTM9012

0.1µF

ENC–

9012 F06

Figure 6. PECL or LVDS Encode Drive

9012fa

For more information www.linear.com/LTM9012

15

�LTM9012

Applications Information

ADC (see Table 1). The minimum sample rate for all serialization modes is 5Msps.

By default the outputs are standard LVDS levels: 3.5mA

output current and a 1.25V output common mode voltage. An external 100Ω differential termination resistor

is required for each LVDS output pair. The termination

resistors should be located as close as possible to the

LVDS receiver.

The outputs are powered by OVDD which is isolated from

the A/D core power.

Programmable LVDS Output Current

The default output driver current is 3.5mA. This current

can be adjusted by control register A2 in the serial programming mode. Available current levels are 1.75mA,

2.1mA, 2.5mA, 3mA, 3.5mA, 4mA and 4.5mA. In the

parallel programming mode the SCK pin can select either

3.5mA or 1.75mA.

Optional LVDS Driver Internal Termination

In most cases using just an external 100Ω termination

resistor will give excellent LVDS signal integrity. In addition, an optional internal 100Ω termination resistor can

be enabled by serially programming mode control register

A2. The internal termination helps absorb any reflections

caused by imperfect termination at the receiver. When the

internal termination is enabled, the output driver current is

doubled to maintain the same output voltage swing. In the

parallel programming mode the SDO pin enables internal

termination. Internal termination should only be used with

1.75mA, 2.1mA or 2.5mA LVDS output current modes.

Data Format

Table 2 shows the relationship between the analog input

voltage and the digital data output bits. By default the

output data format is offset binary. The 2’s complement

format can be selected by serially programming mode

control register A1.

Table 2. Output Codes vs Input Voltage

CHn + TO CHn –

(0.2V RANGE)

D13 TO D0

(OFFSET BINARY)

D13 TO D0

(2’s COMPLEMENT)

>0.1000000V

+0.0999878V

+0.0999756V

11 1111 1111 1111

11 1111 1111 1111

11 1111 1111 1110

01 1111 1111 1111

01 1111 1111 1111

01 1111 1111 1110

+0.0000122V

+0.0000000V

–0.0000122V

–0.0000244V

10 0000 0000 0001

10 0000 0000 0000

01 1111 1111 1111

01 1111 1111 1111

00 0000 0000 0001

00 0000 0000 0000

11 1111 1111 1111

11 1111 1111 1110

–0.0999878V

–0.1000000V