A4952 and A4953

Full-Bridge DMOS PWM Motor Drivers

Description

Features and Benefits

• Low RDS(on) outputs

• Overcurrent protection (OCP)

▫ Motor short protection

▫ Motor lead short to ground protection

▫ Motor lead short to battery protection

• Low Power Standby mode

• Adjustable PWM current limit

• Synchronous rectification

• Internal undervoltage lockout (UVLO)

• Crossover-current protection

• Fault output (A4952 only)

• Selectable retry (A4952 only)

Designed for pulse width modulated (PWM) control of DC

motors, the A4952 and A4953 are capable of peak output

currents to ±2 A and operating voltages to 40 V.

Input terminals are provided for use in controlling the speed and

direction of a DC motor with externally applied PWM control

signals. Internal synchronous rectification control circuitry is

provided to lower power dissipation during PWM operation.

Internal circuit protection includes overcurrent protection,

motor lead short to ground or supply, thermal shutdown with

hysteresis, undervoltage monitoring of VBB, and crossovercurrent protection.

Packages:

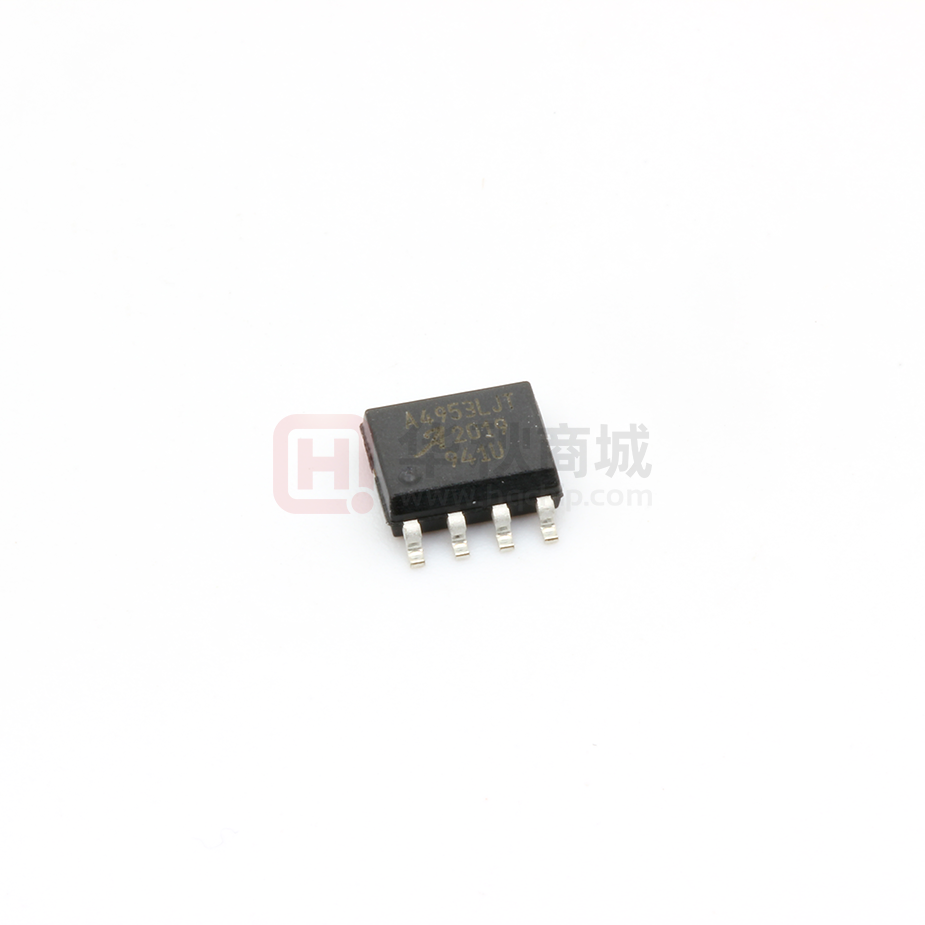

The A4952 is provided in a low-profile 10-pin MSOP package

(suffix LY) and the A4953 is provided in a low-profile

8-pin SOICN package (suffix LJ). Both packages have an

exposed thermal pad, and are lead (Pb) free, with 100% matte tin

leadframe plating.

10-pin MSOP

with exposed thermal pad

(LY package)

8-pin SOICN

with exposed thermal pad

(LJ package)

Not to scale

Functional Block Diagram

Load Supply

VINT

A4952 only

OSC

RTRY

IN1

Charge

Pump

VBB

Control

Logic

Disable

IN2

TSD

UVLO

OUT1

OUT2

7V

GND

A4952 only

FLTn

VREF

A4952-DS, Rev. 3

LSS

÷ 10

(Optional)

�A4952 and

A4953

Full-Bridge DMOS PWM Motor Drivers

Selection Guide

Part Number

Packing

A4952ELYTR-T

A4953ELJTR-T

4000 pieces per 13-in. reel

3000 pieces per 13-in. reel

Absolute Maximum Ratings

Characteristic

Load Supply Voltage

Logic I/O Voltage Range

Symbol

Rating

Unit

VBB

Notes

40

V

VIN

–0.3 to 6

V

FLTn Sink Current

IFLTN

10

mA

VREF Input Voltage Range

VREF

–0.3 to 6

V

VS

–0.5 to 0.5

V

–2 to 42

V

2

A

Sense Voltage (LSS pin)

Motor Outputs Voltage

VOUT

Output Current

IOUT

Duty cycle = 100%

Transient Output Current

iOUT

TW < 500 ns

Operating Temperature Range

Maximum Junction Temperature

Storage Temperature Range

6

A

–40 to 85

°C

TJ(max)

150

°C

Tstg

–55 to 150

°C

TA

Temperature Range E

Thermal Characteristics may require derating at maximum conditions, see application information

Characteristic

Package Thermal Resistance

Symbol

RθJA

Test Conditions*

Value

Unit

LJ package, on 4-layer PCB based on JEDEC standard

35

ºC/W

LJ package, on 2-layer PCB with 0.8 in2. 2-oz. copper each side

62

ºC/W

LY package, on 4-layer PCB based on JEDEC standard

48

ºC/W

LY package, (estimate) on 2-layer PCB with 1 in2. 2-oz. copper each side

60

ºC/W

*Additional thermal information available on the Allegro website.

Terminal List Table

Pin-out Diagrams

GND

1

IN2

2

IN1

3

VREF

4

8 OUT2

PAD

7 LSS

6 OUT1

5 VBB

LJ Package (A4953)

10 GND

FLTn 1

9 OUT2

RTRY 2

IN2 3

IN1 4

VREF 5

PAD

8 LSS

7 OUT1

6 VBB

LY Package (A4952)

Name

Number

Function

A4952

A4953

FLTn

1

–

Fault output, active low

GND

10

1

Ground

IN1

4

3

Logic input 1

IN2

3

2

Logic input 2

LSS

8

7

Power return – sense resistor connection

OUT1

7

6

DMOS full bridge output 1

OUT2

9

8

DMOS full bridge output 2

PAD

–

–

Exposed pad for enhanced thermal dissipation

RTRY

2

–

Logic input

VBB

6

5

Load supply voltage

VREF

5

4

Analog input

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

2

�A4952 and

A4953

Full-Bridge DMOS PWM Motor Drivers

ELECTRICAL CHARACTERISTICS Valid at TJ = 25°C, unless otherwise specified

Characteristics

Symbol

Test Conditions

Min.

Typ.

Max.

Unit

8

–

40

V

IOUT = |1.5 A|, TJ = 25°C

–

0.8

1.0

Ω

IOUT = |1.5 A|, TJ = 125°C

–

1.3

1.6

Ω

fPWM < 30 kHz

–

10

–

mA

Low Power Standby mode

–

–

10

µA

Source diode, If = –1.5 A

–

–

1.5

V

Sink diode, If = 1.5 A

–

–

1.5

V

General

Load Supply Voltage Range

VBB

RDS(on) Sink + Source Total

RDS(on)

Load Supply Current

IBB

Body Diode Forward Voltage

Vf

Logic I/O Inputs

Logic Input Voltage Range

Logic Input Pull-Down Resistance

Logic Input Current

Input Hysteresis

VIN(1)

INx pins

2.0

–

–

V

VIN(0)

INx pins

–

–

0.8

V

VIN(STANDBY) INx pins, Low Power Standby mode

–

–

0.4

V

RLOGIC(PD) VIN = 0 V = IN1 = IN2

–

50

–

kΩ

RR

IIN(1)

INx pins, VIN = 2.0 V

–

40

100

µA

IIN(0)

INx pins, VIN = 0.8 V

–

16

40

µA

–

250

550

mV

VHYS

Logic I/O Inputs (A4952 only)

Retry Input Voltage

VRTRY

RTRY pin = valid

–

–

200

mV

VRTRY(OC)

RTRY pin = open

–

3

–

V

Retry Short Circuit Current

IRTRY

RTRY pin = GND

–

10

–

µA

Fault Output Voltage

VRST

FLTn pin, IOUT = 1 mA

–

–

0.5

V

FLTn pin, no fault, pull-up to 5 V

–

–

1

µA

Retry Overcurrent Protection Pullup

Voltage

Fault Output Leakage Current

ILK

Timing

Crossover Delay

tCOD

50

400

500

ns

VREF Input Voltage Range

VREF

0

–

5

V

VREF / ISS , VREF = 5 V

9.5

–

10.5

V/V

VREF / ISS , VREF = 2.5 V

9.0

–

10.0

V/V

VREF / ISS , VREF = 1 V

8.0

–

10.0

V/V

Current Gain

Blank Time

Constant Off-time

A V

tBLANK

2

3

4

µs

toff

16

25

34

µs

–

1

1.5

ms

–

–

30

µs

7

7.5

7.95

V

–

500

–

mV

–

160

–

°C

°C

Standby Timer

tst

Power-Up Delay

tpu

IN1 = IN2 < VIN(STANDBY)

Protection Circuits

UVLO Enable Threshold

UVLO Hysteresis

Thermal Shutdown Temperature

Thermal Shutdown Hysteresis

VBBUVLO

VBB increasing

VBBUVLOhys

TJTSD

TTSDhys

Temperature increasing

–

20

–

Overcurrent Protection Limit

IOCP

Recovery = TJTSD – TTSDhys

2.5

–

6.5

A

Overcurrent Protection Pulse Width

tOCP

1

–

4

µs

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

3

�A4952 and

A4953

Full-Bridge DMOS PWM Motor Drivers

Characteristic Performance

PWM Control Timing Diagram

VIN(1)

IN1

GND

VIN(1)

IN2

GND

+IREG

IOUT(x)

0A

-IREG

Forward/

Fast Decay

Reverse/

Fast Decay

Forward/

Slow Decay

Reverse/

Slow Decay

PWM Control Truth Table

IN1

IN2

10×VS > VREF

OUT1

OUT2

0

1

1

0

0

1

Function

False

L

H

Reverse

False

H

L

Forward

1

True

H/L

L

Chop (mixed decay), reverse

0

True

L

H/L

Chop (mixed decay), forward

1

1

False

L

L

Brake (slow decay)

0

0

False

Z

Z

Coast, enters Low Power Standby mode after 1 ms

Note: Z indicates high impedance.

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

4

�A4952 and

A4953

Full-Bridge DMOS PWM Motor Drivers

Functional Description

Device Operation

The A4952 and A4953 are designed to operate DC motors. The

output drivers are all low-RDS(on) , N-channel DMOS drivers

that feature internal synchronous rectification to reduce power

dissipation. The current in the output full bridge is regulated with

fixed off-time pulse width modulated (PWM) control circuitry.

The IN1 and IN2 inputs allow two-wire control for the bridge.

Overcurrent Protection

In the A4952, a current monitor will protect the IC from damage

due to output shorts. The internal Overcurrent Protection (OCP)

has the following features:

Protection circuitry includes internal thermal shutdown, and protection against shorted loads, or against output shorts to ground

or supply. Undervoltage lockout prevents damage by keeping the

outputs off until the driver has enough voltage to operate normally.

• Retry Input (RTRY pin). Sets the action taken by the IC to respond to an OCP fault. If the RTRY pin is tied to GND, then the

outputs will be turned-on again after a 2-ms timeout, to check

if a fault condition remains. If the RTRY pin is left open, then

the fault will be latched, and the IC will disable the outputs. The

fault latch can only be cleared by coming out of Low Power

Standby mode or by cycling the power to VBB.

Standby Mode

Low Power Standby mode is activated when both input (INx)

pins are low for longer than 1 ms. Low Power Standby mode

disables most of the internal circuitry, including the charge pump

and the regulator. When the A4952/A4953 is coming out of

standby mode, the charge pump should be allowed to reach its

regulated voltage (a maximum delay of 30 µs) before any PWM

commands are issued to the device.

Internal PWM Current Control

Initially, a diagonal pair of source and sink FET outputs are

enabled and current flows through the motor winding and the

optional external current sense resistor, RS . When the voltage

across RS equals the comparator trip value, then the current sense

comparator resets the PWM latch. The latch then turns off the

sink and source FETs (Mixed Decay mode).

VREF

The maximum value of current limiting is set by the selection of

RSx and the voltage at the VREF pin. The transconductance function is approximated by the maximum value of current limiting,

ITripMAX (A), which is set by:

ITripMAX =

VREF

AV RS

where VREF is the input voltage on the VREF pin (V) and RS is

the resistance of the sense resistor (Ω) on the LSS terminal.

• Fault Output (FLTn pin). If a short is detected, the open drain

FLTn output signal goes low.

Note: The A4953 overcurrent protection behaves in the same

manner but the fault is latched and can only be reset by putting

the device into standby mode or by cycling the power to VBB.

During OCP events, Absolute Maximum Ratings may be

exceeded for a short period of time before the device latches.

Shutdown

If the die temperature increases to approximately 160°C, the full

bridge outputs will be disabled until the internal temperature falls

below a hysteresis, TTSDhys , of 20°C. Internal UVLO is present

on VBB to prevent the output drivers from turning-on below the

UVLO threshold.

Braking

The braking function is implemented by driving the device in

Slow Decay mode, which is done by applying a logic high to both

inputs, after a bridge-enable Chop command (see PWM Control

Truth Table). Because it is possible to drive current in both directions through the DMOS switches, this configuration effectively

shorts-out the motor-generated BEMF, as long as the Chop command is asserted. The maximum current can be approximated by

VBEMF / RL . Care should be taken to ensure that the maximum

ratings of the device are not exceeded in worse case braking situations: high speed and high-inertia loads.

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

5

�A4952 and

A4953

Full-Bridge DMOS PWM Motor Drivers

Synchronous Rectification

When a PWM off-cycle is triggered by an internal fixed off-time

cycle, load current will recirculate. The A4952/A4953 synchronous rectification feature turns-on the appropriate DMOSFETs

during the current decay, and effectively shorts out the body

diodes with the low RDS(on) driver. This significantly lowers

power dissipation. When a zero current level is detected, synchronous rectification is turned off to prevent reversal of the load

current.

Mixed Decay Operation

The bridges operate in Mixed Decay mode. Referring to the

lower panel of the figure below, as the trip point is reached, the

device goes into fast decay mode for 50% of the fixed off-time

period. After this fast decay portion the device switches to slow

decay mode for the remainder of the off-time. During transitions

from fast decay to slow decay, the drivers are forced off for the

Crossover Delay, tCOD . This feature is added to prevent shootthrough in the bridge. During this “dead time” portion, synchronous rectification is not active, and the device operates in fast

decay and slow decay only.

Mixed Decay Mode Operation

VPHASE

+

IOUT

See Enlargement A

0

–

Enlargement A

Fixed Off-Time, toff = 25 µs

0.50 × toff

0.50 × toff

ITrip

IOUT

Fast Decay

tCOD

tCOD

Slow Decay

tCOD

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

6

�A4952 and

A4953

Full-Bridge DMOS PWM Motor Drivers

Application Information

Sense Pin (LSS)

In order to use PWM current control, a low-value resistor is

placed between the LSS pin and ground for current sensing purposes. To minimize ground-trace IR drops in sensing the output

current level, the current sensing resistor should have an independent ground return to the star ground point. This trace should be

as short as possible. For low-value sense resistors, the IR drops in

the PCB can be significant, and should be taken into account.

thermal pad of the device makes a good location for the star

ground point. The exposed pad can be connected to ground for

this purpose.

When selecting a value for the sense resistor be sure not to

exceed the maximum voltage on the LSS pin of ±500 mV at

maximum load. During overcurrent events, this rating may be

exceeded for short durations.

Layout

The PCB should have a thick ground plane. For optimum electrical and thermal performance, the A4952/A4953 must be soldered

directly onto the board. On the underside of the A4952/A4953

package is an exposed pad, which provides a path for enhanced

thermal dissipation. The thermal pad must be soldered directly to

an exposed surface on the PCB in order to achieve optimal thermal conduction. Thermal vias are used to transfer heat to other

layers of the PCB.

Ground

A star ground should be located as close to the A4952/ A4953

as possible. The copper ground plane directly under the exposed

The load supply pin, VBB, should be decoupled with an electrolytic capacitor (typically 100 μF) in parallel with a lower valued

ceramic capacitor placed as close as practicable to the device.

Layout for the A4952 (LY package)

GND

Ground (1 oz.)

PCB

OUT2

Thermal (2 oz.)

Thermal Vias

RS

OUT1

A4952

1

C2

BULK

CAPACITANCE

Trace (2 oz.)

Signal (1 oz.)

LY

Package

C1

Solder

A4952

GND

VBB

RTRY

IN2

IN1

VREF

GND

OUT2

FLTn

PAD

LSS

RS

OUT1

VBB

VBB

C1

GND

C2

GND

Bill of Materials

Item

Reference

Value

Units

Description

1

RS

0.25

(for VREF = 5 V, IOUT = 2 A)

Ω

2512, 1 W, 1% or better,

carbon film chip resistor

2

C1

0.22

µF

X5R minimum, 50 V or greater

3

C2

100

µF

Electrolytic, 50 V or greater

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

7

�A4952 and

A4953

Full-Bridge DMOS PWM Motor Drivers

Layout for the A4953 (LJ package)

GND

Solder

A4953

GND

Trace (2 oz.)

Signal (1 oz.)

Ground (1 oz.)

PCB

OUT2

Thermal Vias

RS

A4953

OUT1

C1

Thermal (2 oz.)

1 GND

C2

BULK

CAPACITANCE

VBB

IN2

IN1

VREF

OUT2

PAD

LSS

RS

OUT1

VBB

VBB

C1

GND

C2

GND

Bill of Materials

Item

Reference

Value

Units

Description

1

RS

0.25

(for VREF = 5 V, IOUT = 2 A)

Ω

2512, 1 W, 1% or better,

carbon film chip resistor

2

C1

0.22

µF

X5R minimum, 50 V or greater

3

C2

100

µF

Electrolytic, 50 V or greater

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

8

�A4952 and

A4953

Full-Bridge DMOS PWM Motor Drivers

Package LJ, 8-Pin SOICN

with exposed thermal pad

4.90 ±0.10

0.65

8°

0°

8

B

A

1

3.90 ±0.10

6.00 ±0.20

0.25 BSC

SEATING PLANE

GAUGE PLANE

Branded Face

SEATING

PLANE

0.10 C

1.27 BSC

1

1.27

0.40

3.30 NOM

0.51

0.31

2.41

1.04 REF

2

8X

C

5.60

2

3.30

C

PCB Layout Reference View

For Reference Only; not for tooling use (reference MS-012BA)

Dimensions in millimeters

Dimensions exclusive of mold flash, gate burrs, and dambar protrusions

Exact case and lead configuration at supplier discretion within limits shown

1.70 MAX

0.15

0.00

1.27

1.75

0.25

0.17

2.41 NOM

8

A Terminal #1 mark area

B

Exposed thermal pad (bottom surface); dimensions may vary with device

C

Reference land pattern layout (reference IPC7351

SOIC127P600X175-9AM); all pads a minimum of 0.20 mm from all

adjacent pads; adjust as necessary to meet application process

requirements and PCB layout tolerances; when mounting on a multilayer

PCB, thermal vias at the exposed thermal pad land can improve thermal

dissipation (reference EIA/JEDEC Standard JESD51-5)

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

9

�A4952 and

A4953

Full-Bridge DMOS PWM Motor Drivers

Package LY, 10-Pin MSOP

with exposed thermal pad

3.00 ±0.10

0° to 6°

10

0.15 ±0.05

3.00 ±0.10

0.30

0.50

10

1.65

4.88 ±0.20

1.73

4.60

A

0.53 ±0.10

1

2

1

0.25

1.98

1

1

Seating Plane

Gauge Plane

2

2

1.98 MIN

C

B

For Reference Only; not for tooling use (reference JEDEC MO-187BA-T)

Dimensions in millimeters

Dimensions exclusive of mold flash, gate burrs, and dambar protrusions

Exact case and lead configuration at supplier discretion within limits shown

1.73

A Terminal #1 mark area

B Exposed thermal pad (bottom surface)

10

0.86 ±0.05

C Reference land pattern layout (reference IPC7351 SOP50P490X110-11M)

All pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary

to meet application process requirements and PCB layout tolerances; when

mounting on a multilayer PCB, thermal vias at the exposed thermal pad land

can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

SEATING

PLANE

0.27

0.18

0.50

REF

0.05

0.15

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

10

�A4952 and

A4953

Full-Bridge DMOS PWM Motor Drivers

Revision History

Revision

Revision Date

Rev. 3

March 12, 2014

Description of Revision

Update Electrical Characteristics table

Copyright ©2010-2014, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to

permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that

the information being relied upon is current.

Allegro’s products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of

Allegro’s product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its

use; nor for any infringement of patents or other rights of third parties which may result from its use.

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

11

�